(19) **日本国特許庁(JP)**

# (12) 特許公報(B2)

(11)特許番号

特許第4219755号 (P4219755)

(45) 発行日 平成21年2月4日(2009.2.4)

(24) 登録日 平成20年11月21日(2008.11.21)

| (51) Int.Cl. |        |            | FΙ   |       |   |

|--------------|--------|------------|------|-------|---|

| HO1L         | 27/146 | (2006.01)  | HO1L | 27/14 | A |

| HO1L         | 31/10  | (2006.01)  | HO1L | 31/10 | A |

| HO4N         | 5/335  | (2006, 01) | HO4N | 5/335 | U |

請求項の数 3 (全 10 頁)

最終頁に続く

| 特願2003-197965 (P2003-197965) | (73)特許権都                                                                                                                                 | <b>對</b> 000116024                                                                                                                                                          |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 平成15年7月16日 (2003.7.16)       |                                                                                                                                          | ローム株式会社                                                                                                                                                                     |

| 特開2005-38938 (P2005-38938A)  |                                                                                                                                          | 京都府京都市右京区西院溝崎町21番地                                                                                                                                                          |

| 平成17年2月10日 (2005.2.10)       | (74) 代理人                                                                                                                                 | 100087701                                                                                                                                                                   |

| 平成16年2月24日 (2004.2.24)       |                                                                                                                                          | 弁理士 稲岡 耕作                                                                                                                                                                   |

| 不服2006-5755 (P2006-5755/J1)  | (74)代理人                                                                                                                                  | 100101328                                                                                                                                                                   |

| 平成18年3月29日 (2006.3.29)       |                                                                                                                                          | 弁理士 川崎 実夫                                                                                                                                                                   |

|                              | (72) 発明者                                                                                                                                 | 澤瀬 研介                                                                                                                                                                       |

|                              |                                                                                                                                          | 京都市右京区西院溝崎町21番地 ローム                                                                                                                                                         |

|                              |                                                                                                                                          | 株式会社内                                                                                                                                                                       |

|                              | (72) 発明者                                                                                                                                 | 松本 裕司                                                                                                                                                                       |

|                              |                                                                                                                                          | 京都市右京区西院溝崎町21番地 ローム                                                                                                                                                         |

|                              | 平成15年7月16日 (2003.7.16)<br>特開2005-38938 (P2005-38938A)<br>平成17年2月10日 (2005.2.10)<br>平成16年2月24日 (2004.2.24)<br>不服2006-5755 (P2006-5755/J1) | 平成15年7月16日 (2003.7.16)<br>特開2005-38938 (P2005-38938A)<br>平成17年2月10日 (2005.2.10)<br>平成16年2月24日 (2004.2.24)<br>不服2006-5755 (P2006-5755/J1)<br>平成18年3月29日 (2006.3.29) (74) 代理人 |

株式会社内

(54) 【発明の名称】 イメージセンサの製造方法およびイメージセンサ

# (57)【特許請求の範囲】

### 【請求項1】

第1導電型の第1領域および上記第1導電型とは異なる第2導電型の第2領域を含む第1フォトダイオードと、上記第2領域および上記第1導電型の第3領域を含む第2フォトダイオードとを有するセンサ部が複数個配列されたイメージセンサの製造方法であって、

半導体基板の上に形成された上記第1領域の上に、<u>上記第2導電型の第1エピタキシャ</u>ル層を形成する工程と、

上記<u>第1エピタキシャル層</u>の上に、<u>上記第1導電型の第2エピタキシャル層</u>を形成する T程と、

上記第1エピタキシャル層から上記第2エピタキシャル層に至る所定の領域に上記第1 導電型への制御のための不純物を導入して、上記第1導電型のウェル層を形成することに より、上記ウェル層により上記第1エピタキシャル層が分離されてなる上記第2領域、お よび上記ウェル層により上記第2エピタキシャル層が分離されてなる上記第3領域を形成 するとともに、上記ウェル層を上記第3領域より不純物濃度が高いものとする工程と、

<u>上記ウェル層を形成する工程の後、上記ウェル層の表面およびその近傍を選択的に酸化</u>させて、素子分離領域を形成する工程と、

上記第3領域の表層部で、当該イメージセンサの受光領域に対応する領域に、上記第1 導電型への制御のための不純物を導入して、上記第3領域の他の部分より不純物濃度が高 い上記第1導電型の第4領域を形成する工程と、

上記素子分離領域と上記第3領域との間に相当する領域に、上記第1導電型で上記第3

領域より不純物濃度が高くされた高濃度領域であって、上記素子分離領域周辺の欠陥が導入されている領域に空乏層が広がらない程度に高い不純物濃度を有する高濃度領域を形成する工程とを含むことを特徴とするイメージセンサの製造方法。

### 【請求項2】

半導体基板に形成された第1導電型の第1領域と、

この第1領域の上にエピタキシャル成長により形成された上記第1導電型とは異なる第2導電型の第2領域と、

この第2領域の上にエピタキシャル成長により形成された上記第1導電型の第3領域と

上記第3領域の表層部で、当該イメージセンサの受光領域に相当する領域に形成され、 上記第3領域の他の部分より不純物濃度が高い上記第1導電型の第4領域とを含み、

上記第1領域および上記第2領域を含む第1フォトダイオードと、上記第2領域および上記第3領域を含む第2フォトダイオードとを有するセンサ部が複数個配列され、

複数の上記第2および第3領域を備え、

上記第3領域より不純物濃度が高く、隣接する上記センサ部の上記第2および第3領域の間に配置された上記第1導電型のウェル層と、

上記ウェル層の上に設けられ、酸化物からなる素子分離領域と、

上記素子分離領域と上記第3領域との間に設けられ、上記第1導電型で上記第3領域より不純物濃度が高い高濃度領域であって、上記素子分離領域周辺の欠陥が導入されている領域に空乏層が広がらない程度に高い不純物濃度を有する高濃度領域とをさらに含むことを特徴とするイメージセンサ。

#### 【請求項3】

上記第1および第2フォトダイオードに逆バイアス電圧を印加するための電源をさらに含むことを特徴とする請求項2記載のイメージセンサ。

【発明の詳細な説明】

[0001]

【発明の属する技術分野】

本発明は、フォトダイオードを含む複数のセンサ部を備えたイメージセンサに関する。

[00002]

【従来の技術】

イメージセンサには、フォトダイオードを備えた複数のセンサ部が配列されていて、そのセンサ部の配列方向に関する光量の分布を測定できるようになっている。このようなフォトダイオードは、従来は、たとえば、導電型がN型の半導体基板(以下、「第1領域」という。)の表層部にP型への制御のための不純物を注入して拡散させることにより製造されていた。これにより、導電型がN型の第1領域と、その上に形成された導電型がP型である領域(以下、「第2領域」という。)とを含む第1フォトダイオードが得られる(たとえば、下記特許文献1参照)。

[0003]

さらに、第2領域の上に導電型がN型である領域(以下、「第3領域」という。)が形成されることがある。この場合、第1フォトダイオードに加えて、第2領域と第3領域とを含む第2フォトダイオードが得られる。この場合、第1および第2フォトダイオードに逆バイアス電圧を印加することにより、第2領域を容易に空乏化することができる。

第 2 領域が完全に空乏化されている場合、同じ光量に対するフォトダイオードによる光起電力(光電流)が最大になるとともに、フォトダイオードの容量は最小となる。

[ 0 0 0 4 ]

このような第3領域は、第2領域を含む領域にN型への制御のための不純物を拡散させることにより形成される。

[0005]

【特許文献1】

特開2000-312024号公報

20

10

30

40

#### [0006]

# 【発明が解決しようとする課題】

ところが、第2領域および第3領域は、所定の不純物濃度プロファイル(所定の厚さおよび所定の不純物濃度)を有して形成されていなければ、第2領域を完全に空乏化することができないが、拡散により正確に不純物濃度プロファイルを制御するのは困難であった。 そこで、この発明の目的は、半導体部の不純物濃度プロファイルを容易に制御できるイメージセンサの製造方法を提供することである。

### [0007]

この発明の他の目的は、<u>第3領域の表面に欠陥が導入されていた場合でも、この欠陥に</u>よる電流のリークが生じないイメージセンサを提供することである。

# [0008]

#### 【課題を解決するための手段および発明の効果】

上記の課題を解決するための請求項1記載の発明は、第1導電型の第1領域(2)およ び上記第1導電型とは異なる第2導電型の第2領域(8)を含む第1フォトダイオード( 24)と、上記第2領域および上記第1導電型の第3領域(9)を含む第2フォトダイオ ード(25)とを有するセンサ部(5)が複数個配列されたイメージセンサ(1)の製造 方法であって、半導体基板(S)の上に形成された上記第1領域の上に、上記第2導電型 の第1エピタキシャル層(31)を形成する工程と、上記第1エピタキシャル層の上に、 上記第1導電型の第2エピタキシャル層(32)を形成する工程と、上記第1エピタキシ ャル層から上記第2エピタキシャル層に至る所定の領域に上記第1導電型への制御のため の不純物を導入して、上記第1導電型のウェル層(13)を形成することにより、上記ウ ェル層により上記第1エピタキシャル層が分離されてなる上記第2領域、および上記ウェ ル層により上記第2エピタキシャル層が分離されてなる上記第3領域を形成するとともに 上記ウェル層を上記第3領域より不純物濃度が高いものとする工程と、上記ウェル層を 形成する工程の後、上記ウェル層の表面およびその近傍を選択的に酸化させて、素子分離 領域(12)を形成する工程と、上記第3領域の表層部で、当該イメージセンサの受光領 域に対応する領域に、上記第1導電型への制御のための不純物を導入して、上記第3領域 の他の部分より不純物濃度が高い上記第1導電型の第4領域(10)を形成する工程と、 上記素子分離領域と上記第3領域との間に相当する領域に、上記第1導電型で上記第3領 域より不純物濃度が高くされた高濃度領域(14)であって、上記素子分離領域周辺の欠 陥が導入されている領域に空乏層が広がらない程度に高い不純物濃度を有する高濃度領域 を形成する工程とを含むことを特徴とするイメージセンサの製造方法である。

#### [0009]

なお、括弧内の英数字は後述の実施形態における対応構成要素等を示す。以下、この項に おいて同じ。

この発明によれば、第 2 領域および第 3 領域は、エピタキシャル成長により形成される。 エピタキシャル成長により、不純物濃度を容易に制御して半導体層を形成できるので、第 2 および第 3 領域の不純物濃度を正確に所定の濃度にできるとともに、第 2 および第 3 領域の厚さを正確に所定の厚さにできる。すなわち、このイメージセンサの製造方法により、第 2 および第 3 領域の不純物濃度プロファイルを容易に制御できる。

# [0010]

第2および第3領域の濃度プロファイルを適当なものとすることにより、第1および第2フォトダイオード(第1領域と第2領域とによるPN接合、および第2領域と第3領域とによるPN接合)に所定の逆バイアス電圧が印加されたときに、第2領域が完全に空乏化するようにすることができる。この場合、第1および第2フォトダイオードの同じ光量に対する光起電力(光電流)が最大になるとともに、当該フォトダイオードの容量は最小となる。すなわち、センサ部を高感度化できる。

#### [0011]

また、この発明によれば、第3領域の表層部に、第3領域の一部をなす第4領域が形成される。第4領域は第3領域の他の部分より不純物濃度が高くされているので、第2フォ

10

20

30

40

トダイオードに逆バイアス電圧が印加された場合でも、第4領域の表面まで空乏層が広がらないようにすることができる。このため、第2エピタキシャル層(第3領域)の表面に欠陥が導入されていた場合でも、この欠陥による電流のリークが生じないようにすることができる。

第1領域は、半導体基板自体であってもよい。また、第1領域は、所定の領域に第1導電型への制御のための不純物が注入された半導体基板上にエピタキシャル層を形成した後、当該不純物を半導体基板およびエピタキシャル層に熱拡散させてなる埋め込み層であってもよい。

# [0012]

この発明によれば、隣接する第2および第3領域がウェル層で分離された複数のセンサ部を形成できる。

また、第 2 領域は導電型が異なる第 1 領域およびウェル層に囲まれるので、 P N 接合によりセンサ部は電気的に分離される。したがって、隣接するセンサ部間でリークする電流を少なくすることができる。これにより、各センサ部で生じる光起電力による光電流を独立して取り出すことができるので、各センサ部で受けられた光量を正確に測定できる。

# [0013]

\_\_ウェル層に加えて、素子分離領域が形成されていることにより、隣接するセンサ部間でリークする電流をさらに少なくすることができる。半導体部がシリコンからなる場合、素子分離領域を形成する工程は、たとえば、LOCOS (localized oxidation of silicon)技術によるものとすることができる。

#### [0014]

このイメージセンサの製造方法は、上記半導体基板に、機能素子を形成する工程をさらに含んでいてもよい。これにより、1つの半導体基板上にセンサ部と機能素子とが形成されたイメージセンサを製造できる。半導体基板に形成される機能素子は、たとえば、NチャネルMOSおよびPチャネルMOSであってもよい。すなわち、上記イメージセンサの製造方法は、上記半導体基板に、CMOS (complementary metal oxide semiconductor)を形成する工程を含んでいてもよい。

#### [0016]

請求項2 記載の発明は、半導体基板(S)に形成された第1導電型の第1領域(2)と、この第1領域の上にエピタキシャル成長により形成された上記第1導電型とは異なる第2導電型の第2領域(8)と、この第2領域の上にエピタキシャル成長により形成された上記第1導電型の第3領域(9)と、上記第3領域の表層部で、当該イメージセンサの受光領域に相当する領域に形成され、上記第3領域の他の部分より不純物濃度が高い上記第1導電型の第4領域(10)とを含み、上記第1領域および上記第2領域を含む第1フォトダイオード(24)と、上記第2領域および上記第3領域を含む第2フォトダイオード(25)とを有するセンサ部(5)が複数個配列され、複数の上記第2および第3領域を備え、上記第3領域より不純物濃度が高く、隣接する上記センサ部の上記第2および第3領域の間に配置された上記第1導電型のウェル層(13)と、上記ウェル層の上に設けられ、酸化物からなる素子分離領域(12)と、上記素子分離領域と上記第3領域との間に設けられ、上記第1導電型で上記第3領域より不純物濃度が高い高濃度領域(14)であって、上記素子分離領域周辺の欠陥が導入されている領域に空乏層が広がらない程度に高い不純物濃度を有する高濃度領域とをさらに含むことを特徴とするイメージセンサ(1)である。

# [0017]

このイメージセンサは、請求項1記載の製造方法により製造することができ、請求項1 記載の製造方法と同様の効果を奏することができる。

#### [0018]

素子分離領域の幅は、ウェル層の幅より広いことが好ましい。

また、上記半導体基板には、機能素子が形成されていてもよい。機能素子は、たとえば、NチャネルMOSおよびPチャネルMOSであってもよい。すなわち、上記半導体基板

10

20

30

40

には、CMOSが形成されていてもよい。

# [0019]

請求項<u>3</u>記載の発明は、上記第1および第2フォトダイオードに逆バイアス電圧を印加するための電源(23)をさらに含むことを特徴とする請求項<u>2</u>記載のイメージセンサである。

### [0020]

この発明によれば、電源により、第1および第2フォトダイオード(第1領域と第2領域とによるPN接合、および第2領域と第3領域とによるPN接合)に逆バイアス電圧を印加して、第2領域をほぼ完全に空乏化できる。

### [0021]

10

20

30

40

#### 【発明の実施の形態】

以下では、添付図面を参照して、本発明の実施の形態について詳細に説明する。

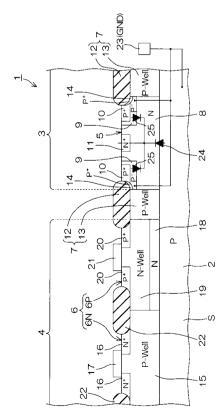

図1は、本発明の一実施形態に係るイメージセンサの構造を示す図解的な断面図である。このイメージセンサ1は、シリコン基板Sに形成された導電型がP型の第1領域2、ならびにその上に形成されたセンサ部形成領域3および機能素子形成領域4を含んでいる。第1領域2は、たとえば、P型への制御のための不純物が導入されてなるシリコン基板S自体であってもよい。

#### [0022]

センサ部形成領域3には、受光により光起電力を生じる複数のセンサ部5がシリコン基板Sの表面に沿って配列されている。各センサ部5では、受ける光量に応じた光起電力が生じる。このため、各センサ部5で生じる光起電力による光電流を測定することにより、センサ部5の配列方向に関する光量の分布を測定できる。

機能素子形成領域4には、機能素子としてNチャネルMOS6NとPチャネルMOS6Pとが形成されている。すなわち、このイメージセンサ1には、NチャネルMOS6NおよびPチャネルMOS6Pを含むCMOS6が形成されている。センサ部形成領域3と機能素子形成領域4(CMOS6のPチャネルMOS6P)との間には、分離部7が形成されている。分離部7により、センサ部形成領域3と機能素子形成領域4とは、電気的に分離されている。

### [0023]

分離部 7 は、イメージセンサ 1 の表層部に形成された L O C O S (localized oxidation o f silicon)による素子分離領域 1 2 、および第 1 領域 2 と素子分離領域 1 2 との間に渡って設けられた導電型が P 型のウェル層 1 3 を含んでいる。ウェル層 1 3 の幅は、素子分離領域 1 2 の幅より小さく、たとえば、 9  $\mu$ m 程度である。

センサ部 5 と C M O S 6 とが 1 つのシリコン基板 S 上に形成されていることにより、センサ部 5 による光電流の生成と、 C M O S 6 による信号処理とが 1 つのシリコン基板 S 上で実施されるようになっている。

# [0024]

センサ部 5 は、シリコン基板 S 上にエピタキシャル成長により形成された導電型が N 型の第 2 領域 8 、および第 2 領域 8 の上にエピタキシャル成長により形成された導電型が P 型の第 3 領域 9 を含んでいる。すなわち、センサ部 5 は、エピタキシャル成長により形成され導電型が異なる 2 つの層を含んでいる。第 2 領域 8 の不純物濃度は、たとえば、 1 × 1 0  $^{15}$  c m  $^{-3}$  以下(たとえば、 7 × 1 0  $^{14}$  c m  $^{-3}$  ないし 1 × 1 0  $^{15}$  c m  $^{-3}$  ) である。

#### [0025]

第3領域9は、センサ部5の表面近傍で中央部を除く領域に形成されており、第3領域9の表層部には、導電型がP<sup>+</sup>型である第4領域10が形成されている。以上のように、センサ部形成領域3は、導電型がP型のシリコン基板S上に、主として、導電型がN型でエピタキシャル成長により形成された第2領域8、導電型がP<sup>-</sup>型でエピタキシャル成長により形成された第3領域9、および導電型がP<sup>+</sup>型である第4領域10が順に形成されてなる4層構造を有している。

# [0026]

また、第 2 領域 8 の上で、シリコン基板 S を垂直に見る平面視においてセンサ部 5 のほぼ中央部には、導電型が N  $^+$ 型である第 5 領域 1 1 が形成されている。第 3 領域 9 と第 5 領域 1 1 との間には、第 2 領域 8 が入り込んでいる。

隣接するセンサ部5の間には分離部7が形成されている。隣接するセンサ部5の間に形成された分離部7と、センサ部形成領域3と機能素子形成領域4との間に形成された分離部7とは、同様の構造を有する。分離部7に備えられたウェル層13の不純物濃度は、第3領域9における第4領域10を除く領域の不純物濃度より高い。

### [0027]

分離部 7 により、隣接するセンサ部 5 の第 2 および第 3 領域 8 , 9 の間が電気的に分離されている。これにより、各センサ部 5 で生じた電流が隣のセンサ部 5 にリークし難くなっている。ウェル層 1 3 に加えて素子分離領域 1 2 が形成されていることにより、隣接するセンサ部 5 間でリークする電流が少なくされている。これにより、このイメージセンサ 1 は、各センサ部 5 で生じた電流を独立に取り出すことができるので、各センサ部 5 が受けた光量を正確に測定することができる。

#### [0028]

各センサ部 5 は、第 1 領域 2 と第 2 領域 8 とを含む第 1 フォトダイオード 2 4 、および 第 2 領域 8 と第 3 領域 9 とを含む第 2 フォトダイオード 2 5 を備えている。第 1 領域 2 は 、分離部 7 により分断されておらず、複数のセンサ部 5 により共有された共通電極となっている。第 5 領域 1 1 は、第 1 および第 2 フォトダイオード 2 4 , 2 5 のカソード取り出し領域として機能する。

センサ部形成領域3において、素子分離領域12の下方(第1領域2側)で、ウェル層13の周囲には、導電型が<u>P</u>+型で第3領域9より不純物濃度が高くされた高濃度領域14が形成されている。高濃度領域14と第3領域9とは接している。素子分離領域12の周辺には、素子分離領域12の形成に伴って導入された欠陥が存在しており、高濃度領域14は、この欠陥が導入された領域を含むより広い領域に形成されている。

#### [0029]

第1領域2および第3領域9には、電源(基準電位)23が接続されている。電源23により、第1フォトダイオード24(第1領域2と第2領域8とによるPN接合)、および第2フォトダイオード25(第2領域8と第3領域9とによるPN接合)に逆バイアス電圧を印加できるようになっている。第2領域8および第3領域9の厚さおよび不純物濃度、ならびに第3領域9の配置は、第1および第2フォトダイオード24,25に所定の大きさの逆バイアス電圧が印加されたときに、第2領域8がほぼ完全に空乏化されるように設定されている。

# [0030]

このイメージセンサ1により、各センサ部5で受けられる光量の測定をするときは、電源23により、第1および第2フォトダイオード24,25に、所定の大きさの逆バイアス電圧が印加され、第2領域8がほぼ完全に空乏化される。

センサ部 5 に光が照射されると、第 1 フォトダイオード 2 4 および第 2 フォトダイオード 2 5 において、その光量に応じた光起電力が生じ、これによる光電流が第 2 領域 8 側から第 1 および第 3 領域 2 ,9 側へと流れる。この際、第 2 領域 8 が完全に空乏化されていることにより、同じ光量に対する第 1 および第 2 フォトダイオード 2 4 , 2 5 による光電流は最大となるとともに、第 1 および第 2 フォトダイオード 2 4 , 2 5 の容量は最小となる。すなわち、センサ部 5 を高感度化できる。

# [0031]

また、第3領域9と高濃度領域14とが接していることにより、第1および第2フォトダイオード24,25に逆バイアス電圧が印加されると、空乏層は高濃度領域14内にも広がる。しかし、高濃度領域14の不純物濃度が高くされていることにより、空乏層は、素子分離領域12周辺の欠陥が導入されている領域には広がらないようにされている。換言すれば、高濃度領域14の不純物濃度は、素子分離領域12周辺の欠陥が導入されている領域に空乏層が広がらない程度に充分高くされている。これにより、イメージセンサ1の

10

20

30

40

(7)

電気特性が変動することがないようにされている。

#### [0032]

NチャネルMOS6Nは、第1領域2の上に形成された導電型がP型であるウェル層15、ウェル層15の表層部に対向配置された導電型がN型の一対のソース/ドレイン領域16、およびウェル層15の上に図示しないゲート絶縁膜を挟んで配置されたゲート電極17を含んでいる。ゲート電極17は、シリコン基板Sに垂直な平面視において、一対のソース/ドレイン領域16にまたがる領域に設けられている。

#### [0033]

一対のソース / ドレイン領域 1 6 の間に一定の大きさの電圧を印加し、ゲート電極 1 7 を 所定の電位にすることにより、一対のソース / ドレイン領域 1 6 の間で、ゲート絶縁膜近 傍のウェル層 1 5 中にチャネルが形成される。これにより、このチャネルに沿って電流( ドレイン電流)が流れる。

PチャネルMOS6Pは、第1領域2の上にエピタキシャル成長されてなる導電型がN型の領域18の上に形成されており、領域18の上に形成された導電型がN型であるウェル層19、ウェル層19の表層部に対向配置された導電型がP型の一対のソース/ドレイン領域20、およびウェル層19の上に図示しないゲート絶縁膜を挟んで配置されたゲート電極21を含んでいる。ゲート電極21は、シリコン基板Sに垂直な平面視において、一対のソース/ドレイン領域20にまたがる領域に設けられている。

#### [0034]

一対のソース / ドレイン領域 2 0 の間に一定の大きさの電圧を印加し、ゲート電極 2 1 を 所定の電位にすることにより、一対のソース / ドレイン領域 2 0 の間で、ゲート絶縁膜近 傍のウェル層 1 9 中にチャネルが形成される。これにより、このチャネルに沿って電流( ドレイン電流)が流れる。

隣接するNチャネルMOS6Nのソース/ドレイン領域16とPチャネルMOS6Pのソース/ドレイン領域20との間には、LOCOSによる素子分離領域22が設けられていて電気的に絶縁されている。

#### [0035]

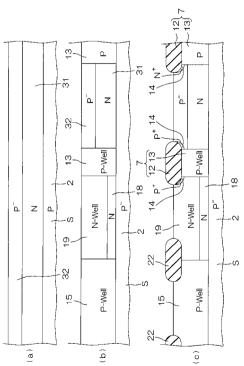

図 2 は、図 1 のイメージセンサ 1 の製造方法を説明するための図解的な断面図である。 先ず、第 1 領域 2 (たとえば、導電型が P 型のシリコン基板 S )の上に、エピタキシャル 成長により、導電型が N 型である第 1 エピタキシャル層 3 1 が形成される。続いて、第 1 エピタキシャル層 3 1 の上に、エピタキシャル成長により、導電型が P 型である第 2 エ ピタキシャル層 3 2 が形成される。この状態が、図 2 (a)に示されている。

#### [0036]

第 1 および第 2 エピタキシャル層 3 1 , 3 2 は、図 1 のイメージセンサ 1 のウェル層 1 3 , 1 9 と比べて不純物濃度が低くされる。たとえば、第 1 エピタキシャル層 3 1 の不純物濃度は、  $1 \times 10^{15}$  c m  $^{-3}$  以下(たとえば、  $7 \times 10^{14}$  c m  $^{-3}$  ないし  $1 \times 10^{15}$  c m  $^{-3}$  )にされる。

エピタキシャル成長により、第1エピタキシャル層31および第2エピタキシャル層32 の不純物濃度を、正確に所定の濃度に制御できるとともに、第1および第2エピタキシャ ル層31,32の厚さを、正確に所定の厚さにすることができる。

# [0037]

次に、第2エピタキシャル層32の高濃度領域14に相当する領域およびこの領域より 浅い領域に、<u>P型への制御のための不純物が導入される。続いて、上記第2エピタキシャル層32の表層部でウェル層15,13に対応する領域に、P型への制御のための不純物が注入され、ウェル層19に対応する領域にN型への制御のための不純物が注入される。その後、これらの不純物が同時に熱拡散されて、ウェル層15,19,13が形成される</u>

# [0038]

第2エピタキシャル層32および第1エピタキシャル層31に対する拡散速度は、P型への制御のための不純物の方がN型への制御のための不純物より大きい。このため、P型へ

10

20

30

40

の制御のための不純物が第1領域2に到達したときには、N型への制御のための不純物は、第1領域2に到達しておらず、このときに拡散を終了することにより、図2(b)に示すように、第1領域2とウェル層19との間に、第1エピタキシャル層31の残部である導電型がN型の領域18が形成される。

### [0039]

ウェル層 1 3 により、センサ部形成領域 3 相当領域の第 1 および第 2 エピタキシャル層 3 1 . 3 2 は、センサ部 5 に相当する複数の領域に分離される。

その後、公知のLOCOS技術により、ウェル層15,19表面でウェル層15とウェル層19との境界部近傍の領域、およびウェル層13の表面近傍の領域が選択的に酸化されて、素子分離領域22,12がそれぞれ形成される。素子分離領域12の幅は、ウェル層13の幅より広くされる。また、素子分離領域12の下方(第1領域2側)には、導電型が $P^+$ 型の高濃度領域14が形成される。この状態が、図2(c)に示されている。

### [0040]

その後、図1のように、所定のパターンの開口を有するマスクを介したP型への制御のための不純物の注入および拡散により、ソース / ドレイン領域20および第4領域10が形成される。また、第2エピタキシャル層32において、図1に示すイメージセンサ1の第3領域9を除く領域に相当する領域に、所定のパターンの開口を有するマスクを介して、N型への制御のための不純物が注入および拡散される。これにより、当該領域の導電型が、第1エピタキシャル層31と同程度の不純物濃度を有するN型にされる。

# [0041]

さらに、所定のパターンの開口を有するマスクを介したN型への制御のための不純物の注入および拡散により、ソース / ドレイン領域 1 6 および第 5 領域 1 1 が形成される。第 2 エピタキシャル層 3 2 の残部と第 4 領域 1 0 とは、第 3 領域 9 となる。また、第 2 エピタキシャル層 3 2 において、第 3 領域 9 と第 5 領域 1 1 との間の部分は、第 1 エピタキシャル層 3 1 の残部とともに、第 2 領域 8 となる。

#### [0042]

その後、機能素子形成領域4の所定の領域に、ゲート絶縁膜およびゲート電極17<u>,2</u> 1が形成されて、図1に示すイメージセンサ1が得られる。

以上のように、第2領域8および第3領域9は、エピタキシャル成長により形成されるので、第2および第3領域8,9の不純物濃度を容易に制御できる。

以上のイメージセンサ1の製造方法において、第1領域2として、導電型がP型にされたシリコン基板Sを使用することができ、シリコン基板Sに埋め込み層を形成する必要はない。このため、工数を少なくすることができる。

#### [0043]

本発明の実施形態の説明は以上の通りであるが、本発明は他の形態でも実施できる。たとえば、第1領域2は、所定の領域にP型への制御のための不純物が注入されたシリコン基板上に第1エピタキシャル層31を形成した後、当該不純物をシリコン基板および第1エピタキシャル層31に熱拡散させてなる埋め込み層であってもよい。

イメージセンサ1の半導体部分の導電型は逆であってもよい。すなわち、上記の実施形態でP型の部分がN型で、上記の実施形態でN型の部分がP型であってもよい。

# [0044]

ウェル層13の代わりに、第2および第3領域8,9(第1および第2エピタキシャル層31,32)を貫通してシリコン基板Sに至るトレンチ(ディープトレンチ)が形成されてなる分離部が形成されていてもよい。すなわち、第2および第3領域8,9(第1および第2エピタキシャル層31,32)の厚さより大きな深さ(たとえば、数μm)を有するディープトレンチが形成されていてもよい。

#### [0045]

この場合、ディープトレンチの内部は、酸化シリコンやポリシリコンで埋められていてもよい。このようなディープトレンチの上に素子分離領域12が形成されてなる分離部によっても、センサ部形成領域3と機能素子形成領域4との間、および複数のセンサ部5の間

10

20

30

40

を電気的に良好に分離できる。

これらの方法によれば、工程は増えるものの、分離領域を小さくできるので、センサ部形成領域3を高密度に形成して、イメージセンサの分解能を向上できるようになる。

#### [0046]

その他、特許請求の範囲に記載された事項の範囲で種々の変更を施すことが可能である。

# 【図面の簡単な説明】

【図1】本発明の一実施形態に係るイメージセンサの構造を示す図解的な断面図である。

【図2】図1のイメージセンサの製造方法を説明するための図解的な断面図である。

# 【符号の説明】

- 1 イメージセンサ

- 2 第1領域

- 5 センサ部

- 8 第2領域

- 9 第3領域

- 10 第4領域

- 13 ウェル層

- 2 3 電源

- 24 第1フォトダイオード

- 25 第2フォトダイオード

- 3 1 第1エピタキシャル層

- 32 第2エピタキシャル層

- S シリコン基板

# 【図1】

# 【図2】

10

# フロントページの続き

(72)発明者 澤 清隆

京都市右京区西院溝崎町21番地 ローム株式会社内

合議体

審判長 河合 章

審判官 近藤 幸浩

審判官 北島 健次

(56)参考文献 特開昭62-131566号公報

特開2001-284629号公報

特開2001-77401号公報