10-2022-0031033

미국 캘리포니아주 94538 프리몬트 레이크뷰 비엘

2022년03월11일

선라이즈 메모리 코포레이션

## (19) 대한민국특허청(KR) (12) 공개특허공보(A)

(51) 국제특허분류(Int. Cl.)

**H01L 27/11565** (2017.01) **H01L 21/28** (2006.01) H01L 27/11568 (2017.01) H01L 27/11578 (2017.01)

(52) CPC특허분류

**H01L 27/11565** (2013.01) **H01L 27/11568** (2013.01)

(21) 출원번호 10-2022-7003041

(22) 출원일자(국제) 2020년07월09일 심사청구일자

(85) 번역문제출일자 **2022년01월26일**

(86) 국제출원번호 PCT/US2020/041343

(87) 국제공개번호 WO 2021/007399 국제공개일자 2021년01월14일

(30) 우선권주장

62/872,174 2019년07월09일 미국(US)

(72) 발명자

푸라야스, 비노드

미국 애리조나 86336 세도나 메도우락 레인 85

친, 우-이 헨리 미국 캘리포니아 95120 산호세 엘드리지 디알. 6844

(74) 대리인

(11) 공개번호

(43) 공개일자

브이디. 46831

(71) 출원인

특허법인 광장리앤고

전체 청구항 수 : 총 33 항

## (54) 발명의 명칭 수평 NOR형 메모리 스트링의 3차원 어레이를 위한 공정

#### (57) 요 약

본원에 제공된 HNOR 어레이를 위한 고효율 제조 공정에서는, HNOR 어레이의 저장 트랜지스터의 채널 영역이 증착 후, 로컬 워드 라인의 형성 전에 수행되는 전하 포획재의 후속 증착까지 보호층에 의해 보호된다. 채널 영역용 실리콘과 보호재는 모두 비정질 형태로 증착된 다음 어닐링 단계를 통해 후속적으로 결정화될 수 있다. 보호재 는 실리콘 붕소, 실리콘 탄소 또는 실리콘 게르마늄일 수 있다. 보호재는 채널 영역의 결정화된 실리콘에 보다 큰 결정립계를 유도하여 보다 높은 전하 운반자 이동도와, 보다 높은 전도도와, 보다 높은 전류 밀도를 제공한다.

## (52) CPC특허분류

**H01L 27/11578** (2013.01) **H01L 29/40117** (2021.08)

## 명세서

## 청구범위

#### 청구항 1

공정에 있어서.

기판의 평평한 표면 위에 복수의 재료층 그룹을 포함하는 구조물을 형성하는 단계 - 각각의 재료층 그룹("활성 층")은 상기 기판의 평평한 표면에 실질적으로 직교하는 제1 방향을 따라 적충되어 제공되고, 각각의 활성층은 (i) 제1 재료의 제1 및 제2 층과, (ii) 상기 제1 재료의 상기 제1 및 제2 층 사이에 제공되는 제2 재료의 층과, (iii) 상기 활성층을 인접한 활성층으로부터 분리하는 격리층을 포함함 -;

상기 활성층을 통해 제1 트렌치 세트를 에칭하는 단계 - 각각의 트렌치는 상기 기판의 평평한 표면에 실질적으로 평행한 제2 방향을 따라 진행하여 상기 구조물로부터 제1 복수의 재료 스택("활성 스택")을 형성함 -;

각각의 활성 스택에서, 상기 활성 스택의 측벽으로부터 상기 제2 재료의 각각의 층의 일부를 제거함으로써 상기 제2 재료의 층 내로 리세스를 형성하는 단계;

상기 활성 스택의 측벽 위에 제3 재료의 층을 등각 증착하는 단계;

상기 제3 재료의 층 위에 제4 재료의 층을 증착하고 상기 리세스를 충전하는 단계;

각각의 활성 스택의 각각의 리세스에서 상기 제4 재료의 층의 일부를 존속시켜 상기 제3 재료의 층의 대응하는 일부를 덮으면서, 상기 활성 스택의 측벽 상의 상기 제3 재료의 층을 노출시키도록 상기 제4 재료의 층을 에칭 백하는 단계;

상기 활성 스택의 측벽으로부터 상기 제3 재료의 층의 노출된 부분을 제거하는 단계;

상기 제1 트렌치 세트를 제5 재료로 충전하는 단계를 포함하는, 공정.

### 청구항 2

제1항에 있어서,

상기 격리층은 실리콘 산탄화물(SiOC)을 포함하는, 공정.

## 청구항 3

제1항에 있어서.

상기 제2 재료는 실리콘 산화물을 포함하는, 공정.

### 청구항 4

제1항에 있어서,

상기 제5 재료는 상기 제2 재료를 포함하는, 공정.

## 청구항 5

제1항에 있어서,

상기 제3 재료는 제1 전도성을 갖는 반도체 재료를 포함하는, 공정.

## 청구항 6

제5항에 있어서,

상기 제1 재료는 상기 제1 전도성과 반대되는 제2 전도성을 갖는 반도체 재료를 포함하고, 상기 제1 재료는 상기 제3 재료보다 도펀트 농도가 높은, 공정.

### 청구항 7

제5항에 있어서,

상기 제4 재료는 실리콘 탄소, 실리콘 붕소 및 실리콘 게르마늄 중 하나를 포함하는, 공정.

#### 청구항 8

제7항에 있어서,

상기 제3 및 제4 재료는 각각 먼저 비정질 형태로 증착되고, 어닐링 단계를 이용하여 후속적으로 결정화되는, 공정.

### 청구항 9

제5항에 있어서,

각각의 활성 스택의 상기 활성층을 통해 제2 트렌치 세트를 생성하기 위해 상기 제1 복수의 활성 스택의 상기 활성층을 에칭하는 단계를 추가로 포함하고, 각각의 트렌치는 상기 제2 방향을 따라 진행하여 상기 제1 복수의 활성 스택으로부터 제2 복수의 활성 스택을 형성하는, 공정.

## 청구항 10

제9항에 있어서.

상기 제1 복수의 활성 스택의 상기 활성층을 에칭하는 단계 이전에, 상기 제5 재료을 추가로 포함하고, 각각의 기둥은 상기 제1 복수의 활성 스택 중 하나를 통해 상기 기판 내로 진행하는, 공정.

### 청구항 11

제10항에 있어서,

상기 기둥은 상기 제1 방향 및 상기 제2 방향 모두에 실질적으로 직교하는 제3 방향을 따라 서로 엇갈린 (staggered) 대형으로 제공되는, 공정.

### 청구항 12

제9항에 있어서,

상기 제2 복수의 활성 스택의 각각의 활성 스택에서, 상기 활성 스택의 측벽으로부터 상기 제2 재료의 각각의 층의 일부를 제거함으로써 상기 제2 재료의 층 내로 리세스를 형성하는 단계;

상기 제2 복수의 활성 스택의 노출된 측벽 위에 상기 제3 재료의 층을 등각 증착하는 단계;

상기 제2 복수의 활성 스택의 노출된 측벽 상에 있는 상기 제3 재료의 층 위에 제4 재료의 층을 증착하고 상기 제2 복수의 활성 스택의 상기 리세스를 충전하는 단계;

상기 제2 복수의 활성 스택 각각의 각각의 리세스에서 상기 제3 재료의 층의 대응하는 일부를 덮도록 상기 제4 재료의 층의 일부를 존속시키면서, 상기 제2 복수의 활성 스택의 상기 측벽 상에 있는 상기 제3 재료의 층을 노출시키도록 상기 제4 재료의 층의 노출된 부분을 에칭 백하는 단계;

상기 제2 복수의 활성 스택의 상기 측벽으로부터 상기 제3 재료의 층의 노출된 부분을 제거하는 단계; 및 상기 제2 트렌치 세트를 상기 제5 재료로 충전하는 단계를 추가로 포함하는, 공정.

### 청구항 13

제12항에 있어서,

상기 제1 재료는 희생재를 포함하고,

상기 공정은,

상기 제2 복수의 활성 스택의 각각의 활성 스택에 리세스를 형성하는 단계에 앞서, 상기 제1 전도성과 반대되는 제2 전도성의 반도체 재료로 상기 희생재를 대체하는 단계를 추가로 포함하고, 상기 제2 전도성의 상기 반도체 재료는 상기 제3 재료보다 높은 도펀트 농도를 가지는, 공정.

### 청구항 14

제12항에 있어서,

각각의 활성층은, 상기 제1 재료의 제1 층과 접촉하는 희생재의 층을 추가로 포함하고, 상기 공정은 상기 제2 복수의 활성 스택의 각각의 활성 스택에 리세스를 형성하는 것 이전에, 금속 도체로 상기 희생재를 대체하는 단 계를 추가로 포함하는, 공정.

### 청구항 15

제12항에 있어서,

상기 제4 재료의 상기 일부를 각각의 샤프트에 노출시키는, 복수의 샤프트를 상기 제1 및 제2 트렌치 세트에 형성하는 단계; 및

상기 제3 재료의 상기 대응하는 일부를 노출시키기 위해 상기 제4 재료의 상기 일부를 제거하는 단계를 추가로 포함하는, 공정.

### 청구항 16

제15항에 있어서,

상기 샤프트의 측벽 상에 전하 포획층을 제공하는 단계를 추가로 포함하는, 공정.

#### 청구항 17

제16항에 있어서,

도전재로 상기 샤프트를 충전하는 단계를 추가로 포함하는, 공정.

### 청구항 18

제15항에 있어서,

상기 샤프트는 연속적인 제1 및 제2 에칭 단계에서 형성되고, 상기 제1 에칭 단계에서 형성된 상기 샤프트는 상기 제1 및 제2 단계 사이에서 희생재로 충전되는, 공정.

## 청구항 19

제18항에 있어서,

상기 희생재는 실리콘 산탄화물(SiOC)을 포함하는, 공정.

#### 청구항 20

제16항에 있어서,

상기 구조물을 형성하는 것 이전에, 상기 평평한 표면 위에 제1 복수의 도체를 형성하는 단계와,

상기 샤프트를 형성하는 상기 제1 에칭 단계에 후속하여, (i) 상기 도체 중에서 선택된 도체를 노출시키기 위해 상기 샤프트 중에서 선택된 샤프트를 굴착하는 단계와, (ii) 제2 복수의 도체 중 일부가 상기 제1 복수의 도체 중 상기 노출된 도체와 접촉하도록, 상기 제2 복수의 도체로 상기 샤프트를 충전하는 단계를 추가로 포함하는, 공정.

### 청구항 21

제20항에 있어서,

상기 제2 복수의 활성 스택은 HNOR 어레이를 형성하고, 상기 HNOR 어레이의 각각의 활성 스택의 각각의 활성층은 상기 제2 방향을 따라 상기 활성층에 형성되는 복수의 저장 트랜지스터를 위한 공통 소스 영역, 공통 드레인 영역 및 채널 영역을 제공하는, 공정.

### 청구항 22

제21항에 있어서,

상기 제1 복수의 도체는 글로벌 워드 라인의 네트워크를 제공하고, 상기 제2 복수의 도체는 상기 HNOR 어레이의 상기 저장 트랜지스터를 위한 복수의 로컬 워드 라인을 제공하는, 공정.

### 청구항 23

제1항에 있어서,

상기 구조물과 상기 기판의 평평한 표면 사이에 에칭 정지층을 제공하는 단계를 추가로 포함하는, 공정.

### 청구항 24

제5항에 있어서,

상기 제1 재료는 희생재를 포함하고,

상기 공정은 상기 제1 전도성과 반대되는 제2 전도성의 반도체 재료에 의해 상기 희생재를 대체하는 단계를 추가로 포함하고, 상기 제2 전도성의 상기 반도체 재료는 상기 제3 재료보다 도펀트 농도가 높은, 공정.

### 청구항 25

제5항에 있어서,

각각의 활성층은 상기 제1 재료의 상기 제1 층과 접촉하는 희생재의 층을 추가로 포함하고,

상기 공정은, 상기 제2 복수의 활성 스택의 각각의 활성 스택에 리세스를 형성하는 것 이전에, 금속 도체로 상기 희생재를 대체하는 단계를 추가로 포함하는, 공정.

### 청구항 26

제5항에 있어서,

상기 제4 재료의 상기 일부를 각각의 샤프트에서 노출시키는, 복수의 샤프트를 상기 트렌치에 형성하는 단계; 및

상기 제3 재료의 상기 대응하는 일부를 노출시키기 위해 상기 제4 재료의 상기 일부를 제거하는 단계를 추가로 포함하는, 공정.

## 청구항 27

제26항에 있어서,

상기 샤프트에 노출된 상기 활성 스택의 측벽 상에 전하 포획층을 제공하는 단계를 추가로 포함하는, 공정.

## 청구항 28

제27항에 있어서,

도전재로 상기 샤프트를 충전하는 단계를 추가로 포함하는, 공정.

## 청구항 29

제27항에 있어서,

상기 샤프트는 연속적인 제1 및 제2 에칭 단계에서 형성되고, 상기 제1 에칭 단계에서 형성된 상기 샤프트는 상기 제1 및 제2 단계 사이에서 희생재로 충전되는, 공정.

## 청구항 30

제29항에 있어서,

상기 희생재는 실리콘 산탄화물(SiOC)을 포함하는, 공정.

## 청구항 31

제27항에 있어서,

상기 구조물을 형성하는 것 이전에, 상기 평평한 표면 위에 제1 복수의 도체를 형성하는 단계와,

상기 샤프트를 형성하는 상기 제1 에칭 단계에 후속하여, (i) 상기 도체 중 선택된 도체를 노출시키기 위해 상기 샤프트 중 선택된 샤프트를 굴착하는 단계와, (ii) 제2 복수의 도체 중 일부가 상기 제1 복수의 도체 중 상기 노출된 도체와 접촉하도록, 상기 제2 복수의 도체로 상기 샤프트를 충전하는 단계를 추가로 포함하는, 공정.

### 청구항 32

제31항에 있어서,

상기 활성 스택은 HNOR 어레이를 형성하고, 상기 HNOR 어레이의 각각의 활성 스택의 각각의 활성층은 상기 제2 방향을 따라 상기 활성층에 형성되는 복수의 저장 트랜지스터를 위한 공통 소스 영역, 공통 드레인 영역 및 채 널 영역을 제공하는, 공정.

## 청구항 33

제32항에 있어서,

상기 제1 복수의 도체는 글로벌 워드 라인의 네트워크를 제공하고, 상기 제2 복수의 도체는 상기 HNOR 어레이의 상기 저장 트랜지스터를 위한 복수의 로컬 워드 라인을 제공하는, 공정.

### 발명의 설명

## 기술분야

[0001] 1. 발명의 분야

[0002] 본 발명은 메모리 회로의 제조 공정에 관한 것이다. 상세하게는, 본 발명은 NOR형 메모리 스트링의 3차원 어레이의 제조 공정에 관한 것이다.

### 배경기술

[0003] 2. 관련 기술의 논의

[0004]

정규 출원은 수평 NOR형 메모리 스트링의 3차원 어레이("HNOR 어레이") 및 이러한 HNOR 어레이를 제조하는 방법 을 개시한다. 본 명세서에서, NOR형 메모리 스트링은 공통 소스 영역과 공통 드레인 영역을 공유하는 다수의 저장 트랜지스터를 포함한다. 이러한 맥락에서 저장 트랜지스터는 그 임계 전압이 채널 영역과 게이트 영역 사 이에 제공되는 전하 저장 영역(예컨대, 산화물-질화물-산화물 삼중층)에 포획 또는 저장되는 전하량에 의해 결 정되는 가변 임계값 트랜지스터이다. 저장 트랜지스터에서 수행되는 읽기(reading), 프로그래밍(programming), 금지(inhibiting) 및 소거(erasing) 동작은 저장 트랜지스터의 소스, 드레인, 게이트 및 채널 영역에 적절한 전 압 바이어스를 인가함으로써 수행된다. 일례로, HNOR 어레이는 반도체 기판의 평평한 표면 위에 제조되고 수평 NOR형 메모리 스트링("HNOR 메모리 스트링")의 규칙적인 배열을 포함한다. 본 개시에서, 용어 "수평"은 평평한 표면에 실질적으로 평행한 방향을 지칭하고 용어 "수직"은 평평한 표면에 실질적으로 직교하는 방향을 지칭한다. 각각의 HNOR 스트링은 반도체 재료의 스트립("활성 스트립")의 일측 또는 양측을 따라 형성되는 저 장 트랜지스터를 포함하되, 각각의 활성 스트립은 (i) 저장 트랜지스터용 공통 드레인 및 공통 소스 영역을 각 각 제공하는 2개의 고농도 도핑된 반도체층과 (ii) 고농도 도핑된 반도체층들 사이에 제공되는 저농도 도핑된 반도체 층을 포함한다. 저농도 도핑된 반도체층은 저장 트랜지스터용 채널 영역을 제공한다. 이 예에서, 고농 도 도핑된 반도체층들 중 적어도 하나는 해당 고농도 도핑된 반도체 층의 전기 저항을 저감하기 위해 그 길이를 따라 금속 도전층과 접촉된다. 다수의 활성 스트립은 서로 적층될 수 있으며("활성 스택"), 다수의 활성 스택 은 나란히 형성되고 서로 이격되어 HNOR 어레이를 형성할 수 있다. 각각의 활성 스택의 측벽에는 전하 포획층 이 제공된다. 인접한 활성 스택 사이에는 수직 도체가 제공되는데, 각각의 수직 도체는 서로 인접한 두 활성 스 택의 다수의 활성 스트립에 있는 저장 트랜지스터의 게이트 전극을 연결하는 로컬 워드 라인 역할을 한다. 저 장 트랜지스터는 활성 스트립의 저농도 도핑된 반도체층이 전하 포획재에 의해 수직 도체와 분리된 상태로 수직 도체에 중첩되는 위치에 형성될 수 있다.

### 발명의 내용

## 해결하려는 과제

[0005] 본 발명은 HNOR 어레이의 고효율 제조 공정을 제공한다. 이들 공정에서, HNOR 어레이의 저장 트랜지스터의 채널 영역은 증착 후, 로컬 워드 라인의 형성 전에 수행되는 전하 포획재의 후속 증착 전까지 보호층에 의해 보호된다. 채널 영역용 실리콘과 보호재는 모두 비정질 형태로 증착될 수 있고 후속적으로 어닐링 단계에서 결정화된다. 보호재는 실리콘 붕소, 실리콘 탄소, 또는 실리콘 게르마늄일 수 있다. 보호재는 채널 영역의 결정화된실리콘에 보다 큰 결정립계를 유도하여 보다 높은 전하 운반자 이동도, 보다 높은 전도도 및 보다 높은 전류 밀도를 제공한다.

## 과제의 해결 수단

- [0006] 본 발명의 일 실시예에 따르면, (a) 기판의 평평한 표면 위에 복수의 재료층 그룹을 포함하는 구조물을 형성하는 단계 각각의 재료층 그룹("활성충")은 기판의 평평한 표면에 실질적으로 직교하는 제1 방향을 따라 적충되어 제공되고, 각각의 활성층은 (i) 제1 재료의 제1 및 제2 층과, (ii) 제1 재료의 제1 및 제2 층 사이에 제공되는 제2 재료의 충과, (iii) 인접한 활성층으로부터 활성층을 분리하는 격리층을 포함함 -; (b) 활성층을 통해제1 트렌치 세트를 예칭하는 단계 각각의 트렌치는 기판의 평평한 표면에 실질적으로 평행한 제2 방향을 따라진행하여 구조물로부터 제1 복수의 재료 스택("활성 스택")을 형성함 -; (c) 각각의 활성 스택에서, 활성 스택의 측벽으로부터 제2 재료의 각각의 층의 일부를 제거함으로써 제2 재료의 층 내로 리세스를 형성하는 단계; (d) 활성 스택의 측벽 위에 채널 재료의 층을 등각 중착하는 단계; (e) 채널 재료의 층의 대응하는 일부를 모도록 보호재의 층의 일부를 존속시키면서, 활성 스택의 측벽 상에 있는 채널 재료의 층을 노출시키기 위해 보호재의 층을 에칭 백(etching back)하는 단계; (g) 활성 스택의 측벽으로부터 채널 재료의 층의 노출된 부분을 제거하는 단계; 및 (h) 제1 트렌치 세트를 제5 재료로 충전하는 단계를 포함하는 공정이 제공된다.

- [0007] 일부 실시예에서, 격리층은 실리콘 산탄화물(SiOC)을 포함하고, 제2 재료는 제5 재료용으로도 선택될 수 있는 실리콘 산화물을 포함한다. 채널 재료는 저농도 도핑된 p형 또는 n형 반도체 재료일 수 있는 반면, 제1 재료는 고농도 도핑된 n형 또는 p형 반도체 재료(즉, 도펀트 유형이 제3 재료와 반대되는 반도체 재료)일 수 있다. 반도체 재료에 대한 증착 및 인시츄 도핑 단계의 횟수를 저감하기 위해 제1 재료는 먼저 희생재로서 제공된 다음 반도체 재료로 후속적으로 대체될 수 있다.

- [0008] 활성 스택은 복수의 트렌치 형성 단계를 통해 형성될 수 있는데, 각각의 연속적인 트렌치 형성 단계는 활성 스택을 보다 좁은 활성 스택들로 분할한다. 트렌치 형성 단계 중에 활성 스택에 기계적 지지를 제공하기 위해 산화물 기둥이 제공될 수 있다. 산화물 기둥은 기판에 고정될 수 있다.

- [0009] 본 발명의 일 실시예에 따르면, 각각의 트렌치 형성 단계 후에, 상기 단계 (c) 내지 (g)가 반복되어 채널 재료 와 보호 커버를 제공한다. 그 후, 본 공정은 (a) 각각의 샤프트에서 보호재의 일부를 노출시키는, 복수의 샤프트를 트렌치에 형성하고, (b) 채널 재료의 대응하는 일부를 노출시키기 위해 보호재의 일부를 제거한다. 이어서, 전하 포획층이 샤프트의 측벽에 증착되고 샤프트가 도전재로 충전될 수 있다. 일부 실시예에서, 샤프트는 다수의 연속 에칭 단계를 통해 형성될 수 있다. 각각의 에칭 단계에서, 이전 에칭 단계에서 형성된 샤프트가 희생재로 충전된다. 이렇게 하여, 에칭 단계가 고종횡비 에칭 단계이더라도 희생재가 기계적 지지를 제공하게된다. 희생재는 예를 들어 실리콘 산탄화물(SiOC)일 수 있다.

- [0010] 본 발명의 공정 단계들을 이용하여, 이와 같이 형성된 HNOR 어레이의 각각의 활성 스택의 각각의 활성층은 저장 트랜지스터용 공통 소스 영역, 공통 드레인 영역 및 채널 영역을 포함한다. 샤프트 내의 도체는 로컬 워드 라인을 제공한다. 로컬 워드 라인은 HNOR 어레이 상부 또는 하부에 제공될 수 있는 글로벌 워드 라인에 의해 디코딩 회로에 연결될 수 있다.

- [0011] 첨부된 도면과 함께 아래의 상세한 설명을 고려하면 본 발명을 더욱 잘 이해할 수 있을 것이다.

### 도면의 간단한 설명

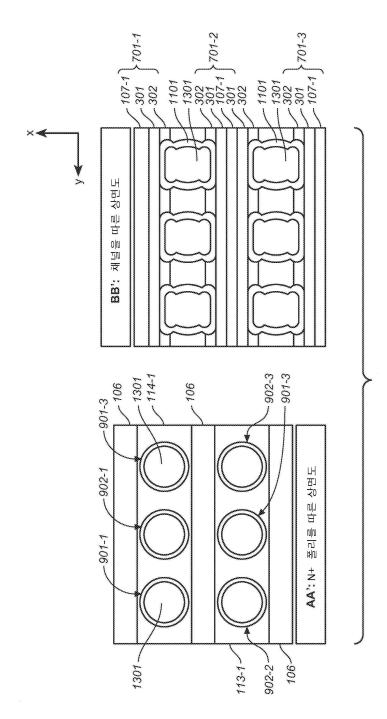

[0012] 도 1은 본 발명의 일 실시예에 따른 HNOR 어레이 제조 공정의 한 중간 단계에서 반도체 구조물(100)의 단면 A 및 B를 도시한다.

도 2는 본 발명의 일 실시예에 따른 리세스 단계를 통해 HTO층(107)에 리세스가 생성된 후의 도 1의 반도체 구조물(100)의 결과적인 단면 A 및 B를 도시한다.

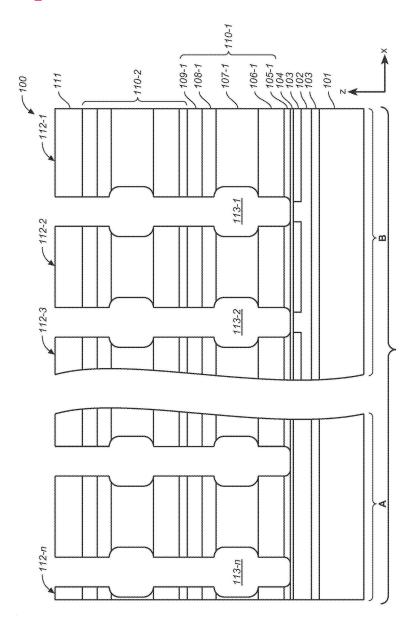

도 3은 본 발명의 일 실시예에 따른 비정질 실리콘층(301) 및 SiGe층(302)의 증착 후의 도 2의 반도체 구조물 (100)의 결과적인 단면 A 및 B를 도시한다.

도 4는 본 발명의 일 실시예에 따른 SiGe층(302)의 이방성 및 등방성 에칭 단계 후의 도 3의 반도체 구조물 (100)의 결과적인 단면 A 및 B를 도시한다.

도 5는 본 발명의 일 실시예에 따른 폴리실리콘층(301)의 등방성 에칭 단계 후의 도 4의 반도체 구조물(100)의 결과적인 단면 A 및 B를 도시한다.

도 6a는 본 발명의 일 실시예에 따른 도 5의 반도체 구조물(100)의 예시적인 활성 스택(112-1 내지 112-3) 상의 예시적인 기둥(601-1 내지 601-5)의 위치를 보여주는 상면도(즉, X-Y 평면도)이다.

도 6b는 본 발명의 일 실시예에 따른 실리콘 산화물을 이용한 기둥(601) 및 트렌치(112)의 충전 및 CMP에 의한 평탄화 후의 도 5의 반도체 구조물(100)의 단면 A 및 B를 도시한다.

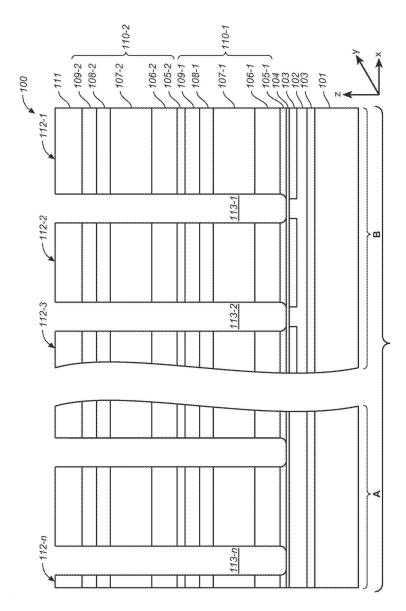

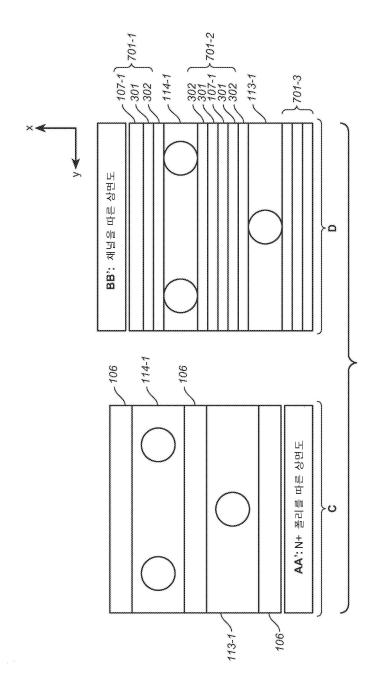

도 7은 본 발명의 일 실시예에 따라 에칭 정지층(104)에 이르기까지 활성층을 에칭함으로써 활성 스택(112-2, 112-3)에 트렌치(114-1, 114-2)를 생성한 후의 도 6b의 반도체 구조물(100)의 결과적인 단면 A 및 B를 도시한다.

도 8은 본 발명의 일 실시예에 따라 충(106, 108)의 SAC1 재료를  $N^+$  도핑된 폴리실리콘으로 대체한 후의 도 7의 반도체 구조물(100)의 결과적인 단면 A 및 B를 도시한다.

도 9a는 본 발명의 일 실시예에 따라 SAC2층(109)을 금속 도체층(109)("드레인 금속")으로 대체하고 활성 스택 (701)의 산화물층(107)의 리세스된 부분에 제2 폴리실리콘층(301) 및 SiGe층(302) 세트를 제공한 후의 도 8의 반도체 구조물(100)의 결과적인 단면 A 및 B를 도시한다.

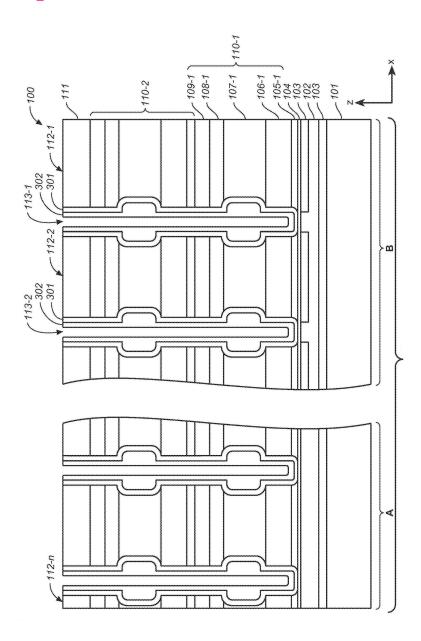

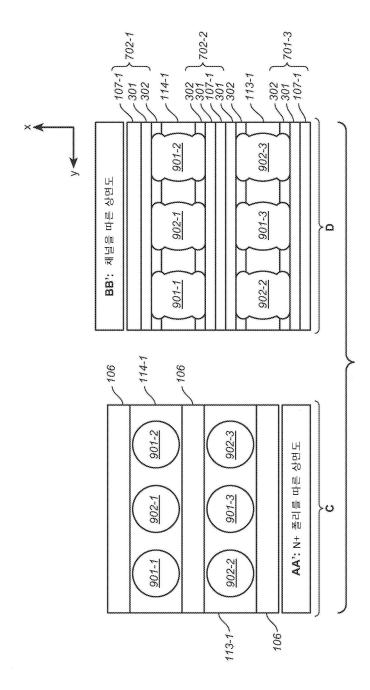

도 9b는 본 발명의 일 실시예에 따라 제1 메모리 홀(901-1 내지 901-3) 세트를 굴착 형성한 후의, N<sup>↑</sup> 도핑된 폴리실리콘충(106 또는 108)을 통과하는 A-A'선과 HTO(107)을 통과하는 B-B'선을 따라 각각 취한 도 9a의 반도체구조물(100)의 일부의 XY 평면 단면 C 및 D를 도시한다.

도 10은 본 발명의 일 실시예에 따라 메모리 홀(901-1 내지 901-3)을 SiOC로 충전한 후의, 도 9b의 반도체 구조물(100)의 단면 C 및 D를 도시한다.

도 11은 본 발명의 일 실시예에 따라 제2 메모리 홀(902-1 내지 902-3) 세트를 굴착 형성한 후의 도 10의 반도체 구조물(100)의 단면 C 및 D를 도시한다.

도 12는 본 발명의 일 실시예에 따라 제1 메모리 홀(901-1 내지 901-3) 세트로부터 SiOC 재료를 제거한 후의 도 11의 반도체 구조물(100)의 단면 C 및 D를 도시한다.

도 13은 본 발명의 일 실시예에 따른 산화물 에칭 단계를 통해 메모리 홀(901, 902)을 확장한 후의 도 12의 반도체 구조물(100)의 단면 C 및 D를 도시한다.

도 14는 본 발명의 일 실시예에 따른 SiGe 에칭 단계를 통해 메모리 홀(901, 902)의 SiGe를 제거하여 밑에 있는 채널 폴리실리콘층(302)을 노출시킨 후의 도 13의 반도체 구조물(100)의 단면 C 및 D를 도시한다.

도 15는 본 발명의 일 실시예에 따른 ONOA층(1101) 및 폴리실리콘 라이너(1102)의 연속 등각 증착 후의 도 14의 반도체 구조물(100)의 단면 C 및 D를 도시한다.

도 16은 본 발명의 일 실시예에 따른 펀치-스루 에칭 단계를 통해 메모리 홀(901) 바닥의 도체로 충전된 비아 (1201)를 노출시킨 후의 도 15의 반도체 구조물(100)의 단면 C 및 D를 도시한다.

도 17은 본 발명의 일 실시예에 따른 메모리 홀(901, 902)을 도체로 충전한 후의 도 16의 반도체 구조물(100)의 단면 C 및 D를 도시한다.

## 발명을 실시하기 위한 구체적인 내용

[0013]

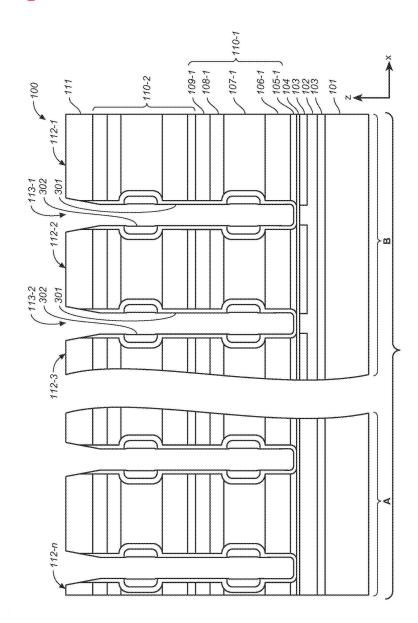

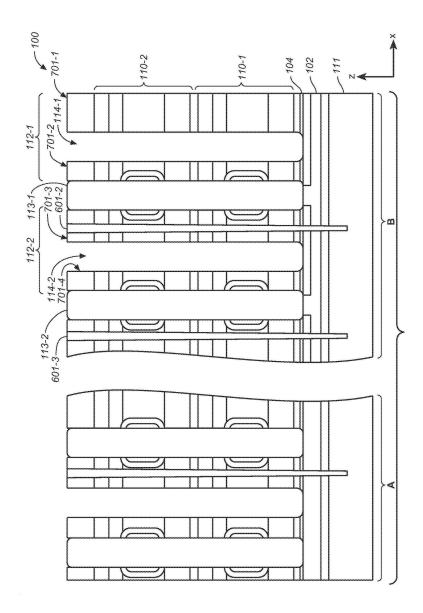

본 발명은 HNOR 어레이의 고효율 제조 공정을 제공한다. 도 1은 본 발명의 일 실시예에 따른 HNOR 어레이 제조 공정의 한 중간 단계에 있는 반도체 구조물(100)의 단면 A 및 B를 도시한다. 먼저, 텅스텐 도체와 같은 상호 연결(interconnection) 도체의 네트워크(102)("하부 워드 라인")가 기판(101)의 평평한 표면 위에 형성된다. 기판(101)은 예를 들면 반도체 웨이퍼(예컨대, 실리콘 웨이퍼)일 수 있다. (전기적 연결을 위해 도체로 충전된

비아를 포함하는) 하부 워드 라인(102)은 예컨대, 다마신(damascene) 공정을 이용하여 형성될 수 있다. 다마신 공정에서, 하부 워드 라인(102)은 절연층(103)(예컨대, 실리콘 산화물)에 정의되고 증착된 후에 화학적/기계적으로 연마된다(CMP). 하부 워드 라인(102)은 동일한 방향을 따라 진행하는 평행한 도체로서 제공된다. 설명의편의를 위해, 도면에서 수직 방향은 Z 방향이라 하고, 도면에서 단면 A 및 B는 X-Z 평면 상에서 취한 것으로 간주되며, Y 방향은 X 방향과 Z 방향 모두에 대해 직교하는 방향이다.

- [0014] 도 1에 도시된 바와 같이, 단면 A는 하부 워드 라인(102)의 인접한 도체 사이의 산화물층(103)을 통과하는 수직 단면이고 단면 B는 하부 워드 라인(102)의 도체를 통과하는 수직 단면이다. 이어서, 하부 워드 라인(102)을 보 호하고 보다 정밀하게 후속 에칭 단계를 수행하기 위해 에칭 정지층(104)(예컨대, 50 Å 내지 100 Å 두께의 알 루미늄 산화물층)이 제공된다. 이어서, 여러 개의 재료층 그룹(본 명세서에서 각각의 재료층 그룹은 "활성층" 이라 지칭됨)이 에칭 정지층(104) 위에 연속적으로 형성된다. 아래에서 설명하는 바와 같이, 각각의 활성층의 재료층은 활성 스트립 내의 기능성 층이거나 기능성 층의 전구체(또는 "희생"층)일 수 있다. 도 1에는 2개의 활성층(즉, 활성층(110-1)과 활성층(110-2))만이 도시되어 있으나, 이는 단지 예시에 불과한 것으로, 임의의 적 절한 수의 활성층이 제공될 수 있다(예컨대, 8개, 16개, 32개 또는 그 이상의 활성층이 제공될 수 있다). 활성 층(110-1)은 (i) 증착된 산화물층(105-1)(예컨대, 500 Å 내지 1500 Å 두께의 산탄화물("SiOC")층)과; (ii) 제1 희생충(106-1)(제1 "SAC1"층; 예컨대, 350 Å 내지 1100 Å 두께의 실리콘 질화물층)과; (iii) 고온 산화물(HTO)층(107-1)(예컨대, 500 Å 내지 1500 Å 두께)과; (iv) 제2 SAC1층(108-1)(예컨대, 150 Å 내지 500 Å 두께)과; (v) 제2 희생층(109-1)("SAC2"층; 예컨대, 250 Å 내지 700 Å 두께 의 실리콘 붕소층(SiB), 실리콘 탄소층(SiC), 또는 실리콘 게르마늄층(SiGe))을 포함한다. 활성층(예컨대, 활성층(110-2))도 각각 실질적으로 동일한 재료층을 갖는다. 본 명세서에서 접미사가 붙은 (suffixed) 참조 부호는 특정 실례("특정 참조 부호")에 대한 참조 부호를 가리킨다. 예컨대, 접미사가 붙은 참조 부호 "105-1"은 참조 부호 "105"로 일반적으로 지칭되는 유사 형상부 세트에 속한 특정 실례에 대한 참조 부호를 가리킨다. 일반 참조 부호(즉, 비특정 참조 부호)와 관련하여 작성된 진술은 모든 특정 참조 부호에도 적용 가능하다.

- [0015] 이어서, 하드 마스크(111)가 활성층 상에 제공된다. 이어서, 에칭 정지층(104)에 이르기까지 활성층(110)의 이 방성 에칭이 수행되어 제1 활성 스택(112) 세트(예컨대, 활성 스택(112-1), 활성 스택(112-2)......활성 스택(112-n))와 트렌치(113)(예컨대, 트렌치(113-1), 트렌치(113-2) ... 트렌치(113-n))를 형성한다. 활성 스택(112)은 (X 방향) 폭이 예를 들어 190 nm이고 트렌치(113)는 (X 방향) 폭이 예를 들어 70 nm일 수 있다.

- [0016] 아래에서 설명하는 바와 같이, 본 실시예에서는 제1 및 제2 SAC1 층(106-1, 108-1)이 저장 트랜지스터용 소스 및 드레인 영역을 각각 제공하기 위해 후속 단계에서 *인시츄* 도핑된 N<sup>†</sup> 폴리실리콘으로 대체되어야 한다. 실리 콘 질화물은 HTO층(107)에 대해 이용 가능한 에칭 선택성을 갖기 때문에 SAC1층의 재료로 사용될 수 있다. SAC2층(109-1)은 드레인 영역에 낮은 저항을 제공하기 위해 차후에 금속층으로 대체되어야 한다. 실리콘 붕소, 실리콘 탄소 및 실리콘 게르마늄 중 어느 것이든 N<sup>†</sup> 도핑된 폴리실리콘에 대하여 에칭 선택성(예컨대, 고온 인산 에칭시)을 갖기 때문에 SAC2층(109-1)의 재료로 선택될 수 있다.

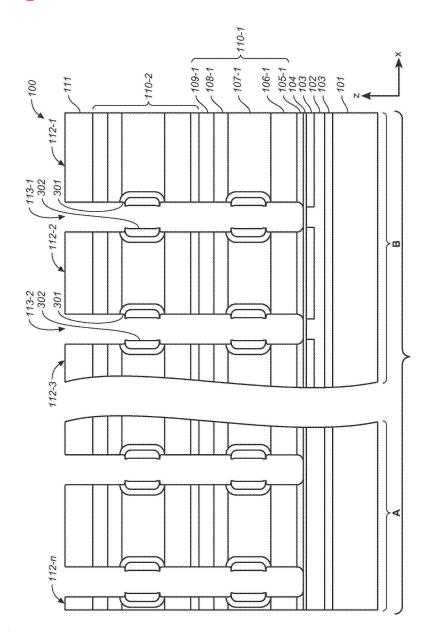

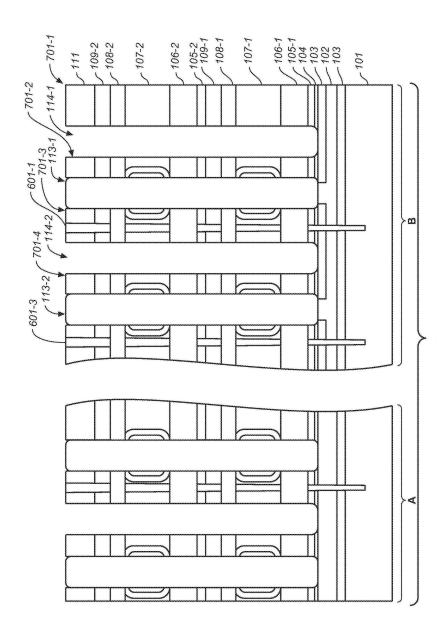

- [0017] 그 후, 등방성 산화물 에칭 단계를 통해, 각각의 활성층마다 HTO층(107)에 (예컨대, 75 Å 내지 250 Å 만큼) 리세스를 형성한다. 도 2에는 그 결과로 얻어지는 반도체 구조물(100)의 단면이 도시되어 있다. 이어서, 비정 질 실리콘층(301)(예컨대, 40 Å 내지 120 Å 두께)이 HTO층(107)의 리세스된 표면을 포함하는 활성 스택(112)의 측벽 위에 등각 중착된다. 비정질 실리콘층(301)의 등각 중착에 이어, 비정질 실리콘 게르마늄(SiGe)층 (302)(예컨대, 100 Å 내지 300 Å 두께)이 비정질 실리콘층(301) 위에 중착된다. 이어서, 비정질 실리콘층 (301)과 비정질 SiGe층(302) 모두를 결정화층으로 결정화하기 위해 어닐링 단계가 수행될 수 있다. 비정질 실리콘층(301)은 폴리실리콘층이 된다.

- [0018] SiGe층(302)은 많은 이점을 제공한다. SiGe는 일반적으로 폴리실리콘보다 더 큰 결정립계를 가지므로 SiGe의 존재 하에 비정질 실리콘을 결정화하여 얻은 재료 또한 통상의 폴리실리콘보다 더 큰 결정립계를 갖고 따라서 보다 높은 운반자 이동도를 갖게 된다. 운반자 이동도가 높을수록 전기 전도도가 높아질 뿐만 아니라 보다 높은 전류 밀도를 유지할 수 있게 된다. SiGe층(302)은 또한 다양한 후속 에칭 단계(예컨대, 이방성 건식 에칭 단계)로부터 폴리실리콘층(301)을 보호하고 폴리실리콘층(301)으로부터 폴리실리콘 스트링거(stringer)가 형성되지 못하도록 한다. 도 3은 본 발명의 일 실시예에 따른 비정질 실리콘층(301) 및 SiGe층(302)의 증착 후의도 2의 반도체 구조물(100)의 결과적인 단면 A 및 B를 도시한다.

- [0019] 이어서, 활성 스택(112)의 측벽으로부터 SiGe층(302)을 제거하기 위해 이방성 에칭 단계와 등방성 에칭 단계가

잇달아 수행된다. 이들 에칭 단계 중에, HTO층(107)의 리세스된 부분 내에서는 SiGe층(302)이 밑에 있는 폴리실리콘층(301)을 보호한다. 폴리실리콘층(301)의 노출된 부분에 대한 손상을 방지하기 위해 등방성 에칭 단계는 폴리실리콘에 대해 높은 선택도(예컨대, 100:1)로 조정될 수 있다. 도 4는 본 발명의 일 실시예에 따른 SiGe층(302)의 이방성 에칭 및 등방성 에칭 단계 후의 도 3의 반도체 구조물(100)의 결과적인 단면 A 및 B를 도시한다.

- [0020] 그 후, 등방성 에칭 단계(예컨대, 수소, 염소, 암모니아 또는 이들 종의 임의의 조합을 원자 또는 분자 형태로 사용하는 라디칼 에칭 단계)를 통해, 활성 스택(112)의 측벽으로부터 폴리실리콘층(301)을 제거한다. HTO층 (107)의 리세스된 부분에 남아 있는 SiGe층(302)이 제거되는 것을 방지하기 위해, 이 등방성 에칭 단계는 SiGe에 대해 높은 선택도(예컨대, 100:1)로 조정될 수 있다. 도 5는 본 발명의 일 실시예에 따른 폴리실리콘층 (301)의 등방성 에칭 단계 후의 도 4의 반도체 구조물(100)의 결과적인 단면 A 및 B를 도시한다. 그 위에 중첩된 SiGe층(302)에 의해 보호되는 폴리실리콘층(301)의 이 부분("채널 폴리실리콘층(301)")은 차후에 HNOR 어레이의 저장 트랜지스터의 채널 영역 역할을 하도록 되어 있다.

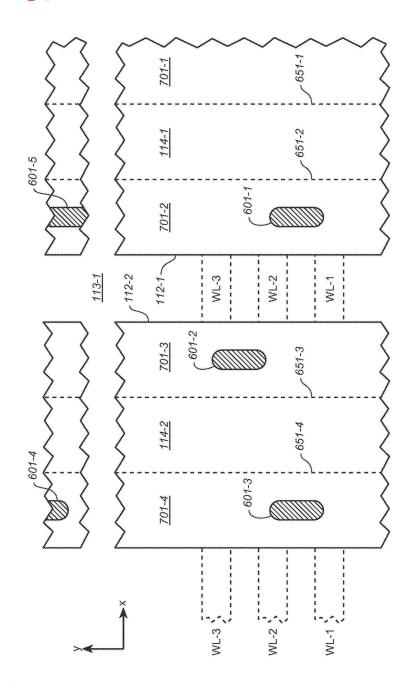

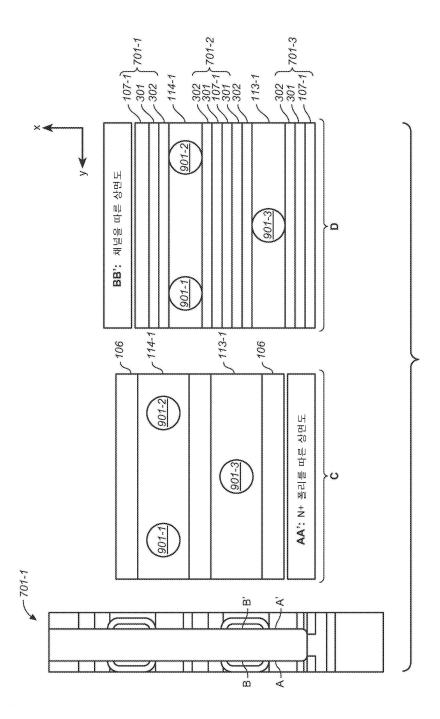

- [0021] 활성 스택의 활성층의 수가 많은 일부 실시예에서는, 활성 스택(112)을 생성하는 에칭 단계를 소정의 종횡비 미만으로 설계하는 것이 바람직할 수 있다. 일 방법에서, HNOR 어레이의 활성 스택은 다수의 에칭 단계에 의해 생성된다. 활성 스택에 기계적 지지를 제공하기 위해 산화물 기둥도 제공된다. 도 6a는 본 발명의 일 실시예에 따른, 예시적인 활성 스택(112-1, 112-2) 상의 예시적인 산화물 기둥(601-1 내지 601-5)의 위치를 보여주는 상면도(즉, X-Y 평면도)이다. 도 6a에서, 예시적인 활성 스택(112-1, 112-2)은 예시적인 트렌치(113-1)에 의해 X 방향을 따라 서로 이격된 상태로 각각 Y 방향을 따라 길게 연장된다. 활성 스택(112-1, 112-2) 아래에는 하부 워드 라인(102)(예컨대, 예시적인 하부 워드 라인 WL-1 내지 WL-3)이 X 방향을 따라 진행한다.

- [0022] 도 6a에는 예시적인 하부 워드 라인(WL-1, WL-2, WL-3)이 점선으로 도시되어 있다. 활성 스택(112-1, 112-2)은 각각 X 방향 폭이 예를 들어 70 nm일 수 있다. 하부 워드 라인(WL-1 내지 WL-3)은 40 nm 만큼 서로 이격될 수 있고, 각각 Y 방향 폭이 예를 들어 40 nm일 수 있다. 예시적인 산화물 기둥(601-1, 601-2, 601-3)은 인접한 활성 스택(112-1, 112-2)에 서로 엇갈린 대형으로 제공된다. 각각의 산화물 기둥은 타원형일 수 있고, X 방향 치수가 40 nm, Y 방향 치수가 80 nm일 수 있다. 도 6a에 도시된 바와 같이, 산화물 기둥(601-1, 601-3)은 각각 서로 인접한 하부 워드 라인(WL-1, WL-2) 각각의 폭의 절반에 중첩되고, 산화물 기둥(601-2)은 서로인접한 하부 워드 라인(WL-2, WL-3) 각각의 폭의 절반에 중첩된다. 예리한 모서리를 갖지 않음으로써 산화물 기둥은 비교적 덜 까다로운 에칭 단계를 이용하여 형성될 수 있다. 활성 스택 형성을 위한 에칭 단계 중에 요구되는 기계적 지지는 (모두 활성 스택(113-2) 상에 제공되는) 산화물 기둥(601-3, 601-4)을 Y 방향을 따라 균일한 미크론 간격으로 배치함으로써 충족될 수 있다.

- [0023] 산화물 기둥(601)은 (도 7과 관련하여 아래에 설명되는) 추가 에칭 단계에서 추가적인 트렌치(114)가 생성될 때활성 스택(112)이 각각 보다 작은 활성 스택(701)으로 더 분할되도록 각각의 활성 스택에 배치된다. 예컨대, 도 6a에 도시된 바와 같이, 활성 트렌치(114-1, 114-2)가 점선(651-1)과 점선(651-2) 사이와 점선(651-3)과 점선(651-4) 사이에 각각 형성되어 활성 스택(112-1, 112-2)이 활성 스택(701-1 내지 701-4)으로 더 분할된다.

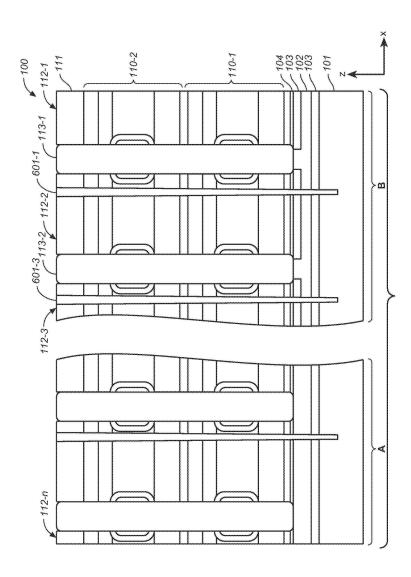

- [0024] 도 5의 등방성 폴리실리콘 에칭 단계에 이어, 산화물 기둥(601)용 샤프트가 에칭된다. 필요한 기계적 지지를 제공하기 위해, 기둥 샤프트는 활성층, 에칭 정지층(104), 격리층(103) 및 하부 워드 라인층(102)을 관통하여 기판(101) 내로 연장된다. 이어서, 트렌치(113-1, 113-2)와 기둥 샤프트가 실리콘 산화물로 충전된다. 도 6b는 본 발명의 일 실시예에 따른 실리콘 산화물을 이용한 산화물 기둥(601)의 기둥 샤프트와 트렌치(113)의 충전 및 CMP에 의한 평탄화 후의 도 5의 반도체 구조물(100)의 결과적인 단면 A 및 B를 도시한다.

- [0025] 산화물 기둥(601) 및 산화물로 충전된 트렌치(113)에 의한 기계적 지지가 제공된 상태에서, 에칭 정지층(104)에 이르기까지 활성층을 제거하는 에칭 단계를 통해 추가적인 트렌치(114)가 활성 스택(112)에 생성된다. 도 7은 본 발명의 일 실시예에 따라 에칭 정지층(104)에 이르기까지 활성층을 에칭함으로써 활성 스택(112-2, 112-3)에 트렌치(114-1, 114-2)를 생성한 후의 도 6의 반도체 구조물(100)의 결과적인 단면 A 및 B를 도시한다. 도 7에 도시된 바와 같이, 트렌치(114-1, 114-2)는 활성 스택(112-1, 112-2)을 에칭함으로써 생성된다. 이 에칭 단계는 활성 스택(112)을 활성 스택(701)으로 분할한다. 예컨대, 도 7에 도시된 바와 같이, 이 에칭 단계를 통해 활성 스택(112-1)은 활성 스택(701-1, 701-2)으로 분할되고 활성 스택(112-2)은 활성 스택(701-3, 701-4)으로 분할된다. 활성 스택(701)은 X 방향 폭이 70 nm이고 트렌치(114)는 X 방향 폭이 60 nm일 수 있다.

- [0026] 트렌치(114)는 활성 스택(701)의 측벽을 노출시킨다. 이어서, 각각의 활성층(110)의 SAC1층(106, 108)이 SAC1 재료의 등방성 에칭 단계(예컨대, 고온 인산 에칭)와 뒤이은 *인시츄* N<sup>†</sup> 도핑된 폴리실리콘(예컨대, 0.5×10<sup>21</sup> cm

$^{-3}$  내지  $1.5 \times 10^{21}$  cm  $^{-3}$ 의 도편트 농도)의 증착을 통해 N  $^{+}$  폴리실리콘층(106, 108)으로 대체된다. 이어서, 이방성 에칭을 통해 트렌치(114)로부터 과잉 N  $^{+}$  도핑된 폴리실리콘을 제거하여 N  $^{+}$  도핑된 폴리실리콘층(106, 108)의 단락을 방지한다. 그 후, 습식 세정 단계(예컨대, SC-1 세정, 수성 불화 수소산 및 탈이온수)가 수행된다. 도 8은 본 발명의 일 실시예에 따라 N  $^{+}$  도핑된 폴리실리콘으로 SAC1층(106, 108)의 SAC1 재료를 대체한 후의 도 7의 반도체 구조물(100)의 결과적인 단면 A 및 B를 도시한다.

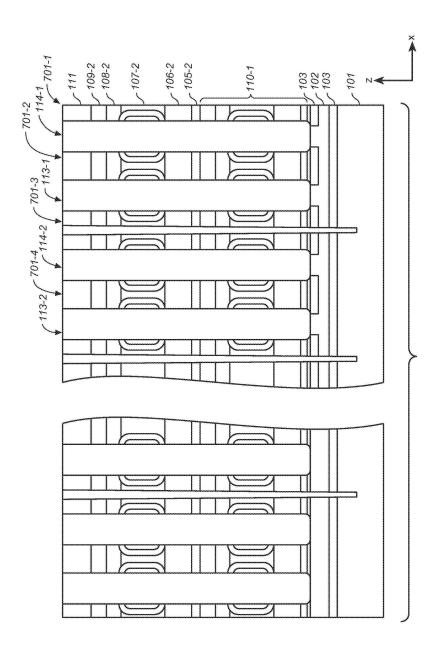

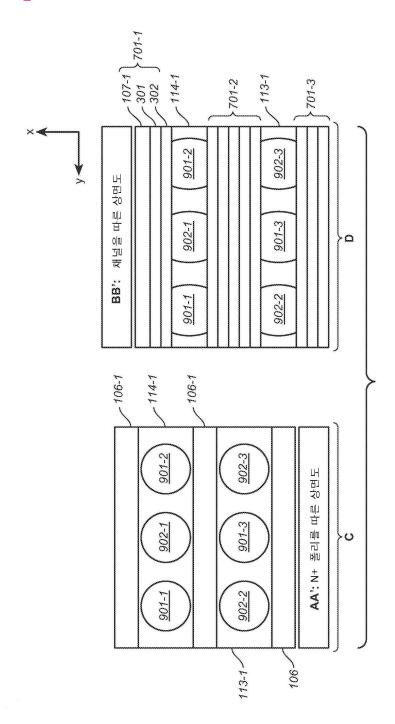

- [0027] 이어서, SAC2층(109)이 금속 도체층으로 대체된다. SAC2층(109)은 SiB, SiC, SiGe 또는 이들의 임의의 조합일수 있기 때문에, SAC2층(109)은 산화물, 질화물 및 실리콘에 대해 선택적인, 적절한 고선택성 라디칼 에칭을 이용하여 제거될 수 있다. 이러한 라디칼 에칭은 예를 들어 기체 상태의 Cl<sub>2</sub>, F<sub>2</sub>, 또는 이들 모두를 사용하여 달성될 수 있다. 이어서, 적절한 금속(예컨대, 텅스텐(W))을 이용한 금속 충전 단계가 라이너 재료(예컨대, 티타늄 질화물(TiN))의 증착에 뒤이어 수행될 수 있다. 이어서, 이방성 에칭 단계를 통해 트렌치(114) 내의 과잉충전 금속 및 라이너를 제거한다. 그 후, 이상에서 설명한 바와 같은 도 2 내지 도 5의 단계(즉, HTO층에 리세스 형성, 비정질 실리콘 및 SiGe층의 증착, 어닐링, SiGe층의 이방성 및 등방성 에칭, 비정질 실리콘의 어닐링을 통해 얻어지는 폴리실리콘층의 이방성 및 등방성 에칭)가 활성 스택(701)의 노출된 측벽에 추가 채널 영역을 마련하기 위해 활성 스택(701)의 측벽을 따라 수행된다. 그 후, 트렌치(114)가 실리콘 산화물로 충전되고 CMP 단계에 의해 평탄화된다.

- [0028] 도 9a는 본 발명의 일 실시예에 따라 금속 도체층(109)("드레인 금속")으로 SAC2층(109)을 대체하고 활성 스택 (701)의 산화물층(107)의 리세스된 부분에 제2 채널 폴리실리콘층(301) 및 SiGe층(302) 세트를 제공한 후의 도 8의 반도체 구조물(100)의 결과적인 단면 A 및 B를 도시한다.

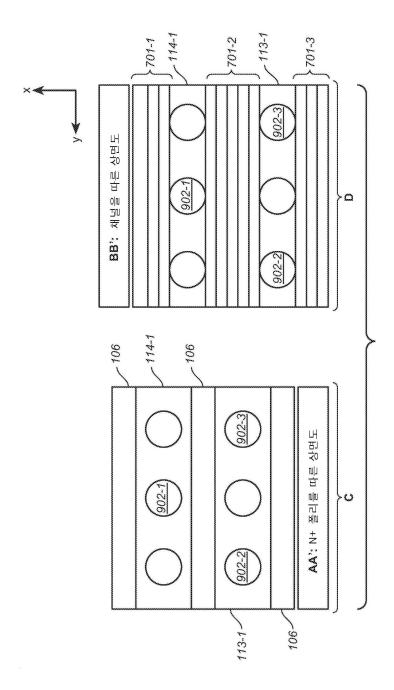

- [0029] 이어서, 산화물 에칭 단계를 통해, 제1 로컬 워드 라인 샤프트("메모리 홀") 세트(901)가 산화물로 충전된 트렌 치(112, 114)에 굴착 형성된다(excavated). 이 에칭 단계에서는 에칭 정지충(104)에 이르기까지 산화물로 충전된 트렌치(112, 114) 내의 실리콘 산화물을 굴착한다. 도 9b는 본 발명의 일 실시예에 따라 제1 메모리 홀 (901-1 내지 901-3) 세트가 절단된 후의, № 도핑된 폴리실리콘충(106 또는 108)을 통과하는 A-A'선과 HTO충(107)를 통과하는 B-B'선을 따라 각각 취한 도 9a의 반도체 구조물(100)의 X-Y 평면 단면 C 및 D를 도시한다. 도 9a에 도시된 바와 같이, 제1 메모리 홀 세트(901)는 서로 엇갈린 대형으로 배열된다.

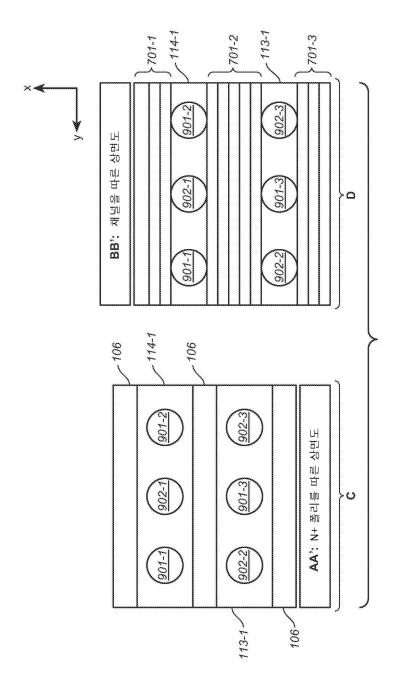

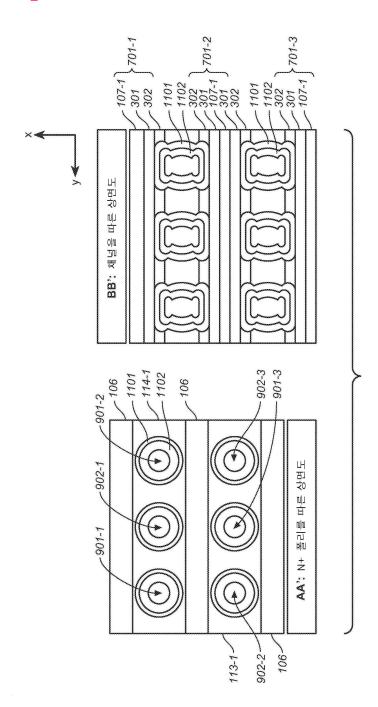

- [0030] 이어서, 제1 메모리 홀 세트(901)가 희생재인 SiOC로 충전된다. 도 10은 본 발명의 일 실시예에 따른 SiOC를 이용한 메모리 홀(901-1 내지 901-3)의 충전 후의 도 9b의 반도체 구조물(100)의 단면 C 및 D를 도시한다. 그후, 산화물 에칭 단계를 통해 제2 메모리 홀 세트(902)가 산화물로 충전된 트렌치(112, 114)에 굴착 형성되는데, 이들 메모리 홀(902)도 서로 엇갈린 대형으로 배열된다. 이 에칭 단계에서는 에칭 정지층(104)에 이르기까지 산화물로 충전된 트렌치(112, 114)의 실리콘 산화물을 굴착한다. 도 11은 본 발명의 일 실시예에 따라 제2 메모리 홀(902-1 내지 902-3) 세트를 굴착 형성한 후의 도 10의 반도체 구조물(100)의 단면 C 및 D를 도시한다.

- [0031] 이어서, 에칭 단계를 통해 메모리 홀(901) 내의 SiOC 재료가 제거된다. 도 12는 본 발명의 일 실시예에 따라 제1 메모리 홀(901-1 내지 901-3) 세트로부터 SiOC 재료를 제거한 후의 도 11의 반도체 구조물(100)의 단면 C 및 D를 도시한다. 이어서, 메모리 홀(901, 902)을 확장하기 위해 산화물 리세스 단계가 수행된다. 도 13은 본 발명의 일 실시예에 따른 산화물 에칭 단계를 통해 메모리 홀(901 및 902)을 확장한 후의 도 12의 반도체 구조물(100)의 단면 C 및 D를 도시한다. 산화물로 충전된 트렌치(112, 114) 모두에 있어, 단면 D(즉, 산화물층 (107), 채널 폴리실리콘층(301) 및 SiGe층(302)를 통과하는 단면)에서의 X 방향 폭은 SiGe층(302) 때문에 단면 C(즉, N 도핑된 폴리실리콘층(106)을 통과하는 단면)에서의 X 방향 폭보다 작다는 것에 유의해야 한다. 결과 적으로, 단면 D에서의 X 방향으로 메모리 홀(901, 902)을 확장하는 산화물 리세스 단계는 단면 C에서의 N 도핑된 폴리실리콘층(106)의 측벽에 도달하기에 앞서 SiGe층(302)에 먼저 도달한다. 따라서, 단면 D에서 메모리 홀 (901, 902)은 타원형이다. 산화물 리세스 단계는 시간 제어되는 에칭 단계일 수 있다. 메모리 홀(901, 902)의 최종 임계 치수(critical dimension)는 에칭 시간에 달려 있다.

- [0032] 이어서, SiGe 에칭 단계를 통해 메모리 홀(901, 902)의 SiGe층(302)을 뚫어 밑에 있는 채널 폴리실리콘층(301)을 노출시킨다. 도 14는 본 발명의 일 실시예에 따른 SiGe 에칭 단계를 통해 메모리 홀(901, 902)의 SiGe 재료를 제거하여 밑에 있는 채널 폴리실리콘층(302)을 노출시킨 후의 도 13의 반도체 구조물(100)의 단면 C 및 D를 도시한다.

- [0033] 그 후, 등각을 이루는 실리콘 산화물층(1101a), 실리콘 질화물층(1101b), 실리콘 산화물층(1101c) 및 알루미늄 산화물층(1101d)을 연속적으로 증착하여 전하 포획층("ONOA")(1101)을 형성한다. 실리콘 산화물("터널 산화물")층(1101a)은 두께가 예를 들어 1.0 nm 내지 1.5 nm일 수 있다. (채널 폴리실리콘(301)로부터 터널 산화물 (1101a)을 터널링하는 전하 운반자를 포획하는) 실리콘 질화물층(1101b)은 두께가 예를 들어 3.0 nm 내지 5.0 nm일 수 있다. 실리콘 산화물층(1101c)은 두께가 1.5 nm 내지 4.5 nm이고 알루미늄 산화물층(1101d)은 두께가 1.0 nm 내지 3.0 nm일 수 있으며, 실리콘 산화물층(1101c)과 산화알루미늄층층(1101d)은 "차단"층을 형성할 수 있다. 추가 희생 폴리실리콘층("폴리실리콘 라이너")(1102)이 다음 에칭 단계 중에 ONOA층(1101)을 보호하기 위해 제공될 수 있다. 도 15는 본 발명의 일 실시예에 따른 ONOA층(1101) 및 폴리실리콘 라이너(1102)의 연속적인 등각 증착 후의 도 14의 반도체 구조물(100)의 단면 C 및 D를 도시한다.

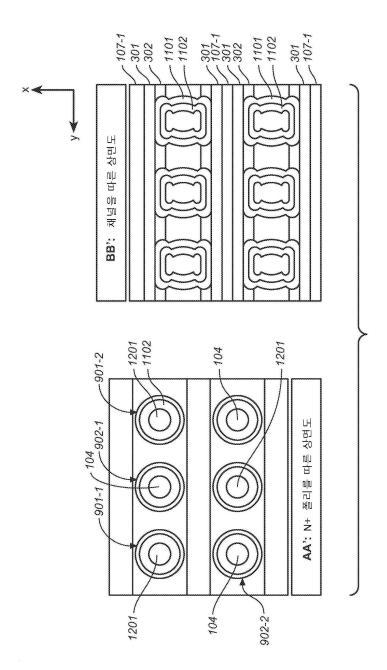

- [0034] 이어서, 이방성 에칭 단계를 통해 메모리 홀(901, 902) 바닥의 ONOA 층(1101) 부분과 폴리실리콘 라이너(1102) 부분을 제거하여 에칭 정지층(104)을 노출시킨다. 본 실시예에서는, 밑에 있는 하부 워드 라인(102)들 중 선택된 하부 워드 라인에 대한 전기적 연결을 가능하게 하는 도체로 충전된 비아(1201) 상부에 메모리 홀(901)이 제공된다. 이어서, 편치-스루 에칭 단계를 통해 메모리 홀(901) 바닥의 에칭 정지층(104)을 제거하여, 차후 메모리 홀(901)에 배치되어 로컬 워드 라인 역할을 수행하게 될 도체 플러그(예컨대, 텅스텐)가 하부 워드 라인 (102)으로부터 바이어스 전압을 인가받을 수 있도록 한다. 본 실시예에서, 메모리 홀(902)의 도체 플러그(예컨대, 텅스텐)는 메모리 구조물(100) 상부에 형성될 워드 라인("상부 워드 라인")으로부터 바이어스 전압을 인가받는 로컬 워드 라인의 역할을 하기 위해 제공된다. 도 16은 본 발명의 일 실시예에 따른 편치-스루 에칭 단계를 통해 메모리 홀(901) 바닥의 도체로 충전된 비아(1201)를 노출시킨 후의 도 15의 반도체 구조물(100)의 단면 C 및 D를 도시한다.

- [0035] 이어서, 폴리실리콘 라이너(1102)가 제거된다. (금속 라이너(예컨대, 티타늄 질화물)층과 같은) 등각 점착층이 메모리 홀(901, 902) 내에 증착되고, 이어서 금속 충전 단계(예컨대, 텅스텐 충전 단계)가 수행된다. 이어서, CMP에 의한 평탄화가 수행될 수 있다. 도 17은 본 발명의 일 실시예에 따라 메모리 홀(901, 902)을 도체로 충전하고 평탄화한 후의 도 16의 반도체 구조물(100)의 단면 C 및 D를 도시한다.

- [0036] 이어서, 상부 워드 라인과 여타의 배선층이 통상적인 방식으로 제공될 수 있다.

- [0037] 상기 상세한 설명은 본 발명의 특정 실시예를 예시하기 위해 제공된 것으로 본 발명을 제한하려는 의도는 없다. 본 발명의 범위를 벗어나지 않고 많은 변형 및 수정이 가능하다. 본 발명은 아래에 첨부된 특허청구범위에 기 재되어 있다.

도면4

# 도면6a

## *도면6b*

## 도면9a

## *도면9b*

도면11

도면17