# (19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(51) 국제특허분류(Int. Cl.)

**H05K 3/46** (2006.01) **H05K 1/18** (2006.01)

(21) 출원번호 **10-2010-0092851**

(22) 출원일자2010년09월24일

심사청구일자 2010년09월24일

(11) 공개번호 10-2012-0031362

(43) 공개일자

(71) 출원인

#### 주식회사 심텍

충청북도 청주시 흥덕구 산단로 73 (송정동)

2012년04월03일

(72) 발명자

#### 이종태

충청북도 청주시 흥덕구 비하로63번길 24, 삼일 아파트 2동 508호 (비하동)

#### 박정권

충청북도 청주시 흥덕구 풍년로 56, 가경뜨란채아 파트 804동 103호 (가경동)

(뒷면에 계속)

(74) 대리인

특허법인 아주양헌

전체 청구항 수 : 총 14 항

#### (54) 발명의 명칭 임베디드 인쇄회로기판 및 제조방법

#### (57) 요 약

인쇄회로기판 내에 매몰된 커패시터와 같은 제1회로 소자, 제1회로 소자에 중첩되게 매몰 적충된 제2회로 소자, 및 제1 및 제2회로 소자를 전기적으로 병렬 연결하는 수직한 범프(bump)들을 포함하는 임베디드(embedded) 인쇄회로기판 및 제조방법을 제시한다.

#### 대 표 도 - 도8

### (72) 발명자

# 차상석

경기도 의왕시 갈미로 8, 대원칸타빌2단지 204동 1101호 (내손동)

### 정창보

서울특별시 노원구 노원로22길 71, 건영3차아파트 307동 1502호 (중계동)

# 오춘환

충청북도 청주시 흥덕구 가경동 1695번지 푸르지오 아파트 505동 1901호

## 특허청구의 범위

#### 청구항 1

인쇄회로기판;

상기 기판 내에 매몰된 제1회로 소자;

상기 제1회로 소자에 중첩되게 매몰 적층된 제2회로 소자; 및

상기 제1 및 제2회로 소자를 전기적으로 연결하는 수직한 범프(bump)들을 포함하는 것을 특징으로 하는 임베디드 인쇄회로기판.

### 청구항 2

제1항에 있어서,

상기 제1 및 제2회로 소자들은 능동 소자, 커패시터 또는 레지스터인 것을 특징으로 하는 임베디드 인쇄회로기 판.

#### 청구항 3

인쇄회로기판;

상기 기판 내에 매몰된 제1커패시터;

상기 제1커패시터에 중첩되게 매몰 적층된 제2커패시터; 및

상기 제1 및 제2커패시터를 전기적으로 연결하는 수직한 범프(bump)들을 포함하는 것을 특징으로 하는 임베디드 인쇄회로기판.

#### 청구항 4

제3항에 있어서,

상기 범프들은 상기 제1 및 제2커패시터를 병렬 연결하게 대향되는 상기 제1 및 제2커패시터의 전극들을 연결하는 것을 특징으로 하는 임베디드 인쇄회로기판.

### 청구항 5

제3항에 있어서,

상기 기판 표면 상에 형성된 외층 회로 배선층; 및

상기 외층 회로 배선층과 상기 제1커패시터를 연결하는 연결 비아(via)들을 더 포함하는 것을 특징으로 하는 임 베디드 인쇄회로기판.

#### 청구항 6

제3항에 있어서,

상기 기판 내에 매몰된 제1레지스터;

상기 제1레지스터에 부분적으로 중첩되게 매몰 적층된 제2레지스터; 및

상기 제1 및 제2레지스터가 부분적으로 중첩되는 부분에 위치하여 상호 직렬 연결시키는 제2의 범프를 더 포함하는 것을 특징으로 하는 임베디드 인쇄회로기판.

#### 청구항 7

제1회로 소자가 표면에 매몰된 제1기판을 형성하는 단계;

상기 제1회로 소자에 대향되는 제2회로 소자가 표면에 매몰된 제2기판을 형성하는 단계;

상기 제2회로 소자 상에 범프를 형성하는 단계;

상기 범프에 상기 제1회로 소자가 대향되게 상기 제1기판을 사이에 절연충을 개재하여 상기 제2기판 상에 정렬하는 단계; 및

상기 제2기판, 절연층 및 제1기판을 압착하여 상호 접착시키며 상기 범프가 상기 절연층을 관통하여 상기 제1회로 소자에 연결되게 하는 단계를 포함하는 것을 특징으로 하는 임베디드 인쇄회로기판 제조방법.

#### 청구항 8

제7항에 있어서,

상기 제1 및 제2회로 소자들은 능동 소자, 커패시터 또는 레지스터로 도입되는 것을 특징으로 하는 임베디드 인 쇄회로기판 제조방법.

#### 청구항 9

제1커패시터가 표면에 매몰된 제1기판을 형성하는 단계;

상기 제1커패시터에 대향되는 제2커패시터가 표면에 매몰된 제2기판을 형성하는 단계;

상기 제2커패시터의 양 전극들 상에 범프들을 형성하는 단계;

상기 범프들에 상기 제1커패시터의 양 전극들이 대향되게 상기 제1기판을 사이에 중간 절연층을 개재하여 상기 제2기판 상에 정렬하는 단계; 및

상기 제2기판, 절연층 및 제1기판을 압착하여 상호 접착시키며 상기 범프들이 상기 중간 절연층을 관통하여 상기 제1커패시터의 양 전극들에 연결되게 하여 상기 제1 및 제2커패시터들을 상호 병렬 연결하는 단계를 포함하는 것을 특징으로 하는 임베디드 인쇄회로기판 제조방법.

#### 청구항 10

제9항에 있어서,

상기 제1기판에 상기 제1커패시터와 이격된 제1레지스터를 매몰하는 단계; 및

상기 제1레지스터에 부분적으로 중첩되게 대향되는 상기 제2기판에 제2레지스터를 매몰하는 단계를 더 포함하고,

상기 범프의 형성 시 상기 제1 및 제2레지스터들을 직렬 연결할 제2의 범프를 함께 형성하는 것을 특징으로 하는 임베디드 인쇄회로기판 제조방법.

#### 청구항 11

제9항에 있어서,

상기 범프는 상기 중간 절연층에 대향되는 끝단이 뾰족한 형상으로 형성되는 것을 특징으로 하는 임베디드 인쇄 회로기판 제조방법.

#### 청구항 12

제9항에 있어서,

상기 제1기판을 형성하는 단계는

양면에 각각 제1 및 제2도전층이 형성된 제1절연층을 도입하는 단계;

상기 제1절연층을 관통하여 상기 제1커패시터가 수용될 캐비티(cavity)를 형성하는 단계;

상기 캐비티 내에 상기 제1커패시터를 수용하는 단계;

일면에 제3도전층이 형성된 제2절연층을 상기 제2절연층이 상기 제1커패시터에 대항되게 도입하는 단계; 및

상기 제2절연층과 상기 제1절연층을 상호 접착하여 상기 제2절연층에 상기 제1커패시터가 접착되게 하는 단계를 포함하는 것을 특징으로 하는 임베디드 인쇄회로기판 제조방법.

#### 청구항 13

제12항에 있어서.

상기 캐비티 내에 상기 제1커패시터를 수용하는 단계는

상기 제1도전층 상에 일면이 상기 캐비티 내에 노출되는 접착 필름을 부착하는 단계; 및

상기 제1커패시터를 상기 캐비티 내에 노출된 상기 접착 필름 부분에 접착시키는 단계를 포함하는 것을 특징으로 하는 임베디드 인쇄회로기판 제조방법.

#### 청구항 14

제13항에 있어서,

상기 제1, 제2 및 제3도전층 각각을 회로 배선층들으로 각각 패터닝하는 단계들을 더 포함하는 것을 특징으로 하는 임베디드 인쇄회로기판 제조방법.

### 명세서

#### 기 술 분 야

[0001] 본 발명은 인쇄희로기판(PCB) 기술에 관한 것으로, 특히, 실장 밀집도를 향상시키는 임베디드(embedded) 인쇄희로기판 및 제조방법에 관한 것이다.

### 배경기술

- [0002] 전자 기기의 소형화에 따라, 전자 부품이 보다 고기능화되고 보다 더 소형화되고 있다. 디지털 네트워크의 고도화에 의해, 휴대폰이나 휴대 컴퓨터 등과 같은 휴대 정보 단말 기기가 고성능 및 고기능화되고 있으며, 다양한 기능이 하나의 기기에 융합되어 복합화되고 있다. 정보량의 급속한 증대에 따라 휴대 단말 기기의 정보 처리 속도 또한 급속히 향상되는 것이 요구되고 있다. 또한, 디지털 기기의 고성능을 위해 로직 소자(LSI)와 유기적인접속을 위한 기판 실장 기술의 중요성이 높아지고 있다.

- [0003] 전자 기기가 소형화되고 고기능화됨에 따라, 인쇄회로기판에 실장되어야 하는 부품 소자 수가 크게 증가되고 있고, 이에 반해 기판의 면적은 크게 감소시키는 것이 요구되고 있다. 휴대폰에 소요되는 기판의 경우 제한된 기판 면적에 보다 많은 부품 소자의 실장이 요구되고 있다. 특히, 기판 표면적이 제한되고 있어, 기판 표면에 다

기능 및 고기능 동작을 위한 부품 소자들의 실장을 위해서, 기판 표면에 실장되는 수동 소자의 수를 줄이는 방안이 요구되고 있다. 기판 표면적의 제한에 의해 표면에 실장될 부품 수의 감소가 요구되는 데 비해, 실질적으로 기판에 실장되어야 할 수동 소자의 부품 수는 휴대폰과 같은 휴대 단말 기기의 고성능 동작을 위해 보다 증대되고 있다. 따라서, 제한된 기판 크기 및 표면적에도 불구하고 보다 많은 부품들을 실장할 수 있는 방법의 개발이 요구되고 있다.

#### 발명의 내용

#### 해결하려는 과제

[0004] 본 발명은 부품 소자들의 실장 밀집도를 향상시킬 수 있는 임베디드 인쇄회로기판 및 제조 방법을 제시하고자 한다.

#### 과제의 해결 수단

- [0005] 본 발명의 일 관점은, 인쇄회로기판; 상기 기판 내에 매몰된 제1회로 소자; 상기 제1회로 소자에 중첩되게 매몰 적충된 제2회로 소자; 및 상기 제1 및 제2회로 소자를 전기적으로 연결하는 수직한 범프(bump)들을 포함하는 임 베디드 인쇄회로기판을 제시한다.

- [0006] 상기 제1 및 제2회로 소자들은 능동 소자, 커패시터 또는 레지스터일 수 있다.

- [0007] 본 발명의 다른 일 관점은, 인쇄회로기판; 상기 기판 내에 매몰된 제1커패시터; 상기 제1커패시터에 중첩되게 매몰 적충된 제2커패시터; 및 상기 제1 및 제2커패시터를 전기적으로 연결하는 수직한 범프(bump)들을 포함하는 임베디드 인쇄회로기판을 제시한다.

- [0008] 상기 범프들은 상기 제1 및 제2커패시터를 병렬 연결하게 대향되는 상기 제1 및 제2커패시터의 전극들을 연결하는 것일 수 있다.

- [0009] 상기 기판 표면 상에 형성된 외충 회로 배선충; 및 상기 외충 회로 배선충과 상기 제1커패시터를 연결하는 연결 비아(via)들을 더 포함할 수 있다.

- [0010] 상기 기판 내에 매몰된 제1레지스터; 상기 제1레지스터에 부분적으로 중첩되게 매몰 적충된 제2레지스터; 및 상기 제1 및 제2레지스터가 부분적으로 중첩되는 부분에 위치하여 상호 직렬 연결시키는 제2의 범프를 더 포함할수 있다.

- [0011] 본 발명의 다른 일 관점은, 제1회로 소자가 표면에 매몰된 제1기판을 형성하는 단계; 상기 제1회로 소자에 대향되는 제2회로 소자가 표면에 매몰된 제2기판을 형성하는 단계; 상기 제2회로 소자 상에 범프를 형성하는 단계; 상기 범프에 상기 제1회로 소자가 대향되게 상기 제1기판을 사이에 절연층을 개재하여 상기 제2기판 상에 정렬하는 단계; 및 상기 제2기판, 절연층 및 제1기판을 압착하여 상호 접착시키며 상기 범프가 상기 절연층을 관통하여 상기 제1회로 소자에 연결되게 하는 단계를 포함하는 임베디드 인쇄회로기판 제조방법을 제시한다.

- [0012] 본 발명의 다른 일 관점은, 제1커패시터가 표면에 매몰된 제1기판을 형성하는 단계; 상기 제1커패시터에 대향되는 제2커패시터가 표면에 매몰된 제2기판을 형성하는 단계; 상기 제2커패시터의 양 전극들 상에 범프들을 형성하는 단계; 상기 범프들에 상기 제1커패시터의 양 전극들이 대향되게 상기 제1기판을 사이에 중간 절연층을 개 재하여 상기 제2기판 상에 정렬하는 단계; 및 상기 제2기판, 절연층 및 제1기판을 압착하여 상호 접착시키며 상기 범프들이 상기 중간 절연층을 관통하여 상기 제1커패시터의 양 전극들에 연결되게 하여 상기 제1 및 제2커패시터들을 상호 병렬 연결하는 단계를 포함하는 임베디드 인쇄회로기판 제조방법을 제시한다.

- [0013] 상기 제1기판에 상기 제1커패시터와 이격된 제1레지스터를 매몰하는 단계; 및 상기 제1레지스터에 부분적으로 중첩되게 대향되는 상기 제2기판에 제2레지스터를 매몰하는 단계를 더 포함하고, 상기 범프의 형성 시 상기 제1 및 제2레지스터들을 직렬 연결할 제2의 범프를 함께 형성할 수 있다.

- [0014] 상기 범프는 상기 중간 절연층에 대향되는 끝단이 뾰족한 형상으로 형성될 수 있다.

- [0015] 상기 제1기판을 형성하는 단계는 양면에 각각 제1 및 제2도전층이 형성된 제1절연층을 도입하는 단계; 상기 제1절연층을 관통하여 상기 제1커패시터가 수용될 캐비티(cavity)를 형성하는 단계; 상기 캐비티 내에 상기 제1커패시터를 수용하는 단계; 일면에 제3도전층이 형성된 제2절연층을 상기 제2절연층이 상기 제1커패시터에 대향되게 도입하는 단계; 및 상기 제2절연층과 상기 제1절연층을 상호 접착하여 상기 제2절연층에 상기 제1커패시터가

접착되게 하는 단계를 포함할 수 있다.

- [0016] 상기 캐비티 내에 상기 제1커패시터를 수용하는 단계는 상기 제1도전층 상에 일면이 상기 캐비티 내에 노출되는 접착 필름을 부착하는 단계; 및 상기 제1커패시터를 상기 캐비티 내에 노출된 상기 접착 필름 부분에 접착시키는 단계를 포함할 수 있다.

- [0017] 상기 제1 내지 제3도전층 각각을 회로 배선층들으로 각각 패터닝하는 단계들을 더 포함할 수 있다.

#### 발명의 효과

- [0018] 본 발명에 따르면 기판 내에 수동 소자(passive device)나 능동 소자(active device)와 같은 회로 소자를 임베드(embed)하여 인쇄회로기판(PCB)을 제조할 때, 회로 소자와 회로 소자를 직적 적충(direct stack)하여 실장 밀집도를 향상시킬 수 있다. 상호 적충되는 회로 소자들은 연결 범프(bump)에 의해 연결되므로, 회로 소자들의 연결을 위한 회로 배선충들이 생략될 수 있어 실장 밀집도를 향상시킬 수 있다.

- [0019] 범프에 의해 회로 소자들, 특히, 커패시터와 같은 수동 소자가 상호 간에 직접적으로 연결될 수 있으므로, 상하 적충된 커패시터들이 병렬로 직접적으로 연결되어 커패시턴스(capacitance)의 증대를 구현할 수 있다. 상하 적충된 커패시터들이 병렬로 연결될 수 있으므로, 커패시터들이 차지하는 면적이 단일 커패시터의 크기로 제한 되면서도, 다수의 커패시터들이 병렬 연결될 수 있어 기판 표면적 당 커패시터의 실장 밀도를 증대시킬 수 있으며 기판 표면적 당 커패시턴스의 증대를 구현할 수 있다. 또한, 커패시터와 커패시터를 연결할 때 별도의 복잡한 회로 배선층이 개재되지 않고, 상하 적층된 커패시터들이 수직한 범프를 통해 직접 연결되므로, 복잡한 회로 배선층에 의해 노이즈(noise)의 발생을 억제할 수 있다.

- [0020] 임베디드된 회로 소자들 사이를 연결하는 별도의 회로 배선층을 생략하여 노이즈를 줄일 수 있으므로, 회로 소자들의 동작 성능을 향상시킬 수 있다. 또한, 회로 소자들이 상하 직접 적층에 의해 범프를 통해 직렬 또는 병렬 연결될 수 있으므로, 기판 표면적의 제한에 따른 실장 밀집도의 한계를 극복할 수 있고, 이에 따라, 기판의디자인(design) 설계에서의 기판 표면적의 제한 한계를 극복할 수 있다. 회로 소자들 간의 연결 경로가 수직한 범프의 높이로 단축되므로, 복잡하게 긴 회로 배선층에 의한 연결 경로의 증가에 따른 회로 노이즈 증가를 억제하고, 회로 노이즈의 감소를 구현할 수 있어 기판의 성능 향상을 구현할 수 있다.

#### 도면의 간단한 설명

[0021] 도 1 내지 도 8은 본 발명의 실시예에 따른 임베디드 인쇄회로기판 및 제조방법을 보여주는 도면들이다.

도 9 및 도 10은 본 발명의 실시예에 따른 임베디드 인쇄회로기판 및 제조방법의 효과를 설명하기 위해 제시한 도면들이다.

#### 발명을 실시하기 위한 구체적인 내용

- [0022] 본 발명의 실시예들은 기판 내에 임베드되는 임베디드 소자(embedded device) 또는 회로 소자들이 상호 간에 직접 적층(direct stack)된 인쇄회로기판 구조 및 이를 위한 제조방법을 제시한다. 임베드되는 회로 소자는 수동 소자(passive device)나 능동 소자(active device)일 수 있으며, 수동 소자의 경우 커패시터나 레지스터 (resistor)일 수 있다.

- [0023] 인쇄회로기판이 휴대폰 단말 기기나 디지털 기기에 채용될 때, 고주파에서의 저 임피던스(low impedance)로 인한 로직 소자(LSI)의 파워 노이즈(power noise)나, 반사 노이즈(reflection noise) 또는 상호 교란(cross talk) 등의 특성을 개선하기 위해서, 보다 높은 커패시턴스를 요구하고 있다. 휴대폰 기판에서 커패시터는 실장되는 전체 수동 소자 부품들 중 60% 정도를 차지하고 있으며, 커패시턴스의 확보를 위해 실장되는 커패시터 수는 증대되고 있다. 그럼에도 불구하고, 기판의 크기는 감소되거나 제한되고 있으므로, 보다 높은 커패시턴스를 확보하기 위해서, 본 발명의 실시예에서는 적층형 세라믹 커패시터(MLCC)와 같은 커패시터 소자들을 기판 내에임베드(embed)하고, 커패시터들 상호 간에 직접 상하로 적층된 구조를 제시한다.

- [0024] 커패시턴스를 확보하기 위해서는 커패시터들이 병렬 연결되어야 하는 데, 커패시터들을 기판 표면에 실장할 경우, 표면 실장된 커패시터 옆에 다른 커패시터가 표면 실장되어야 하므로, 커패시터들이 차지하는 기판 표면적은 그 수에 비례하여 급격히 증가하게 된다. 기판의 표면적은 제한되므로 기판 표면에 실장될 커패시터의 수는 제한되게 된다. 이를 극복하기 위해서, 본 발명의 실시예에는 커패시터를 기판 내에 임베드하고, 임베드된 커패시터 상에 중첩되는 위치에 다른 커패시터를 다시 임베드하고, 이를 반복 적층하여 다수 개의 커패시터들을 적

층한 임베디드 기판 구조를 제시한다.

- [0025] 이때, 커패시터들을 병렬 연결하여 보다 큰 커패시턴스를 확보하기 위해서, 상호 적충된 커패시터의 전극들을 연결 범프(bump)를 이용하여 수직 연결한다. 이와 같이 커패시터들이 상호 간에 상하로 직접 적충(direct stack)되므로, 기판에 실질적으로 실장된 커패시터의 수가 증가됨에도 이에 요구되는 기판 표면적의 증가를 유효하게 억제할 수 있다. 이에 따라, 기판에 실장되는 밀집도를 증가시킬 수 있으며, 실질적으로 40% 정도의 기판 크기 감소 효과를 구현할 수 있다.

- [0026] 커패시터와 커패시터가 수직 범프에 의해 직접 연결되므로, 이들 커패시터들을 연결하기 위해 별도의 회로 배선 충을 배제할 수 있다. 적충된 커패시터들을 회로 배선충을 통해 연결하기 위해서는 관통 비아(via)와 비아까지의 연장되는 트레이서(tracer) 배선충이 요구되지만, 수직한 범프를 통해 상측에 적충된 커패시터의 전극과 하측에 적충된 커패시터의 전극이 직접 연결되므로, 즉, 직접 적충 방식으로 커패시터들이 적충되므로, 복잡한 회로 배선충이 생략될 수 있다. 복잡한 회로 배선충은 연장되는 배선충의 길이가 길어 연결 경로가 길고 복잡하기때문에, 긴 연결 경로에 기인하는 기생 커패시턴스 성분과 노이즈가 유발될 수 있다. 이에 비해 연결 범프를 통한 직접 적충 시에는 연결 경로가 범프 높이에 제한되고, 경로가 단순화되므로, 이러한 기생 커패시턴스 성분과노이즈를 유효하게 크게 억제시킬 수 있다. 이에 따라, 기판을 포함하는 모듈(module)의 전기적 특성 및 신뢰성향상을 구현할 수 있다.

- [0027] 본 발명의 실시예에서 제시하는 커패시터의 직접 적층에 의한 임베디드 기판 구조는, 레지스터를 다층으로 적층 하여 임베드하는 구조에도 적용될 수 있다. 이에 따라, 모듈의 소형화를 유효하게 구현할 수 있다.

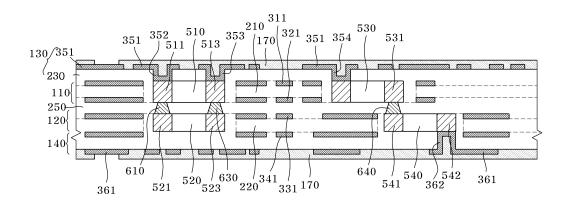

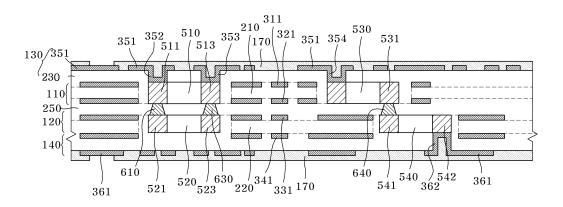

- [0028] 도 1 내지 도 8은 본 발명의 실시예에 따른 임베디드 인쇄회로기판 및 제조방법을 보여준다. 도 1 내지 도 8은 6층의 회로 배선층을 구비하는 인쇄회로기판을 구현하는 과정을 예시하여 본 발명의 실시예에 따른 기판 구조 및 제조 방법을 보여주지만, 본 6층 이상의 회로 배선층을 구비하게 구성하는 데 적용될 수 있다.

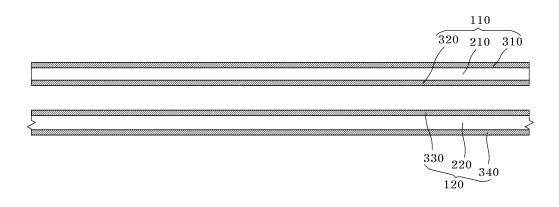

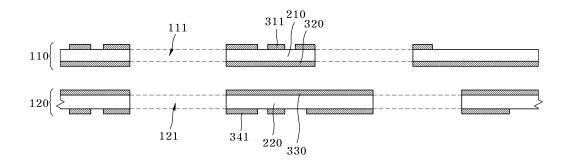

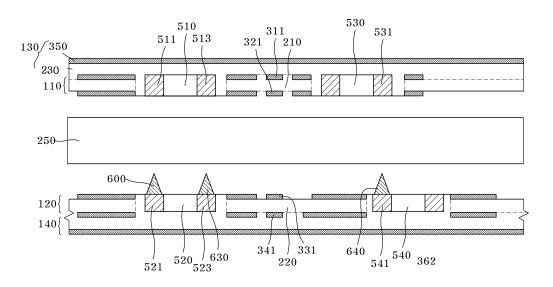

- [0029] 도 1을 참조하면, 2층 및 3층(L2/L3)의 회로 배선층을 위한 제1동박적층기판(CCL: Copper Clad Laminate: 110) 및 제2동박적층기판(120)을 형성한다. 제1 및 제2동박적층기판(110, 120)은 각각은 절연 수지의 제1절연층 (210) 및 제2절연층(220)을 구비하고, 각각의 양면에 도전층들을 형성하여 구빈된다. 제1절연층(210)의 양면에는 예컨대, 구리층의 제1도전층(310) 및 제2도전층(320)이 형성되고, 제2절연층(220)의 양면에는 제3도전층 (330) 및 제4도전층(340)이 구비된다. 제1 내지 제4도전층(310, 320, 330, 340)들은 기판의 2층(L2), 3층(L3), 4층(L4) 및 5층(L5)의 회로 배선층들로 패터닝되기 위해 구비된다.

- [0030] 도 2를 참조하면, 제1 및 제2동박적층기판(110, 120)에 내층 이미지(image) 전사 과정을 사진 노광 및 현상, 식각 과정을 포함하여 수행한다. 이러한 이미지 전사 과정은 도전층을 패터닝하여 구현하고자하는 회로도에 따라 회로 배선층을 패터닝하는 과정이다. 제1동박적층기판(110)의 제1도전층(310)에 이러한 제1내층 이미지 전사 과정을 수행하여, 제1절연층(210) 상의 제1도전층(310)을 회로 배선층인 제1도전층 패턴(311)으로 패터닝한다. 또한, 제2동박적층기판(120)의 제4도전층(340)에 제2내층 이미지 전사 과정을 수행하여, 제2절연층(220) 상의 제4도전층(340)을 역시 회로 배선층인 제4도전층 패턴(341)으로 패터닝한다. 제1도전층 패턴(311)과 제4도전층 패턴(341)은 기판의 내부에 위치하는 내층 회로 배선층 패턴으로 구비된다.

- [0031] 이후에, 기계적 드릴링(drilling) 또는 레이저(laser) 드릴링과 같은 가공 방법을 이용하여 제1절연층(210) 및 제2도전층(320)을 관통하는 제1캐비티(cavity: 111)를 가공한다. 또한, 제2절연층(220) 및 제3도전층(330)을 관통하는 제2캐비티(121)를 가공한다. 이러한 제1 및 제2캐비티(111, 121)들을 기판 내에 임베드될 회로 소자, 예 컨대, 커패시터와 같은 수동 소자가 위치할 공간을 제공하기 위해서 형성된다.

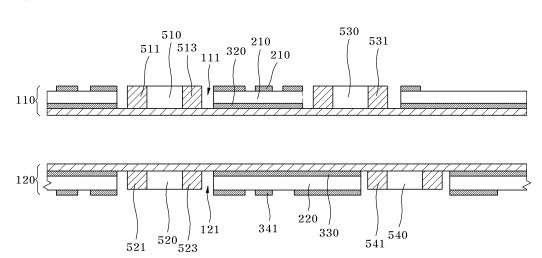

- [0032] 도 3을 참조하면, 이미지 전사에 의한 패터닝이 수행되지 않은 제2도전층층(320) 상에 제1접착 필름(410)을 접착하고, 제1접착 필름(410)에 접착되게 제1캐비티(111)에 제1커패시터(510)를 임베드될 회로 소자로 수용한다. 마찬가지로, 이미지 전사에 의한 패터닝이 수행되지 않은 제3도전층층(330) 상에 제2접착 필름(420)을 접착하고, 제2접착 필름(420)에 접착되게 제2캐비티(121)에 제2커패시터(520)를 임베드될 회로 소자로 수용한다. 이러한 과정은 커패시터(510, 520) 외에 다른 레지스터(530, 540)와 같은 수동 소자나 또는 능동 소자를 임베드시키는 과정에 적용될 수 있다. 제1레지스터(530)는 제1커패시터(510)에 이격된 다른 제1캐비티(111) 내에 수용되고, 제2레지스터(540)는 제2커패시터(520)에 이격된 다른 제2캐비티(121) 내에 수용될 수 있다. 이때, 제1커패시터(510)와 제2커패시터(520)는 상호 간에 중첩되는 위치에 수용되고, 제1레지스터(530)는 제2레지스터(540)와 연결 부분만이 부분적으로 중첩되는 위치에 수용될 수 있다.

- [0033] 도 4를 참조하면, 1층(L1)의 회로 배선층을 위한 제5도전층(350)이 구리층과 같은 도전 물질의 층이 표면에 형

성된 제3절연충(230)의 제3동박적충기판(130)을 준비하고, 6충(L6)의 회로 배선충을 위한 제6도전충(360)이 구리충과 같은 도전 물질의 충이 표면에 형성된 제4절연충(240)의 제4동박적충기판(140)을 준비한다. 이때, 제3절연충(230) 및 제4절연충(240)은 프레스(press)에 의해 다른 기판과 접착될 수 있는 프리프레그(prepreg) 기판을 이루는 절연 수지로 형성될 수 있다.

- [0034] 제3동박적층기판(130)의 제3절연층(230)에 제1도전층 패턴(311)이 매몰되게 제3동박적층기판(130)과 제1동박적 층기판(110)을 프레스(press)하여 상호 접착시킨다. 이때, 프레스 압착 시 열을 인가하여 접착이 이루어지게 할 수 있다. 마찬가지로, 제4동박적층기판(140)의 제4절연층(240)에 제4도전층 패턴(341)이 매몰되게 제4동박적층기판(140)과 제2동박적층기판(120)을 프레스(press)하여 상호 접착시킨다.

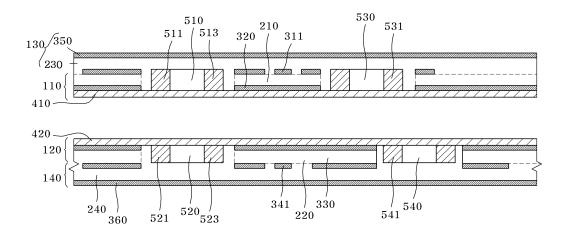

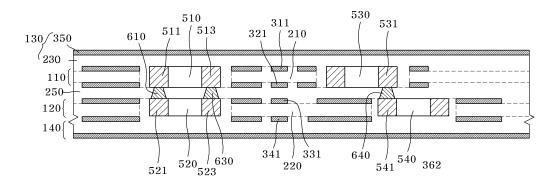

- [0035] 도 5를 참조하면, 제1 및 제2접착 필름(410, 420)을 벗겨내어 제거하고, 노출되는 제2도전층(320) 및 제3도전층 (330) 각각에 내층 이미지(image) 전사 과정을 사진 노광 및 현상, 식각 과정을 포함하여 수행한다. 이러한 이미지 전사 과정은 도전층을 패터닝하여 구현하고자하는 회로도에 따라 회로 배선층을 패터닝하는 과정이다. 제2도전층(320)에 이러한 제3내층 이미지 전사 과정을 수행하여, 제1절연층(210) 상의 제2도전층(320)을 내층 회로 배선층인 제2도전층 패턴(321)으로 패터닝한다. 또한, 제2동박적층기판(120)의 제3도전층(330)에 제4내층 이미지 전사 과정을 수행하여, 제2절연층(230) 상의 제3도전층(330)을 역시 내층 회로 배선층인 제3도전층 패턴 (331)으로 패터닝한다.

- [0036] 도 6을 참조하면, 제3도전층 패턴(331)에 인근하게 노출되는 제2커패시터(520)의 제1전극(521) 및 제2전극(523) 상에 전기적 연결을 위한 도전성의 범프(bump: 600)를 형성한다. 이때, 범프(600)는 원뿔이나 다각뿔과 같이 뾰족한 끝단을 가지는 형상으로 형성될 수 있다. 범프(600)는 제1전극(521) 및 제2전극(523) 상에 인쇄 방식, 예 건대, 스크린 프린트(screen print) 방식으로 형성될 수 있다. 이때, 층간 연결이 요구되는 제2레지스터(540)의 전극(541) 상에도 또한 범프(600)가 형성될 수 있다. 범프(600)가 제2커패시터(520)의 제1전극(521) 및 제2전극(523), 제2레지스터(540)의 전극(541) 상에 형성되는 경우를 예시했지만, 반대로, 제1커패시터(510)의 제1전극(511) 및 제2전극(513), 제1레지스터(530)의 전극(531) 상에 형성될 수도 있다.

- [0037] 범프(600)를 형성한 후, 제3도전층 패턴(331)과 제2도전층 패턴(321)이 마주보게, 즉, 제1커패시터(510)와 제2 커패시터(520)가 마주 대향되게 하고, 그 사이에 제5절연층(250)의 기판, 예컨대 프리프레그 기판을 도입한다. 연후에, 범프(600)가 제5절연층(250)을 관통하게 프레스 압착하여 제5절연층(250)에 제3도전층 패턴(331)과 제2 도전층 패턴(321)이 수용되게 접착시킨다. 이에 따라, 전체적인 임베디드 인쇄회로기판(100)이 구성된다.

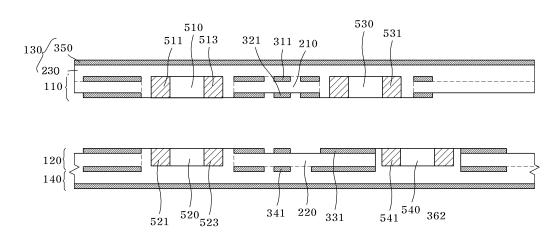

- [0038] 도 7을 참조하면, 범프(600)가 제5절연층(250)을 관통하게 프레스 압착 과정이 수행됨에 따라, 제1커패시터 (510)의 제1전극(511)과 제2커패시터(520)의 제1전극(521)을 상호 연결하는 제1범프(610)가 구비되고, 제1커패시터(510)의 제2전극(513)과 제2커패시터(520)의 제2전극(523)을 상호 연결하는 제2범프(630)가 구비된다. 수직한 형상의 제1범프(610)와 제2범프(630)에 의해서 제5절연층(250)에 의해 격리된 제1 및 제2커패시터(510, 520)는 상호 간에 병렬 연결되게 된다.

- [0039] 따라서, 제1 및 제2커패시터(510, 520)를 상호 병렬 연결시키기 위한 별도의 회로 배선층을 구현하기 위해서, 별도의 도전층의 개재가 요구되지 않는다. 제1범프(610)와 제2범프(630)만으로 제1 및 제2커패시터(510, 520)가 상호 병렬 연결될 수 있으므로, 연결 경로가 매우 짧게 단축되고, 이에 따라, 기생 커패시턴스나 노이즈의 발생을 유효하게 억제할 수 있다. 따라서, 커패시터들에 의해서 구현될 수 있는 전체 커패시턴스의 용량을 유효하게 증가시킬 수 있다. 이와 같이 커패시터(510, 520)들이 직접 적층에 의해 기판(100) 내에 임베드될 수 있으므로, 커패시터가 차지하는 기판(100) 표면적의 증가없이 다수 개의 커패시터들을 기판(100)에 실장하는 것이 가능하다.

- [0040] 한편, 제5절연충(250)을 관통하는 제3범프(640)는 제1레지스터(530)의 전극(531)과 제2레지스터(540)의 전극 (541)을 연결시킨다. 이에 따라, 제1레지스터(530)와 제2레지스터(540)는 직렬 연결되어 보다 중대된 저항 용량을 구현할 수 있다.

- [0041] 도 8을 참조하면, 제3절연층(230)을 관통하여 제1커패시터(510)의 제1전극(511) 및 제2전극(513) 각각을 노출하는 비아홀(via hole)을 레이저 드릴(laser drill) 등으로 형성하고, 노출된 제1전극(511) 및 제2전극(513) 각각에 연결되는 제1연결 비아(352) 및 제2연결 비아(353)를 형성한다. 이때, 제1레지스터(530)의 다른 전극(532, 542)을 노출하는 비아홀을 역시 형성하고, 이에 연결되는 제3연결 비아(354, 362)를 형성할 수 있다. 이러한 연결 비아들은 임베디드된 커패시터나 레지스터를 외층의 회로 배선층에 전기적으로 연결한다. 한편, 기판(100)의 양면으로 노출되어 상호 대향되는 제5도전층(350) 및 제6도전층(360)을 상호 전기적으로 연결시키기 위해서, 기

판(100) 전체를 관통하는 관통홀(도시되지 않음)을 형성하고, 이러한 관통홀을 통해 제5도전층(350) 및 제6도전 층(360)을 연결하는 관통 비아(도시되지 않음) 또한 형성될 수 있다. 이러한 연결 비아나 관통 비아의 형성은 구리 도금과 같은 도전층 형성 방법을 이용하여 비아홀이나 관통홀 내로 도전층이 연장시켜 형성될 수 있다.

- [0042] 기판(100)의 외부로 노출된 제5도전층(350) 및 제6도전층(360) 각각에 외층 이미지 전사 과정을 수행하여 제5도 전층 패턴(351) 및 제6도전층 패턴(361)을 형성한다. 이러한 이미지 전사 과정은 도전층을 패터닝하여 구현하고 자하는 회로도에 따라 회로 배선층을 패터닝하는 과정이다. 제5도전층(350)에 이러한 제1외층 이미지 전사 과정을 수행하여, 제5도전층(350)을 회로 배선층인 제5도전층 패턴(351)으로 패터닝한다. 또한, 제6도전층(360)에 제2외층 이미지 전사 과정을 수행하여, 제6도전층(360)을 역시 회로 배선층인 제6도전층 패턴(361)으로 패터닝한다. 이후에, 제5 및 제6도전층 패턴(351, 361)을 덮는 솔더 마스크(solder mask: 170)를 형성하여, 외부 기기 와의 연결을 위한 노출 부분, 예컨대, 연결 패드(pad)나 랜드(land) 부분만을 선택적으로 노출하고 나머지 제5 및 제6도전층 패턴(351, 361)을 덮어 보호한다.

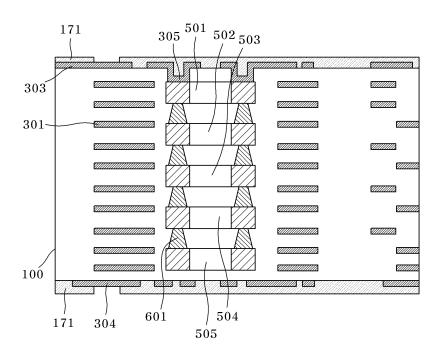

- [0043] 도 9 및 도 10은 본 발명의 실시예에 따른 임베디드 인쇄회로기판 및 제조방법의 효과를 보여주는 도면들이다.

- [0044] 도 9를 참조하면, 본 발명의 실시예에 따른 임베디드 인쇄회로기판은 커패시터와 같은 회로 소자를 수용하는 과정과 범프를 형성하는 과정을 반복하여, 기판(100) 내부에 다수 개의 커패시터(501, 502, 503, 504, 505)들을 상호 중첩되게 적층하고, 이들을 범프(601)를 통해 직접 연결시킬 수 있다. 다수 개의 커패시터(501, 502, 503, 504, 505)가 직접 적층됨에도 불구하고, 각각의 커패시터들은 범프(601)들로만 전기적으로 연결되고, 이들의 연결을 위한 별도의 배선 회로들이 요구되지 않는다.

- [0045] 따라서, 내층 회로 배선층(301)의 설계 디자인이 단순화될 수 있어, 기판 설계 시 제약 요소들이 유효하게 감소하여 다양한 설계가 가능하다. 범프(601)에 의한 직접 연결이 가능하므로, 별도의 복잡한 배선 회로들을 내층 도전층 패턴으로 구비할 필요가 없어, 도전층 패턴들에 의한 노이즈나 기생 커패시턴스의 유발에 의해, 소자의 동작 성능의 저하가 유효하게 억제될 수 있다. 커패시터(501, 502, 503, 504, 505)를 외부의 다른 회로 배선층, 즉, 외층 회로 배선층(303, 304)에 연결하기 위해서, 하나의 커패시터(501)의 두 전극들에 각각 연결되는 연결비아(305)만이 요구되므로, 커패시터(501)의 전기적 연결을 위해 복잡한 연결 배선 구조가 요구되지 않는다.

- [0046] 도 10을 참조하면, 이러한 본 발명의 실시예에 따른 효과에 대비되는 비교예로서, 범프가 아닌 회로 배선충(31, 32, 33, 34, 35, 36, 37, 38, 39)으로 기판(10)에 임베디드된 커패시터들(50)을 연결시키는 경우를 고려하면, 보다 큰 전체 커패시턴스를 확보하기 위해서 커패시터들(50)을 병렬 연결시키기 위해서는 매우 복잡한 회로 배선충(31, 32, 33, 34, 35, 36, 37, 38, 39) 구조의 설계 및 구현이 요구된다.

- [0047] 커피시터(50)의 전극(51, 53)들 간을 병렬 연결하기 위해서, 제1전극(51)들을 연결시키는 회로 배선층의 구조와 제2전극들(53)을 연결시키는 회로 배선층의 구조가 상호 간에 솔더 마스크(17)에 의해 전기적으로 격리되어야 한다. 따라서, 제1전극들(51)을 연결시키기 위해서 제1연결 비아(31), 제1외층 회로 배선(32), 제1관통홀(11)에 형성되는 제1관통 비아(33), 이에 연결되는 다수의 제1내층 회로 배선들(34)이 요구된다. 또한, 제1전극들(51)을 상호 연결시키기 위해서 제2연결 비아(35), 제2외층 회로 배선(36), 제2관통홀(12)에 형성되는 제2관통 비아(37), 이에 연결되는 다수의 제2내층 회로 배선들(38)이 요구된다. 또한, 기판(100) 내부에 임베드된 커피시터 (50)의 전극에 내층 회로 배선들(34, 38)을 연결하기 위한 내부 연결 비아(39)들 또한 요구된다. 커피시터들 (50)을 병렬 연결시키기 위해서는 매우 복잡한 회로 배선층(31, 32, 33, 34, 35, 36, 37, 38, 39) 구조의 설계 및 구현이 요구된다.

- [0048] 커피시터들(50)을 병렬 연결시키기 위해서는 매우 복잡한 회로 배선층(31, 32, 33, 34, 35, 36, 37, 38, 39) 구조가 요구되므로, 이를 설계하는 데 매우 다양한 제약들이 발생될 수 있어 설계 디자인이 매우 어려워질 수 있으며, 이를 구현하는 공정 또한 매우 복잡해지게 된다. 이에 비해 도 9에 제시된 바와 같은 본 발명의 실시예에 따른 임베디드 인쇄회로기판은 상대적으로 매우 단순한 구조로 구현될 수 있어, 그 설계 상 상대적으로 용이하고 이를 구현하는 공정 또한 상대적으로 단순화될 수 있다. 더욱이, 기판의 표면에 나란히 커페시터들을 실장하는 경우에 비해 실장되는 커페시터당 커페시터의 실장에 요구되는 기판의 표면적이 매우 감소될 수 있으므로, 다양한 휴대 기기에 본 발명의 실시예에 따른 임베디드 인쇄회로기판은 유효하게 적용될 수 있다.

# 부호의 설명

[0049] 100: 인쇄회로기판, 510, 520: 커패시터,

610, 630: 범프.

# 도면

# 도면1

# 도면2

# 도면4

# 도면5

# 도면7

# 도면8