35

(21) Application No. 22810/78 (22) Filed 25 May 1978

(31) Convention Application No. 841431 (32) Filed 12 Oct. 1977 in

(33) United States of America (US)

(44) Complete Specification Published 23 Sep. 1981

(51) INT. CL.<sup>3</sup> G05B 15/02

(52) Index at Acceptance G3N 385 402 BA4

## (54) INTEGRATED CIRCUIT CONTROLLER PROGRAMMABLE WITH UNIDIRECTIONAL-LOGIC INSTRUCTIONS REPRESENTATIVE OF SEQUENTIAL WIRE NODES AND CIRCUIT ELEMENTS OF A LADDER DIAGRAM

(71) We, CUTLER-HAMMER WORLD TRADE INC. a Corporation organised and existing under the laws of the State of Delaware, United States of America of 4201 North 27th Street, Milwaukee, Wisconsin 53216, United States of America, do hereby declare the invention, for which we pray that a patent may be granted to us, and the method by which it is to be performed to be particularly described in and by the following statement:-

This invention relates to a programmable controller, which is programmable with logic

instructions representative of circuit nodes of a ladder diagram.

The task of a programmable controller is to compute the logic status represented by interconnected contacts and to apply the end result of such logic computation to a coil to either energize or deenergize it or to send such result to the outside to control external

devices such as solenoids, for example.

This logic and the interconnected contacts represented thereby is illustrated by a diagram. The convention used in such diagram is based on the standard practice used to represent electro-mechanical relay logic and is retained in programmable controller applications because of the widespread familiarity with this type of diagram, commonly termed a "ladder diagram" because each set of logic that corresponds to one output resembles the rung of a ladder. That is, in a ladder diagram, the left and right verticals are the power lines and the horizontal "rungs" are the sets of logic representing the control elements such as interconnected contacts as shown in Figure 1 of the accompanying drawings

In an electro-mechanical relay ladder diagram, the direction of logic is from the left hand vertical 110 volt A.C. power line flowing through the contacts and coils to the right hand vertical power line. The programmable controller emulates this action, but there are quite significant differences between the internal functions of the programmable controller and

the relay system that it replaces. Among these are:

1. In the relay system, the logic actions occur in parallel or simultaneously through the "rungs" of the ladder. In the programmable controller, these logic actions are computed

sequentially, one contact at a time.

2. In the programmable controller, the external contacts are not an actual part of the logic, as are the pushbuttons and limit switches of the relay system, but rather power signals therefrom are brought into the programmable controller and then "relayed" through isolators to become input signals. The programmable controller then treats these external contacts in the same manner as internal contacts except as controlled by an input signal

3. There are no L1 and L2 power lines for the logic section of the control even though two vertical lines may be drawn on a programmable controller diagram. In the latter, there is a logic flow from the left line to the right line rather than a power flow as in the relay

system ladder diagram.

4. In the programmable controller, the results of logic actions are "relayed" out through such devices as photo-isolators and Triacs in order to control external devices.

In view of the above, the functions of programmable controllers can be actually grouped into three sections: (1) the input section consisting of the power source from line L1-L2 and connections through limit switches and pushbuttons to the input terminals of the controller; (2) the logic section based on internal processing resembling to a great degree computer-like functions; and (3) the output section where logic function results control

45

5

10

15

20

25

30

35

40

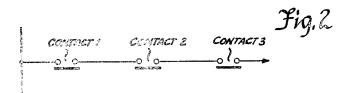

| 5  | external devices connected to the output terminals of the controller and power lines L1-L2. As stated previously, the logic task consists of determining the state of a signal coming from a set of interconnected contacts, based both on how the contacts are interconnected and the states of the individual contacts, open or closed. There are only two basic contact connections to be considered: the series connection and the parallel connection. Figure 2 shows the series connection. The logic action is: a logic signal will flow from left to right and be present at the "output" if, and only if, all three contacts are closed. This is the equivalent of an AND-logic operation, that is a logic "1" is obtained if Contact-1 and Contact-2 and | 5  |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

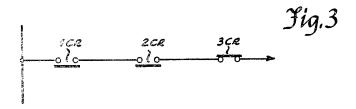

| 10 | Contact-3 are closed.  But more precisely, one does not think in terms of contacts being open or closed but rather whether the devices controlling the contacts are energized or deenergized. This leads to the concept of normally-open and normally-closed contacts. Figure 3 shows three contacts where reference is made to the control coils controlling the contacts and where that contact controlled by coil 3CR is normally-closed. The logic action is now described as                                                                                                                                                                                                                                                                                  | 10 |

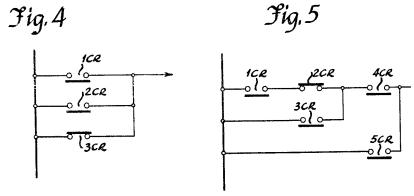

| 15 | follows: a logic "1" signal is obtained if, and only if, coils 1CR and 2CR are energized and coil 3CR is deenergized. The logic equivalent of labeling a contact as normally closed is the NOT-logic operation.  The parallel connection is shown in Figure 4. Here, the logic action is: a logic output of                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 15 |

| 20 | "1" is obtained if, and only if, either coil 1CR or 2CR is energized or if coil 3CR is deenergized. This is commonly regarded as equivalent to the logic-OR operation.  Programmable controllers compute the logic represented by series and parallel contacts through sequential instructions placed into a memory. Each instruction has a portion indicating the type of operation to be performed, series or parallel, and a reference number                                                                                                                                                                                                                                                                                                                   | 20 |

| 25 | defining where the internal processor is to go to find the status of the device (input or coil) controlling the contact. The programmer must determine and write these instructions according to the manner in which the contacts are interconnected.  Programming is quite simple for contacts in series. One could write three instructions for the logic of Figure 3 thus:                                                                                                                                                                                                                                                                                                                                                                                      | 25 |

| 30 | SERIES N.O. 1CR<br>SERIES N.O. 2CR<br>SERIES N.C. 3CR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 30 |

| 35 | where "SERIES" indicates the type of internal action to be performed, actually an AND-logic operation, and 1CR, 2CR and 3CR are the "reference numbers" for the internal control coils energizing the "contacts". As seen, the instructions are also "tagged" N.O. or N.C., meaning normally-open and normally-closed.  Programming is also simple for the parallel connection of Figure 4 where one would write:                                                                                                                                                                                                                                                                                                                                                  | 35 |

| 40 | OR N.O. 1CR<br>OR N.O. 2CR<br>OR N.C. 3CR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 40 |

| 45 | Programming simplicity, however, can be retained when series and parallel operations are intermixed only if all paralleled contacts are connected to the left line as illustrated in Figure 5. The instructions for this would be:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 45 |

| 50 | SERIES N.O. 1CR<br>SERIES N.C. 2CR<br>OR N.O. 3CR<br>SERIES N.O. 4CR<br>OR N.O. 5CR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 50 |

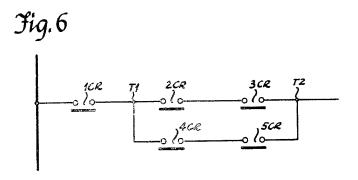

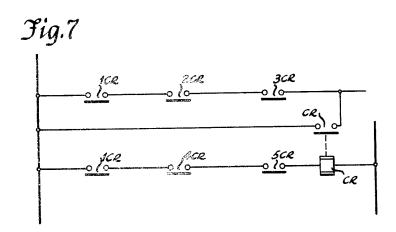

| 55 | The early prior art controllers required parallel contacts to be connected in this fashion; most of the small ones still do. This means that a diagram such as Figure 6 must be modified as shown in Figure 7 by introducing a coil to get the single contact going to the left line since you can "OR" only a single contact with the previous result. The added elements increase                                                                                                                                                                                                                                                                                                                                                                                | 55 |

| 60 | It is desirable to have a programming means which accommodates such configurations as Figure 6 without requring the user to modify his diagram. This could be done if means within the processor were provided to store and retrieve the partial results of the logic operation. The program for Figure 6 might then be written:                                                                                                                                                                                                                                                                                                                                                                                                                                   | 60 |

|    | SERIES N.O. 1CR<br>STORE T1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5  | SERIES N.O. 2CR SERIES N.O. 3CR STORE T2 RETRIEVE T1 SERIES N.O. 4CR SERIES N.O. 5CR OR T2                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5  |

| 10 | The action is as follows: at the first branch, it is recognized that one will have to come back                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 10 |

| 15 | later and compute the alternative parallel branch. Accordingly, the logic value at that point is stored in location T1 of the memory present for this purpose. When the first branch has been traversed, the logic value at this point is also stored in location T2. The programmer then backs up and retrieves the value in location T1 to start the second branch. The result at the end of the second branch is OR'd with the value in location T2.  The procedure outlined is available in certain prior art large controllers and in at least         | 15 |

| 20 | one small controller. The large controllers provide cathode-ray tube diagram monitors which simplify the task of storing and retrieving temporary logic results. However, programming can become difficult without such aids when diagrams become complex, for the programmer must then keep track of a number of temporary results, storing and retrieving them as required. It is especially difficult for maintenance men to grasp the logic being performed by a list of instructions as given above. Accordingly, it is desirable to                   | 20 |

| 25 | provide improved means that are simple and easy to program and does not require any diagram modification.                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 25 |

|    | In accordance with the present invention, there is provided a programmable controller having a main memory in which is stored program data defining the configuration of a ladder diagram, and a control means operative to address the main memory sequentially and repetitively and perform logic computations and control functions in executing said                                                                                                                                                                                                    |    |

| 30 | program in accordance with the ladder diagram configuration, the ladder diagram comprising rungs having numbered contacts connected in series by numbered wires (forming circuit nodes) such that the number of an output wire from a contact is the same as the number of an input wire to the next contact, said control means comprising an                                                                                                                                                                                                              | 30 |

| 35 | addressable wire number memory storing the current state of each numbered wire and an addressable control coil memory storing the current state of each of a plurality of coils of the ladder diagram which coils control at least predetermined ones of said contacts, and said control means being operative, in response to any change of state of any numbered wire or                                                                                                                                                                                  | 35 |

| 40 | coil, to update the wire number memory or control coil memory, in respect of that wire or coil. An embodiment of the invention to be described herein is an improved programmable controller that renders programming of a ladder diagram simple and easy without requiring modification of the ladder diagram for programming purposes. The wire number and control coil memories store the result of each and every logic function and the status of every control coil whereby the programmer need not keep track of which logic function                | 40 |

| 45 | results have been stored and which have not. The stored program uses unidirectional-logic instructions and the status of each wire number of the ladder diagram is stored thereby to                                                                                                                                                                                                                                                                                                                                                                        | 45 |

|    | render programming simple and straightforward.  The embodiment includes means for forcing "on" or "off" any wire number under manual control thereby to observe the performance of the outputs or set up latching relays when restarting from an interrupted condition. A means is provided including wired-in logic                                                                                                                                                                                                                                        |    |

| 50 | means setting a state indicative to the processor that the left-hand vertical power conductor of a ladder diagram is always in the "on" state thereby to avoid the necessity of a special instruction therefor.                                                                                                                                                                                                                                                                                                                                             | 50 |

| 55 | The embodiment includes logic function circuitry consisting primarily of a combination of three flip-flops and clock control for performing AND logic functions and controlling storage of the results thereof and in addition thereto an inhibit logic circuit for performing OR logic functions and controlling storage of the results thereof. It also includes improved initial-power-on control means for holding the logic circuits in a reset or "0" output condition when power is first turned on and then when power is fully on, controlling the | 55 |

| 60 | processor to be clocked so that it will start at the beginning of an address scan rather than on a random time basis.  The embodiment includes improved programming means affording programming a series "rung" of a ladder diagram in partial overlapping sequence with respect to wire numbers                                                                                                                                                                                                                                                            | 60 |

| 65 | and contacts in logic terms such that the state of a second wire number is the logic AND result of the states of a first wire number and first contact, the state of a third wire number is the logic AND result of the states of a first wire number and first contact, the state of a third                                                                                                                                                                                                                                                               | 65 |

|    | wire number is the logic AND result of the states of the second wire number and a second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5  | contact, etc.  Improved programming means are provided in the embodiment, affording programming all but the last of a set of parallel contacts connected to an output wire number such that the output wire number can be set to an "on" state by any of the parallel contact instructions                                                                                                                                                                                                                                                                                                                                             | 5  |

| J  | and final action is inhibited until the last parallel contact instruction has been processed thereby to obtain an OR-logic result. Improves means is provided for storing the results of all of its AND and OR logic functions for use in subsequent logic operations.  Such embodiment of this invention will now be described, by way of example only, with                                                                                                                                                                                                                                                                          | J  |

| 10 | reference to the accompanying drawings, in which:  Figure 1 shows a standard relay ladder diagram of an electrical system for turning a lamp on and off;                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 10 |

|    | Figure 2 is a diagram showing series normally-open contacts representing an AND-logic function;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

| 15 | Figure 3 is a diagram showing a series connection of normally-open contacts and a normally-closed contact representing an AND-logic function which includes a NOT logic function represented by the normally-closed condition of the contact;  Figure 4 is a diagram showing a parallel connection of normally-open contacts and a                                                                                                                                                                                                                                                                                                     | 15 |

| 20 | normally-closed contact representing an OR-logic function which includes a NOT logic function represented by the normally-closed condition of the contact;  Figure 5 is a diagram showing series and parallel connection of normally-open contacts and normally-closed contact representing AND and OR-logic functions wherein all                                                                                                                                                                                                                                                                                                     | 20 |

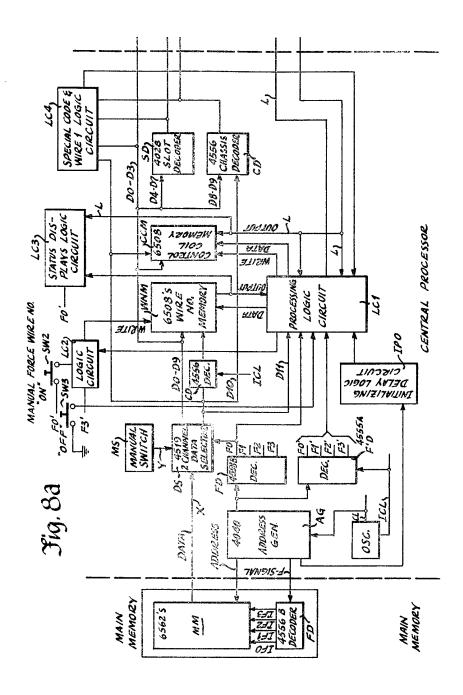

| 25 | paralleled contacts connected to the left power line of the ladder diagram;  Figure 6 is a diagram showing series and parallel connection of normally-open contacts wherein the paralleled contacts do not connect to the left power line of the ladder diagram;  Figure 7 is a diagram showing how the diagram of Figure 6 must be modified to obtain a condition wherein all paralleled contacts are connected to the left power line;  Figures 8a-b are a block diagram showing generally the architecture of an embodiment of                                                                                                      | 25 |

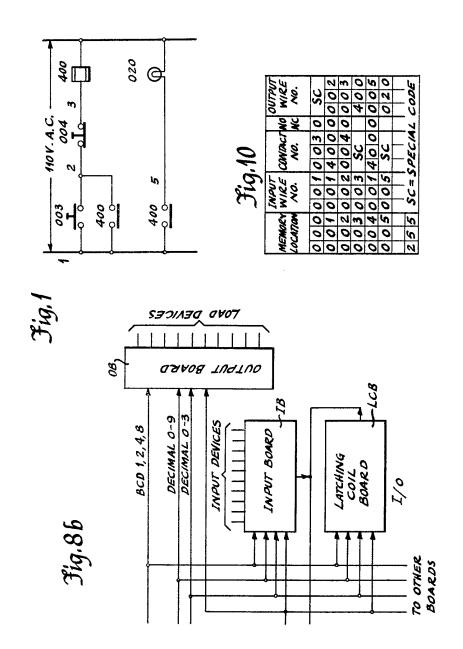

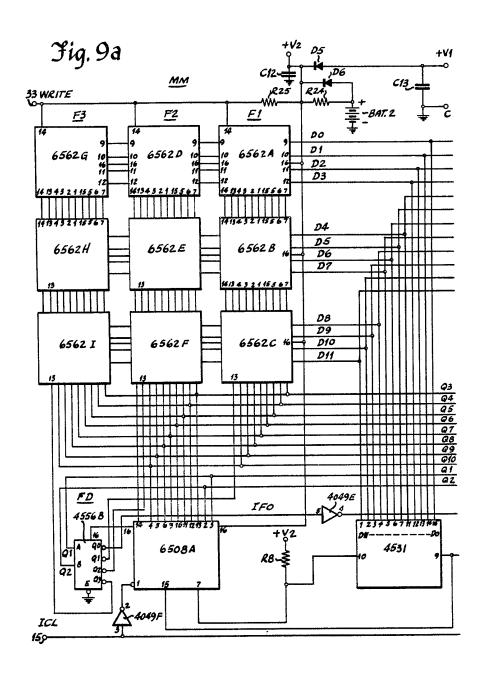

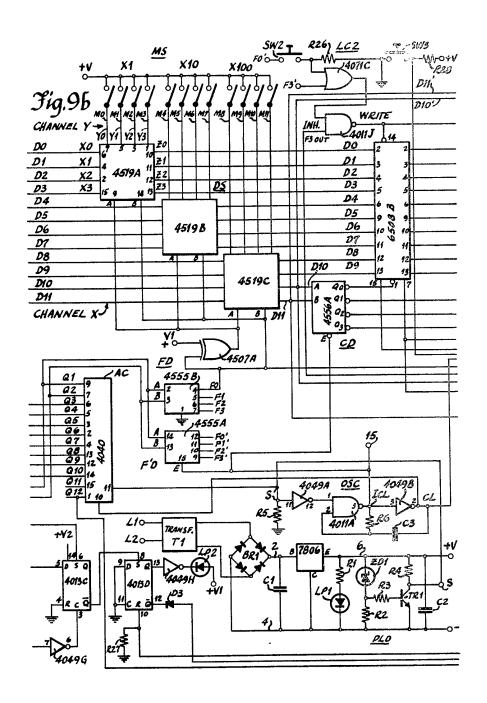

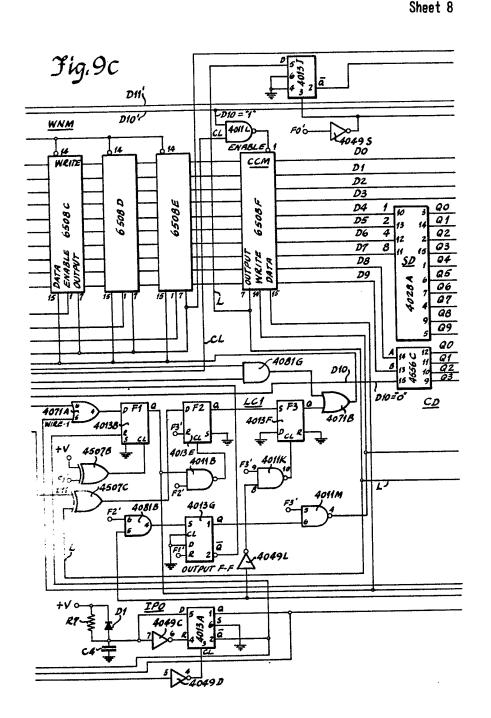

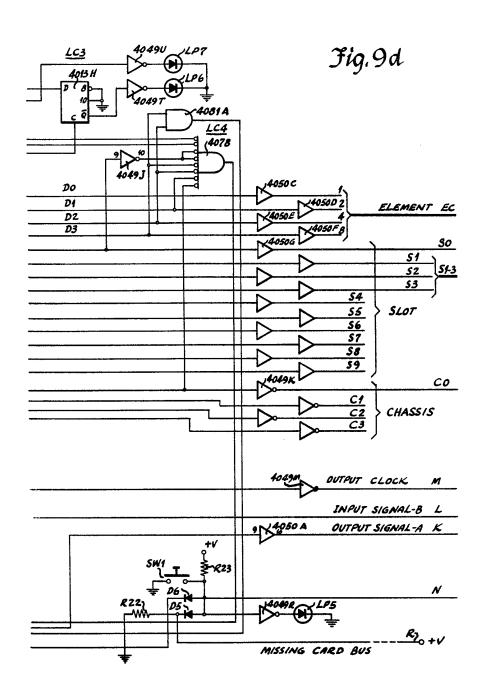

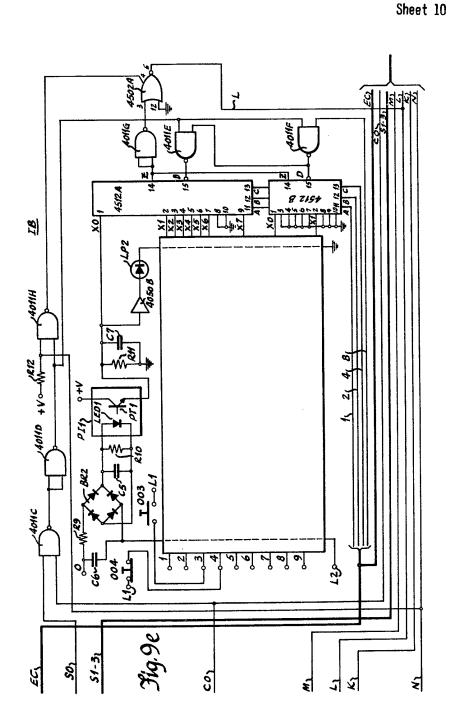

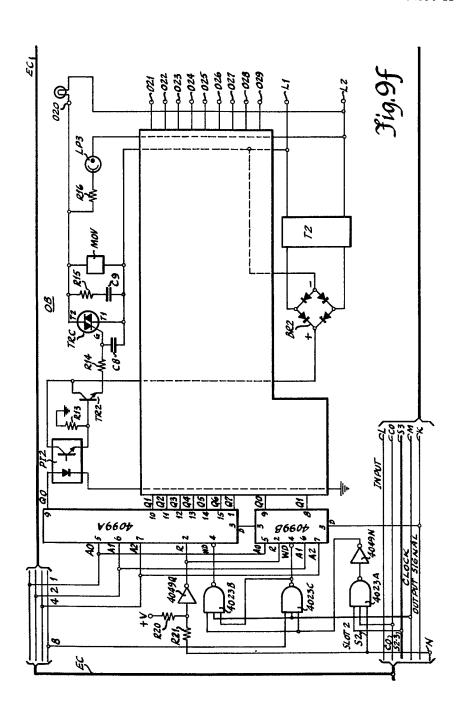

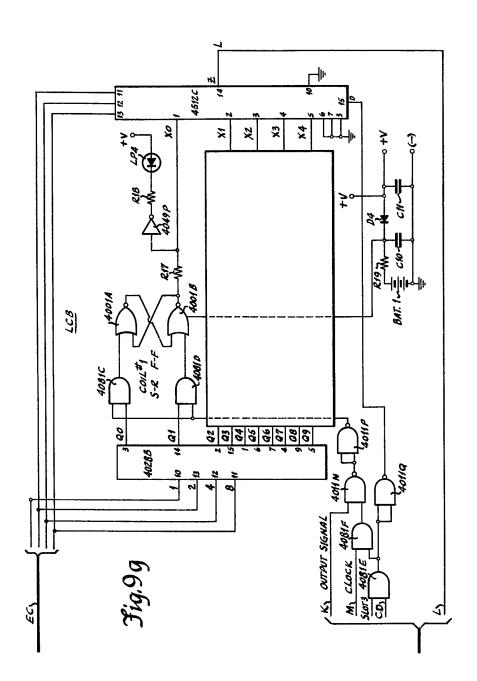

| 30 | programmable controller in accordance with the invention;  Figures 9a-g are a logic diagram showing in detail the construction of the programmable controller of Figures 8a-b;                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 30 |

| 35 | Figure 10 is a table showing in decimal form how the ladder diagram of Figure 1 may be programmed into the main memory of the controller;  Figure 11 is a table showing how the main memory may be addressed to read out the program of Figure 10 therefrom;  Figure 12 is a graph showing initial power on operating characteristics of the controller of Figure 9a-g; and                                                                                                                                                                                                                                                            | 35 |

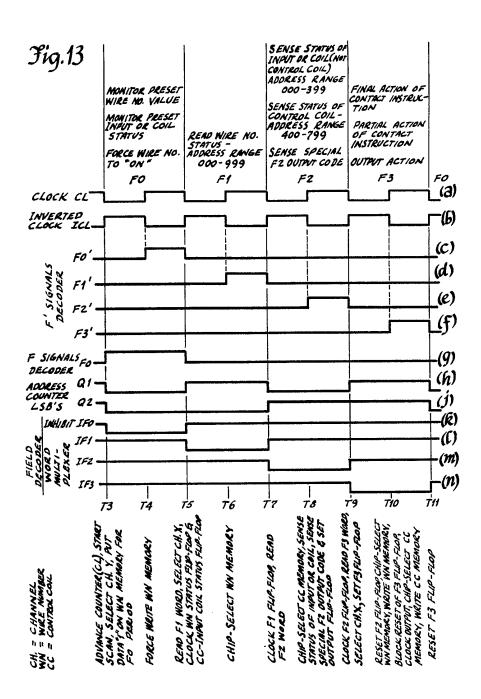

| 40 | Figure 13 is a timing chart showing operating characteristics of the programmable controller of Figures 9a-g.  This description will begin with a general description of the block diagrm of Figures 8a-b and will continue with a detailed description of the detailed diagram of Figures 9a-g.  Referring to Figures 8a-b, there is shown a programmable controller in block diagram                                                                                                                                                                                                                                                 | 40 |

| 45 | form constructed in accordance with the invention. This controller comprises three generally distinct parts, namely, a main memory section, a central processor section, and an input-output (I/O) section.  The main memory section shown at the left-hand portion of Figure 8a comprises a field decoder FD and a memory module MM or a plug-in type printed circuit (PC) board having                                                                                                                                                                                                                                               | 45 |

| 50 | a memory array of the required word capacity mounted thereon. The function of this memory module is to receive, store and make available to the central processor the series of instruction words constituting the program for the controller. For this purpose, this memory module may be of the RAM (random access memory), ROM (read only memory) or the PROM (programmable read only memory) type, or any other type suitable for the purpose.                                                                                                                                                                                     | 50 |

| 55 | While a single memory module is shown for illustrative purposes, it will be apparent that more than one memory module may be used if needed for a larger word capacity. Also, a single bord may have a memory chip array of one of several different word capacities depending upon the desired application of the controller.                                                                                                                                                                                                                                                                                                         | 55 |

| 60 | The I/O section shown in Figure 8b comprises input modules or PC boards, output modules or PC boards, and combination input-output modules or PC boards of the latching coil type or the like. Other types such as timers, steppers, sequencers or the like may also be used therein. The input boards receive external input signals from input devices such as pushbuttons, limit switches, transducers, or the like, and transform them to logic levels. They then may be transmitted to the central processor. The output boards receive internal output signals from the central processor and transform them to power levels for | 60 |

| 65 | transmission to output or load devices such as solenoids, contactors, indicator lamps, or the like to control the same. The combination I/O boards receive internal logic signals from the                                                                                                                                                                                                                                                                                                                                                                                                                                             | 65 |

central processor in response to which they perform certain functions such as latching, or the like, and then transmit logic signals back to the central processor to link such functions to control "contacts" therein. While only one input board IB, one output board OB, and one latching coil board LCB have been shown in Figure 8b, it will be understood that more thereof and other types of boards can be connected to the multiple conductors.

5

10

15

20

25

30

35

40

45

50

55

60

65

The central processor is the control part of the system. This central processor includes a clock CL in the form of an oscillator OSC for performing the timing functions of the system so that every action occurs in its proper and logical order without interfering with any of the other functions. This central processor also includes an address generator AG for providing scanning or cyclic signals for performing certain functions. One of these functions is to address the main memory so that program instruction words may be read out therefrom. Some of these signals are sent to a field decoder FD in the main memory for providing inverted F-signals IF1, IF2 and IF3 for time-division multiplexing purposes and others of these signals are sent directly to the main memory for addressing the same. The multiplexing signals IF1, IF2 and IF3 select memory chip groups whereas the address signals address locations in these memory chip groups to read out the instructions or data therefrom. Signal IF0 is an inhibit signal as hereinafter described in connection with Figures 9a-g.

9a-g.

This address generator also supplies F-signals to a pair of decoders including an F-decoder FD and an inverted clock ICL controlled F'-decoder F'D. As shown in Figure 8a, the F-decoder gates a 2-channel data selector DS to connect a manual selector switch MS therethrough during the FO time period or to connect the output data channel from the main memory therethrough during the F1, F2 and F3 time periods. These periods are time division multiplex periods or fields as shown graphically in Figure 13 during which instruction words read from the main memory or received from the manual selector switch are processed. Inverted clock ICL controlled F'-decoder F'D provides timing signals for controlling the processing logic circuits as hereinafter more fully described in connection

with the detailed logic diagram shown in Figures 9a-g.

The central processor also includes an initializing delay or initial power on logic circuit IPO. The purpose of this logic circuit is to hold the processor logic elements and circuits in their reset or "0" output condition when power is first turned on or if there is a significant dip in power. Then, when power is fully on, rather than allowing the processor to start on a random time basis, this initial power on logic circuit will allow the processor to be clocked so that it will start at the beginning of a scan at main memory address zero rather than commencing at a random place in a scanning cycle.

The central processor also includes a wire number memory WNM shown in Figure 8a. This wire number memory is the significant portion of the processor architecture that provides the programming basis termed wire number programming. The ladder diagram shown in Figure 1 is given wire numbers as with relay control, such as wire numbers 1, 2, 3 and 5. Each wire number defines a wire or "circuit node" connecting the output of one circuit element to the input of the next circuit element. The instructions written by the programmer define the logic connected to each wire number. The processor then determines the status of each wire number and maintains a complete record thereof in the wire number memory incorporated for this purpose. That is, the processor stores in the wire number memory the status of each wire number and updates this status if there is any change in it each time that the program is repeatedly run, that is, on each scan. As will be seen, this makes possible a particularly simple programming method for, in effect, the result of every logic operation is now stored away and the programmer no longer has to pick and choose as well as to keep track of what has been stored. The maintaining of wire number status also affords a powerful maintenance tool in that signal tracing is now just a matter of calling up wire number values from the wire number memory. The wire number memory is addressed by the data received through the 2-channel data selector from the main memory. A portion of this data is transmitted to a chip-decoder CD that decodes the same under inverted clock ICL control for selection of the correct chip in the wire number memory while the remainder of the data addresses the location in the wire number

number status will be described in more detail in connection with Figures 9a-g.

The central processor alao includes a control coil memory CCM shown in Figure 8a. The control coils are relay coils such as coil 400 in Figure 1 exclusive of any coils such as latching coils or the like that are in the I/O section of the controller. The control coil memory is addressed by the data received through the 2-channel (X,Y) data selector DS from the main memory. This is done whenever a contact of the control relay shown in the ladder diagram is being processed thereby to ascertain the status of the contact. That is, if the control coil status read from the control coil memory over bus L is indicative of an energized control

memory. Wire number status is written into the wire number memory under the control of logic circuits LC1 and LC2 and signal F3'. The apparatus for reading and writing the wire

|    | coil and the contact being processed is a normally-open contact, the logic circuits will perform a function indicating that such contact is closed so that the logic signal will flow from left to right through such contact. On the other hand, if the control coil status read                                                                                                                                                                                                   |    |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5  | from the control coil memory is indicative of a deenergized control coil and the contact<br>being processed is a normally-closed contact, the logic circuits will perform a function<br>indicating that such contact is closed so that the logic signal will flow from left to right<br>through such contact. Similarly, an energized coil and a normally-closed contact indication<br>and a deenergized coil and a normally-open contact indication will prevent such logic signal | 5  |

| 10 | flow. A normally-open (N.O.) contact and a normally-closed contact (N.C.) are indicated by a data bit read from the main memory, the NC contact being an inversion or NOT function relative to the NO contact on data bus D11. When a control coil is energized or deenergized as a result of an output signal, the new status of such control coil is written into                                                                                                                 | 10 |

| 15 | the control coil memory by the logic circuits. The apparatus for reading or writing the control coil status from or into the control coil memory will be described in more detail in connection with Figures 9a-g.  The central processor is also provided with a slot decoder SD and a chassis decoder CD                                                                                                                                                                          | 15 |

| 20 | shown in Figure 8a for transforming the data received through the 2-channel (X, Y) data selector from the main memory to put it in suitable form for output from the central processor and for addressing the input and output devices in the I/O section of the system. As indicated in Figure 8b, the first four data by Do-D3 are used on a binary-coded decimal                                                                                                                 | 20 |

| 25 | BCD-1, 2, 4, 8 basis to address one of ten elements on a selected I/O printed circuit (PC) board. The next four data bits D4-D7 are changed in slot decoder SD from BCD to decimal 0-9 to address one of ten slots in a selected chassis of I/O PC boards and, consequently, the PC board in the selected slot. The next two data bits D8-D9 are changed in chassis decoder CD from binary to one-of-four 0-3 to address one of four chassis. And the next data bit D10             | 25 |

| 25 | is used to distinguish I/O addressing from control coil memory addressing.  The central processor is also provided with means to monitor a selected wire number status or a selected control coil or input status. For this purpose, the address of a desired wire number is set on manual switches MS. During the FO time period, the address on the                                                                                                                               | 23 |

| 30 | manual switches is substituted for the data from the main memory and is transmitted to the wire number memory, the control coil memory, and to the inputs and coil elements in the I/O section of the system. The status of the addressed wire number is applied from the output of the wire number memory to status displays logic circuit LC3. The latter is gated                                                                                                                | 30 |

| 35 | by the FO' signal to display the status of the wire number on suitable indicators. The input signal on bus L which holds the status of the output of the control coil memory or the status of the input or coil in the I/O section is applied to status displays logic circuit LC3 which is gated by the FO' signal to display the status of the selected control coil or selected input or                                                                                         | 35 |

| 40 | coil in the I/O section.  The central processor is also provided with means for forcing any wire number to "on" or "off" state. This means is useful to observe the performance of an output device or to set up latching relays or to drop out a sealed circuit, or the like. For example, if the operator                                                                                                                                                                         | 40 |

| 45 | desires to check the operation of an output device, he can force the corresponding output wire number to "on" state and then observe whether the output device operates properly. Also, in the event of a machine stoppage due to power interruption or some other cause, the operator can use this means to conveniently set up the latching relays in their correct                                                                                                               | 45 |

|    | states to pick up the sequence of operation from the point of interruption. Or the operator can drop out a maintained circuit.  For this purpose, the desired wire number is set up on manual switches MS whereby the selected wire number will be addressed in the wire number memory during the FO time                                                                                                                                                                           |    |

| 50 | period. At the same time, processing logic circuit LC1 applies a data signal "1" or "0" to the wire number memory under the control of switch SW3 for the FO time period. Now when manual force wire number pushbutton switch SW2 is pressed closed, a write signal is applied through logic circuit LC2 during the FO' time to force the wire number "on" or                                                                                                                       | 50 |

| 55 | "off", followed by the consequent results hereinbefore described.  The central processor is also provided with a special code and wire-1 logic circuit LC4 shown in Figure 8a. The wire-1 logic circuit provides a condition indicative that the left-hand power conductor, that is, wire-1 in the ladder diagram of Figure 1, is always "on"                                                                                                                                       | 55 |

| 60 | or energized. This enables the program to get started without a special instruction for this purpose. For this purpose, logic circuit LC4 provides a signal for wire-1 that is substituted for the output from the wire number memory to indicate the "on" condition to the logic circuit LC1.                                                                                                                                                                                      | 60 |

| 65 | The aforesaid special code logic circuit LC4 is used to define an output instruction. This is done by a special code in the F2 time period. This special code provided by this logic circuit is other than a decimal code. When the processing logic circuit senses this special code, an output action will take place rather than writing the status into the wire number memory.                                                                                                 | 65 |

| The aforesaid special code logic circuit LC4 is also used to control an OR logic function where the outputs of several contacts go to the same wire number. The instructions for such contacts are processed as a group but all except the last are partial instructions. The processor will OR together the results of the partial instructions, finally combining with the final instruction for outputting to the wire number memory. This OR action is obtained by using the special code from logic circuit LC4 to inhibit resetting a flip-flop on each partial instruction until the final instruction. The result is that any parallel OR contact can develop an output on a partial instruction as well as on the final instruction and will remain until after the final instruction of the last parallel contact has been processed.  These functions will be described in more detail hereinafter by reference to the specific logic elements in connection with the detailed diagram shown in Figures 9a-g. | 5    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Detailed Description  Referring to Figures 9a-g, there is shown a detailed logic diagram of the programmable controller that was shown in block diagram form in Figures 8a-b. The various logic elements will be identified and their functional characteristics will be described in connection with the description of operation of this detailed diagram.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 15   |

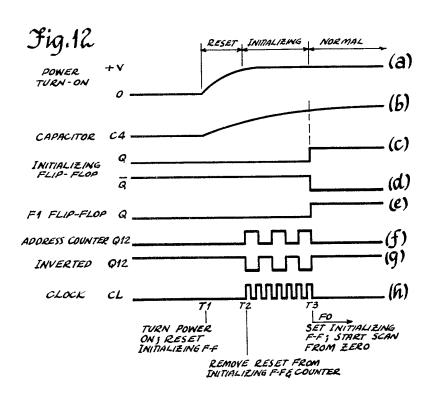

| To consider the operation of this controller, let it first be assumed that power is initially connected thereto. This means that a D.C. voltage of proper magnitude is applied to the various points marked $+V$ , $+V1$ and $+V2$ . As shown by curve 12(a); meaning curve (a) in Figure 12, when the power is first turned on at time T1, its value is initially low from which it rises to almost its full value at time T2. When this power voltage $+V$ is initially low,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 20   |

| power level detector PLD at the lower portion of Figure 9b responds thereto to apply a positive voltage from terminal S to reset terminal 4040-11 of 12-stage binary counter 4040; terminal 4040-11 meaning terminal 11 of integrated circuit (IC) 4040 this 4040 being the conventional identifying number therefor used in integrated circuit handbooks. This convention will be used throughout the description of Figures 9a-g. This positive voltage,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 25   |

| meaning logic high or "1" as compared to logic low or "0", on reset terminal 4040-11 resets all the 12 outputs of this counter to "0" state and holds them at "0" state until the applied power has risen almost to its full value. Since a CMOS memory such as is used herein for the main memory cannot be cycled while the power level is changing below about 95 percent of rated value, that is why the counter is held at reset until the power level has risen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 30   |

| to near full value.  This power level detector as well as the power supply circuit are shown in detail in Figure 9b. A.C. power is connected to power supply lines L1 and L2 and then through a transformer T1 and a full-wave rectifier bridge BR1 to conductors 2 and 4. A filter capacitor C1 is connected across conductors 2 and 4. The B and C input terminals of an integrated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 35   |

| circuit fixed-voltage regulator 9806 are connected across conductors 2 and 4 while the 6-volt D.C. output terminal E thereof is connected to conductor 6 and common terminal C thereof is connected to conductor 4. An indicator circuit consisting of a resistor R1 and a lamp LP1 such as an LED (light emitting diode) or the like are connected in series across conductors 6 and 4 to indicate when the power is on. The aforesaid power level detector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 40   |

| circuit PLD comprises a zener diode ZD1 and a resistor R2 connected in series across conductors 6 and 4 with the junction therebetween connected through a resistor R3 to the base of a transistor TR1. The collector of this transistor is connected to terminal S and also through a resistor R4 to conductor 6 while its emitter is connected to conductor 4. A filter capacitor C2 is connected across conductors 6 and 4. Conductors 6 and 4 are connected to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 45   |

| positive and negative (common or ground) D.C. supply terminals +V and (-), respectively, while terminal S is connected to the oscillator terminal S'.  When A.C. power is connected to lines L1 and L2 as shown by curve 12(a) at time T1, the DC voltage begins to rise on conductor 6 toward its 6-volt final value. Initially, transistor TR1 is non-conducting since zener diode ZD1 having a value of 4.7 breakover voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ` 50 |

| blocks current flow through resistor R3 to the transistor base as the voltage on conductor 6 rises. Consequently, the positive voltage on conductor 6 is applied through resistor R4 and terminal S to terminal S' at the oscillator OSC.  As aforementioned, this positive voltage is applied from terminal S' to reset terminal 4040-11 to hold the binary counter reset to zero for the initializing period. This blocks addressing of the CMOS memory MM while power is rising or falling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 55   |

addressing of the CMOS memory MM while power is rising or falling.

This power level detector PLD also holds oscillator OSC inoperative for the initializing period by applying the positive voltage to inverter terminal 4049A-11, which is connected through resistor R5 to ground. This positive voltage causes a low output from this inverter to be applied to NAND terminal 4011A-1 which in turn causes a high output from NAND terminal 4011A-3. This high output is applied through resistor R6 to NAND input terminal 4011A-2 and to inverter input terminal 4049B-3 and a resultant low is applied from inverter output 4049B-2 to capacitor C3 to maintain the oscillator inoperative from time T1 to time

T2 as shown by curve 12(h).

15

20

25

At time T2, the power voltage +V on conductor 6 has risen above 4.7 volts, the breakover voltage of zener diode ZD1, as shown by curve 12(a). As a result, current flows from conductor 6 through zener diode ZD1 and resistor R3 to the base of transistor Q2 to turn it on. This causes the voltage at terminal S to be dropped very near ground potential, in effect, a logic "low", thus removing the "high" from reset terminal 4040-11 of the binary counter and from terminal 4049A-11 of the inverter to allow the oscillator to start running as shown by curve 12(h) at time T2. This is the end of the reset period and the start of the initializing period as indicated at the top of Figure 12. As a result, the oscillator applies clock pulses from inverter terminal 4049B-2 to input terminal 4040-10 of the binary counter to start the latter counting and thus generating memory addresses as hereinafter described. Like integrated circuits such as the 4049 type inverters in the oscillator as referenced 4049A, 4049B, etc., 4049 being its handbook identification number.

5

10

15

20

25

30

35

40

45

50

55

60

65

The clock pulses shown in Figure 12(h) are exaggerated for illustrative purposes. The address generator is a 12-bit binary counter whereby it takes 4096 clock pulses input to this counter to operate the counter through one address scan, that is, from zero count through the counter capacity back to zero count. Thus, in Figure 12(f), the address counter Q12 (twelfth binary bit) pulse goes to "1" at a count of 2048 half-way through the address scan and to "0" at a count of 4096 at the end of the address scan. Thus, it is apparent from comparing curves (f) and (h) in Figure 12 that there are many more clock pulses for each address counter Q12 pulse. However, that will serve to illustrate the function of the invention. What is important and will be used is the "1" to "0" transition of the counter output bit Q12 to set the initializing flip-flop as hereinafter described rather than allowing

random setting thereof during a scan.

The initializing period indicated at the top of Figure 12 is controlled by the initializing delay logic IPO shown at the lower portion of Figure 9c. When power is first turned on as aforementioned, or if there is a significant dip in power level, the action in this integrated circuit controller must be similar to the action in relay control, that is, sealed-in relays must drop out, etc. The equivalent action is produced by the initializing delay circuit at the lower portion of Figure 9c. Initially, before power is turned on as aforementioned, capacitor C4 is discharged. Upon application of power, the capacitor C4 voltage will still be low with the result that this low is applied to inverter input 4049C-7, effecting a high from inverter output 4049C-6 that is applied as a reset signal to initializing flip-flop 4013A reset R terminal 4013A-4 to reset this flip-flop. As a result, a high is applied from the Q output 4013A-2 to the reset terminal R of the F1 flip-flop 4013B to reset the latter. The result is that the F1 field will be held at "0" and all processor actions will result in "0" F3 outputs both as to wire numbers and output devices.

As hereinbefore alluded to, initializing flip-flop 4013A will be clocked back to its set condition. For this purpose, capacitor C4 will charge by current flow through resistor R7 as shown by curve (b) in Figure 12. As shown therein, this capacitor C4 charging delay is longer than the reset time T1-T2 and extends near time T3. After this delay when capacitor C4 has charged enough, the inverted reset signal will have decreased and been removed from initializing flip-flop 4013A and at the same time a data "1" will be applied to data terminal 4013A-5 of the initializing flip-flop and the latter will be clocked back on or to its set state by the address counter. This data "1" high will be applied directly from capacitor C4 to data terminal 4013A-5. During this time, the oscillator is running and the address counter is counting. When the address counter reaches its full count completing its present scan and all output bits are reset to "0" including bit Q12, a clock pulse is taken from Q12 output terminal 4040-1 and applied to inverter input 4049D-5 where a positive-going pulse is applied from inverter output 4049D-4 to clock terminal 4013A-3 to clock the initializing flip-flop back to its set state. This removes the reset from the F1 flip-flop and insures that normal processor action starts at the beginning of the next scan (memory address zero)

rather than commencing at a random place in the scanning cycle. Diode D1 in the initializing control circuit in Figure 9c allows a fast discharge of capacitor C4 if there is a significant dip in the power supply voltage level thereby affording reset and initializing actions similar to those hereinbefore described. This is done because otherwise

such dips in power voltage might result in erroneous operation.

Program storage

Before describing the operation of the controller, it will first be explained how the ladder diagram configuration is arranged in the main memory. Figure 1 shows a simple ladder diagram that will serve for illustrative purposes. As shown therein, the left vertical is numbered "1" and the wire nodes toward the right along the "rungs" starting from the top run are numbered "2", "3", etc. as is common practice in relay ladder diagrams. The controller to be described has a capacity for processing 1,000 wire numbers numbered from

25

5

10

15

20

30

35

40

45

50

55

65

zero to 999 or over an address range of 0-999.

In this ladder diagram, the pushbuttons and lamp are input and output elements in the I/O section of the controller. The pushbuttons are numbered 003 and 004 and the lamp is numbered 020. This controller has a capacity such that up to 400 such elements can be addressed in the I/O section over an address range of 000-399. This address range may overlap the wire number address range because they are in different multiplexed time slots so that there will be no interference as will become apparent.

The address range from 400-799 is used to address control coils in the control coil memory. As shown in Figure 1, the control coil is numbered 400 and each of its two contacts is also numbered 400. The control coil memory is actually the equivalent of an input-output device but having a capacity of the equivalent of 400 control coils. It is located in the processor for convenience as shown in Figure 8a and 9c. One bit, D11, in the control coil addressing word defines a N.O. or N.C. contact. If the contact is N.O., D11 is "0" and if the contact is N.C., D11 is "1". As will be apparent, this amounts to nothing more than inverting the signal from the sensed control coil element if D11 is "1", that is, if the contact is N.C.

The ladder diagram configuration shown in Figure 1 is programmed into the main memory as shown in Figure 10. The left column shows the successive memory locations numbered in sequence from 000 to 005 and up to 255 if needed. Figure 9a shows nine HM-6562 memory chips of the 256 X 4 CMOS RAM type with three columns F1, F2 and F3 having three chips, 6562A-C, 6562D-F, and 6562G-I in the respective columns. These columns of memory chips are identified as F1, F2 and F3 to relate them to similarly identified multiplexed time slots or fields hereinafter for convenience. Each chip has four bits output and 256 locations so that the three chips in parallel in each column provide 12-bit words. With the main memory having three columns of chips with three in each column, there is provided memory capacity of three 12-bit words for each memory location. That is, column F1 has a 12-bit word in location 000, column F2 has a 12-bit word in location 000, and column F3 has a 12-bit word in location 000. With this memory arrangement, the input wire number 001 shown in the second column of Figure 10 is stored in column F1, location 000 of the memory. The contact number 003 shown in the third column of Figure 10 is stored in column F2, location 000 of the memory along with one "0" bit Q11 indicative of the N.O. character of the contact. And the special code SC shown in the last column of Figure 10 is stored in column F3, location 000 of the memory. From this arrangement, it will be seen that the main memory can be addressed by multiplexing the same location in the three memory chip columns in sequence.

This method of programming a ladder diagram shown in Figures 1 and 10 is called wire number programming. Each wire number defines an interconnected portion, or node, of the circuit. The instructions written by the programmer as illustrated in Figure 10 define the logic connected to each wire number. Wire number programming requires only two instructions: (1) the contact instruction (having three parts) and (2) the output instruction.

## Contact Instruction

The contact instruction is written for each contact and consists of the aforesaid three parts shown in Figures 1, 10 and 11 including: (F1) the number of the input wire at the left of the contact, (F2) the contact reference number, and (F3) the output wire number at the right of the contact. As aforementioned, the contact reference number further has a Q11 bit flagging the contact as normally-open or normally-closed. As indicated above, the three sections of this instruction are termed F1, F2 and F3, respectively, to relate them to the data word fields or periods and the respective columns of memory chips in Figure 9a. In the contact instruction, the logic is taken as flowing from the left to the right only, that is, unidirectional logic.

Processing starts with wire number 001 which is assumed to be permanently "on" by having its logic wired in as hereinafter described. This enables the program to get started without a special instruction. The instructions for series contacts are processed in succession. For each, the status of the input wire is retrieved from the wire number memory unless it is wire-1. If the input wire is "on" and the contact is closed, the output wire is set "on" and stored as such in the wire number memory.

In the case where contacts are connected in parallel, the instructions are stored in the memory in succession as a group except all but the last one are stored in the memory as "partial", and the last one is stored as "final". For the "partial" instructions, a special code, SC in Figure 10, is substituted for the output wire number code. The processor detects this special code when going through the instructions and treats this and any following instructions also having such special code as connected to the same wire. Logically, the results from these instructions are OR'd until the final instruction is detected whereupon the result of the OR operations, including the final operation, is stored in the wire number

|    | memory. Figure 10 shows contact instructions in memory locations 000, 001, 002 and 004.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5  | Output Instruction  The output instruction has only two parts, F1 and F3. The input wire number connected to an output such as a control coil, latching coil, timing coil, or power output is stored in field F1. The output device reference number is then stored in field F3. A special code (1111) is stored in field F2 to indicate to the processor that an output instruction is present. This special code is the same as the partial instruction special code as hereinafter described                                                                                                                        | 5  |

| 10 | except that it is in the F2 field rather than the F3 field. Figure 10 shows output instructions in memory locations 003 and 005, each having a special code SC in field F2.  The special code SC in both cases is actually 1111 and this is automatically displayed as a blank on the programming panel (not shown) when the memory is being programmed. All 1's is a very convenient special code to use, however, it suffices to sense only the 4 and 8 bits of the 1, 2, 4, 8 BCD code since that is a non-decimal special code and, as such, would not                                                             | 10 |

| 15 | be used for addressing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15 |

| 20 | Timing Chart, Figure 13  Before continuing with the description of operation of the Figure 9a-g diagram, reference will be made to the timing chart shown in Figure 13. This timing chart may be regarded as starting at its left side from the point where the initializing graph of Figure 12 ended at its right side at time T3, that is, the normal period.  As shown in Figure 13, a continuously running symmetrical oscillator, OSC in Figure 9b, and the size of the first helf of                                                                                                                             | 20 |

| 25 | generates a clock signal CL, curve (a) in Figure 13, that goes negatively for the first half of each F period and positively for the second half thereof. The F periods are F0, F1, F2 and F3 as indicated at the top of Figure 13 and repeat as shown in Figure 11 and hereinafter described. This clock signal CL is primarily used for running address generator binary counter 4040 in Figure 9b.                                                                                                                                                                                                                  | 25 |

| 30 | There is also an inverted clock signal ICL, curve (b) shown in Figure 13, used for clocking the wire number memory chip-select decoder 4556A and the F' signal decoder 4555A in Figure 9b and for controlling the parity check in the main memory as hereinafter described. The next four signals (c), (d), (e) and (f) in Figure 13 are the F0', F1', F2' and F3' signals provided by F' decoder 4555A in Figure 9b for performing many of the timing operations in                                                                                                                                                   | 30 |

| 35 | the processor as hereinafter more fully described.  The next signal (g) in Figure 13 is the F0 signal provided by F-period decoder 4555B in Figure 9b for controlling the data channel switches and the data input to the wire number memory.                                                                                                                                                                                                                                                                                                                                                                          | 35 |

| 40 | The next two signals (h) and (j) are the two least significant bits outputs Q1 and Q2 of the binary address counter AC in Figure 9b for controlling the field decoder 4556B in the main memory in Figure 9a.  The next signal (k) in Figure 13 is the inhibit FO signal IFO for the parity check flip-flop 4013C in Figure 9c provided by the first output Q0 of the field decoder 4556B in Figure 9b.  The last three signals (l), (m) and (n) are the word multiplexer signals IF1, IF2, and IF3 provided by the second, third and fourth outputs Q1, Q2 and Q3 of the inverted-F, field decoder 4556B in Figure 9a. | 40 |

| 45 | Main Memory Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 45 |

| 50 | The purpose of main memory addressing is to read the program instructions from the memory in sequence and to process them in conjunction with any inputs to provide the resultant outputs to run a machine or the like. The manner of memory addressing is shown in Figure 11. The oscillator generates the basic timing signal known as the clock CL, curve (a) in Figure 13, and it is applied to binary counter input terminal 4040-10 in Figure 9b. As shown in Figure 13(a), this clock signal goes low for the first half thereof and goes high for                                                              | 50 |

| 55 | the second half thereof. This binary counter is advanced on the leading negative-going edge of the clock pulse as depicted in Figure 13. Thus, at time T3, the clock pulse goes negative which causes all outputs of the binary counter to be set to zero for the beginning of a new scan. The negative-going edge of the next clock pulse advances the counter to count 1 as shown by guest (b) in Figure 12, that is, this curve goes from "0" to "1". The next clock                                                                                                                                                | 55 |

| 60 | shown by curve (h) in Figure 13, that is, this curve goes from "0" to "1". The next clock pulse sets curve (j) to "1" and resets curve (h) to "0" for a binary count of 2. And the next clock pulse sets curve (h) to "1" while leaving curve (j) at "1" for a binary count of 3, etc. These curves (h) and (j) are the two least significant bits (LSB's) Q1 and Q2 of the binary counter output and are used for main memory addressing as hereinafter described.  These two LSB's also define the F0, F1, F2 and F3 time periods.                                                                                   | 60 |