(19) 日本国特許庁(JP)

# (12) 特許公報(B2)

(11)特許番号

特許第6155168号 (P6155168)

(45) 発行日 平成29年6月28日 (2017.6.28)

(24) 登録日 平成29年6月9日(2017.6.9)

FI(51) Int. CL.

HO2M 3/155 (2006, 01)

HO2M 3/155 HO2M 3/155

> (全 10 頁) 請求項の数 2

特願2013-225188 (P2013-225188) (21) 出願番号

(22) 出願日 平成25年10月30日 (2013.10.30) (65) 公開番号 特開2015-89210 (P2015-89210A)

平成27年5月7日(2015.5.7) (43) 公開日 審查請求日

平成27年11月4日(2015.11.4)

前置審查

||(73)特許権者 501137636

C

W

東芝三菱電機産業システム株式会社 東京都中央区京橋三丁目1番1号

|(74)代理人 110001737

特許業務法人スズエ国際特許事務所

(72) 発明者 清田 一樹

> 東京都港区三田三丁目13番16号 東芝 三菱電機産業システム株式会社内

審査官 宮本 秀一

最終頁に続く

## (54) 【発明の名称】電力変換装置

#### (57)【特許請求の範囲】

# 【請求項1】

直流入力電源の電圧を、直流リアクトルとチョッパ素子が直列接続されたチョッパ回路 を複数個並列接続された電力変換回路により昇圧して電力母線に印加する電力変換装置に おいて、

前記各チョッパ素子を点弧するゲート信号を発信する共通のチョッパ素子用ゲート信号 生成回路と、

前記1つのチョッパ素子に流れる電流を検出する第1のホール電流検出器と、

前記第1のホール電流検出器の出力から一つのチョッパ回路の電流値を検出する電流検 出回路と、

前記直流入力電源と前記チョッパ回路との接続部に流れる総電流を検出する第2のホー ル電流検出器と、

第2のホール電流検出器の出力から総電流値を検出する総電流検出回路と、

前記総電流検出回路で求めた総電流値の過電流レベルが設定された総過電流レベル設定 器と、

前記総電流検出回路で求めた総電流値と前記総過電流レベル設定器で設定された電流設 定値を比較し、前記総電流値が電流設定値を超えたときに1を出力する総過電流比較器と

前記総電流検出回路で検出した総電流値を前記チョッパ回路の並列数で除算することに より個別電流の平均値を算出する個別電流算出回路と、

前記個別電流算出回路の出力と前記電流検出回路の出力の差を求める減算器と、 前記減算器の出力を絶対値にする全波整流回路と、

前記全波整流回路の出力のアンバランスレベルを設定するアンバランスレベル設定器と

前記アンバランスレベル設定器のアンバランスレベルと前記全波整流回路の出力とが比較され、前記全波整流回路の出力が前記アンバランスレベルの設定値を上回ったとき 1 が出力されるアンバランス比較器と、

前記総過電流比較器の出力と前記アンバランス比較器の出力の内、いずれかが1を出力 した時に1を出力する論理和素子と、

前記論理和素子の反転出力と前記チョッパ素子用ゲート信号生成回路出力の論理積から前記各チョッパ素子の点弧、消弧を制御する論理積素子と、

を備え、<u>少なくとも一つの前記チョッパ回路の電流値は検出せずに、</u>前記電力変換回路の過電流及び前記各チョッパ回路毎の過電流から保護するようにしたことを特徴とする電力変換装置。

#### 【請求項2】

直流入力電源の電圧を、直流リアクトルとチョッパ素子が直列接続されたチョッパ回路を複数個並列接続された電力変換回路により昇圧して電力母線に印加する電力変換装置において、

前記各チョッパ素子を点弧するゲート信号を発信する共通のチョッパ素子用ゲート信号生成回路と、

前記1つのチョッパ素子<u>の入力側</u>に流れる電流を検出する第1のホール電流検出器と、前記第1のホール電流検出器の出力から一つのチョッパ回路の電流値を検出する電流検出回路と、

前記電力変換回路と前記電力母線との接続部に流れる<u>総</u>電流を検出する第2のホール電流検出器と、

第2のホール電流検出器の出力から出力電流値を検出する出力電流検出回路と、

前記出力電流検出回路で求めた出力電流値の過電流レベルが設定された総過電流レベル設定器と、

前記出力電流検出回路で求めた出力電流値と前記総過電流レベル設定器で設定された電流設定値を比較し、前記出力電流値が電流設定値を超えたときに1を出力する総過電流比較器と、

前記出力電流検出回路で検出した出力電流値を前記チョッパ回路の並列数で除算することにより前記チョッパ回路の出力の個別電流の平均値を算出する個別電流算出回路と、

前記個別電流算出回路の出力と前記電流検出回路の出力の差を求める減算器と、

前記減算器の出力を絶対値にする全波整流回路と、

前記全波整流回路の出力のアンバランスレベルを設定するアンバランスレベル設定器と

前記アンバランスレベル設定器のアンバランスレベルと前記全波整流回路の出力とが比較され、前記全波整流回路の出力が前記アンバランスレベルの設定値を上回ったとき 1 が出力されるアンバランス比較器と、

前記総過電流比較器の出力と前記アンバランス比較器の出力の内、いずれかが1を出力 した時に1を出力する論理和素子と、

前記論理和素子の反転出力と前記チョッパ素子用ゲート信号生成回路出力の論理積から前記各チョッパ素子の点弧、消弧を制御する論理積素子と、

を備え、<u>少なくとも一つの前記チョッパ回路の電流値は検出せずに、</u>前記電力変換回路の過電流及び前記各チョッパ回路毎の過電流から保護するようにしたことを特徴とする電力変換装置。

【発明の詳細な説明】

【技術分野】

10

20

30

40

本実施形態は、直流入力電源の電圧を、直流リアクトルとチョッパ素子が直列接続されたチョッパ回路を複数個並列接続された電力変換回路により昇圧して電力母線に印加する電力変換装置に関する。

#### 【背景技術】

## [0002]

従来、直流入力電源の電圧を、直流リアクトルとチョッパ素子が直列接続されたチョッパ回路を複数個並列接続された電力変換回路により昇圧して電力母線に印加する電力変換装置がある。

【先行技術文献】

【特許文献】

[0003]

【特許文献1】特開平5-260726号公報

【発明の概要】

【発明が解決しようとする課題】

[0004]

前述の電力変換装置にあっては、電力変換回路全体、および、並列構成のチョッパ回路 毎の過電流を防ぐことができる電力変換装置の開発が望まれていた。

[0005]

本実施形態は、電力変換回路全体、および、並列構成のチョッパ回路毎の過電流を防ぐことができる電力変換装置を提供することを目的とする。

【課題を解決するための手段】

[0006]

本実施形態の代表例は、直流入力電源の電圧を、直流リアクトルとチョッパ素子が直列 接続されたチョッパ回路を複数個並列接続された電力変換回路により昇圧して電力母線に 印加する電力変換装置において、前記各チョッパ素子を点弧するゲート信号を発信する共 通のチョッパ素子用ゲート信号生成回路と、前記1つのチョッパ素子に流れる電流を検出 する第1のホール電流検出器と、前記第1のホール電流検出器の出力から一つのチョッパ 回路の電流値を検出する電流検出回路と、前記直流入力電源と前記チョッパ回路との接続 部に流れる総電流を検出する第2のホール電流検出器と、第2のホール電流検出器の出力 から総電流値を検出する総電流検出回路と、前記総電流検出回路で求めた総電流値の過電 流レベルが設定された総過電流レベル設定器と、前記総電流検出回路で求めた総電流値と 前記総過電流レベル設定器で設定された電流設定値を比較し、前記総電流値が電流設定値 を超えたときに1を出力する総過電流比較器と、前記総電流検出回路で検出した総電流値 を前記チョッパ回路の並列数で除算することにより個別電流の平均値を算出する個別電流 算出回路と、前記個別電流算出回路の出力と前記電流検出回路の出力の差を求める減算器 と、前記減算器の出力を絶対値にする全波整流回路と、前記全波整流回路の出力のアンバ ランスレベルを設定するアンバランスレベル設定器と、前記アンバランスレベル設定器の アンバランスレベルと前記全波整流回路の出力とが比較され、前記全波整流回路の出力が 前記アンバランスレベルの設定値を上回ったとき1が出力されるアンバランス比較器と、

前記総過電流比較器の出力と前記<u>アンバランス</u>比較器の出力の内、いずれかが1を出力した時に1を出力する論理和素子と、前記論理和素子の反転出力と前記チョッパ素子用ゲート信号生成回路出力の論理積から前記各チョッパ素子の点弧、消弧を制御する論理積素子と、を備え、<u>少なくとも一つの前記チョッパ回路の電流値は検出せずに、</u>前記電力変換回路の過電流及び前記各チョッパ回路毎の過電流から保護するようにしたことを特徴とする電力変換装置である。

# [0007]

上記実施形態によれば、電力変換回路全体、および、並列構成のチョッパ回路毎の過電流を防ぐことができる電力変換装置を提供できる。

【図面の簡単な説明】

[ 0 0 0 8 ]

10

20

30

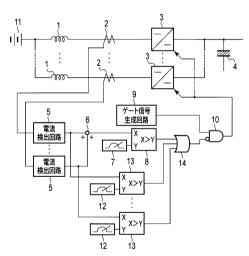

- 【図1】実施形態1を説明するための概略構成図。

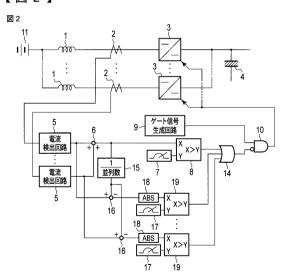

- 【図2】実施形態2を説明するための概略構成図。

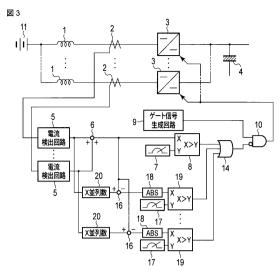

- 【図3】実施形態3を説明するための概略構成図。

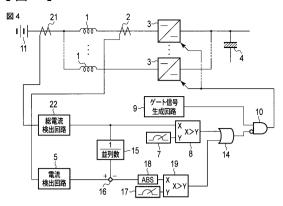

- 【図4】実施形態4を説明するための概略構成図。

- 【図5】実施形態5を説明するための概略構成図。

【発明を実施するための形態】

#### [0009]

以下、各実施形態について、図面を参照して説明する。

# [ 0 0 1 0 ]

図1は実施形態1を説明するための概略構成図であり、これは直流入力電源11の電圧を、直流リアクトル1とチョッパ素子3が直列接続されたチョッパ回路を複数個並列接続された電力変換回路により昇圧して電力母線に印加する電力変換装置において、以下のようになっている。

## [0011]

各チョッパ素子3を点弧するゲート信号を発信する共通のチョッパ素子用ゲート信号生成回路9と、電力変換回路の出力を平滑化する共通のコンデンサ例えば電解コンデンサ4と、各チョッパ素子3に流れる電流をそれぞれ検出する複数の電流検出器2と、各ホール電流検出器2の出力から電流値をそれぞれ検出する複数の電流検出回路5と、加算器6で求めた総電流の過電流レベルが設定された総過電流レベル設定器7と、加算器6で求めた総電流値と総過電流レベル設定器7で設定された電流設定値を比較し、検出レベルを超えた時に1を出力する総過電流比較器8と、各電流検出回路5で検出した電流値の過電流レベルが設定された複数の個別過電流比較器8と、各電流検出回路5で検出した電流値の過電流レベル設定器12と、各電流検出回路5で検出した電流値の過電流レベルが設定された複数の個別過電流比較器8の出力と各個別過電流比較器13の出力の内、いずれかが1を出力した時に1を出力する論理和素子14と、論理和素子14の反転出力とチョッパ素子用ゲート信号生成回路9の出力の論理積から各チョッパ素子3の点弧、消弧を制御する論理積素子10とを備えたものである。

#### [0012]

以上説明した実施形態1によれば、チョッパ回路の並列回路毎に設置されたホール電流検出器2と、電流検出回路5の組み合わせにより検出された並列回路毎の電流値と、個別過電流レベル設定器12の値が個別過電流比較器13により比較され、個別過電流レベルを上回ったときに1が出力される。個別過電流比較器13の出力と、総過電流比較器8の出力のいずれが1になると論理和素子14から1が出力される。このとき、チョッパ素子用論理積素子10の出力が0となり、チョッパ素子3を停止させる信号が発信される。

#### [0013]

このように実施形態 1 によれば、チョッパ回路を複数個並列接続された電力変換回路において、チョッパ回路の並列回路毎に検出された電流の合計値だけでなく、個別の電流値でも過電流を検出してチョッパ素子 3 のインタロックをかけることで、電力変換回路全体だけでなく個々のチョッパ回路の過電流まで防ぐことができる。

# [0014]

図2は実施形態2を説明するための概略構成図であり、これは直流入力電源11の電圧を、直流リアクトル1とチョッパ素子3が直列接続されたチョッパ回路を複数個並列接続された電力変換回路により昇圧して電力母線に印加する電力変換装置において、以下のようになっている。

# [0015]

図1と同様に各チョッパ素子3を点弧するゲート信号を発信する共通のチョッパ素子用ゲート信号生成回路9と、電力変換回路の出力を平滑化する共通のコンデンサ例えば電解コンデンサ4と、各チョッパ素子3に流れる電流をそれぞれ検出する複数のホール電流検出器2と、各ホール電流検出器2の出力から電流値をそれぞれ検出する複数の電流検出回

10

20

30

40

10

20

30

40

50

路5と、各電流検出回路5毎の電流値から総電流値を算出する共通の算出器例えば加算器6と、加算器6で求めた総電流の過電流レベルが設定された総過電流レベル設定器7と、加算器6で求めた総電流値と総過電流レベル設定器7で設定された電流設定値を比較し、検出レベルを超えた時に1を出力する総過電流比較器8を備えている。

#### [0016]

これ以外は、図1とは異なる点で、加算器6で算出された総電流値を、チョッパ回路の並列回路数で除算して個別電流値の平均値を求める個別電流算出回路15と、各電流検出回路5の出力と個別電流算出回路15の出力の差をそれぞれ求める複数の減算器16と、各減算器16の出力の絶対値をそれぞれ求める複数個の全波整流回路18と、各全波整流回路18からの絶対値のアンバランスレベルをそれぞれ設定する複数のアンバランスレベル設定器17と、各アンバランスレベル設定器17の設定値と各全波整流回路18の出力をそれぞれ比較し、アンバランスレベルの設定値を超えた時に1を出力するする複数のアンバランス比較器19と、総過電流比較器8の出力と各アンバランス比較器19の出力の内、いずれかが1を出力した時に1を出力する論理和素子14と、論理和素子14の反転出力とチョッパ素子用ゲート信号生成回路の9出力の論理積から各チョッパ素子3の点弧、消弧を制御する論理積素子10とを備えたものである。

#### [0017]

以上述べた実施形態 2 によれば、チョッパ回路の並列回路毎に設置されたホール電流検出器 2 と、電流検出回路 5 と、加算器 6 と、個別電流算出回路 1 5 の組み合わせにより算出された個別電流算出値とホール電流検出器 2 と、5の電流検出回路の組み合わせにより検出された並列回路毎の電流値の差が、減算器 1 6 により出力される。全波整流回路 1 8 により、減算器 1 6 の出力の絶対値が取られ、アンバランス比較器 1 9 により、アンバランスレベル設定器 1 7 の値と比較され、アンバランスレベルを上回ったときに1が出力される。アンバランス比較器 1 9 の出力と、総過電流比較器 8 の出力のいずれかが1になると論理和素子 1 4 から1が出力される。このとき、チョッパ素子用論理積素子 1 0 の出力が0となり、チョッパ素子 3 を停止させる信号が発信される。

#### [0018]

この結果、実施形態 2 によれば、加算器 6 の出力である総電流が総過電流レベル設定器 7 の設定値を上回るか、各電流検出回路 5 の出力である検出値と加算器 6 で求めた総電流から算出した各チョッパ回路の平均値との差の絶対値が、各アンバランスレベル設定器 1 7 の設定値を上回った時に、チョッパ素子 3 の駆動を停止させる信号を発生することで、回路全体の過電流だけでなく、並列回路間のアンバランスによる過電流を防ぐことができる。

#### [0019]

図3は実施形態3を説明するための概略構成図であり、これは直流入力電源11の電圧を、直流リアクトル1とチョッパ素子3が直列接続されたチョッパ回路を複数個並列接続された電力変換回路により昇圧して電力母線に印加する電力変換装置において、以下のようになっている。

#### [0020]

図1と同様に各チョッパ素子3を点弧するゲート信号を発信する共通のチョッパ素子用ゲート信号生成回路9と、電力変換回路の出力を平滑化する共通のコンデンサ例えば電解コンデンサ4と、各チョッパ素子3に流れる電流をそれぞれ検出する複数のホール電流検出器2と、各ホール電流検出器2の出力から電流値をそれぞれ検出する複数の電流検出回路5と、各電流検出回路5毎の電流値から総電流値を算出する共通の算出器例えば加算器6と、加算器6で求めた総電流の過電流レベルが設定された総過電流レベル設定器7と、加算器6で求めた総電流値と総過電流レベル設定器7で設定された電流設定値を比較し、検出レベルを超えた時に1を出力する総過電流比較器8を備えている。

#### [0021]

これ以外は、図1とは異なる点で、各電流検出回路5で検出した各チョッパ回路の電流値に、チョッパ回路の並列数を積算して電力変換回路の総電流を算出する複数の総電流算

出器 2 0 と、各総電流算出器 2 0 の出力と加算器 6 で求めた総電流の差を求める複数の減算器 1 6 と、各減算器 1 6 の出力の絶対値をそれぞれ求める複数個の全波整流回路 1 8 と、各全波整流回路 1 8 からの絶対値のアンバランスレベルをそれぞれ設定する複数のアンバランスレベル設定器 1 7 の設定値と各全波整流回路 1 8 の出力をそれぞれ比較し、アンバランスレベルの設定値を超えた時に1を出力するする複数のアンバランス比較器 1 9 と、総過電流比較器 8 の出力と各アンバランス比較器 1 9 の出力の内、いずれかが1を出力した時に1を出力する論理和素子 1 4 と、論理和素子 1 4 の反転出力とチョッパ素子用ゲート信号生成回路の 9 出力の論理積から各チョッパ素子 3 の点弧、消弧を制御する論理積素子 1 0 とを備えたものである。

#### [0022]

以上述べた実施形態 3 において、チョッパ回路毎に設置されたホール電流検出器 2 及び電流検出回路 5 と、加算器 6 の組み合わせにより出力される電力変換回路の総電流値と、ホール電流検出器 2 と、電流検出回路 5 と、総電流算出器 2 0 の組み合わせにより算出される総電流算出値の差が、減算器 1 6 により出力される。全波整流回路 1 8 により、減算器 1 6 の出力の絶対値が取られ、アンバランス比較により、アンバランスレベル設定器 1 7 の値と比較され、アンバランスレベル上回ったときに1が出力される。アンバランス比較器 1 9 の出力と、総過電流比較器 8 の出力のいずれかが1になると論理和素子 1 4 から1が出力される。このとき、チョッパ素子用論理積素子 1 0 の出力が0となり、チョッパ素子3を停止させる信号が発信される。

## [0023]

この結果、実施形態 3 によれば、チョッパ回路が並列に構成された電力変換回路において、チョッパ回路毎の電流値から算出された総電流値とチョッパ回路毎の電流値の合計値を比較し、両者の差が大きいときにアンバランスを検出してチョッパ素子 3 のインタロックをかけることで、チョッパ回路間のアンバランスを防ぐことができる。

#### [0024]

図4は実施形態4を説明するための概略構成図であり、これは直流入力電源11の電圧を、直流リアクトル1とチョッパ素子3が直列接続されたチョッパ回路を複数個並列接続された電力変換回路により昇圧して電力母線に印加する電力変換装置において、以下のようになっている。

#### [0025]

図 1 と同様に各チョッパ素子 3 を点弧するゲート信号を発信する共通のチョッパ素子用ゲート信号生成回路 9 と、電力変換回路の出力を平滑化する共通のコンデンサ例えば電解コンデンサ 4 を備えている。

#### [0026]

これ以外は、図1とは異なる点で、1つのチョッパ素子3に流れる電流を検出する第1 のホール電流検出器2と、ホール電流検出器2の出力から一つのチョッパ回路の電流値を 検出する電流検出回路5と、直流入力電源11とチョッパ回路との接続部に流れる総電流 を検出する第2のホール電流検出器21と、ホール電流検出器21の出力から総電流値を 検出する総電流検出回路22と、総電流検出回路22で求めた総電流値の過電流レベルが 設定された総過電流レベル設定器7と、総電流検出回路22で求めた総電流値と総過電流 レベル設定器7で設定された電流設定値を比較し、総電流値が電流設定値を超えたときに 1を出力する総過電流比較器8と、総電流検出回路22で検出した総電流値をチョッパ回 路の並列数で除算することにより個別電流を算出する個別電流算出回路15と、個別電流 算出回路15の出力と電流検出回路5の出力の差を求める減算器16と、減算器16の出 力を絶対値にする全波整流回路18と、全波整流回路18の出力のアンバランスレベルを 設定するアンバランスレベル設定器17と、アンバランスレベル設定器17のアンバラン スレベルと全波整流回路18の出力とが比較され、全波整流回路18の出力がアンバラン スレベルの設定値を上回ったとき1が出力されるアンバランス比較器19と、総過電流比 較器8の出力とアンバランス比較器19の出力の内、いずれかが1を出力した時に1を出力 する論理和素子14と、論理和素子14の反転出力とチョッパ素子用ゲート信号生成回路

10

20

30

40

10

20

30

40

50

9の出力の論理積から前記各チョッパ素子の点弧、消弧を制御する論理積素子10とを備えたものである。

#### [0027]

以上述べた実施形態 4 において、電力変換回路全体の総電流を検出できる位置に設置されたホール電流検出器 2 1 と、総電流検出回路 2 2 と、総電流検出回路 2 2 の出力をチョッパ回路の並列数で除算することで個別電流を算出する個別電流算出回路器 1 5 の組み合わせにより算出された個別電流算出値と、任意のチョッパ回路に設置されたホール電流検出器 2 と、電流検出回路 5 の組み合わせにより検出された電流値の差が、減算器 1 6 により出力される。全波整流回路 1 8 により、減算器 1 6 の出力の絶対値が取られ、アンバランス比較器 1 9 により、アンバランスレベル設定器 1 7 の値と比較され、アンバランスレベルを上回ったときに1が出力される。アンバランス比較器 1 9 の出力と、総過電流比較器 8 の出力のいずれかが1になると論理和素子 1 4 から1が出力される。このとき、チョッパ素子用論理積素子 1 0 の出力が0となり、チョッパ素子 3 を停止させる信号が発信される。

#### [0028]

この結果、実施形態 4 によれば、並列に構成された電力変換回路において、並列に分岐する前のチョッパ回路に流れる総電流から算出されたチョッパ回路毎の電流値と任意のチョッパ回路の電流実測値を比較し、両者の差が大きいときのアンバランスを検出してチョッパ素子のインタロックをかけることで、少数のホール電流検出器 2 、および、電流検出回路 5 にて並列回路間のアンバランスを防ぐことができる。

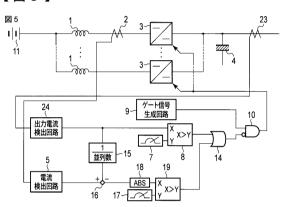

#### [0029]

図5は実施形態5を説明するための概略構成図であり、これは直流入力電源11の電圧を、直流リアクトル1とチョッパ素子3が直列接続されたチョッパ回路を複数個並列接続された電力変換回路により昇圧して電力母線に印加する電力変換装置において、以下のようになっている。

#### [0030]

図1と同様に各チョッパ素子3を点弧するゲート信号を発信する共通のチョッパ素子用ゲート信号生成回路9と、電力変換回路の出力を平滑化する共通のコンデンサ例えば電解コンデンサ4を備えている。

#### [0031]

これ以外は、図1とは異なる点で、1つのチョッパ素子3に流れる電流を検出する第1 のホール電流検出器2と、ホール電流検出器2の出力から一つのチョッパ回路の電流値を 検出する電流検出回路5と、電力変換回路と電力母線との接続部に流れる電流を検出する 第2のホール電流検出器23と、ホール電流検出器23の出力から出力電流値を検出する 出力電流検出回路24と、出力電流検出回路24で求めた出力電流値の過電流レベルが設 定された総過電流レベル設定器7と、出力電流検出回路24で求めた出力電流値と総過電 流レベル設定器7で設定された電流設定値を比較し、出力電流値が電流設定値を超えたと きに1を出力する総過電流比較器8と、出力電流検出回路24で検出した出力電流値をチ ョッパ回路の並列数で除算することにより個別電流を算出する個別電流算出回路15と、 個別電流算出回路15の出力と電流検出回路5の出力の差を求める減算器16と、減算器 1 6 の出力を絶対値にする全波整流回路 1 8 と、全波整流回路 1 8 の出力のアンバランス レベルを設定するアンバランスレベル設定器17と、アンバランスレベル設定器17のア ンバランスレベルと全波整流回路18の出力とが比較され、全波整流回路18の出力がア ンバランスレベルの設定値を上回ったとき1が出力されるアンバランス比較器19と、総 過電流比較器8の出力とアンバランス比較器19の出力の内、いずれかが1を出力した時 に1を出力する論理和素子14と、論理和素子14の反転出力とチョッパ素子用ゲート信 号生成回路9の出力の論理積から各チョッパ素子3の点弧、消弧を制御する論理積素子1 0とを備えたものである。

#### [0032]

以上述べた実施形態5において、電力変換回路の出力側に設置されたホール電流検出器

23と、出力電流検出回路24と、個別電流算出回路15の組み合わせにより算出された個別電流算出値と、任意の並列回路に設置されたホール電流検出器2と、電流検出回路5の組み合わせにより検出された電流値の差が、減算器16により出力される。全波整流回路18により、減算器16の出力の絶対値が取られ、アンバランス比較器19により、アンバランスレベル設定器17の値と比較され、アンバランスレベルを上回ったときに1が出力される。アンバランス比較器19の出力と、総過電流比較器8の出力のいずれかが1になると論理和素子14から1が出力される。このとき、チョッパ素子用論理積素子10の出力が0となり、チョッパ素子3を停止させる信号が発信される。

#### [0033]

この結果、実施形態 5 によれば、チョッパ回路が並列に構成された電力変換回路において、出力側に流れる電流から算出された並列回路毎の電流値と任意の並列回路の電流実測値を比較し、両者の差が大きいときにアンバランスを検出してチョッパ素子のインタロックをかけることで、少数のホール電流検出器、および、電流検出回路にて並列回路間のアンバランスを防ぐことができる。

#### 【符号の説明】

# [0034]

1…直流リアクトル、2…ホール電流検出器、3…チョッパ素子、4…電解コンデンサ、5…電流検出回路、6…加算器、7…総過電流レベル設定器、8…総過電流比較器、9…チョッパ素子用ゲート信号生成回路、10…チョッパ素子用論理積素子、11…直流入力電源、12…個別過電流レベル設定器、13…個別過電流比較器、14…論理和素子、15…個別電流算出回路、16…減算器、17…アンバランスレベル設定器、18…全波整流回路、19…アンバランス比較器、20…総電流算出器、21…ホール電流検出器、24…出力電流検出回路。

# 【図1】

図 1

# 【図2】

10

# 【図3】

# 【図4】

# 【図5】

# フロントページの続き

(56)参考文献 特開2006-271069(JP,A)

特開2013-059228(JP,A)

特開2003-284333(JP,A)

特開2012-016230(JP,A)

特開平08-084465(JP,A)

(58)調査した分野(Int.CI., DB名)

H02M3/00-3/44