# (19) 대한민국특허청(KR)

## (12) 등록특허공보(B1)

(51) Int. Cl.

H01L 29/786 (2006.01) G02F 1/136 (2006.01)

(21) 출원번호 10-2009-7014698(분할)

(22) 출원일자(국제출원일자) **2002년03월21일** 심사청구일자 **2009년07월14일**

(85) 번역문제출일자 2009년07월14일

(65) 공개번호 10-2009-0089475

(43) 공개일자 2009년08월21일

(62) 원출원 **특허 10-2002-7015659** 원출원일자(국제출원일자) **2002년03월21일** 심사청구일자 **2007년03월20일**

(86) 국제출원번호 PCT/IB2002/000945

(87) 국제공개번호 **WO 2002/78094** 국제공개일자 **2002년10월03일**

(30) 우선권주장

0107410.3 2001년03월23일 영국(GB)

(56) 선행기술조사문헌 JP06333941 A\*

JP09148266 A\*

\*는 심사관에 의하여 인용된 문헌

(45) 공고일자 2010년07월16일

(11) 등록번호 10-0970217

(24) 등록일자 2010년07월07일

(73) 특허권자

### 치메이 이노럭스 코포레이션

중화민국 타이완 미아오리 카운티 350 주난 신추 사이언스 파크 주난 사이트 케슈 로드 넘버 160

(72) 발명자

### 롤핑, 프랑크, 베.

네델란드, 아아 아인드호펜 5656, 프로프. 홀스트 란 6

(74) 대리인 **문경진**

전체 청구항 수 : 총 6 항

심사관 : 김태훈

### (54) 전자 디바이스를 제조하는 방법

#### (57) 요 약

본 발명은 능동-메트릭스 액정 디스플레이 또는 다른 큰 영역 전자 디바이스에서의 사용을 위한 유리 또는 절연중합체 기판 같은 기판(4)상의 박막 트랜지스터(TFT)의 제조에 관한 것이다. TFT 를 형성하는 방법은 반도체 막(2)상에 마스크 층(8)을 증착하는 단계 및 상기 마스크 층(8)의 일부를 제거하여 미리결정된 크기와 분포를 가지는, 그 층을 관통하는 다수의 구멍을 형성하는 단계를 포함한다. 마스크 층(8)의 구멍이 뚫린 부분(26,28)은 도펀트 주입 단계동안 반도체 막(2)의 일부를 마스킹하여 소스 및 드레인 영역(16,18)의 한정과 동시에 전계 경감영역(20,22)을 형성하는 기능을 한다.

#### 대 표 도 - 도1c

## (81) 지정국

CN, JP, KR, EP(AT, BE, CH, LI, DE, DK, ES, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE, FI, CY),

### 특허청구의 범위

#### 청구항 1

박막 트랜지스터를 포함하는 전자 디바이스를 제조하는 방법으로서,

- (a) 절연 기판 상에 반도체 막을 형성하는 단계;

- (b) 상기 반도체 막 상에 게이트 절연층을 형성하는 제 1 마스크 층을 증착하고, <u>상기 제 1 마스크 층 상에, 다</u>이블록 공중합 막에 주기적으로 배치된 나노 입자를 포함하는 교질 막을 증착하는 단계와;

- (c) <u>상기 제 1 마스크 층에</u> 제 1 패턴으로 <u>나노 구멍을 형성하기 위해 아르곤 빔을 사용하여 상기 교질 막</u>을 <u>스</u> 퍼터 에칭하는 단계;

- (d) 상기 <u>교질 막</u>상에 <u>게이트 전극층을 형성하는</u> 제 2 마스크 층을 증착하는 단계;

- (e) 상기 제 2 마스크 층을 패터닝하여 상기 제 1 패턴의 영역 내에 존재하는 제 2 패턴을 한정하는 단계;

- (f) 적어도 상기 제 1 마스크 층을 주입 마스크로 사용하여 상기 반도체 막에 이온을 주입하되, 상기 구멍의 적어도 일부를 한정하는 상기 제 1 마스크 층의 일부로 주입을 부분적으로 마스킹하여, 소스 영역과 드레인 영역, 상기 소스 영역과 드레인 영역 사이에 소스 영역과 드레인 영역 사이에 상기 드레인 영역보다 낮은 도핑 농도를 가지는 전계-경감 영역(field-relief region)을 한정하는 단계

를 포함하는, 전자 디바이스를 제조하는 방법.

#### 청구항 2

제 1 항에 있어서, 상기 단계 (b)는,

상기 반도체 막상에 이격되고 상승된(raised) 특징부의 배열을 제공하는 단계;

그 위에 상기 제 1 마스크 층을 증착시키는 단계; 및

상기 상승된 특징부 상에 존재하는 상기 제 1 마스크 층 물질의 일부와 함께 상기 상승된 특징부를 제거하는 단계

를 포함하는, 전자 디바이스를 제조하는 방법.

#### 청구항 3

삭제

### 청구항 4

제 1 항에 있어서, 상기 제 1 마스크 층에 구멍을 에칭하는 단계는 상기 단계 (e) 이후에 수행되어서, 상기 구멍이 상기 제 1 마스크 층의 노출된 영역을 통해 형성되는, 전자 디바이스를 제조하는 방법.

### 청구항 5

제 1 항에 있어서, 상기 단계 (d)는 상기 단계 (c) 이전에 수행되고, 상기 방법은, 상기 단계 (d) 이후와 상기 단계 (c) 이전에 상기 제 2 마스크 층을 패터닝하여 상기 단계 (c)에서의 제 1 마스크 층의 패터닝을 위한 제 1 패턴으로 마스크를 형성하는 단계 (h)를 추가적으로 포함하는, 전자 디바이스를 제조하는 방법.

#### 청구항 6

제 5 항에 있어서, 상기 단계 (h)는,

상기 제 2 마스크 층에 제 2 패턴을 한정하는 단계; 및

그후 상기 제 2 마스크 층에 인접한 측벽 스페이서(spacer)를 형성하여 상기 제 1 패턴을 한정하는 단계를 포함하는, 전자 디바이스를 제조하는 방법.

### 청구항 7

제 1 항에 있어서, 상기 단계 (e)는,

상기 제 2 마스크 층 상에 제 3 마스크 층의 제 2 패턴을 한정하는 단계;

상기 제 2 마스크 층의 노출된 부분을 산화시키는 단계; 및

그 후 상기 제 2 마스크 층의 산화된 부분을 제거하여 상기 제 2 마스크 층에 제 2 패턴을 한정하는 단계를 포함하는, 전자 디바이스를 제조하는 방법.

### 청구항 8

삭제

#### 청구항 9

삭제

### 명세서

### 발명의 상세한 설명

## 기술분야

[0001] 본 발명은 예를 들면 유리 또는 절연 중합체 기판 같은 기판 상에 박막 트랜지스터(이하 TFT)를 포함하는 전자 디바이스에 관한 것이다. 이러한 디바이스에는 예를 들면 능동-메트릭스 액정 디스플레이 또는 다른 평면 패널 디스플레이, 또는 매트릭스내에 그리고 예를 들면 박막 데이터 저장소 또는 이미지 센서 같은 구동회로내에 TFT 를 가지는 임의의 다른 유형의 큰 영역 전자 디바이스같은 것이 있다. 또한 본 발명은 이러한 전자 디바이스를 제조하는 방법에 관한 것이다.

#### 배경기술

- [0002] 수년 동안 큰 영역 전자공학 응용에 있어서, 유리 및/또는 다른 저렴한 절연 기판상에 TFT를 가지는 박막 회로를 발전시키는 데에 많은 관심이 있어왔다. 비결정 또는 다결정 반도체 막으로 제조된 그러한 TFT는 예를 들면 미국 특허 출원 제 5,130,829 호 (코닌클리케 필립스 일렉트로닉스사 관리번호:PHB 33646)에 기술된 것과 같은 평면 패널 디스플레이내의 셀 메트릭스의 스위칭 소자를 형성할 수 있다. 좀더 최근의 연구는 예를 들면 그러한 셀 메트릭스를 위한 집적 구동 회로로서 TFT 로 인한 회로의 제조 및 집적(흔히 다결정 실리콘을 이용하는)을 포함한다. 따라서, 예를 들면 공개된 유럽 특허 출원 제 0 629 003 호(코닌클리케 필립스 일렉트로닉스사 관리번호:PHB 33845)는 그러한 전자 디바이스를 기술하는데, 이 전자 디바이스는 박막 스위칭 트랜지스터의 스위칭 메트릭스 및 이 메트릭스 외부에 위치한 주변 구동 회로를 기판상에 포함하고, 이러한 메트릭스의 스위칭 TFT에 연결된 박막 회로 트랜지스터를 포함한다. 미국 특허 출원 제 5,130,829 호 및 유럽 특허 출원 제 0 629 003 호는 여기서 본 명세서에 참고 문헌으로 병합되었다.

- [0003] 불행하게도, 그러한 TFT, 특히 저온 공정을 사용하여 형성된 다결정 실리콘으로 제조된 TFT의 트랜지스터 특성에서는 바람직하지 않은 전계-유도 효과가 발생한다. 예를 들면 온-전류 손실, 다결정 실리콘내의 바이어스-유도 상태 생성, 및 핫 캐리어(hot carrier) 유도 상태 생성 및 캐리어 트래핑(trapping) 같은 몇 불안정성 메커니즘이 발생한다. 발생하는 또다른 효과는 드레인 전계-향상된 누설 전류의 증가이다. 트랜지스터 특성(예를 들면 오프-상태 누설 전류, 임계 전압 및 온-상태 전류)의 열화는 그러한 회로내의 TFT 의 사용을 매우 제한한다.

- [0004] TFT 에서의 그러한 영향을 감소시키는 한가지 방법은 드레인 영역보다 더 낮은 도핑 농도를 가지는 전계-경감 영역에 의하는 것이다. TFT는 소스와 드레인 영역 사이에 반도체 막에서의 전도 채널을 제어하기 위해 결정 반도체 막에 인접한 절연된 게이트를 포함한다. 전계 경감 영역은 TFT의 전도 채널 및 드레인 영역 사이에 존재한다. 그것은 게이트의 측면에 위치하거나, 게이트와 완전히 또는 부분적으로 겹쳐질 수도 있다.

- [0005] 종래의 전계-경감 구조의 문제점은 추가적으로 저-도우즈(dose) 주입 단계를 필요로 한다는 것이다. 고-도우즈 주입은 소스 및 드레인의 형성에 필요한 반면, 저-도우즈 주입은 전계-경감 영역에 필요하다. 전계-경감 영역의 도입이 TFT 성능을 상당히 개선시킨다 하더라도, 추가적인 주입 단계는 TFT 생산 공정을 복잡하게 한다. TFT 제조 공정을 간략화하기 위해서는 소스, 드레인 및 전계-경감 영역을 단일한 주입 단계로 제조하는 것이 바람직하

고, 이렇게함으로써 생산 단가를 감소시키고 단위시간당 처리량 및 수율을 개선시킨다. 이러한 문제점은 TFT 제조 방법에 대해 기술된 일본 특허 명세서 제 9,148,266 호에서 다루어지며, 여기서는 게이트 전극의 에지가 산화되어서 다공성의(porpous) 막을 형성한다. 다공성의 막은 마스크로 사용되어 활성층 내에 주입된 불순물 이온의 양을 감소시키고 그럼으로써 소스 및 드레인에 인접한 전계-경감 영역을 형성한다.

### 발명의 내용

## 해결 하고자하는 과제

본 발명의 목적은 단일한 주입 단계에서 전계 경감 영역을 한정하는 개선된 방법을 제공하는 것이다.

#### 과제 해결수단

[0007] 본 발명은 이하의 단계:

[0006]

- [0008] (a) 절연 기판상에 반도체 막을 형성하는 단계;

- [0009] (b) 반도체 막상에 제 1 마스크 층을 증착하고, 그 일부를 제거하여 상기 층의 상부 표면으로부터 하부 표면까지 실질적으로 수직인 다수개의 구멍을 형성하는 단계;

- [0010] (c) 제 1 패턴으로 제 1 마스크 층을 패터닝하는 단계;

- [0011] (d) 제 1 마스크 층상에 제 2 마스크 층을 증착하는 단계;

- [0012] (e) 제 2 마스크 층을 패터닝하여 제 1 패턴의 영역내에 존재하는 제 2 패턴을 한정하는 단계; 및

- [0013] (f) 반도체 막을 주입시키는 단계로서, 적어도 몇개의 구멍을 한정하는 제 1 마스크 층의 일부가 부분적으로 이러한 주입을 마스킹하도록, 적어도 제 1 마스크 층을 주입 마스크로 사용하여 반도체 막을 주입시킴으로서, 이러한 주입 단계가 소스 및 드레인 영역, 소스 및 드레인 영역 사이의 도핑되지 않은 전도 채널, 및 이러한 전도 채널 및 드레인 영역사이에 드레인 영역보다 낮은 도핑 농도를 가지는 전계-경감 영역을 한정하는, 반도체 막을 주입시키는 단계를 포함하는, 박막 트랜지스터를 포함하는 전자 디바이스를 제조하는 방법을 제공한다.

#### 直과

- [0014] 따라서, 소스, 드레인, 및 전계-경감 영역의 결합된 주입은 전계-경감 영역의 한정을 위한 마스크 층 또는 형판 (template)의 사용으로 달성되고, 이것은 형판이 없는 소스 및 드레인 영역에 비해 제어된 형식으로 주입 도우 즈를 감소시킨다.

- [0015] 제 1 마스크 층은 층 아래로 도달하는 많은 수의 수직 구멍을 한정하고, 이 구멍을 통해 도펀트가 주입된다. 구멍으로 덮힌 형판 영역 부분은 이러한 형판에 의해 한정된 영역에서의 유효 도펀트 농도를 결정한다. 구멍 수의증가 및 구멍 크기의 감소는 전계-경감 영역에서의 준-동질(quasi-homogeneous) 도핑 프로파일을 생성할 것이고, 그 영역에서의 도핑 균일도는 후속하는 도펀트 활성화 및 레이저를 사용하여 용해 실리콘내의 도펀트를 옆으로 확산시키는 확산 공정의 결합으로 추가적으로 개선될 수 있다. 그러므로 이러한 도핑 도우즈 및 분포는적절한 농도 및 구멍의 크기를 선택함으로써 제어가능한 방식으로 쉽게 지시될 수 있다. 이것을 용이하게 하는 기술은 이하에서 논의된다.

- [0016] 위에서 언급된 일본 특허 명세서 제 9,148,266 호에 개시된 접근방식으로, 전계 경감 영역의 도펀트 농도는 오직 산화층의 두께를 변화시킴으로써 소스 및 드레인 영역의 도펀트 농도에 비해 조절될 수 있다.

- [0017] 구멍의 수 및 크기에 따라, 형판내의 구멍은 예를 들면 리쏘그래피(lithography) 또는 마이크로미터가 아니라 나노미터 정도의 크기를 가지는 형상을 한정하는 기술인 "나노 기술" 을 사용하여 준비될 수 있다.

- [0018] 반도체 막상에 다수의 구멍을 가지는 제 1 마스크 층을 형성하는 단계인 단계(b)는, 반도체 막상에 이격되고 상 승된(raised) 특징부의 배열을 제공하는 단계, 그 위에 제 1 마스크 층을 증착시키는 단계, 및 상기 상승된 특징부상에 존재하는 제 1 마스크 층 물질의 일부와 함께 상기 상승된 특징부를 제거하는 단계를 포함한다. 대안 적으로, 단계(b)는 상기 반도체 막상에 제 1 마스크 층을 증착시키는 단계, 상기 제 1 마스크 층에 에칭액 마스크(etchant mask)를 한정하는 단계, 및 상기 제 1 마스크 층의 물질을 통해 다수의 구멍을 에칭하는 단계를 포함한다.

- [0019] 제 1 패턴으로 제 1 마스크 층을 패터닝하는 단계(c)는, 제 1 마스크 층에 구멍을 에칭하는 단계 이전에 수행된

다.

- [0020] 본 방법의 바람직한 실시예에서, 제 1 마스크 층에 구멍을 형성하는 단계는 단계(e)이후에 수행되어, 이러한 구멍은 제 1 마스크 층의 노출된 영역을 통해 형성된다.

- [0021] 제 1 및 제 2 마스크 층의 패터닝은 여러 방식으로 수행될 수 있다. 바람직한 공정에서, 단계(d)는 단계(c) 이전에 수행되고, 본 방법은 단계(d) 이후 단계(c) 이전에 제 2 마스크 층을 패터닝하여 단계(c)에서 제 1 마스크 층을 패터닝하기 위한 제 1 패턴으로 마스크를 형성하는 추가적인 단계(h)를 포함한다. 좀 더 상세하게, 단계(h)는 제 2 마스크 층에 제 2 패턴을 한정하는 단계 및 제 2 마스크 층에 인접한 측벽 스페이서를 형성하여 제 1 패턴을 한정하는 단계를 포함한다.

- [0022] 제 2 층을 패터닝하는 단계(e)는, 제 2 마스크 충상에 제 3 마스크 충에서의 제 2 패턴을 한정하는 단계, 제 2 마스크 충의 노출된 부분을 산화시키는 단계, 및 그 후 제 2 마스크 충의 산화된 부분을 제거하고 그럼으로써 제 2 마스크 층에 제 2 패턴을 한정하는 단계를 포함한다.

- [0023] 이러한 산화 기술 또는 스페이서의 사용은 상대적으로 좁은 전계 경감 영역의 형성을 가능하게 하고, 이와 관련된 기생 커페시턴스 및 직렬 저항을 감소시킨다.

- [0024] 바람직하게, 제 1 마스크 층은 게이트 전극 층을 형성할 수 있고, 본 방법은 단계(a) 이후 단계(b) 이전에 게이트 절연 층을 증착시키는 단계를 포함한다. 이것은 완전히 자기-정렬(self-aligned)되고, 게이트-겹쳐진 조금-도핑된-드레인(FSA GOLDD) 디바이스 구조를 가능하게 한다.

- [0025] 대안적으로, 제 1 마스크 층은 게이트 절연층을 형성하고, 제 2 마스크 층은 게이트 전극층을 형성한다.

- [0026] 또다른 양상에 따라, 본 발명은, 절연 기판상의 패턴닝된 반도체 막, 상기 반도체 막상에 게이트 절연층, 및 상기 게이트 절연층상에 게이트 전극을 포함하는 박막 트랜지스터를 포함하는 전자 디바이스로서, 상기 반도체 막은 소스 및 드레인 영역, 상기 소스 영역과 드레인 영역사이의 도핑되지 않은 전도 채널, 및 상기 전도 채널과 상기 드레인 영역 사이에 상기 드레인 영역보다 낮은 도핑 농도를 가지는 전계-경감 영역을 포함하고, 상기 게이트 전극의 일부는, 상기 전계-경감 영역와 겹치고, 그를 통해 한정된, 그 상부 표면으로부터 하부 표면으로 실질적으로 수직으로 연장하는 다수개의 구멍을 가지는, 전자 디바이스를 제공한다.

- [0027] 또 다른 양상에 따라, 본 발명은, 절연 기판상의 패턴닝된 반도체 막, 상기 반도체 막상에 게이트 절연층, 및 상기 게이트 절연층상에 게이트 전국을 포함하는 박막 트랜지스터를 포함하는 전자 디바이스로서, 상기 반도체 막은 소스 및 드레인 영역, 상기 소스 영역과 드레인 영역사이의 도핑되지 않은 전도 채널, 및 상기 전도 채널 과 상기 드레인 영역 사이에 상기 드레인 영역보다 낮은 도핑 농도를 가지는 전계-경감 영역을 포함하고, 상기 게이트 절연층의 일부는, 상기 전계-경감 영역과 겹치고, 그를 통해 한정된, 그 상부 표면으로부터 하부 표면까지 실질적으로 수직으로 연장하는 다수개의 구멍을 가지고, 상기 게이트 전국은 상기 전도 채널과 자기-정렬되는, 전자 디바이스를 제공한다.

- [0028] 바람직하게, 전계-경감 영역의 길이는 1/cm 이하이다. 예를 들면 스페이서 기술의 사용에 의해, 패터닝된 마스크 층의 산화 또는 패터닝된 마스크 층의 과-에칭(overetching)은 1/cm 보다 매우 작은 길이를 가지는 비교적 좁은 전계 경감 영역의 형성을 가능하게 한다.

- [0029] 제 1 마스크 층의 구멍은 TFT 의 안정도를 최적화시키기 위해 기저층의 1% 내지 10% 정도를 노출시킨다. 평균 구멍 직경은 100nm 이하인 것이 바람직하다.

- [0030] TFT 제조에 사용되는 층 한정 및 주입 방법은 공지된 기술 및 공정 단계를 채택하고, 이는 당업자에게 널리 알려져 있다. 소스 및 드레인 영역 및 전계 경감 영역은 반도체 막에 존재하는 하나의 전도 유형의 도핑된 영역일수 있고/있거나, 그들은 상기 반도체 막에 인접한 하나이상의 추가적인 반도체 막의 도핑된 영역일수 있다. 제이트-정렬된 공정이 기생 효과를 감소시키기 위해 사용될수 있다. 따라서, 예를 들면 회로 TFT의 적어도 일부는 게이트와 실질적으로 전부 겹치는 그 전계 경감 영역을 가질수 있고, 이러한 TFT의 게이트 및/또는 다른 회로 TFT는, 실질적으로 드레인 영역의 에지에 정렬된 에지를 가질수 있다.

- [0031] 본 발명의 실시예는 이하 첨부 도면을 참조하여 예를 들어 설명될 것이다.

- [0032] 도면은 개략적이고 축적에 맞게 도시되지는 않았음을 유의하여야 한다. 이러한 도면들의 부분의 상대적인 크기 및 비례는 도면 작성의 편의 및 명료함을 위해 과장되거나 줄여서 도시되었다.

## 발명의 실시를 위한 구체적인 내용

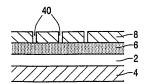

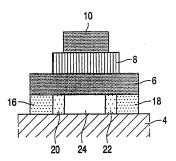

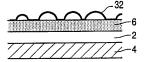

- [0033] 도 <u>la-lc</u> 은 전계 경감을 가지는 자기-정렬된(SA) TFT 구조 분야의 제조에 적절한 공정을 도시하고, 여기서 전계-경감 영역의 주입을 위한 마스크 층은 게이트의 한정 이전에 형성된다.

- [0034] 도 1a 에 도시된 구조는 이하와 같이 형성된다. 우선, 반도체 막(2)이 기판(4)상에 증착된다. 예를 들면 비결정실리콘이 증착되고 그 후 전형적으로 레이저 같은 에너지 빔에 의한 조사(irradiation)에 의해 결정화된다. 이러한 층은 약 40nm의 두께를 가진다. 게이트 절연층(6)(예를 들면 실리콘 이산화물)이 그 후 증착되고, 그 후 제 1 마스크 층을 구성하는 절연층(8)이 뒤따른다. 이 층은 그를 관통하는 다수의 구멍을 가지고, 이러한 구멍의 형성은 이하에 논의된다. 그 후 전형적으로 알루미늄-티타늄 합금으로 형성된 게이트 전극 층(10)이 증착되고, 패터닝되고(제 2 마스크 층을 형성), 예를 들면 실리콘 산화물 또는 질소화물로 이루어진 스페이서(12,14)가 그 게이트 전극층(10)의 각 에지를 따라 형성된다.

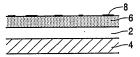

- [0035] 도 1b 에 도시된 바와 같이, 그 후 절연층(8)이 패터닝된 게이트 전극 층(10)과 스페이서(12,14)의 결합을 마스크로 사용하여 에칭된다.

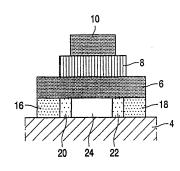

- [0036] 그 후 스페이서는 제거되고, 반도체 막(2)의 주입이 수행되어, 구멍 뚫린 절연층(8)의 노출된 부분은 제 1 의, 부분적인 마스크를 구성하고, 게이트 층(10)은 제 2 마스크로 기능한다. 이에 의해 소스(16), 드레인(18), 전계 경감 영역(20,22) 및 반도체 막(2)내의 전도 채널(24)이 한정된다.

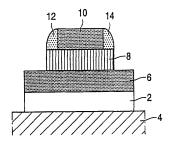

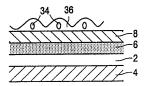

- [0037] 도 <u>2a-2b</u> 는 게이트 한정 후 구멍이 절연층(8)으로 인입되는 전계 경감 영역을 가지는 SA TFT 를 생산하기 위한 접근법을 도시한다. 도 2b 에 도시된 바와 같이, 그 후 구멍은 층(8)의 노출된 부분(26 및 28)에 제한된다. 도 <u>2a-2b</u> 에 도시된 공정 흐름에 대안적으로, 게이트 층(10)의 한정 직 후 구멍이 절연층(8)으로 인입되고, 그 후 스페이서(12,14)의 제조, 절연층(8)의 에칭, 스페이서의 제거, 및 이온의 주입 단계가 뒤따른다.

- [0038] 도 1a-1c 및 2a-2b와 관련하여 전술한 공정은 완전히 자기-정렬되고, 조금-도핑된-드레인 (FSA LDD) 디바이스를 야기한다. 층(6 및 8)은 함께 게이트 유전층을 형성한다. 이 경우, 층(6)이 생략되어, 층(8)이 단독으로 게이트 유전층을 형성하는 것도 가능함을 이해하여야 한다. 대안적으로, 도 1a-1c 및 2a-2b에서, 층(8)(제 1 마스크 층을 나타냄)은 전도성 물질로 이루어져 게이트를 형성하고, 층(10)은 절연 물질(제 2 마스크 층을 형성함) 또는 다른 적절한 마스크 물질로 이루어질 수 있다. 이것은 완전히 자기-정렬된, 게이트-겹쳐진 조금-도핑된-드레인 (FSA GOLDD) 디바이스를 제공한다는 것을 알 수 있다. 그러한 공정에서, 층(8)은 단독으로 주입 마스크를 형성할 수 있다. 이 경우에, 층(10)은 도펀트 주입 단계 이전에 제거될 수 있다. 여하튼, 층(8)이 게이트 층을 형성하는 경우에는, 층(10)은 완제된 디바이스로부터 생략될 수 있다.

- [0039] 전형적으로, 소스 및 드레인 영역(16 및 18)에서의 도핑 레벨은 예를 들면  $10^{15} \,\mathrm{cm}^{-2}$  이상이다. 전계 경감 영역 (20 및 22)의 도핑 레벨은  $10^{13} \,\mathrm{cm}^{-2}$  정도이다.

- [0040] 게이트-오프셋 TFT 및 게이트-겹침 TFT 양쪽 모두에 대한 전계 경감 영역(20 및 22)의 최적 길이는, 채널 영역 (24)의 길이, 게이트 및 최대 드레인 동작 전압, 및 TFT를 통하는 전류 레벨에 특히 의존한다. 전형적인 예에서, 그 채널 영역(24)에 대해서 5½m 내지 10½m 정도의 길이를 가지는 TFT 에서, 전계 경감 영역(20 및 22)의 길이는 1½m(마이크로미터) 내지 3½m 정도이다. 완전히 자기-정렬된 실시예의 사용으로, 본 발명은 그 길이가 1½m보다 훨씬 작은, 비교적 좁은 LDD 영역을 제공한다.

- [0041] 여전히 전계 경감 영역을 가지는 FSA 디바이스를 생성하는 한, 전술한 공정은 여러 방식으로 수정될 수 있다는 것을 이해하여야 한다. 예를 들면, LDD 또는 GOLDD 영역을 한정하는데 스페이서를 사용하는 대신에, 이 영역은 충(10)의 양국 산화(anodic oxidation) 또는 과-에칭에 의해 한정될 수 있고, 그 후 충(8)으로의 구멍의 인입 및 도펀트 주입 단계가 뒤따를 수 있다. SA LDD 및 SA GOLDD 디바이스는 또한 2개의 별도의 마스크를 사용하여 충(8 및 10)을 한정하는 공정으로도 형성될 수 있다.

- [0042] 반도체 막(2)내의 도펀트의 균일도는 충(8)에서의 구멍의 수와 크기에 의존한다. 구멍 수의 증가 및 구멍크기의 감소는 전계 경감 영역에서 준-동질(quasi-homogeneous) 도핑 프로파일을 생성한다. 만약 필요하다면, 도펀트 활성화 및, 레이저 같은 에너지 빔을 사용하여 반도체 물질내의 도펀트를 옆으로 확산시키는, 확산 공정의 결합으로 도펀트의 균일도는 개선될 수 있다.

- [0043] GOLDD 디바이스가 양호한 안정도를 보여주기 위해서, GOLDD 영역에서의 주입 도우즈(dose)는 소스 및 드레인 영역에 대한 것보다 한 차수 이상 더 낮은 크기를 가지는 것이 바람직하다. 그러므로, 구멍으로 덮힌 충(8)의 부

분은 10% 이하이어야 한다. GOLDD 실시예에서, 충(8)은 게이트 전극을 형성한다. 충내에 아무 구멍이 없을 때에 비해 게이트 전극에 구멍이 있을 때는, 게이트 전계가 감소된다. 그러나, 만약 구멍으로 덮힌 영역이 10% 이하라면, 그러한 전계 감소는 무시할 수 있다.

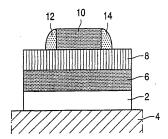

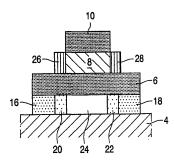

- [0044] 구멍의 형성에 사용되는 적절한 기술이 이하 설명될 것이다. 이러한 공정은 이격되고 상승된 특징부의 배열을 반도체 막상에 제공하는 단계, 그 위에 제 1 마스크 층을 증착하는 단계, 및 상기 상승된 특징부 위에 존재하는 제 1 마스크 층 물질 부분과 함께 상기 상승된 특징부를 제거하는 단계를 포함한다. 그러한 기술중 하나는 게이 트 유전체의 상단에 자기-조립된 나노-아일랜드 배열(self-assembled array of nano-island)을 전개시키는 것 을 포함한다. 츄치야(S.Tsuchiva), 그린(M.Green) 및 심(R.R.A. Syms)에 의한 논문 "탄화 플루오르 반응성 이 온 에칭 플라즈마에서 세슘 염화물 아일랜드 배열을 레지스트로 사용한 구조적 제조(Structual fabrication using cesium chloride island array as resist in a fluorocarbon reactive ion etching plasma -Elctrochemical and Solid-state Letters 3, 44-46, 2000년)"과 그린(M.Green) 및 츄치야(T.J.Tsuchiya)에 의 한 논문 "구조적 제조에서 레지스트로서의 사용을 위한 메조스코픽 반구 배열(Mesoscopic hemisphere arrays for use as resist in structure fabrication - Vac. Sci. and Tech. B17. 2074-2083, 1999년)"은 세슘 염화 물의 반구 아일랜드 배열의 사용을 설명한다. 이러한 공정은 도 3 에 도시된다. 도 3a 에 도시된 아일랜드(30) 는, 열적 증발을 통해 실리콘 산화층(6)상에 세슘 염화물 박막을 증착시키고, 그 후 수증기에 상기 세슘 염화물 을 노출시킴으로써 형성된다. 수증기 존재하에서의 막 파괴(break-up) 및 아일랜드의 형성은 표면 자유 에너지 를 최소화시키는 요구에 따라 유도된다. 이 후 도 3b 에 도시된 바와 같이 자기-조립된 구조상에 게이트 금속층 (32)을 증착시키는 단계가 뒤따른다. 예를 들면 초음파 진동에 의해 레지스트(resist) 아일랜드를 코팅한 금속 막이 제거될 수 있어서, 구멍을 포함하는 게이트 전극(8)이 형성된다(도 3c).

- [0045] 실리콘 아일랜드가 또한 나노-구조된 레지스트 마스크로 사용될 수 있다. 르그랑(B. Legrannd), 아가쉐(V. Agache), 니즈(J.P.Nys), 세네즈(V. Senez) 및 스티브나드(D. Stievenard)에 의한 논문 "열적 어닐링시에 절연 기판상의 실리콘에 실로콘 아일랜드의 형성{Formation of silicon island on a silicon on insulator substrate upon thermal annealing Appl.Phys. Lett., 76(22), 3271(2000)}" 에 이러한 속성에 대한 접근법 이 설명되어 있다. 이러한 기술은 실리콘 산화충상의 실리콘 박막을 섭씨 500도 내지 900도로 가열하는 단계를 포함한다. 아일랜드 형성은 Si/SiO<sub>2</sub> 시스템의 자유 에너지의 최소화의 결과로 믿어진다. 그 후 게이트 층이 아일랜드 상에 증착된다. 초음과 또는 에칭이 인가되어 게이트층의 위에 존재하는 부분과 함께 아일랜드를 제거하고, 게이트 층에는 구멍이 남게된다.

- [0046] 하기노야(C.Haginoya), 이시바시(M.Ishibashi) 및 코이케(K.Koike)에 의한 "크기-제어가능한 자연적인 리쏘그래 피를 사용한 나노구조 배열 제조{Nanostructure array fabrication with a size-controllable natural lithography Appl.Phys. Lett., 71(20), 2934(1999)}" 는 그 직경이 반응성 이온 에칭에 의해 제어가능한 방식으로 감소된 폴리스티렌 볼(ball)의 육변형 배열의 형성을 설명한다. 금속막이 이러한 배열의 상단에 증착되고, 그 후 이러한 금속-커버된 폴리스티렌 볼을 리프트-오프(lift-off)하여 구멍 배열을 가진 금속 막을 형성하는 단계가 뒤따른다.

- [0047] 광전자공학, 단일 전자공학 및 필드 에미터(field emmitter) 에서의 넓은 응용 분야에 기인하여, 넓은 영역에 걸쳐 실리콘 나노-기둥(nano-pillar)의 제조에 있어서 최근 급속한 진전이 있었다. 5nm 내지 수 마이크로미터의 직경 범위와 1/m의 기둥 높이가 보고되었다. 실리콘 나노-기둥은 나노-구멍의 정렬된 배열을 가진 금속막의 제조를 가능하게 하기 때문에, 실리콘 나노-기둥은 도 la-lc 에서의 TFT 공정 흐름에도 사용될 수 있다. 이것은 게이트 유전체 상단에 실리콘 필름을 증착시키는 것과 그것을 실리콘 나노-기둥 배열로 변형시키는 것을 포함한다. 그 후 게이트 금속이 증착되고, 그 후 건식 또는 습식 에칭에 의해 나노-기둥을 제거하는 것이 뒤따른다. 이로 인해 그 직경이 나노-기둥의 직경에 대응하는 게이트 금속내 구멍의 배열이 생성된다. 이것은 예를 들면, 그린(M.Green), 가르시아-파라조(M.Garcia-Parajo), 칼리크(F. Khaleque) 및 머레이(R.Murray)에 의한 ""자연적" 리쏘그래피를 사용하여 제조된 n+ 갈륨 아르세나이드 상에 제조된 양자 기둥 구조(Quantum pillar structure fabricated on n+ gallium arsenide fabricated using "natural" lithography Applied Physics Letters 63, 264-266, 1993년)" 에 개시되어 있다.

- [0048] 대안적으로, 구멍 형성 단계는 반도체 막 상에 제 1 마스크 층을 증착하고, 그 후 제 1 마스크 층의 물질을 통하는 다수의 구멍을 형성하는 단계를 포함한다. 예를 들면, 구멍은, 제 1 마스크 층상에 에칭액 마스크를 한정하고, 제 1 마스크 층을 통해 구멍을 에칭함으로써 형성된다.

- [0049] 예를 들면 스파츠(J.P.Spatz), 헤르초크(T.Herzog), 뫼스머(S.Moβmer), 찌만(P.Ziemann) 및 뮐러(M.Moller)에

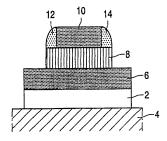

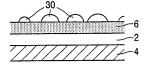

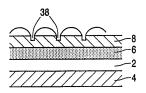

의한 논문 "교질 무기-중합체 하이브리드 시스템 - 나노리쏘그래피를 위한 툴{Micellar inorganic-polymer hybrid systems - a tool for nanolithography, Advanced Material 11(2), 149(1999)}"은 게이트를 위해 도핑된 반도체 물질의 사용을 필요로 하는 방법에 관한 것이다. 80nm 만큼 떨어진, 10 nm 직경의 구멍이 다이블록 공중합(diblock copolymer)된 모노-교질 막의 자기-조립된 마스크를 사용하여 GaAs (및 다른 반도체)로 인입되고, 그럼으로써 이러한 교질은 적절한 전이 금속 염으로 채워진다(loaded). 다이블록 공중합 마스크 요소 사이의 고 에칭-속도 콘트라스트는 구멍의 형성을 가능하게 한다. 이러한 공정은 도 4 에 도시된다. 도 4a 에 도시된 바와 같이, 다이블록 공중합 막(36)에 주기적으로 배치된 나노입자(34)를 포함하는 교질 막이 게이트 층(8)상에 중착된다. 나노입자는 금으로 형성되고, 예를 들면 폴리스티렌 다이블록 공중합체가 사용된다. 예를 들면 아르곤 빔을 사용하는 후속하는 스퍼터(sputter) 에칭은 오목부(38)를 형성하고, 결국 도 4b 및 4c 에 도시된 바와 같이 구멍(40)을 형성한다.

- [0050] 대안적으로, 라텍스 구(latex sphere)를 반응성 이온 에칭 레지스트로 사용하여, 균일한 라텍스 입자의 육변형 배열이, 도핑된 반도체 층상에 증착될 수 있고, 반도체에 육변형의 구멍 배열이 생성된다. 이 기술은 팡(H.Fang), 젤러(R.Zeller) 및 스타일스(P.J.Stiles)에 의한 논문 "GaAs/AlGaAs 헤테로구조에 있어서 준-제로-크기의 서브마이크론 점 어레이 및 커패시턴스 스펙트로스코피의 제조{Fabrication of quasi-zero-dimensional submicron dot array and capacitance spectroscopy in a GaAs/AlGaAs heterostructure Applied Physics Letters, 55(14), 1433(1989)}" 에 개시되어 있다.

- [0051] 나노-구멍을 그 내부에 가지는 게이트 전극을 형성하는데 사용되는 추가적인 기술은, 시거(K.Seeger), 팔머 (R.E.Palmer)에 의한 논문 "거친 금속막을 플라즈마 에칭 마스크로 사용한 실리콘 콘 및 기둥의 제조 {Fabrication of silicon cones and pillars using rough metal films as plasma etching masks Applied Physics Letters, 74(11), 1627(1999)}" 에 설명되어 있다. 은 막이 스퍼터 코팅을 통해 증착될 때, 막은 층마다 형성되는 방식으로가 아니라 3차원 은 클러스터(약 20 내지40 nm)의 형태로 생장한다. 그 에칭후에 뒤따르는은 클러스터 막의 스퍼터링은 나노-구조된 구멍을 가진 은 막의 형성을 가능하게 하고, 이것은 게이트 물질로 사용될 수 있다.

- [0052] 위에서 언급된 논문들의 모든 내용은 본 명세서에 참고 문헌으로 병합된다.

- [0053] 본 개시물을 읽음으로서, 다른 변형 및 수정도 당업자에에 명백할 것이다. 그러한 변형 및 수정은 등가물 및 다른 특성을 포함할 것이고, 그러한 등가물 및 특성은 박막 회로, 반도체 디바이스 및 그의 구성 부품을 포함하는 전자 디바이스의 설계, 제조 및 사용에 이미 공지되어 있고, 본 명세서에서 이미 설명된 특성에 갈음하여 또는 부가하여 사용될 수 있다.

- [0054] 본 출원의 청구범위가 특정 특성의 결합으로 명확히 선언되었지만, 임의의 청구항에서 현재 기재된 것과 동일한 발명에 관한 것이든, 본 발명이 해결하는 것과 동일한 기술적인 문제중 일부 또는 모두를 해결하는 것이든, 본 발명의 개시의 범주는, 본 명세서에서 명백히 기재되거나 함축적으로 기재된 임의의 신규한 특성 또는 임의의 신규한 특성들의 결합들 또는 그들의 임의의 일반화를 또한 포함함을 인식하여야 한다. 별도의 실시예의 내용에 설명된 특성은 또한 단일한 실시예에서의 결합에도 제공된다. 역으로, 간략화를 위해 단일 실시예의 내용에서 설명된 다양한 특성들은 별도로 제공되거나 임의의 적절한 하위 결합으로 제공될 수 있다. 본 출원 또는 이로부터 유도되는 임의의 추가적인 출원의 수행동안, 그러한 특성 및/또는 그러한 특성들의 결합에 대해 새로운 청구항이 세워질 수도 있음을 본 출원인은 여기서 고지하고자 한다.

## 산업이용 가능성

[0055] 전술한 바와 같이, 본 발명은 예를 들면 유리 또는 절연 중합체 기판 같은 기판 상에 박막 트랜지스터(이하 TFT)를 포함하는 전자 디바이스에 이용가능하다.

## 도면의 간단한 설명

- [0056] 도 1a 내지 1c 는 본 발명의 제 1 실시예에 따른 TFT 제조 단계를 도시하는 도면,

- [0057] 도 2a 내지 2b 는 본 발명의 제 2 실시예에 따른 TFT 제조 단계를 도시하는 도면,

- [0058] 도 3a 내지 3c 및 도 4a 내지 4c 는 층내 이격된 구멍 배열을 형성하는 기술에 대한 2가지 예를 도시하는 도면.

# 도면

## 도면1a

## 도면1b

## 도면1c

# 도면2a

## 도면2b

## 도면3a

## 도면3b

# 도면3c

# 도면4a

## *도면4b*

## 도면4c