# (10) **DE 10 2020 202 842 A1** 2021.09.09

(12)

# Offenlegungsschrift

(21) Aktenzeichen: 10 2020 202 842.7

(22) Anmeldetag: **05.03.2020**(43) Offenlegungstag: **09.09.2021**

(51) Int Cl.: **H03K 17/08** (2006.01)

(71) Anmelder:

Robert Bosch Gesellschaft mit beschränkter Haftung, 70469 Stuttgart, DE

(72) Erfinder:

Maier, Christian, 72770 Reutlingen, DE; Strache, Sebastian, 72827 Wannweil, DE; Oberdieck, Karl, 72622 Nürtingen, DE

| (56) | ) Ermitteiter | Stand | aer | i ecnnik: |

|------|---------------|-------|-----|-----------|

|      |               |       |     |           |

| US | 9 490 798        | B1        |

|----|------------------|-----------|

| US | 10 193 544       | B2        |

| US | 2015 / 0 003 133 | <b>A1</b> |

Rechercheantrag gemäß § 43 PatG ist gestellt.

Die folgenden Angaben sind den vom Anmelder eingereichten Unterlagen entnommen.

(54) Bezeichnung: Treiberschaltung für ein niederinduktives Leistungsmodul sowie ein niederinduktives Leistungsmodul mit erhöhter Kurzschlussfestigkeit

(57) Zusammenfassung: Erfindungsgemäß wird eine Treiberschaltung 200 für ein niederinduktives Leistungsmodul 400 zur Verfügung gestellt, welche einen Anschluss 10 und einen Ausgang 20 umfasst. Der Anschluss ist mit dem Source-Kontakt 15 eines Leistungstransistors 12 und der Ausgang 20 ist mit dem Gate-Kontakt 11 des Leistungstransistors 12 verbindbar. Die Treiberschaltung 200 ist dazu ausgelegt, in einem ersten Betriebsmodus eine erste Gate-Source-Spannung U<sub>GS1</sub> für den Gate-Kontakt 11 des Leistungstransistors 200 zu erzeugen und an dem Ausgang 20 der Treiberschaltung 200 zur Verfügung zu stellen. Erfindungsgemäß ist die Treiberschaltung 200 ferner dazu ausgelegt, in einem zweiten Betriebsmodus während wenigstens einer voreingestellten Mindestzeitspanne eine geringere zweite Gate-Source-Spannung  $U_{GS2}$  für den Gate-Kontakt 11 des Leistungstransistors 12 zu erzeugen und an dem Ausgang 20 der Treiberschaltung 200 zur Verfügung zu stellen.

#### **Beschreibung**

[0001] Die vorliegende Erfindung betrifft eine Treiberschaltung für ein niederinduktives Leistungsmodul, welche einen Anschluss und einen Ausgang umfasst, wobei der Anschluss mit dem Source-Kontakt eines Leistungstransistors und der Ausgang mit dem Gate-Kontakt des Leistungstransistors verbindbar ist. Die Treiberschaltung ist dazu ausgelegt, in einem ersten Betriebsmodus eine erste Gate-Source-Spannung für den Gate-Kontakt des Leistungstransistors zu erzeugen und an dem Ausgang der Treiberschaltung zur Verfügung zu stellen.

#### Stand der Technik

[0002] Niederinduktive Leistungsmodule, insbesondere Leistungsmodule die Halbleiter mit großer Bandlücke nutzen wie beispielsweise Siliziumcarbid MOSFETs (SiC MOSFETs) bieten - verglichen beispielsweise mit anderen Schaltmitteln - signifikante Vorteile im Bereich der Schaltverluste, was unter anderem zu größeren Reichweiten von Elektrofahrzeugen beiträgt. Um überlegene Schaltleistungen mit großen schaltbaren Spannungen (du/dt > 10V/ns) und großen schaltbaren Strömen (di/dt > 1A/ns) zu ermöglichen, werden für besagte Leistungsmodule Module mit kleiner Induktivität (L < 15nH) benötigt.

[0003] Zur Erreichung der oben erwähnten überlegenen Schaltleistung werden die hier in Rede stehenden Leistungsmodule meist auf dünnen Chips zur Verfügung gestellt, welche - verglichen mit anderen, auf dickeren Chips bereitgestellten Leistungsmodulen - eine geringere thermische Kapazität aufweisen, was die Zeitspanne verkleinert, während derer die Leistungsmodule einem Kurzschluss widerstehen beziehungsweise standhalten können. Hierbei spielen insbesondere zwei verschiedene, sogenannte Kurzschlusstypen beziehungsweise Kurzschlussbedingungen eine hervorzuhebende Rolle.

[0004] Beim sogenannten Kurzschlusstyp 1 tritt ein Kurzschluss direkt bei beziehungsweise während des Einschaltvorgangs des Leistungsmoduls - insbesondere eines Leistungstransistors - auf, während beim sogenannten Kurzschlusstyp 2 ein Kurzschluss nach dem Einschaltvorgang des Leistungsmoduls beziehungsweise des Leistungstransistors auftritt. So ist die oben beschriebene, erhöhte Schaltleistung besonders mit Blick auf den Kurzschlusstyp 1 kritisch, da zum Beispiel ein Leistungstransistor wie ein Leistungs-MOSFET im Kurzschlusstyp 1- Kurzschlussfall mit einer hohen Gate-Source-Spannung, U<sub>GS</sub>, eingeschaltet und mit einer sehr hohen Drain-Source-Spannung, U<sub>DS</sub>, betrieben wird. Dies kann beispielsweise passieren, wenn der Komplementärpartner des kurzgeschlossenen Leistungs-MOSFETs (zum Beispiel innerhalb einer Inverter-Schaltung) beschädigt ist. In einem solchen Fall muss eine mit dem

Leistungsmodul beziehungsweise dem Leistungstransistor verbundene Kurzschluss-Überwachungsschaltung, welche im Falle einer Überwachungsschaltung der Spannung über einem Leistungstransistor im Englischen oft auch als "Desaturation Detection Circuit" (DeSat) bezeichnet wird, das Vorliegen des Kurzschlussfalls erkennen und das Leistungsmodul beziehungsweise den Leistungstransistor abschalten. Die vorbezeichnete Überwachungsschaltung reagiert auf die Halbleiterspannung und ist deshalb im Schaltmoment unwirksam geschaltet, der sogenannten Ausblendzeit (im Englischen oft auch als "blanking time" bezeichnet). Zusätzlich zu dieser Ausblendzeit gibt es eine Reaktionszeit, in der die kurzgeschlossenen Leistungshalbleiter abgeschaltet werden. Diese Ausblend- und Reaktionszeit darf nicht denjenigen Maximalzeitraum überschreiten, innerhalb dessen das Leistungsmodul beziehungsweise der Leistungstransistor noch in der Lage ist, einem Kurzschluss zu widerstehen/standzuhalten, bevor es/er ausfällt.

[0005] Auf Grund des bei der oben beschriebenen überlegenen Schaltleistung gegebenen, nur kurzen Stromanstiegszeitraums, also auf Grund des schnellen Stromanstiegs, kommt es während der oben beschriebenen Ausblend- und Reaktionszeit zu einer signifikanten Stromüberschreitung, bei welcher Ströme fließen, die zehnmal so groß sind wie der Nominalstrom. Diese Stromüberschreitung führt zu einer signifikanten Aufheizung des Leistungsmoduls beziehungsweise des Leistungstransistors, was eine zusätzliche Degradation des Leistungsmoduls/Leistungstransistors bewirkt, was den oben beschriebenen Maximalzeitraum, während welchem der Leistungstransistor noch in der Lage ist, einem Kurzschluss zu widerstehen, verkürzt.

[0006] Beim sogenannten Kurzschlusstyp 2 tritt ein Kurzschluss auf, während sich das Leistungsmodul beziehungsweise der Leistungstransistor bereits im (vollständig) eingeschalteten Zustand befindet. Dies kann beispielsweise passieren, wenn der Komplementärpartner eines kurzgeschlossenen Leistungs-MOSFETs (zum Beispiel innerhalb einer Inverter-Schaltung) im eingeschalteten Zustand beschädigt wird. Nach einem Fehler des Leistungsmoduls/Leistungstransistors, also beispielsweise nach einem Ausfall des komplementären Schalttransistors, erhöht sich zunächst der durch den Leistungstransistor fließende Strom di/dt und im Anschluss daran die in diesem vorherrschende Spannung.

[0007] Auf Grund eines Verschiebungsstroms, welcher sich während der Erhöhung der Transistor-Spannung du/dt einstellt, erhöht sich die Gate-Source-Spannung  $U_{GS}$  des Leistungstransistors über den normalen Einschaltwert hinaus. Die Erhöhung der Gate-Source-Spannung  $U_{GS}$  über den normalen Einschaltwert hinaus erhöht den Kurzschlussstrom noch

weiter. Eine Kurzschluss-Überwachungsschaltung (siehe oben: "Desaturation Detection Circuit" (DeSat) ) beziehungsweise eine Abschaltschaltung, welche die Stromveränderung di/dt über der Zeit mittels einer Hilfsinduktivität misst, triggert den Abschaltprozess des Leistungstransistors. Allerdings vermag die Kurzschluss-Überwachungsschaltung nicht die Belastung (insbesondere bei Spitzenströmen) des Leistungsmoduls/Leistungstransistors während derartiger Fehlerfälle zu reduzieren. Solche Belastungen, insbesondere Beanspruchungen innerhalb des Leistungsmoduls/Leistungstransistors, können zu einer Degradation der Parameter eben dieses Leistungsmoduls/Leistungstransistors führen.

[0008] Verschiedene Verfahren beziehungsweise Schaltungsvarianten existieren im Stand der Technik, um den oben beschriebenen Widerstands-Maximalzeitraum - während dem das Leistungsmodul beziehungsweise der Leistungstransistor einem Kurzschluss zerstörungsfrei standzuhalten in der Lage ist - zu verlängern. Dabei führen beispielsweise konventionelle Verfahren wie das Gate-Source Feedback oder das Vorsehen eines höheren Gate-Widerstands zu einer Verringerung der Schaltleistung des Leistungsmoduls/Leistungstransistors und erhöhen daher die Schaltenergie. Weitere derartige Verfahren sind beispielsweise in der US 9490798 B1 oder in der US 10193544 B2 detailliert beschrieben.

#### Offenbarung der Erfindung

[0009] Erfindungsgemäß wird eine Treiberschaltung für ein niederinduktives Leistungsmodul zu Verfügung gestellt, welche einen Anschluss und einen Ausgang umfasst. Der Anschluss ist mit dem Source-Kontakt eines Leistungstransistors und der Ausgang ist mit dem Gate-Kontakt des Leistungstransistors verbindbar. Die Treiberschaltung ist dazu ausgelegt, in einem ersten Betriebsmodus eine erste Gate-Source-Spannung für den Gate-Kontakt des Leistungstransistors zu erzeugen und an dem Ausgang der Treiberschaltung zur Verfügung zu stellen. Erfindungsgemäß ist die Treiberschaltung ferner dazu ausgelegt, in einem zweiten Betriebsmodus während wenigstens einer voreingestellten Mindestzeitspanne eine geringere zweite Gate-Source-Spannung für den Gate-Kontakt des Leistungstransistors zu erzeugen und an dem Ausgang der Treiberschaltung zur Verfügung zu stellen.

[0010] Mit einer derartigen Treiberschaltung ist es vorteilhaft möglich, das Leistungsmodul beziehungsweise den Leistungstransistor bei gleichbleibendem Schaltverhalten, also bei gleichbleibender Schaltleistung beziehungsweise Schalteffizienz mit den bekannten geringen Leistungsverlusten, vor einer Beschädigung durch einen Kurzschluss - in beiden zuvor beschriebenen Kurzschluss-Fällen 1 und 2 - wirksam zu schützen. Dies geschieht, indem die Trei-

berschaltung den Betrieb des Leistungsmoduls/Leistungstransistors in zwei verschiedenen Betriebsmodi mit zwei verschiedenen Gate-Source-Spannungen erlaubt. Für einen Schutz gegen den Kurzschlusstypen 1 wird die Stromspitze im Leistungsmodul/dem Leistungstransistor (welche sich während des Kurzschlussfalls einstellt) durch eine Reduktion der Gate-Source-Spannung in einer Zeitspanne während der Kurzschluss-Detektionszeit (also während einiger Mikrosekunden) der Kurzschluss-Überwachungsschaltung bzw. Kurzschluss-Erkennungsschaltung (DeSat) im zweiten Betriebsmodus herabgesetzt. Auf Grund dieser Herabsetzung der Gate-Source-Spannung ist der Sättigungsstrom des Leistungsmoduls/Leistungstransistors im Ausgangskennlinienfeld (also der Strom ID =  $f(U_{DS})$ , das heißt der Drain-Strom ID als Funktion der Drain-Source-Spannung) reduziert. Nach Ablauf der voreingestellten Mindestzeitspanne erhöht die Treiberschaltung im ersten Betriebsmodus die Gate-Source-Spannung von der zweiten auf die erste Gate-Source-Spannung und stellt diese am Ausgang der Treiberschaltung für den Gate-Kontakt eines mit dem Ausgang der Treiberschaltung verbundenen Leistungstransistors zur Verfügung. Nach Ablauf der voreingestellten Mindestzeitspanne wird also (wieder) die nominale Gate-Source-Spannung des Leistungstransistors innerhalb der Treiberschaltung erzeugt bzw. generiert und am Ausgang der Treiberschaltung zur Verfügung gestellt. Dies ermöglicht den bekannten, vorteilhaften Betrieb des Leistungstransistors mit geringen Leitungsverlusten, welcher sich insbesondere bei der Verwendung von SiC MOSFETs einstellt. bei gleichzeitig verbessertem Kurzschlussschutz. Die gesteigerte Leitungsverlustenergie während der Verringerung der Gate-Source-Spannung im zweiten Betriebsmodus kann folgendermaßen berechnet wer-

$$\Delta J_{\text{cond}} = (R_{\text{DSon}}, u_{\text{GS1}} - R_{\text{DSon}}, u_{\text{GS2}}) * I_{\text{D}}^2 * tu_{\text{GS1}}$$

$$\Delta J_{\text{cond}} = U_{\text{DS}} * I_{\text{D}} * tu_{\text{GS1}},$$

wobei  $\Delta J_{cond}$  die Veränderung der Leitungsverlustenergie ist,  $R_{DSon}$ ,  $U_{GS1}$  der On-State Widerstand der Drain-Source-Strecke des Leistungstransistors bei der ersten Gate-Source-Spannung im ersten Betriebsmodus ist,  $R_{DSon}$ ,  $U_{GS2}$  der On-State Widerstand der Drain-Source-Strecke des Leistungstransistors bei der zweiten Gate-Source-Spannung im zweiten Betriebsmodus ist, ID der Drain-Strom des Leistungstransistors ist und tu\_{GS1} die voreingestellten Mindestzeitspanne ist. Zu beachten ist, dass die verringerte zweite Gate-Source-Spannung immer noch groß genug zu wählen ist, sodass eine sichere beziehungsweise normale Einschaltung des Leistungstransistors gewährleistet bleibt.

[0011] Bevorzugt entspricht die voreingestellte Mindestzeitspanne derjenigen Zeitspanne, die von ei-

ner mit dem Leistungstransistor verbundenen Kurzschluss-Erkennungsschaltung benötigt wird, um einen Kurzschluss bei der Einschaltung des Leistungstransistors zu erkennen und eine Abschaltung des Leistungstransistors einzuleiten und/oder vorzunehmen. In einer derartigen Ausführung ist das Leistungsmodul beziehungsweise der Leistungstransistor in einem mit der erfindungsgemäßen Treiberschaltung verbundenen Zustand besonders gut vor einer kurzschlussbedingten Beschädigung beziehungsweise Degradation geschützt.

**[0012]** Gemäß einer bevorzugten Ausführung wird der zweite Betriebsmodus durch die Erkennung einer Einschaltung eines mit der Treiberschaltung verbundenen Leistungstransistors initiiert.

**[0013]** Vorzugsweise umfasst die Treiberschaltung zwei verschiedene Spannungsquellen, mittels welcher die erste und die zweite Gate-Source-Spannung erzeugbar und am Ausgang der Treiberschaltung zur Verfügung stellbar sind. Auf diese Weise können die zwei verschiedenen Gate-Source-Spannungen besonders sicher und im schnellen Wechsel zur Verfügung gestellt werden.

[0014] In einer bevorzugten Ausführungsform der Erfindung haben die zwei verschiedenen Spannungsquellen jeweils einen mit dem Anschluss der Treiberschaltung verbundenen Eingang sowie jeweils einen Spannungsausgang, wobei der Spannungsausgang der ersten Spannungsquelle über eine Reihenschaltung aus einer ersten Diode und einem ersten Widerstand mit dem Ausgang der Treiberschaltung verbunden ist, während der Spannungsausgang der zweiten Spannungsquelle über eine Parallelschaltung zweier Pfade mit dem Ausgang der Treiberschaltung verbunden ist, wobei in jedem der Pfade eine Diode und/oder ein Widerstand vorgesehen ist. Über die zwei verschiedenen Spannungsausgänge, die ihrerseits jeweils mit dem Ausgang der Treiberschaltung elektrisch leitfähig verbunden sind, lassen sich die Gate-Source-Spannungen nicht nur besonders gut und genau einstellen, sondern auch kontrollieren.

**[0015]** Bevorzugt ist in einigen Ausführungsformen der Gate-Widerstand - verglichen mit den Gate-Widerständen bei herkömmlichen Treiberschaltungen beziehungsweise verglichen mit dem Gate-Widerstand in einem Spannungspfad, welcher für die Bereitstellung der zweiten Gate-Source-Spannung im zweiten Betriebsmodus vorgesehen ist - reduziert beziehungsweise reduziert gewählt.

**[0016]** Insbesondere bei derartigen Ausführungsformen kann die gleiche Schaltleistung beziehungsweise Schalteffizienz beibehalten werden, besonders verglichen zu einer Treiberschaltung, mittels welcher lediglich eine Gate-Source-Spannung zur Verfügung

stellbar ist. Auch garantiert ein solcher, verringerter Gate-Widerstand, dass es bei Anliegen der reduzierten zweiten Gate-Source-Spannung nicht zu einer Einschaltverzögerung des Leistungstransistors kommt.

[0017] Bevorzugt umfasst die Treiberschaltung ferner eine Ansteuerschaltung, welche die Spannungsquellen entsprechend eines vorbestimmten Algorithmus betreibt. Bevorzugt umfasst die Ansteuerschaltung einen Controller, insbesondere einen Microcontroller, einen Computer oder einen Microcomputer. In anderen erfindungsgemäßen Ausführungsvarianten kann die erfindungsgemäße Treiberschaltung auch lediglich Steuermittel und/oder einen Steueranschluss (und keine eigene Ansteuerschaltung) umfassen, welche dazu ausgebildet sind, von einer externen, außerhalb der Treiberschaltung vorgesehenen Ansteuerschaltung gesteuert zu werden. Solche Steuermittel können beispielsweise Schaltmittel umfassen, mittels welcher die Spannungsquellen jeweils in einen aktiven oder inaktiven Zustand schaltbar sind. Bevorzugt umfasst die Ansteuerschaltung eine Zeitnehmer-Schaltung (im englischen oft auch als Timer bezeichnet). In einer derartigen Ausführung kann die Steuerung der Spannungsquellen vorteilhafterweise direkt in und von der Treiberschaltung selbst vorgenommen werden. Dies ermöglicht den autonomen Einsatz der Treiberschaltung gemeinsam mit dem Leistungsmodul/Leistungstransistor.

**[0018]** Bevorzugt umfasst die Ansteuerschaltung einen RC-Schaltkreis beziehungsweise einen RC-Schwingkreis.

[0019] Vorzugsweise ist zwischen dem Ausgang und dem Anschluss der Treiberschaltung mindestens eine Spannungsquelle vorgesehen, mittels welcher der Ausgang der Treiberschaltung mit einer Spannung beaufschlagbar ist, wobei mindestens eine Induktivität mittels eines Schaltmittels dem elektrischen Pfad zwischen der mindestens einen Spannungsquelle und dem Anschluss reversibel hinzuschaltbar ist. In einer derartigen Ausführungsform ist die erfindungsgemäße Treiberschaltung besonders gut gegen Kurzschlüsse des Kurzschlusstyps 2 geschützt. Die reversibel hinzuschaltbare Induktivität fungiert hier als optionales Source Feedback für einen mit der Treiberschaltung verbundenen Leistungstransistor, welches Kurzschluss-Stromspitzen innerhalb des Leistungsmoduls/Leistungstransistors bei gleichbleibender Schaltleistung reduziert. Bevorzugt bedeutet die Formulierung reversibel hinzuschaltbar, dass die Induktivität - in einem mit dem Leistungsmodul/ Leistungstransistor verbundenen Zustand der Treiberschaltung - in einer ersten Stellung des Schaltmittels einer Rückkopplungsschleife, welche den Source-Anschluss des Leistungstransistors über eine die Gate-Spannung bereitstellende Spannungsquelle und einen Gate-Widerstand mit dem Gate-An-

### DE 10 2020 202 842 A1 2021.09.09

schluss des Leistungstransistors verbindet, hinzugeschaltet ist und in einer zweiten Stellung des Schaltmittels aus dieser Rückkopplungsschleife herausgekoppelt ist. In dieser Ausführung ist die erfindungsgemäße Treiberschaltung also mit einer auswählbaren Source-Verbindung ausgestattet. Bevorzugt ist die Treiberschaltung dazu ausgebildet, die Induktivität während des Einschaltvorgangs des Leistungsmoduls beziehungsweise des Leistungstransistors dem elektrischen Pfad zwischen der mindestens einen Spannungsquelle und dem Anschluss nicht hinzuzuschalten. Mit anderen Worten ausgedrückt ist die Treiberschaltung bevorzugt dazu ausgebildet, die Induktivität während des Einschaltvorgangs des Leistungsmoduls beziehungsweise des Leistungstransistors aus dem elektrischen Pfad zwischen der mindestens einen Spannungsquelle und dem Anschluss der Treiberschaltung herauszukoppeln. Des Weiteren ist die Treiberschaltung bevorzugt dazu ausgebildet, die Induktivität nach Abschluss des Einschaltvorgangs dem elektrischen Pfad zwischen der mindestens einen Spannungsquelle und dem Anschluss der Treiberschaltung hinzuzuschalten, also in diesen einzukoppeln. Bevorzugt wird dieses Hinzu- oder Herausschalten beziehungsweise das Ein- oder Auskoppeln der Induktivität durch die oben beschriebene oder durch eine weitere Ansteuerschaltung beziehungsweise über die oben beschriebenen oder durch weitere Steuermittel und/oder über einen Steueranschluss durchgeführt. Besonders bevorzugt kann diese, eine reversibel hinzuschaltbare Induktivität umfassende Ausführungsform mit den zuvor beschriebenen Ausführungsformen kombiniert werden.

[0020] Bevorzugt umfasst die Treiberschaltung ferner eine weitere Spannungsquelle, welche mit der Induktivität in Reihe geschaltet ist und mittels des Schaltmittels gemeinsam mit der Induktivität dem elektrischen Pfad zwischen der mindestens einen Spannungsquelle und dem Anschluss reversibel hinzuschaltbar ist. In dieser Ausführungsvariante ist die Treiberschaltung besonders einfach und kostengünstig gegen Kurzschlüsse sowohl des ersten Kurzschlusstyps 1 als auch des zweiten Kurzschlusstyps 2 geschützt ohne die Schaltenergien zu erhöhen.

[0021] Ferner bevorzugt weist mindestens eine der Spannungsquellen der Treiberschaltung einen linearen Regler, einen RC Spannungsteiler, mindestens einen Bipolar-Transistor und/oder eine Bootstrap-Schaltung auf und/oder ist mindestens eine der Spannungsquellen der Treiberschaltung unter Verwendung einer Bipolar-Transistor-Struktur und/oder einer MOSFET-Struktur, insbesondere als ASIC oder mittels diskreter Bauteile, realisiert. In dieser Ausführungsvariante kann die erfindungsgemäße Treiberschaltung besonders kostengünstig und/oder kompakt zur Verfügung gestellt werden. In einer solchen Ausführungsvariante kann die Spannung am Gate

beispielsweise mittels einer Stromquelle dynamisch nachgebildet werden.

[0022] Des Weiteren wird ein niederinduktives Leistungsmodul mit einer erfindungsgemäßen Treiberschaltung bereitgestellt, welches einen Leistungstransistor mit einem Source-Kontakt und einem Gate-Kontakt aufweist, wobei der Source-Kontakt mit dem Anschluss der Treiberschaltung und der Gate-Kontakt mit dem Ausgang der Treiberschaltung verbunden ist. Bei derartigen Leistungsmodulen kommen die zuvor für die Treiberschaltung erwähnten Vorteile zum Tragen.

**[0023]** Bevorzugt ist der Leistungstransistor ein Siliziumcarbid-MOSFET. SiC MOSFETs, also Siliziumcarbid MOSFETs, bieten - verglichen beispielsweise mit anderen Schaltmitteln - signifikante Vorteile im Bereich der Schaltleistung, was unter anderem zu größeren Reichweiten für Elektrofahrzeuge beiträgt.

**[0024]** Bevorzugt meinen die Begriffe verbunden und/oder verbindbar eine elektrisch leitfähige Verbindung beziehungsweise eine elektrisch leitfähige Verbindbarkeit.

**[0025]** Bevorzugt ist die voreingestellte Mindestzeitspanne auf einen Wert von 2µs voreingestellt.

**[0026]** Bevorzugt ist die voreingestellte Mindestzeitspanne auf einen Wert von MZS voreingestellt, wobei MZS  $\in$  [0,1  $\mu$ s;  $5\mu$ s].

**[0027]** Vorteilhafte Weiterbildungen der Erfindung sind in den Unteransprüchen angegeben und in der Beschreibung beschrieben.

#### Figurenliste

**[0028]** Ausführungsbeispiele der Erfindung werden anhand der Zeichnungen und der nachfolgenden Beschreibung näher erläutert. Es zeigen:

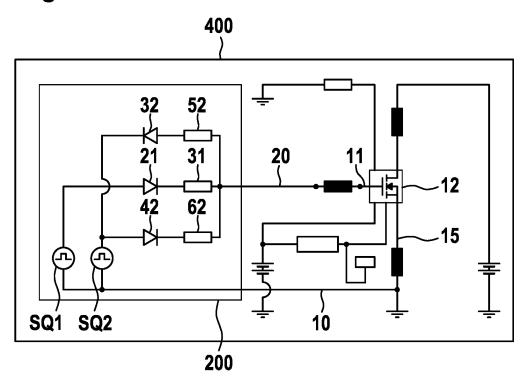

Fig. 1 eine schematische Darstellung eines ersten Ausführungsbeispiels einer erfindungsgemäßen Treiberschaltung mit zwei Spannungsquellen in einem mit einem Leistungstransistor verbundenen Zustand:

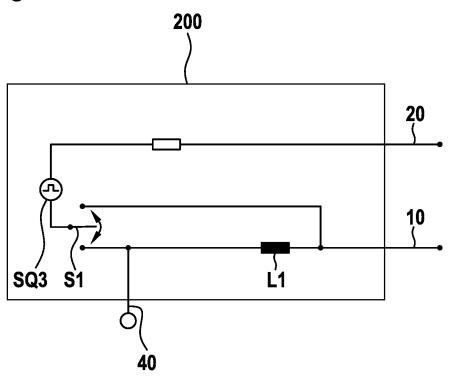

**Fig. 2** eine erste Anwendung des ersten Ausführungsbeispiels der erfindungsgemäßen Treiberschaltung mit einem Leistungstransistor;

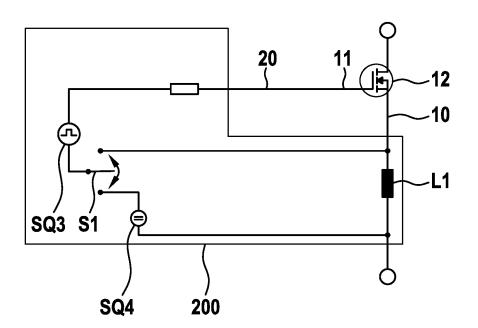

**Fig. 3** ein zweites Ausführungsbeispiel einer erfindungsgemäßen Treiberschaltung mit einer koppelbaren Induktivität;

Fig. 4 ein drittes Ausführungsbeispiel einer erfindungsgemäßen Treiberschaltung, und

**Fig. 5** ein viertes Ausführungsbeispiel einer erfindungsgemäßen Treiberschaltung mit einem Mehrfach-Chip Leistungsmodul.

#### Ausführungsformen der Erfindung

[0029] In der Fig. 1 ist eine schematische Darstellung eines ersten Ausführungsbeispiels einer erfindungsgemäßen Treiberschaltung 200 mit zwei Spannungsquellen SQ1, SQ2 in einem mit einem Leistungstransistor verbundenen Zustand dargestellt. Diese erfindungsgemäße Treiberschaltung 200 ist für den Betrieb eines niederinduktiven Leistungsmoduls 400 ausgelegt, welches in diesem Ausführungsbeispiel rein beispielhaft als Siliziumcarbid-Leistungstransistor, genauer rein beispielhaft als Siliziumcarbid-MOSFET ausgeführt ist. Die erfindungsgemäße Treiberschaltung kann aber auch für andere Arten von Leistungsmodulen bzw. Leistungstransistoren verwandt werden. Die erfindungsgemäße Treiberschaltung 200 umfasst einen Anschluss 10 und einen Ausgang 20, wobei in Fig. 1 der Anschluss 10 mit dem Source-Kontakt 15 eines Leistungstransistors 12 und der Ausgang 20 mit dem Gate-Kontakt 11 des Leistungstransistors 12 verbunden ist.

[0030] Die erfindungsgemäße Treiberschaltung 200 ist dazu ausgelegt, in einem ersten Betriebsmodus eine erste Gate-Source-Spannung U<sub>GS1</sub> für den Gate-Kontakt 11 des Leistungstransistors 12 zu erzeugen und an dem Ausgang 20 der Treiberschaltung 200 zur Verfügung zu stellen. Ferner ist die Treiberschaltung 200 dazu ausgelegt, in einem zweiten Betriebsmodus während wenigstens einer voreingestellten Mindestzeitspanne eine geringere zweite Gate-Source-Spannung U<sub>GS2</sub> für den Gate-Kontakt 11 des Leistungstransistors 12 zu erzeugen und an dem Ausgang 20 der Treiberschaltung 200 zur Verfügung zu stellen. In diesem Ausführungsbeispiel ist eine Kurzschluss-Erkennungsschaltung (in Fig. 1 nicht dargestellt) mit dem Leistungstransistor 12 elektrisch leitfähig verbunden.

[0031] Die oben erwähnte voreingestellte Mindestzeitspanne entspricht in diesem ersten Ausführungsbeispiel derjenigen Zeitspanne, die von der mit dem Leistungstransistor 12 verbundenen Kurzschluss-Erkennungsschaltung benötigt wird, um einen Kurzschluss bei der Einschaltung des Leistungstransistors 12 zu erkennen und eine Abschaltung des Leistungstransistors 12 einzuleiten und vorzunehmen. Die voreingestellte Mindestzeitspanne kann aber auch der Ausblendzeit (Englisch "blanking time" genannt) der Kurzschluss-Erkennungsschaltung entsprechen und/oder flexible an ein von der Kurzschluss-Erkennungsschaltung erzeugtes Signal gekoppelt sein, sodass die Kurzschluss-Erkennungsschaltung die Treiberschaltung mittels eines Signals in den zweiten Betriebsmodus überführt oder diesen initiiert.

[0032] In diesem ersten Ausführungsbeispiel weist die Treiberschaltung 200 zwei verschiedene Spannungsquellen SQ1, SQ2 auf, mittels welchen die ers-

te und die zweite Gate-Source-Spannung  $U_{GS1}$ ,  $U_{GS2}$ erzeugbar und am Ausgang 20 der Treiberschaltung 200 zur Verfügung stellbar sind. Es können allerdings auch erfindungsgemäße Treiberschaltungen 200 realisiert werden, welche nur eine Spannungsquelle oder mehr als zwei Spannungsquellen aufweisen. Die zwei verschiedenen Spannungsquellen SQ1 und SQ2 weisen jeweils einen mit dem Anschluss 10 der Treiberschaltung 200 verbundenen Eingang sowie jeweils einen Spannungsausgang auf. Der Spannungsausgang der ersten Spannungsquelle SQ1 ist in diesem ersten Ausführungsbeispiel rein beispielhaft über eine Reihenschaltung aus einer ersten Diode 21 und einem ersten Widerstand 31 mit dem Ausgang 20 der Treiberschaltung 200 verbunden. Der Spannungsausgang der zweiten Spannungsquelle SQ2 ist in diesem ersten Ausführungsbeispiel rein beispielhaft über eine Parallelschaltung zweier Pfade P1, P2 mit dem Ausgang 20 der Treiberschaltung 200 verbunden, wobei in jedem der Pfade eine Diode 32, 42 und ein Widerstand 52, 62 vorgesehen ist.

[0033] In diesem ersten Ausführungsbeispiel umfasst die erfindungsgemäße Treiberschaltung 200 ferner eine Ansteuerschaltung (nicht dargestellt in Fig. 1), welche die Spannungsquellen SQ1 und SQ2 entsprechend eines vorbestimmten Algorithmus betreibt. Der Algorithmus betreibt die Treiberschaltung 200 also wechselnd im ersten beziehungsweise zweiten Betriebsmodus.

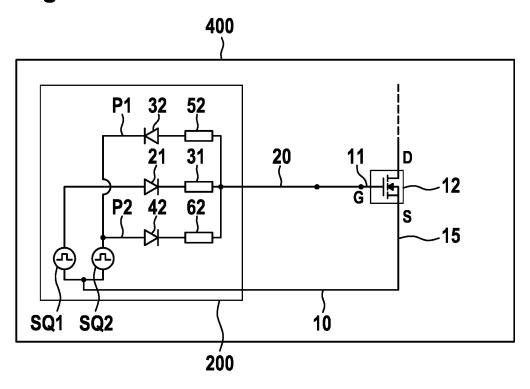

[0034] Fig. 2 zeigt eine erste Anwendung des ersten Ausführungsbeispiels der erfindungsgemäßen Treiberschaltung 200 mit einem Leistungstransistor 12. In dieser in Fig. 2 dargestellten Anwendung weist das Leistungsmodul, welches hier unter anderem die Treiberschaltung 200 und den Leistungstransistor umfasst, noch weitere elektronische Komponenten beziehungsweise Bauteile auf, die für den von der erfindungsgemäßen Treiberschaltung 200 bereitgestellten technischen Effekt aber nicht weiter von Bedeutung sind. Es ist wichtig zu verstehen, dass der erfindungsgemäße Zweck auf verschiedene Weise erreicht werden kann. So können die zwei verschiedenen Gate-Source-Spannungen U<sub>GS1</sub>, U<sub>GS2</sub> zum Beispiel dadurch bereitgestellt werden, dass die beiden Spannungsquellen SQ1 und SQ2 alternierend eingeschaltet werden (also nicht gemeinsam betrieben werden beziehungsweise eingeschaltet sind). Die zwei verschiedenen Gate-Source-Spannung U<sub>GS1</sub>, U<sub>GS2</sub> können zum Beispiel aber auch durch eine zeitversetze Einschaltung der beiden Spannungsquellen SQ1 und SQ2 bereitgestellt werden, sodass zunächst zum Beispiel die zweite Spannungsquelle SQ2 zur Bereitstellung der zweiten Gate-Source-Spannung U<sub>GS2</sub> eingeschaltet wird und nach Ablauf der voreingestellten Mindestzeitspanne die erste Spannungsquelle SQ1 zur Bereitstellung der ersten Gate-Source-Spannung  $U_{GS1}$  hinzugeschaltet wird. Bei dieser Ausführung werden die Spannungen der

beiden Spannungsquellen **SQ1** und **SQ2** also superpositioniert.

[0035] Fig. 3 zeigt ein zweites Ausführungsbeispiel einer erfindungsgemäßen Treiberschaltung 200 mit einer koppelbaren Induktivität L1. In diesem Ausführungsbeispiel ist zwischen dem Ausgang 20 und dem Anschluss 10 der Treiberschaltung 200 lediglich eine Spannungsquelle SQ3 vorgesehen, mittels welcher der Ausgang 20 der Treiberschaltung 200 mit einer Spannung beaufschlagbar ist. Ferner ist eine Induktivität L1 mittels eines Schaltmittels S1 dem elektrischen Pfad zwischen der mindestens einen Spannungsquelle und dem Anschluss 10 reversibel hinzuschaltbar. Wie bereits oben erläutert fungiert die reversibel hinzuschaltbare Induktivität hier als optionales Source Feedback für einen mit der Treiberschaltung verbundenen Leistungstransistor, welches Kurzschluss-Stromspitzen innerhalb des Leistungsmoduls/Leistungstransistors bei gleichbleibender Schaltleistung reduziert. In diesem zweiten Ausführungsbeispiel führt die Induktivität L1 den vollen Laststrom. Sie kann in anderen Ausführungen aber auch einen Strom führen, der geringer ist als der volle Laststrom. Mittels des Abgriffs 40, welcher hier einen Leistungsabgriff darstellt, kann die Treiberschaltung 200 in einem mit einem Leistungsmodul verbundenen Zustand mit weiteren Komponenten, zum Beispiel einer Last verbunden werden.

[0036] Fig. 4 zeigt ein drittes Ausführungsbeispiel einer erfindungsgemäßen Treiberschaltung 200, welches weitgehend mit dem in Fig. 3 dargestellten identisch ist, jedoch ferner eine weitere Spannungsquelle SQ4 umfasst, welche mit der Induktivität L1 in Reihe geschaltet ist und mittels des Schaltmittels S1 gemeinsam mit der Induktivität L1 dem elektrischen Pfad zwischen der mindestens einen Spannungsquelle SQ3 und dem Anschluss 10 reversibel hinzuschaltbar ist. Insbesondere in dieser dritten Ausführung bietet die erfindungsgemäße Treiberschaltung 200 einen effizienten Schutz gegen beide Kurzschlusstypen 1 und 2. Auch in diesem dritten Ausführungsbeispiel führt die Induktivität L1 rein beispielhaft den vollen Laststrom. Sie kann in anderen Ausführungen aber auch einen Strom führen, der geringer ist als der volle Laststrom.

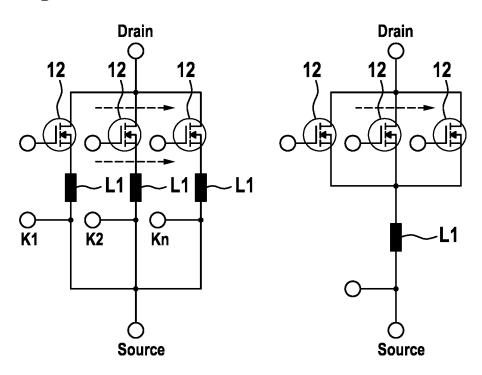

[0037] Fig. 5 zeigt einen Teil eines vierten Ausführungsbeispiels einer erfindungsgemäßen Treiberschaltung 200 mit einem Mehrfach-Chip Leistungsmodul. Dabei sind zwei verschiedene Schaltungsvarianten einander gegenübergestellt. Links in Fig. 5 ist eine erste Schaltungsvariante gezeigt, bei welcher jeder einzelne Chip beziehungsweise jeder auf einem solchen Chip realisierte Leistungstransistor 12 ein eigenes Source-Feedback aufweist. Hier umfasst also jeder einzelne auf einem Chip realisierte Leistungstransistor 12 eine eigene, reversible dem Source-Pfad des jeweiligen Leistungstransistors 12 hinzu-

schaltbare Induktivität L1. In der links in Fig. 5 gezeigten Schaltungsvariante beziehungsweise Schaltungskonfiguration müssen die Gate-Kontakte der Leistungstransistoren 12 im Leistungsmodul und/ oder in der Treiberschaltung 200 miteinander elektrisch leitfähig verbunden sein. Auch müssen die Anschlüsse K1 bis Kn der Induktivitäten L1 in der Treiberschaltung 200 oder im Leistungsmodul elektrisch leitfähig miteinander verbunden sein, oder es muss alternativ dazu - je Induktivität L1 ein Schaltmittel zum herein- oder herauskoppeln der jeweiligen Induktivität L1 in den jeweiligen Source-Pfad des jeweiligen Leistungstransistors 12 vorgesehen sein. Ferner sollten bei dieser ersten Schaltungsvariante sämtliche Induktivitäten L1 symmetrisch ausgeführt sein, um Oszillationen der Gesamtschaltung zu reduzieren.

[0038] Rechts in Fig. 5 ist eine zweite Schaltungskonfiguration gezeigt, welche ein gemeinsames Source-Feedback für alle Chips beziehungsweise für alle auf jeweils einem Chip realisierten Leistungstransistoren 12 umfasst. Hier ist also lediglich eine reversible den Source-Pfaden sämtlicher Leistungstransistoren 12 gemeinsam hinzuschaltbare Induktivität L1 vorgesehen. Auch in dieser rechts in Fig. 5 gezeigten Schaltungsvariante beziehungsweise Schaltungskonfiguration müssen die Gate-Kontakte der Leistungstransistoren 12 im Leistungsmodul und/oder in der Treiberschaltung 200 miteinander elektrisch leitfähig verbunden sein. Allerdings reicht bei dieser Schaltungsvariante lediglich ein Schaltmittel aus, um die Hinzuschaltbarkeit beziehungsweise die Herauskoppelbarkeit der einen gemeinsamen Induktivität L1 zu gewährleisten.

[0039] Obwohl die Erfindung im Detail durch bevorzugte Ausführungsbeispiele näher illustriert und beschrieben wurde, so ist die Erfindung nicht durch die offenbarten Beispiele eingeschränkt und andere Variationen können vom Fachmann hieraus abgeleitet werden, ohne den Schutzumfang der Erfindung zu verlassen.

## DE 10 2020 202 842 A1 2021.09.09

#### ZITATE ENTHALTEN IN DER BESCHREIBUNG

Diese Liste der vom Anmelder aufgeführten Dokumente wurde automatisiert erzeugt und ist ausschließlich zur besseren Information des Lesers aufgenommen. Die Liste ist nicht Bestandteil der deutschen Patent- bzw. Gebrauchsmusteranmeldung. Das DPMA übernimmt keinerlei Haftung für etwaige Fehler oder Auslassungen.

#### **Zitierte Patentliteratur**

- US 9490798 B1 [0008]

- US 10193544 B2 [0008]

#### **Patentansprüche**

- 1. Treiberschaltung (200) für ein niederinduktives Leistungsmodul (400), umfassend einen Anschluss (10) und einen Ausgang (20),

- wobei der Anschluss (10) mit dem Source-Kontakt (15) eines Leistungstransistors (12) und der Ausgang (20) mit dem Gate-Kontakt (11) des Leistungstransistors (12) verbindbar ist und

wobei die Treiberschaltung (200) dazu ausgelegt ist, in einem ersten Betriebsmodus eine erste Gate-Source-Spannung ( $U_{\rm GS1}$ ) für den Gate-Kontakt (11) des Leistungstransistors (12) zu erzeugen und an dem Ausgang (20) der Treiberschaltung (200) zur Verfügung zu stellen;

#### dadurch gekennzeichnet, dass

die Treiberschaltung (200) ferner dazu ausgelegt ist, in einem zweiten Betriebsmodus während wenigstens einer voreingestellten Mindestzeitspanne eine geringere zweite Gate-Source-Spannung (U<sub>GS2</sub>) für den Gate-Kontakt (11) des Leistungstransistors (12) zu erzeugen und an dem Ausgang (20) der Treiberschaltung (200) zur Verfügung zu stellen.

- 2. Treiberschaltung (200) nach Anspruch 1, wobei die voreingestellte Mindestzeitspanne derjenigen Zeitspanne entspricht, die von einer mit dem Leistungstransistor (12) verbundenen Kurzschluss-Erkennungsschaltung benötigt wird, um einen Kurzschluss bei der Einschaltung des Leistungstransistors (12) zu erkennen und eine Abschaltung des Leistungstransistors (12) einzuleiten und/oder vorzunehmen.

- 3. Treiberschaltung (200) nach einem der vorhergehenden Ansprüche, wobei die Treiberschaltung (200) zwei verschiedene Spannungsquellen (SQ1, SQ2) umfasst, mittels welchen die erste und die zweite Gate-Source-Spannung ( $U_{\rm GS1}$ ;  $U_{\rm GS1}$ ) erzeugbar und am Ausgang (20) der Treiberschaltung (200) zur Verfügung stellbar sind.

- 4. Treiberschaltung (200) nach Anspruch 3, wobei die zwei verschiedenen Spannungsquellen (SQ1; SQ2) jeweils einen mit dem Anschluss (10) der Treiberschaltung (200) verbundenen Eingang sowie jeweils einen Spannungsausgang haben, wobei der Spannungsausgang der ersten Spannungsquelle (SQ1) über eine Reihenschaltung aus einer ersten Diode (21) und einem ersten Widerstand (31) mit dem Ausgang (20) der Treiberschaltung (200) verbunden ist, während der Spannungsausgang der zweiten Spannungsquelle (SQ2) über eine Parallelschaltung zweier Pfade (P1, P2) mit dem Ausgang (20) der Treiberschaltung (200) verbunden ist, wobei in jedem der Pfade eine Diode (32, 42) und/oder ein Widerstand (52, 62) vorgesehen ist.

- 5. Treiberschaltung (200) nach Anspruch 4, ferner umfassend eine Ansteuerschaltung, welche die Spannungsquellen (SQ1; SQ2) entsprechend eines vorbestimmten Algorithmus betreibt.

- 6. Treiberschaltung (200) nach einem der vorhergehenden Ansprüche, wobei zwischen dem Ausgang (20) und dem Anschluss (10) der Treiberschaltung (200) mindestens eine Spannungsquelle (SQ3) vorgesehen ist, mittels welcher der Ausgang (20) der Treiberschaltung (200) mit einer Spannung beaufschlagbar ist, wobei mindestens eine Induktivität (L1) mittels eines Schaltmittels (S1) dem elektrischen Pfad zwischen der mindestens einen Spannungsquelle und dem Anschluss (10) reversibel hinzuschaltbar ist.

- 7. Treiberschaltung (200) nach Anspruch 6, ferner umfassend eine weitere Spannungsquelle (SQ4), welche mit der Induktivität (L1) in Reihe geschaltet ist und mittels des Schaltmittels (S1) gemeinsam mit der Induktivität (L1) dem elektrischen Pfad zwischen der mindestens einen Spannungsquelle (SQ3) und dem Anschluss (10) reversibel hinzuschaltbar ist.

- 8. Treiberschaltung (200) nach Anspruch 7, wobei mindestens eine der Spannungsquellen (SQ1, SQ2, SQ3, SQ4) der Treiberschaltung (200) einen linearen Regler, einen RC Spannungsteiler, mindestens einen Bipolar-Transistor und/oder eine Bootstrap-Schaltung aufweist und/oder wobei mindestens eine der Spannungsquellen (SQ1, SQ2, SQ3, SQ4) der Treiberschaltung (200) unter Verwendung einer Bipolar-Transistor-Struktur und/oder einer MOSFET-Struktur, insbesondere als ASIC oder mittels diskreter Bauteile, realisiert ist.

- 9. Niederinduktives Leistungsmodul (400) mit einer Treiberschaltung (200) nach einem der Ansprüche 1 bis 8, umfassend einen Leistungstransistor (12) mit einem Source-Kontakt (15) und einem Gate-Kontakt (11), wobei der Source-Kontakt (15) mit dem Anschluss (10) der Treiberschaltung (200) und der Gate-Kontakt (11) mit dem Ausgang (20) der Treiberschaltung (200) verbunden ist.

- 10. Niederinduktives Leistungsmodul (400) nach Anspruch 9, wobei der Leistungstransistor ein Siliziumcarbid-MOSFET ist.

Es folgen 3 Seiten Zeichnungen

# Anhängende Zeichnungen

Fig. 1

Fig. 2

Fig. 3

Fig. 4

Fig. 5