(19) **日本国特許庁(JP)**

# (12) 特許公報(B2)

(11)特許番号

特許第5145666号 (P5145666)

(45) 発行日 平成25年2月20日(2013.2.20)

(24) 登録日 平成24年12月7日(2012.12.7)

| (51) Int.Cl. | FI                          |                     |                 |

|--------------|-----------------------------|---------------------|-----------------|

| HO1L 29/786  | <b>(2006.01)</b> HO 1       | , 29/78 626A        |                 |

| HO1L 21/288  | <b>(2006.01)</b> HO 1       | . 21/288 Z          |                 |

| HO1L 21/336  | <b>(2006.01)</b> HO 1       | , 29/78 6 1 7 K     |                 |

| HO1L 51/05   | <b>(2006.01)</b> HO 1       | , 29/78 6 1 8 B     |                 |

|              | HO1                         | , 29/78 626C        |                 |

|              |                             | 講求項の数 9             | (全 21 頁) 最終頁に続く |

| (21) 出願番号    | 特願2006-209239 (P2006-20923  | (73) 特許権者 000006747 |                 |

| (22) 出願日     | 平成18年7月31日 (2006.7.31)      | 株式会社リコ              | _               |

| (65) 公開番号    | 特開2008-34760 (P2008-34760A) | 東京都大田区              | 中馬込1丁目3番6号      |

| (43) 公開日     | 平成20年2月14日 (2008.2.14)      | (74)代理人 100070150   |                 |

| 審査請求日        | 平成21年4月23日 (2009.4.23)      | 弁理士 伊東              | 忠彦              |

|              |                             | (72)発明者 近藤 浩        |                 |

|              |                             | 東京都大田区              | 中馬込1丁目3番6号 株式   |

|              |                             | 会社リコー内              |                 |

|              |                             | 審査官 竹口 泰裕           |                 |

最終頁に続く

## (54) 【発明の名称】電子素子、電流制御ユニット、電流制御装置、演算装置及び表示装置

## (57)【特許請求の範囲】

## 【請求項1】

基板上に形成された溝内部が、導電層、半導体層、絶縁層及び第一の電極層が順次積層された構造、又は半導体層、導電層、絶縁層及び第一の電極層が順次積層された構造であり、さらに、該半導体層と接し、かつ該導電層と接していない第二の電極層及び第三の電極層が形成され、

前記基板の表面がエネルギー付与により少なくとも臨界表面張力の大きな高表面エネルギー部と、より臨界表面張力の小さな低表面エネルギー部との二つの部位を含み、

前記溝の側面は前記低表面エネルギー部であり、

前記溝の底面、及び、前記溝の側面を介して前記溝の底面と連続する前記基板上の所定 領域は前記高表面エネルギー部であり、

前記溝の底面の前記高表面エネルギー部に前記導電層が形成され、前記所定領域の前記 高表面エネルギー部に前記第二の電極層及び前記第三の電極層が形成され でいることを特 徴とする電子素子。

#### 【請求項2】

前記第二の電極層、第三の電極層及び導電層が同一の材料からなることを特徴とする請求項1に記載の電子素子。

#### 【請求項3】

前記第一の電極層、第二の電極層、第三の電極層、導電層及び半導体層の少なくとも一つが塗布可能な材料からなることを特徴とする請求項1に記載の電子素子。

20

#### 【請求項4】

前記第二の電極層、第三の電極層及び導電層薄膜の半導体接触部位と半導体非接触部位とで仕事関数が異なることを特徴とする請求項1乃至<u>3</u>のいずれか一項に記載の電子素子

## 【請求項5】

溝が形成された基板の表面にエネルギーを付与し、少なくとも臨界表面張力の大きな高表面エネルギー部と、より臨界表面張力の小さな低表面エネルギー部との二つの部位を形成する第1工程と、

<u>前記</u>基板上に複数の電子素子の第二の電極層、第三の電極層及び導電層を、第一の粒子 分散液を用いてインクジェット法によりパターニングして形成する第2工程と、

該第一の粒子分散液に含まれる金属の仕事関数に応じて該電子素子の必要な部位のみに電圧が印加するように接続し、該第一の粒子分散液に含まれる金属とは反対の仕事関数を有する電解メッキ中に基板を浸漬させて、該部位に該電解メッキの薄膜を積層して成膜し、

該電子素子間の配線電極を第二の粒子分散液を用いてパターニングす<u>る第3工程と、を</u>有し、

前記第1工程では、前記溝の側面は前記低表面エネルギー部となり、前記溝の底面、及び、前記溝の側面を介して前記溝の底面と連続する前記基板上の所定領域は前記高表面エネルギー部となり、

前記第2工程では、前記溝の底面の前記高表面エネルギー部に前記導電層を形成し、前 記所定領域の前記高表面エネルギー部に前記第二の電極層及び前記第三の電極層を形成す ることを特徴とする電子素子の製造方法。

#### 【請求項6】

請求項1乃至<u>4</u>のいずれか一項に記載の電子素子、第一の電極層に電圧を印加する第一の電圧制御デバイス並びに第二の電極層及び第三の電極層に電圧を印加する第二の電圧制御デバイスを有し、該第一の電圧制御デバイス及び第二の電圧制御デバイスを用いて、該第二の電極層及び第三の電極層の間を流れる電流を制御することを特徴とする電流制御ユニット。

#### 【請求項7】

請求項<u>6</u>に記載の前記電流制御ユニットが基板上に形成されていることを特徴とする電流制御装置。

## 【請求項8】

請求項1乃至4のいずれか一項に記載の電子素子、請求項6に記載の電流制御ユニットまたは請求項7に記載の電流制御装置を有することを特徴とする演算装置。

#### 【請求項9】

対向して設けられている二つの基板の対向する面の一つに形成されている電極間の電圧 または電流の変化によって表示の切替を行う表示装置において、

請求項1乃至<u>4</u>のいずれか一項に記載の電子素子、請求項<u>6</u>に記載の電流制御ユニット、または請求項<u>7</u>に記載の電流制御装置が画素スイッチングまたは画素駆動に用いられていることを特徴とする表示装置。

【発明の詳細な説明】

#### 【技術分野】

## [0001]

本発明は、低コストで作製でき、寄生容量が低減され、高速応答が可能な電子素子に関し、さらに、該電子素子を有する電流制御ユニット、電流制御装置、演算装置及び表示装置に関するものである。

## 【背景技術】

#### [0002]

現在、情報表示等の目的に用いられる代表的な表示装置はCRT、液晶表示装置、EL表示 装置である。CRTは比較的低い装置コスト、高い表示品質の点で従来から今日に至るまで 10

20

30

40

10

20

30

40

50

表示装置として広く用いられてきたが、ブラウン管の小型化、低消費電力化が困難である。こういった背景から液晶表示装置、さらに最近はEL表示装置の需要が急速に高まってきている。また、非接触でデータを読み出しや書込みが可能なICタグは、物流・個人情報管理用途に今後大きな市場が期待されており、この中には多数の演算素子が組み込まれている。

#### [0003]

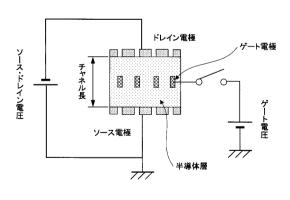

一方表示素子・演算素子に用いられる一般的な能動素子は、半導体材料、第一の電極( ゲート電極)、第二の電極(ソース電極)、第三の電極(ドレイン電極)を有したトラン ジスタ構造である。このトランジスタの一般的な構造としては、プレナー型、逆スタガー 型が挙げられる。

## [0004]

この半導体材料については、近年塗布プロセスの適用が可能な有機半導体材料の開発が 盛んに行われている。塗布による製造が可能な有機半導体デバイスは、真空成膜プロセス を用いる必要がないため、製造コストの大幅なコストダウンが可能となる利点を有する。

#### [00005]

近年塗布可能な材料で高移動度材料として、ポリチオフェン材料が注目されてきているが、(非特許文献 1 参照)、その移動度は0.1 cm²/V・秒未満であり現状のアモルファスシリコンと比較しても一桁近く小さい。このため高速応答の指標である遮断周波数について、一般に有機半導体材料を用いたトランジスタの場合はKHzレベルオーダーであり、一般に数MHz以上の遮断周波数が必要となる高精細な動画表示素子の駆動や、ICタグに用いることはできない。

#### [0006]

この遮断周波数の向上させる手段としては、半導体材料の移動度向上以外に、トランジスタのチャネル長の短チャネル化が挙げられる。しかし、1 μm前後からそれ以下のチャネル長にソース・ドレイン間距離をパターニングするためには、一般に煩雑な工程や高額の製造装置が必要であるため、製造コストが増加するという問題がある。

#### [0007]

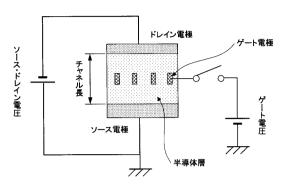

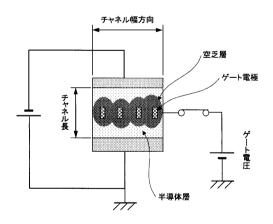

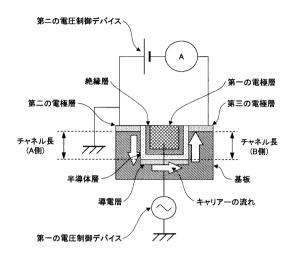

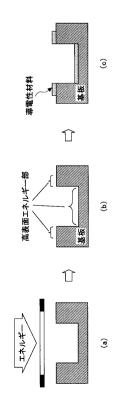

このような問題を解決するために、ソース電極、ゲート電極、ドレイン電極を順次積層したSIT構造(図2及び3参照)が一般に知られている。SIT構造の場合、ソース/ドレイン間の電流のON/OFFは、図3に示すように、ゲート電圧の印加による半導体層の空乏層領域の増加により、ソース/ドレイン間の抵抗値を増大させ、この間を流れる電流値を制御している。

#### [00008]

図2から判るように、SIT構造のチャネル長は半導体層の膜厚によって制御可能であるため、短チャネル化においては作製プロセスが非常に容易であり、高速応答のトランジスタとして期待されている。しかしながら、SIT構造は、ゲート電極の間隔が大きくなると、空乏層がチャネル幅方向全域に広がらず、この場合OFF時の電流が大きくなるという問題を有する。このため、ゲート電極の間隔が1μm未満になるようにパターニングする必要があり、製造プロセスには煩雑な工程が必要となる。

#### [0009]

さらに、遮断周波数を向上させるためには、素子内部の寄生容量の低減が必要である。例えば、図1(a)の場合は、ゲート電極及びソース電極の間、並びにゲート電極及びドレイン電極の間にゲート絶縁膜を狭持することで寄生容量が形成されている。寄生容量が大きい場合は、ゲート電圧の印加によって回路動作に無関係な部位に充電を行うこととなるため、高速応答が困難なものとなる。また、ゲート電圧が高周波の場合は、コンデンサによるインピーダンスが非常に小さくなるため、ゲート電流がソース電極及びドレイン電極に流れ、素子の消費電力が非常に大きくなり、特に、モバイル用途のようにバッテリー駆動するアプリケーションには適用が困難になる。

#### [0010]

したがって、プレナー型の場合、ゲート電極と、ソース電極及びドレイン電極は、殆ど

(4)

重ならないようにアライメントする必要が生じるが、特に、基板の材料が樹脂フィルムのように収縮しやすい材質である場合に、このアライメントは、面積が大きくなるほど、困難となる。

## [0011]

SIT構造の場合も同様に、図2の場合は、ゲート電極とソース電極、ドレイン電極が半導体層を狭持することで寄生容量が形成され、高速動作・低消費電力化において不具合が生じる。また、微細加工されたゲート電極と重ならない様にソース電極及びドレイン電極を図4のようにアライメントするのは非常に困難である。

#### [0012]

そこで、特許文献1には、基板上に形成され、凸部を有する第一の電極と、上記第一の電極を覆う絶縁層と、上記絶縁層上に形成され、上記第一の電極の凸部の上方に位置する第二の電極と、上記第一の電極の凸部の両側のうちの少なくとも一方に、上記絶縁層を介して位置すると共に、上記第一の電極の凸部の高さよりも低い第三の電極と、上記第二の電極と第三の電極とに接する一方、上記絶縁層によって上記第一の電極と隔てられた半導体層とを備えることを特徴とする電界効果トランジスタが開示されている。

#### [0013]

また、特許文献 2 には、(A)基体上に形成され、頂面、第一の側面及び第二の側面を有し、断面形状が略四角形のゲート電極、(B)ゲート電極の頂面、第一の側面、及び第二の側面に形成された絶縁膜、(C)ゲート電極の頂面上に位置する絶縁膜の部分の上に形成された第一のソース / ドレイン電極、(D)ゲート電極の第一の側面に面する基体の部分の上に形成された第三のソース / ドレイン電極、並びに、(F)第二のリース / ドレイン電極がら第一のリース / ドレイン電極、並びに、(F)第二のリース / ドレイン電極がら第一のソース / ドレイン電極と、第一のソース / ドレイン電極と、第一のソース / ドレイン電極と、ゲート電極と、第一のソース / ドレイン電極と、ゲート電極と、第一のリース / ドレイン電極とが新聞の部分の上に形成された半導体材料層の部分の上に形成された半導体材料層の部分がら成る第一のチャネル形成領域と、第二のソース / ドレイン電極と、分が高速によって第二の電界効果型トランジスタが構成され、ゲート電極と、第一のソース / ドレイン電極と、分がら成る第二のチャネル形成領域と、第三のソース / ドレイン電極とによって第二の電界効果型トランジスタが構成されていることを特徴とする電界効果型トランジスタが開示されている。

## [0014]

しかしながら、これらの構成は、短チャネル化は容易であるが、いずれもゲート電極の 頂部をソース電極又はドレイン電極として用いるため、ゲート電極とソース電極又はドレ イン電極間に寄生容量が形成され、高速応答することが困難となる。

【特許文献1】特開2005-19446号公報

【特許文献2】特開2004-349292号公報

【非特許文献 1】Applied Physics Letter, vol.69. p4108 (1996)

【発明の開示】

【発明が解決しようとする課題】

## [0015]

したがって、本発明は上述に鑑みてなされたものであり、上記問題点を解決し、低コストで作製することができ、寄生容量を低減して、高速応答を実現したトランジスタを提供することを目的とする。

【課題を解決するための手段】

## [0016]

本発明者らは、上述の課題を解決するために鋭意検討した結果、本発明を完成するにいたった。

#### [0017]

本電子素子は、基板上に形成された溝内部が、導電層、半導体層、絶縁層及び第一の電

10

20

30

極層が順次積層された構造、又は半導体層、導電層、絶縁層及び第一の電極層が順次積層された構造であり、さらに、該半導体層と接し、かつ該導電層と接していない第二の電極層及び第三の電極層が形成され、前記基板の表面がエネルギー付与により少なくとも臨界表面張力の大きな高表面エネルギー部と、より臨界表面張力の小さな低表面エネルギー部との二つの部位を含み、前記溝の側面は前記低表面エネルギー部であり、前記溝の底面、及び、前記溝の側面を介して前記溝の底面と連続する前記基板上の所定領域は前記高表面エネルギー部であり、前記溝の底面の前記高表面エネルギー部に前記導電層が形成され、前記所定領域の前記高表面エネルギー部に前記第二の電極層及び前記第三の電極層が形成されていることを特徴とする。

#### 【発明の効果】

[0028]

本発明によれば、低コストで作製することが可能で、寄生容量が低減でき、高速応答することが可能な電子素子、該電子素子を有する電流制御ユニット及び該電流制御ユニットを有する電流制御装置を提供でき、さらに、該電子素子、電流制御ユニットまたは電流制御装置を有する演算装置及び表示装置を提供することができる。

【発明を実施するための最良の形態】

[0029]

次に、本発明を実施するための最良の形態を図面と共に説明する。

[0030]

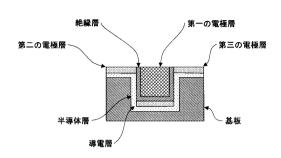

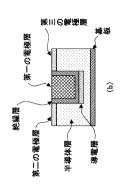

本発明の電子素子は、図5、6に示すように、基板上に形成された溝内部が、導電層、半導体層、絶縁層及び第一の電極層が順次積層された構造であるか、又はその溝内部が半導体層、導電層、絶縁層及び第一の電極層が順次積層された構造に形成されており、さらに、その構造において、該半導体層と接し、かつ該導電層と接していない2つの電極として第二の電極層及び第三の電極層が形成されている。本発明において、導電層は、第二の電極層及び第三の電極層と接触していない。また、少なくとも第一の電極層の厚さによって、導電層と、第二の電極層及び第三の電極層の間隔(チャネル長)が規定されている。このため、本発明の電子素子は、短チャネル化が容易である。

[0031]

また、本発明の電流制御装置は、図5に示すように、本発明の電子素子と、第一の電極層に電圧を印加する第一の電圧制御デバイス並びに第二の電極層及び第三の電極層に電圧を印加する第二の電圧制御デバイスを用いて、第二の電極層及び第三の電極層の間を流れる電流を制御する電流制御ユニットを有する。このとき、電流制御ユニットは、基板上に形成されていることが好ましい。

[0032]

遮断周波数f c に関し、Appl.Phys.Lett.,vol.76, No.14, 3 April(2000),1941-1943では、式(1)

$fc = \mu Vd / 2 L^{2}$

が実験値と良い一致を見ることが報告されている。ここで、μは、キャリア移動度、Vdは ソース・ドレイン電圧、Lはチャネル長である。これにより、寄生容量が無視してよい位 に小さい場合には、短チャネル化によって高速応答が可能となることがわかる。

[0033]

本発明の電子素子は、第一の電極層と、第二の電極層及び第三の電極層が重ならないようにセルフアライメントされるため、寄生容量の低減が容易である。また、第一の電極層と導電層の間に寄生容量が形成されるが、電圧が印加されるのは第一の電極層と、第二の電極層及び第三の電極層の間であるため、この寄生容量に充電を行うためには、半導体層を介することとなる。ここで、半導体層の抵抗は、配線抵抗と比較して、ON時においても非常に高いため、見かけ上、寄生容量があったとしても、第一の電極層に電圧を印加することによって、第一の電極層と導電層の間に充電されることは殆ど無い。このため、寄生容量を実質的に低減させることができ、高速応答することが可能となる。また、第一の電極層に印加する電圧を高周波駆動としても半導体層の抵抗によってゲート電流が第二の

10

20

30

40

10

20

30

40

50

電極層及び第三の電極層に流れることが殆ど無いため、消費電力も抑えることが可能となる。

#### [0034]

図5に示すように、本発明の電流制御装置においては、第一の電圧制御デバイスが第一の電極層に電圧を印加すると、第二の電極層と導電層(図5中、チャネルA側)、及び導電層と第三の電極層(図5中、チャネルB側)間にチャネルが形成され、この状態で第二の電圧制御デバイスによって、第二の電極層と第三の電極層の間に電圧が印加された場合、キャリアは第二の電極から半導体層を通って導電層に入り、導電層から半導体層に注入され、さらに第三の電極へと流れる。

#### [0035]

本発明において、第一の電極層、第二の電極層、第三の電極層及び導電層には、クロム(Cr)、Ta(タンタル)、チタン(Ti)、銅(Cu)、アルミニウム(Al)、モリブデン(Mo)、タングステン(W)、ニッケル(Ni)、金(Au)、パラジウム(Pd)、白金(Pt)、銀(Ag)、錫(Sn)等の金属、ITO、IZO等の合金、ポリアセチレン系導電性高分子、ポリパラフェニレン及びその誘導体、ポリフェニレンとびその誘導体などのポリフェニレン系導電性高分子、ポリピロール及びその誘導体、ポリチオフェン及びその誘導体、ポリフラン及びその誘導体などの複素環系導電性高分子、ポリアニリン及びその誘導体などのイオン性導電性高分子のうち少なくとも1種を用いることができる。なお、これらの金属、合金、導電性高分子を併用することも可能である。

#### [0036]

また、これら導電性高分子は、適当なドーパントをドーピングすることにより導電率を高くして用いてもよい。ドーピングに用いられるドーパントとしては、ポリスルホン酸、ポリスチレンスルホン酸、ナフタレンスルホン酸、アルキルナフタレンスルホン酸などの蒸気圧の低いものを用いるのが好ましい。

#### [0037]

本発明において、これら第一の電極層、第二の電極層、第三の電極層及び導電層の体積抵抗率は、通常、 $1 \times 10^{-3}$  ・cm以下、 $1 \times 10^{-6}$  ・cm以下が好ましい。

#### [0038]

本発明において、半導体層には、フルオレン、ポリフルオレン誘導体、ポリフルオレノ ン、フルオレノン誘導体及び、ポリ - N - ビニルカルバゾール誘導体、ポリ - - カルバ ゾリルエチルグルタメート誘導体、ポリビニルフェナントレン誘導体、ポリシラン誘導体 、オキサゾール誘導体、オキサジアゾール誘導体、イミダゾール誘導体、モノアリールア ミン、トリアリールアミン誘導体等のアリールアミン誘導体、ベンジジン誘導体、ジアリ ールメタン誘導体、トリアリールメタン誘導体、スチリルアントラセン誘導体、ピラゾリ ン誘導体、ジビニルベンゼン誘導体、ヒドラゾン誘導体、インデン誘導体、インデノン誘 導体、ブタジエン誘導体、ピレン・ホルムアルデヒド、ポリビニルピレン等のピレン誘導 - フェニルスチルベン誘導体、ビススチルベン誘導体等のスチルベン誘導体、エナ ミン誘導体、ポリアルキルチオフェン等のチオフェン誘導体よりなる群から選ばれる少な くとも1種の有機半導体材料、或いは、ペンタセン、テトラセン、ビスアゾ、トリスアゾ 系色素、ポリアゾ系色素、トリアリールメタン系色素、チアジン系色素、オキサジン系色 素、キサンテン系色素、シアニン系色素、スチリル系色素、ピリリウム系色素、キナクリ ドン系色素、インジゴ系色素、ペリレン系色素、多環キノン系色素、ビスベンズイミダゾ ール系色素、インダンスロン系色素、スクアリリウム系色素、アントラキノン系色素、及 び、銅フタロシアニン、チタニルフタロシアニン等のフタロシアニン系色素等の有機半導 体材料、並びにCdS、ZnO、PbTe、PbSnTe、InGaZnO、GaP、GaAIAs、GaN等の化合物半導体 、多結晶シリコン、アモルファスシリコン等のシリコン半導体材料が適用可能である。中 でも、塗布可能な材料以外で、低コスト化するためには、アモルファスシリコンが好まし い。また、アモルファスシリコンは、TFTの耐久性、動作安定性の面からも好ましい。

## [0039]

本発明において、絶縁層としては、基板材料は、SiO $_2$ 、Ta $_2$ O $_5$ 、Al $_2$ O $_3$ 等の無機絶縁材

料、ポリイミド樹脂、スチレン樹脂、ポリエチレン系樹脂、ポリプロピレン、塩化ビニル系樹脂、ポリエステルアルキド樹脂、ポリアミド、ポリウレタン、ポリカーボネート、ポリアリレート、ポリスルホン、ジアリルフタレート樹脂、ポリビニルブチラール樹脂、ポリエーテル樹脂、ポリエステル樹脂、アクリル樹脂、シリコーン樹脂、エポキシ樹脂、フェノール樹脂、尿素樹脂、メラミン樹脂、PFA、PTFE、PVDF等のフッ素系樹脂、パリレン樹脂、エポキシアクリレート、ウレタン・アクリレート等の光硬化性樹脂、プルラン・セルロース等の多糖類及びその誘導体等の有機絶縁材料を用いることができる。

#### [0040]

本発明において、絶縁層の体積抵抗率が $1 \times 10^{13}$  ・cm以上であることが好ましく、 $1 \times 10^{14}$  ・cm以上がさらに好ましい。

[0041]

本発明において、絶縁層は、蒸着、スパッタ、CVD等の真空成膜プロセス、陽極酸化法、又は凸版を用いる印刷法、例えばフレキソ印刷、孔版を用いる印刷法、例えばスクリーン印刷、平版を用いる印刷法、例えばグラビア印刷、またスピンコート法、ディッピング法、スプレーコート法、インクジェット法等の印刷法を用いて形成することができる。

[0042]

本発明において、基板としては、ガラス、表面に上記の絶縁材料をコーティングした金属材料、上記の絶縁材料と同様の樹脂材料をフィルム化したもの等を用いることができる

[0043]

また、本発明においては、第一の電極層が形成された部位に対して、一義的に、第二の電極層、第三の電極層及び導電層の位置を決定することができるため、アライメントが容易となり、製造コストを低減することが可能となる。なお、第二の電極層、第三の電極層及び導電層は、別々のプロセスで形成しても良いし、同時に形成してもよい。また、第二の電極層、第三の電極層及び導電層を形成した後に、チャネル部に導電性材料が付着している場合は、これらの材料を溶解する液体に浸漬してもよい。

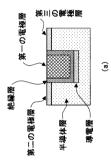

[0044]

本発明において、溝の断面形状は、基板表面に対して60°以上の角度で立ち上がっている部位を有することが好ましく、80°以上がさらに好ましく、90°以上が特に好ましい。これにより、第二の電極層及び第三の電極層と、導電層との距離(チャネル長)を規定し易くなる。図7(a)は、溝が基板の表面に対して完全に90°で立ち上がっている状態であるが、図7(b)のように、溝の一部が基板の表面に対して90°で立ち上がっている状態でもよい。また図7(c)は、基板の表面に対して、90°よりも大きな角度で立ち上がっている状態である。これらの状態は、いずれも本発明に好ましい状態である。

[0045]

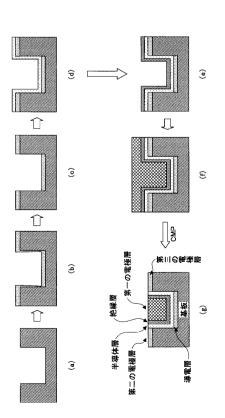

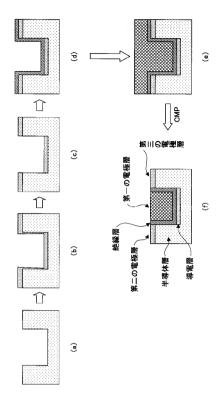

図8に、本発明の電子素子の作製プロセスの流れを示す。この図8は、図1の電子素子を作製する場合のプロセスの一例である。

[0046]

図8(b)のプロセスで形成された導電層の材料は、図8(b)にあるように、基板に形成された溝の側壁に付着する場合がある。この場合は、エッチング処理を行うことにより、図8(c)のように側壁に付着した導電性材料を除去することが望ましい。

[0047]

また、図8(f)の構造を作製した後、図8(g)の構造を作製するためには、CMP(化学的機械研磨)法によると、簡便に作製することが可能となる。

[0048]

この図 8 の電子素子の作製プロセスにおいては、絶縁層と半導体層の少なくとも一方は CVDで形成されることによって、膜表面形状が、基板に形成された溝形状を忠実に反映することが可能となる。

10

20

30

40

#### [0049]

本発明において、基板に形成された溝形状の作製方法としては、基板上にレジストを所望の形状にパターニングし、これをウェットエッチング、ドライエッチングする方法、凸形状を有する金型を基板に押厚するスタンパー法等が挙げられるが、特に、スタンパー法が簡便で好ましい。スタンパー法を用いる場合、図8(c)の構成を得るために、図9のプロセスも好ましく適用できる。

#### [0050]

本発明の電子素子は、図10に示すように、半導体材料中に形成された溝内部が、導電層、絶縁層及び第一の電極層が順次積層された構造であり、さらに、該半導体と接し、かつ該導電層と接していない第二の電極層及び第三の電極層が形成されている。したがって、短チャネル化、寄生容量の実質的な低減によって、高速応答が可能となる。

#### [0051]

本発明における半導体基板としては、単結晶シリコンの他、上記に記載の半導体材料が適用可能である。また図10(b)のように、上記に記載の半導体材料が、絶縁性基板上に形成され、かつ、この半導体材料に溝形状が形成されていても良い。その他、絶縁層材料、電極層材料も同様に上記に記載の材料が適用可能である。

#### [0052]

本発明の電子素子は、第二の電極層、第三の電極層及び導電層が同一の材料からなることが好ましい。これにより、第二の電極層、第三の電極層と導電層を同時に形成することができるため、電子素子を容易に製造することが可能となる。

#### [0053]

本発明において、第二の電極層、第三の電極層及び導電層は、蒸着、スパッタ、CVD等の真空成膜プロセス、または凸版を用いる印刷法、例えばフレキソ印刷、孔版を用いる印刷法、例えばスクリーン印刷、平版を用いる印刷法、例えばオフセット印刷、凹版を用いる印刷法、例えばグラビア印刷等の印刷プロセスが適用可能である。中でも、大面積化・プロセスタクト向上が容易であることから、フレキソ印刷、スクリーン印刷、オフセット印刷、グラビア印刷等の有版印刷法が好適である。

#### [0054]

本発明の電子素子は、第一の電極層、第二の電極層、第三の電極層、導電層及び半導体層の少なくとも一つが、塗布可能な材料からなることが好ましい。これにより、印刷プロセスを用いて電子素子を製造することが可能となり、スパッタ等の真空成膜プロセスを用いる場合と比較して、製造コストを低減させることが可能となる。

#### [0055]

本発明において、印刷法としては、凸版を用いる印刷法、例えばフレキソ印刷、孔版を用いる印刷法、例えばスクリーン印刷、平版を用いる印刷法、例えばオフセット印刷、凹版を用いる印刷法、例えばグラビア印刷、またスピンコート法、ディッピング法、スプレーコート法、インクジェット法等を用いることができる。中でも、大面積化、プロセスタクト向上が容易であることから、フレキソ印刷、スクリーン印刷、オフセット印刷、グラビア印刷等の有版印刷法が好ましい。

#### [0056]

本発明において、第一の電極層、第二の電極層、第三の電極層、導電層の塗工液としては、Ag、Au等のナノ粒子を溶媒中に分散した金属ナノ粒子分散液、ポリアセチレン系導電性高分子、ポリパラフェニレン及びその誘導体、ポリフェニレン及びその誘導体などのポリフェニレン系導電性高分子、ポリピロール及びその誘導体、ポリチオフェン及びその誘導体、ポリフラン及びその誘導体などの複素環系導電性高分子、ポリアニリン及びその誘導体などのイオン性導電性高分子のうち少なくとも1種を溶媒に分散又は溶解した溶液を用いることができる。また、これら導電性高分子は、適当なドーパントをドーピングすることにより導電率を高くして用いてもよい。ドーパントとしては、ポリスルホン酸、ポリスチレンスルホン酸、ナフタレンスルホン酸、アルキルナフタレンスルホン酸等の蒸気圧の低い化合物を用いることが好ましい。

10

20

30

40

#### [0057]

本発明の電子素子は、その表面がエネルギー付与により少なくとも臨界表面張力の大きな高表面エネルギー部と、より臨界表面張力の小さな低表面エネルギー部との二つの部位となり、第二の電極層、第三の電極層及び導電層のうち少なくとも一つが塗布可能な材料からなることが好ましい。

#### [0058]

したがって、低コスト且つ高精細に、第二の電極、第三の電極及び導電層のパターニングを行うことが可能となる。

## [0059]

本発明において、高表面エネルギー部と低表面エネルギー部とのパターン形状に従って 導電性材料を含有する液体を確実に付着させるためには、表面張力差が大きいことが望ま しい。本発明ではこの差が10mN/m以上であることが好ましく、この値以上であれば確 実に導電性材料が含有した液体を、絶縁層表面に付着させることができる。

#### [0060]

図11に本発明の電子素子の構成の一例を示す。ここでは、低表面エネルギー部となっている基板上に、エネルギーを付与し局所的に高表面エネルギー部とした後、導電性材料を含む液体を高表面エネルギー部に塗布した構成の例である。このとき溝側面部は、エネルギーが付与され難いため、低表面エネルギー部のままとなり、導電性材料が付着しない

## [0061]

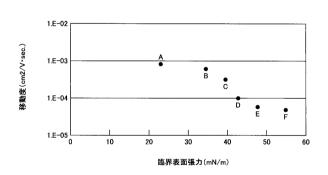

また本発明においては、低表面エネルギー部の臨界表面張力が、40mN/mより小さいことが好ましい。これにより、半導体層の移動度を高くすることができると共に、低表面エネルギー部での液体反発性が良好なものとなり、第二の電極、第三の電極、導電層の良好なパターニングを行なうことが可能となる。

#### [0062]

図12に、半導体層の移動度と絶縁層の臨界表面張力の関係を示す。なお、このプロットは、構造式(1)

#### [0063]

#### 【化1】

$OC_{10}H_{21}$   $OC_{10}H_{21}$   $OC_{10}H_{21}$   $OC_{10}H_{21}$   $OC_{10}H_{21}$   $OC_{10}H_{21}$

で表される有機半導体材料を用いて図1(a)のTFTを作製し、半導体層の移動度と絶縁層の臨界表面張力を測定することにより得られたものである。これより、臨界表面張力40mN/m前後における移動度の変化量は大きく、臨界表面張力が小さいほど移動度が向上することが判る。

## [0064]

また、本発明において、基板材料はその表面に、エネルギーの付与によって臨界表面張

20

10

30

40

力が大きく変化する材料がコーティングされていても良い。

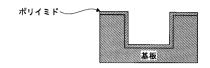

#### [0065]

このコーティングのための材料として、側鎖に疎水性基を含むポリイミド材料からなることが好ましい。ポリイミドは耐溶剤性並びに耐熱性に優れているため、溶媒や焼成による温度変化によって、膨潤したリクラックが入ったりするといったことが殆どない。したがって、信頼性の高い電子素子を作製することが可能となる。

#### [0066]

この側鎖に疎水性基を有するポリイミド材料としては、特開2002-162630公報、特開2003-96034公報、特開2003-267982公報等に記載されている材料を用いることができる。また、これら疎水性基の主鎖骨格を構成するテトラカルボン酸二無水物については、脂肪族系、脂環式、芳香族系など種々の材料を用いることが可能である。具体的には、ピロメリット酸二無水物、シクロブタンテトラカルボン酸二無水物、ブタンテトラカルボン酸二無水物等が挙げられる。この他に、特開平11-193345号公報、特開平11-193347号公報等に記載されている材料についても用いることが可能である。

#### [0067]

また、本発明において、臨界表面張力を変化させる際に用いられるエネルギーは、紫外線であることが好ましい。これにより、大気中で操作することができ、高い解像度が得られ、層内部に対する損傷を抑制することができる。

#### [0068]

本発明の電子素子は、第二の電極層、第三の電極層及び導電層薄膜の半導体接触部位と 半導体非接触部位とで仕事関数が異なることが好ましい。これにより、電極層及び導電層 の仕事関数の制御が容易なものとなる。

#### [0069]

半導体層と金属が接する部位には、半導体材料との仕事関数の整合が必要となる。特に、n型の半導体材料とp型の半導体材料が一枚の基板上に共存する場合、以下のような問題が生じることがある。すなわち、n型半導体の場合、金属材料の仕事関数が半導体よりも大きいと、金属から半導体へのキャリア注入は妨げられ、逆にp型半導体の場合、金属材料の仕事関数が半導体よりも小さいと、金属から半導体へのキャリア注入は妨げられる。したがって、キャリアの注入が妨げられないようにするためには、二種以上の電極材料が必要となるが、使用するp型半導体へのキャリア注入が妨げられないよう、このp型半導体よりも大きな仕事関数を持つ電極材料を第二の電極層、第三の電極層及び導電層材料として形成した後、使用するn型半導体よりも小さな仕事関数を持つ電極材料を、n型半導体と接触する部位のみに積層することが好ましい。

#### [0070]

本発明において、p型の半導体材料を用いて半導体層を形成する場合、第二の電極層、第三の電極層及び導電層の最表面部は、Ag、Au、Pt等の仕事関数が大きい導電性材料で形成されていることが好ましい。また、n型の半導体材料を用いて半導体層を形成する場合、第二の電極層、第三の電極層及び導電層の最表面部は、Mg、AI、Cr等の仕事関数が小さい導電性材料で形成されていることが好ましい。

## [0071]

本発明において、第二の電極層、第三の電極層及び導電層は、蒸着、スパッタ、CVDといった真空成膜プロセス、または凸版を用いる印刷法、例えばフレキソ印刷、孔版を用いる印刷法、例えばスクリーン印刷、平版を用いる印刷法、例えばオフセット印刷、凹版を用いる印刷法、例えばグラビア印刷、またスピンコート法、ディッピング法、スプレーコート法、インクジェット法といった印刷法によって形成可能である。

#### [0072]

図13及び14に本発明の構成例を示す。ここでは、第二の電極層、第三の電極層及び 導電層が二種の金属からなり、膜厚方向における材料の分布を示している例である。図1 4は、例えば、図13(b)の状態を図5の電子素子に適用した場合、基板上に成膜され 10

20

30

40

る第二の電極層、第三の電極層及び導電層を示す。

#### [0073]

本発明の電子素子の製造方法は、上述した電子素子の構成において、第二の電極層、第三の電極層及び導電層の形成で、第一層目を形成後にその表面を電解メッキによって積層構造とすることが好ましい。電解メッキは、電圧が印加されている部位のみに選択合いをでは、電性材料が形成されるため、仮に基板が伸縮・変形した場合においても高度な位置合わせのプロセスを必要とせず、非常に簡便なプロセスにて、第二の電極層、第三の電極層及び導電層を積層構造とすることが可能となる。例えば、Au薄膜を形成した後、所望の方法は、Cr薄膜を積層する場合には図15に示す方法を用いることができる。なお、この方法は、基板上に、4個の電子素子をアレイ状に並べ、各々の素子を配線する場合の作製方法である。まず、第二、第三、導電層を、Auナノ粒子分散液を用いて、インクジェット法によりパターニングする(図15(a))。次に、Auより低い仕事関数が必要な部位のみを除するに接続し、Crの電解メッキ液中に基板を浸漬させ、所望の部位のみCr薄膜を積層成膜である。まず、第二、第三、導電層を、Auナノ粒子分散液を用いて、インクジェット法によりに接続し、Crの電解メッキ液中に基板を浸漬させ、所望の部位のみCr薄膜を積層があるともできる。Cr薄膜を先に形成した後にCrより高い仕事関数のAu薄膜を形成することもできる。

#### [0074]

本発明の電子素子を有する電流制御ユニットは、第一の電圧制御デバイスによる第一の電極層への電圧印加によって、さらに、第二の電圧制御デバイスによる第二の電極層及び第三の電極層への電圧印加によって、これら電極層間を流れる電流が制御されている。これによって、高速応答することが可能な電子素子を有する電流制御ユニットを提供でき、さらに、該電流制御ユニットが基板上に形成された電流制御装置を提供できる。

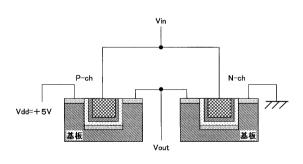

## [0075]

図16に本発明の電流制御装置を有する演算装置の構成例を示す。 p-ch、n-chはそれぞれ正孔輸送材を用いたトランジスタと、電子輸送材を用いたトランジスタを示している。ここで、Vinに+5Vを印加した場合、n-chはONとなるものの、p-chはOFFとなり、Voutは0Vとなる。また、Vinが0Vの時は、n-chはOFFとなり、またVddが+5Vであるためp-chのゲート・ソース間の電位差が5Vとなり、Voutは+5Vが出力される。このように、VinとVoutの電位が反転するため、図16の回路はインバータ回路として適用することが可能である。さらに、このインバータ回路、及びAND回路、NAND回路、NOR回路、XOR回路等の演算回路どうしを組合わせることで、制御装置を作製することができる。

#### [0076]

本発明は、基板上に溝を形成する装置、溝が形成された基板に導電層、第二の電極層及び第三の電極層を形成する装置、エッチングを行う装置、半導体層を形成する装置、絶縁層を形成する装置、並びに第一の電極層を形成する装置を具備する製造装置によって製造することができる。このため安価で製品を製造することが可能となる。図8には、本発明で用いる製造装置のプロセスフローが例示される。図8(a)では基板上に溝が形成され、これに導電層、第二の電極層及び第三の電極層を形成すると図8(b)となる。これにエッチングを行う事によって図8(c)となり、半導体層を成膜することで図8(d)となる。さらに絶縁層を成膜し図8(e)となり、第一の電極層を形成し図8(f)となる。最後にCMP(化学的機械研磨)によって図8(g)の素子が得られる。この図8(c)の工程の後、図15(a)~図15(c)に示されるような、表面に所望の金属のメッキを行うことも可能である。また、各々のプロセス全てが一体となった製造装置内で行うことも可能である。また適宜各々のプロセスが分離した製造装置であっても良い。

## [0077]

また、基板表面がエネルギーの付与によって臨界表面張力の異なる部位になる場合は、図8(a)の工程の後、紫外線等を照射する工程を設けても良い。

#### [0078]

本発明はまた、表面が半導体材料からなる基板上に溝を形成する装置、溝が形成された

10

20

30

40

基板に導電層、第二の電極層及び第三の電極層を形成する装置、エッチングを行う装置、 絶縁層を成膜する装置、並びに第一の電極層を形成する装置を具備する製造装置によって 製造することができる。このため安価な製品を製造可能となる。図17(a)~(g)に本発明 で用いる製造装置のプロセスフローが例示される。図17(a)では半導体に溝が形成され、 これに導電層、第二の電極層、第三の電極層を形成すると図17(b)となる。これにエッチ ングを行うことによって図17(c)となり、さらに絶縁層を成膜し図17(d)となり、第一 の電極層を形成し図17(e)となる。最後にCMP(化学的機械研磨)によって図17(f)の 素子が得られる。この図17(c)の工程の後、図15(a)~図15(c)に示されるような、 表面に所望の金属のメッキを行うことも可能である。また、各々のプロセス全てが一体と なった製造装置内で行うことも可能である。また適宜各々のプロセスが分離した製造装置 であっても良い。

10

#### [0079]

次に、本発明の表示装置を説明する。

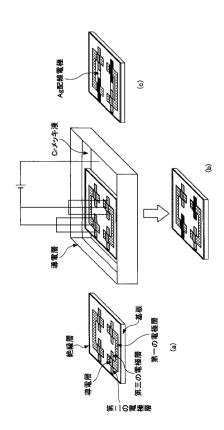

#### [0800]

本発明の表示装置は、対向して設けられている二つの基板の対向する面の一つに形成されている電極間の電圧値変化によって表示の切替を行う表示素子を用いて、上記の電子素子、電流制御ユニット、電流制御装置に適用できることが好ましい。したがって、低コストにて高速応答が可能な表示装置を作製できる。本発明における、対向している基板の対向面側に成膜されている電極間の電圧値変化によって表示を行う表示素子の例として、液晶表示素子、電気泳動表示素子、プラズマ表示素子等が挙げられる。

20

#### [0081]

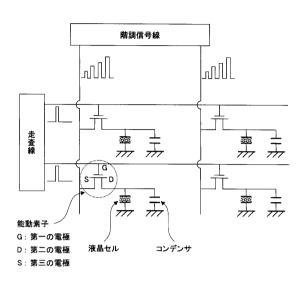

図18に、本発明の表示装置の一例として、液晶表示装置の構成例を示す。階調信号線からは各々の画素の階調にしたがって電圧が印加されている。走査線からは一ラインごと順次ON / OFFの信号電圧が印加され、一画面の走査が終了した後、次画面の走査が開始される。動画対応の場合、この間隔は50Hz以上(1/50sec.以下)であることが望ましい。コンデンサは、一画面から次画面の走査に移るまでの時間、階調信号の電圧を充電し、液晶セルに電圧を印加する機能を有する。

#### [0082]

本発明の表示装置は、対向して設けられている二つの基板の対向する面の一つに形成されている電極間を流れる電流によって表示の切替を行う表示素子を用いて、上記の電流制御ユニット、電流制御装置、電子素子を画素スイッチング、又は画素駆動に用いることを特徴とする。したがって、低コストで高速応答できる表示装置が作製可能となる。本発明の対向している基板の対向面側に成膜されている電極間に流れる電流によって表示を行う表示素子の例として、EL表示素子、エレクトロクロミック表示素子、エレクトロデポジション表示素子等が挙げられる。

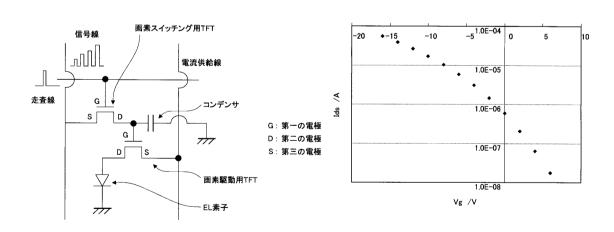

図19に、本発明の表示装置の一例として、EL表示装置の構成例を示す。これは、EL表示装置の1画素を取り出した構成図の例である。走査線から画素スイッチング用TFTに電圧が印加されると、コンデンサに電荷が充電され、画素駆動用TFTの第一の電極層に(図19中、G)電圧が印加され、電流供給線から電流がEL素子に供給され、発光する。コンデンサは、一画面から次画面の走査に移るまでの時間、電荷が充電されるため、画素駆動用TFTはON状態となり、EL素子の発光が継続する。

40

30

#### 【実施例】

#### [0083]

以下、実施例を挙げて本発明をさらに詳しく説明するが、これら実施例によって、本発明はなんら制限されるものではない。

## [0084]

#### (実施例1)

図 5 に示すような構成の電子素子を作製し、その電気特性の評価を行った。結果を図 2 0 及び 2 1 に示す。作製は図 8 に示す通りに行なった。

## [0085]

まず、ガラス基板を作製した。具体的には、バッファードフッ酸によりエッチングを行いガラス面に溝を形成後、ヘキサメチルジシラザンによりはっ水処理することにより、図8(a)の基板を作製した。Auからなる第二の電極層、Auからなる第三の電極層及びAuからなる導電層を蒸着により成膜した。成膜後に、Auエッチング液に浸漬した。その上に、構造式(1)で表される有機半導体材料(移動度 $3.3\times10^{-2}\,(\text{cm}^2/\text{V}\cdot\text{sec.})$ )からなる半導体層を成膜した。さらに、その上に、パレリンCからなる絶縁層をCVDにより、膜厚250nmで成膜した。最後、その上にA1からなる第一の電極層を幅9μmとして積層し、図5に示すような電子素子とした。得られた電子素子のチャネル長(チャネルA側及びチャネルB側の合計)は、2.9μmであった。

#### [0086]

第一の電源電圧(Vg)を+6~-16V、第二の電源電圧(Vds)を-16Vとして、各々の電圧を印加した時に流れる電流値を測定した。結果を図20に示す。このVgは第一の電圧制御デバイスの電圧値、Idsは第二の電極層と、第三の電極層間の電流値を示す。

ここから、Vg=Vds=-16Vの時に、5.8 × 10<sup>-5</sup> (A) の電流が得られ、Vg が+6~-16Vの範囲にて、ON/OFF比として 3 桁以上が得られていることが判る。

#### [0087]

第一の電源 (Vg) を -8 ~ -14 V (sin波)、第二の電源 (Vds) を -16 Vとし、第一の電圧制御デバイスの電源周波数を 1KHz ~ 600 KH z として、1KHz の時に得られたゲインを 1 とし、これが -3 db となる時の周波数を遮断周波数とした。結果を図 2 1 に示す。ここから、600 KH z 以上の遮断周波数が得られていることがわかる。

#### [0088]

本検討における、各々のパラメータから計算される遮断周波数は、ゲート電極(第一の電極層)が他の電極層(第二の電極層、第三の電極層)との重なりが無いことを前提とした前述の式(1)

$fc = \mu \, Vd \, / \, 2$   $L^2$  (  $\mu$ : キャリア移動度、Vd: 第二の電源電圧、L: チャネル長) より、約900KH z と推定される。したがって、実際のデバイス上では導電層と第一の電極層とは $9 \, \mu$ mもの重なりがあるにも関わらず、第一の電極層と他の電極の重なりが無い場合の、遮断周波数計算式に近い値が得られている。

#### [0089]

なお、重なりがある場合の遮断周波数の計算値(概算値)は、重なり幅をDとした時、 下記式

$f c = \mu V d / 2 L(D+L)$

で表される。このDが大きいほど、寄生容量が大きくなり、遮断周波数が小さくなることを意味する。

この式にD=9 $\mu$ mを代入すると、L=2.9 $\mu$ mの場合、fcはDが0の時の1/4程度に減少することが分かる。

## [0090]

#### (実施例2)

実施例1の絶縁層をポリイミド(X491;膜厚200nm)(チッソ社製)で成膜後、スタンパー法にて図22の形状の溝を形成した以外は、実施例1と同様にして、電子素子を作製した。

## [0091]

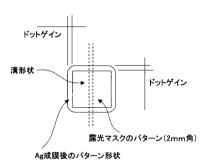

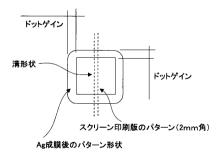

以下、上記のプロセスを具体的に説明する。第二の電極層、第三の電極層及び導電層に相当する形状の露光マスクを用いて、波長 250nmにおける照射エネルギーが $9J/cm^2$ の紫外線を絶縁層に照射した。次に、Agナノ粒子分散液(住友電気工業社製)を用いて、<math>Agからなる第二の電極層、<math>Agからなる第三の電極層及びAgからなる導電層を成膜した後、市販の<math>Agエッチング液に浸漬することによりエッチングした。

#### [0092]

また、上記の露光マスクと略同一パターンを有する印刷版を用い、スクリーン印刷法により、第二の電極層、第三の電極層、導電層を成膜した以外は、上記と同様にして電子素

10

20

30

40

子を作製した。 A g 成膜後のパターン形状と、露光マスクのパターンとの比較を行い、光学顕微鏡でドットゲインを測定したところ、図 2 3 に示すように最大で 6 μ m であることを確認した。

[0093]

さらにまた、紫外線照射を行なわずに、本実施例2の露光マスクと同一パターンのスクリーン印刷版を用いて、第二の電極層、第三の電極層及び導電層を成膜した以外は、本実施例2と同様にして、電子素子を作製した。Ag成膜後のパターン形状と、スクリーン印刷版のパターンとの比較を行い、光学顕微鏡でドットゲインを測定したところ、図24に示すように最大で20μmであることを確認した。

[0094]

10

以上、本発明の好ましい実施例について詳述したが、本発明はかかる特定の実施形態に限定されるものではなく、特許請求の範囲に記載された本発明の趣旨の範囲内において、種々の変形・変更が可能である。

【図面の簡単な説明】

[0095]

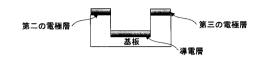

- 【図1】トランジスタの一般的な構造を示す図である。

- 【図2】SIT構造の能動素子の一般的な構造を示す図である。

- 【図3】SIT構造の能動素子の一般的な構造を示す図である。

- 【図4】SIT構造の能動素子の一般的な構造を示す図である。

- 【図5】本発明の電子素子及び電流制御ユニットの構成例を示す模式図である。

- 【図6】本発明の電子素子の別の構成例を示す模式図である。

- 【図7】本発明で用いられる基板の溝の断面形状を表す図である。

- 【図8】本発明の電子素子の作製プロセスの一連の流れを示す図である。

- 【図9】本発明で用いられる基板の溝形状の作製例を示す図である。

- 【図10】本発明の電子素子のまた別の構成例を示す模式図である。

- 【図11】本発明で用いられる基板へのエネルギー付与を示す図である。

- 【図12】本発明で用いられる半導体層の移動度と絶縁層の臨界表面張力の関係を示す図である。

- 【図13】本発明で用いられる第二の電極層、第三の電極層及び導電層の材料の膜厚方向における分布を示す断面図である。

- 【図14】本発明で用いられる第二の電極層、第三の電極層及び導電層の材料の膜厚方向における分布を示す断面図である。

- 【図15】本発明で用いられる電解メッキを示す模式図である。

- 【図16】本発明の電流制御装置としての演算装置の構成例を示す模式図である。

- 【図17】本発明で用いられる電子素子の製造装置による作製プロセスの一連の流れを示す図である。

- 【図18】本発明の液晶表示装置の構成例を示す模式図である。

- 【図19】本発明のEL表示装置の構成例を示す模式図である。

- 【図20】実施例1の静特性評価の結果を示す図である。

- 【図21】実施例1の動特性評価の結果を示す図である。

- 【図22】実施例2の電子素子の断面構造を示す図である。

- 【図23】実施例2でスクリーン印刷法を用いた場合のドットゲインを説明する図である

- 【図24】実施例2で紫外線照射を用いない場合のドットゲインを説明する図である。

20

30

# 【図1】

#### トランジスタの一般的な構造を示す図

# 【図2】

# SIT構造の能動素子の一般的な構造を示す図

# 【図3】

# SIT構造の能動素子の一般的な構造を示す図

# 【図4】

## SIT構造の能動素子の一般的な構造を示す図

# 【図5】

## 本発明の電子素子及び電流制御ユニットの構成例を示す模式図

# 【図6】

## 本発明の電子素子の別の構成例を示す模式図

# 【図7】

# 本発明で用いられる基板の溝の断面形状を表す図

## 【図8】

## 本発明の電子素子の作製プロセスの一連の流れを示す図

# 【図9】

#### 本発明で用いられる基板の溝形状の作製例を示す図

# 【図11】

# 本発明で用いられる基板へのエネルギー付与を示す図

# 【図10】

#### 本発明の電子素子のまた別の構成例を示す模式図

## 【図12】

#### 本発明で用いられる半導体層の移動度と 絶縁層の臨界表面張力の関係を示す図

- A:はっ水性ポリイミド

- D:熱酸化膜

- B:ポリビニルフェノール C:有機シリカ

- E:ポリイミド F:SiO2(スパッタ)

C:有機シリカ

# 【図13】

## 本発明で用いられる第二の電極層、第三の電極層及び導電層の材料の 膜厚方向における分布を示す断面図

# 【図14】

## 本発明で用いられる第二の電極層、第三の電極層及び導電層の材料の 膜厚方向における分布を示す断面図

# 【図15】

#### 本発明で用いられる電解メッキを示す模式図

## 【図16】

# 本発明の電流制御装置としての演算装置の構成例を示す模式図

## 【図17】

本発明で用いられる電子素子の製造装置による 作製プロセスの一連の流れを示す図

【図18】

#### 本発明の結晶表示装置の構成例を示す模式図

## 【図19】

# 本発明のEL表示装置の構成例を示す模式図

## 【図20】

# 実施例1の静特性評価の結果を示す図

# 【図21】

#### 実施例1の動特性評価の結果を示す図

# 9p/((2HXL)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y)\$pl/(y

1.0E+04

周波数 /Hz

1.0E+05

# 【図22】

#### 実施例2の電子素子の断面構造を示す図

# 【図23】

実施例2でスクリーン印刷法を用いた場合のドットゲインを説明する図

# 【図24】

1.0E+02

1.0E+03

実施例2で紫外線照射を用いない場合のドットゲインを説明する図

# フロントページの続き

(51) Int.CI. F I

H 0 1 L 29/28 1 0 0 A

(56)参考文献 特表2006-510210(JP,A)

特開2006-049617(JP,A)

特開2006-059896(JP,A)

(58)調査した分野(Int.CI., DB名)

H01L 21/33、29/786