### (19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第4855717号 (P4855717)

(45) 発行日 平成24年1月18日(2012.1.18)

(24) 登録日 平成23年11月4日(2011.11.4)

(51) Int. Cl. F 1

**HO3G 3/10 (2006.01)** HO3G 3/10 D **HO3G 3/30 (2006.01)** HO3G 3/30 E

請求項の数 7 (全 13 頁)

(21) 出願番号 特

特願2005-163009 (P2005-163009)

(22) 出願日 (65) 公開番号 平成17年6月2日 (2005.6.2) 特開2006-340097 (P2006-340097A)

(43) 公開日

審查請求日

特開2006-340097 (P2006-340097A 平成18年12月14日 (2006.12.14) 平成20年5月22日 (2008.5.22) (73)特許権者 599091793

アールエフ・チップス・テクノロジー株式

会社

神奈川県川崎市高津区坂戸3丁目2番1号

||(74)代理人 100109656

弁理士 三反崎 泰司

|(74)代理人 100098785

弁理士 藤島 洋一郎

|(72)発明者 五十嵐 貞男

神奈川県川崎市高津区坂戸3丁目2番1号 アールエフ・チップス・テクノロジー株

式会社内

審査官 儀同 孝信

最終頁に続く

(54) 【発明の名称】利得制御回路および利得制御機能を有するアンプ回路

## (57)【特許請求の範囲】

## 【請求項1】

ゲート・ドレイン間が相互接続された第1のMOSトランジスタと、

第 1 の信号入力端子にソースが接続されると共に、ドレイン・ソース間電位が同一とされ、抵抗素子として機能する第 2 の M O S トランジスタと、

第2の信号入力端子にソースが接続されると共に、ドレイン・ソース間電位が同一とされ、抵抗素子として機能する第3のMOSトランジスタと、

前記第1のMOSトランジスタのドレインに接続され、前記第1のMOSトランジスタ に電流を供給する電流供給手段と

を備え、

10

前記第1のMOSトランジスタのゲート・ソース間電圧が前記第2および第3のMOSトランジスタそれぞれのゲート・ソース間に印加されると共に、前記第1のMOSトランジスタと前記第2のMOSトランジスタとがカレントミラーの関係となり、かつ、前記第1のMOSトランジスタとがカレントミラーの関係となり、前記第1ないし第3のMOSトランジスタのゲート長が互いに同一となるように構成され、

前記電流供給手段による前記第1のMOSトランジスタへの供給電流を変化させることにより、前記第2および第3のMOSトランジスタそれぞれのドレイン・ソース間抵抗の値を変化させ、利得制御がなされるように構成されている

ことを特徴とする利得制御回路。

## 【請求項2】

前記第2および第3のMOSトランジスタのソース間において、前記第2および第3の MOSトランジスタに対して並列接続された第1および第2の抵抗器をさらに備えた ことを特徴とする請求項1に記載の利得制御回路。

## 【請求項3】

前記第2および第3のMOSトランジスタのドレイン間において、前記第2および第3 のMOSトランジスタに対して並列接続された第3および第4の抵抗器をさらに備えた ことを特徴とする請求項1または2に記載の利得制御回路。

#### 【請求項4】

前記第2および第3のMOSトランジスタのソース間において前記第2および第3のM OSトランジスタに対して並列接続されると共に、ドレイン - ソース間電位が同一とされ 、抵抗素子として機能する第4のMOSトランジスタと、

ゲート・ドレイン間が相互接続されると共に、ゲート・ソース間電圧が前記第4のMO Sトランジスタのゲート・ソース間に印加されるように構成された第5のMOSトランジ スタと、

前記第1のMOSトランジスタと共にカレントミラー回路を構成すると共に、ドレイン が前記第5のMOSトランジスタのゲートに接続された第6のMOSトランジスタと

をさらに備えたことを特徴とする請求項1ないし3のいずれか1項に記載の利得制御回 路。

## 【請求項5】

前記電流供給手段は、入力されたコントロール電圧に応じて出力電流値が変化する電圧 ・電流変換回路を含み、

前記コントロール電圧に応じて前記電圧・電流変換回路による前記第1のMOSトラン ジスタへの供給電流を変化させることにより、前記第2および第3のMOSトランジスタ それぞれのドレイン・ソース間抵抗の値を変化させ、利得制御がなされるように構成され ている

ことを特徴とする請求項1ないし4のいずれか1項に記載の利得制御回路。

#### 【請求項6】

請求項1ないし5のいずれか1項に記載の利得制御回路と、

- 一端が前記第2のMOSトランジスタのドレインに接続された第1のコンデンサと、

- 一端が前記第3のMOSトランジスタのドレインに接続された第2のコンデンサと、

前記第1および第2のコンデンサの他端に接続され、前記第1および第2のコンデンサ を介して前記利得制御回路がカスケード接続されたアンプ回路部と

を備えたことを特徴とする利得制御機能を有するアンプ回路。

### 【請求項7】

前記アンプ回路部は、差動増幅器を構成する一対のMOSトランジスタを含み、 前記第1および第2のコンデンサの他端が前記-対のMOSトランジスタのそれぞれの ゲートに接続されることにより、前記利得制御回路がカスケード接続されている ことを特徴とする請求項6に記載の利得制御機能を有するアンプ回路。

## 【発明の詳細な説明】

【技術分野】

[00001]

本発明は、利得を制御することができる利得制御回路および利得制御機能を有するアン プ回路に関する。

### 【背景技術】

#### [0002]

例えば、信号を送信または受信する通信機器では、入力された信号の強度や送信すべき 信号のレベルに応じて機器内部の利得を変化させることのできる利得制御回路が用いられ ている。特に受信信号の強弱にかかわらず出力信号を一定に保つためには、AGC(Auto matic Gain Control)アンプが用いられる。従来、このような利得制御回路は、ギルバー

10

20

30

40

トマルチプライヤを用いる方式が一般的であった。また、CMOS (Complementary Metal Oxide Semiconductor)トランジスタで形成する場合には、利得制御回路としてドレイン・ソース間の抵抗を利用して、T型または 型の抵抗減衰器を構成する方式が考えられる。これらの回路では、コントロール電圧によって利得を制御するのが一般的である。

## [0003]

特許文献1には、可変利得器の出力を整流器により検波・整流して制御電圧を生成し、その制御電圧を可変利得器の利得制御に供すべく構成した負帰還ループにより自動利得制御を行うAGCアンプに関する発明が記載されている。このAGCアンプでは、トランジスタに直接、制御電圧を印加することで利得を制御している。

【特許文献1】特開平9-36680号公報

【発明の開示】

【発明が解決しようとする課題】

[0004]

しかしながら、従来のギルバートマルチプライヤを用いる方式の利得制御回路において、特にCMOSトランジスタで形成する場合、ギルバートマルチプライヤの電流源のアンプ、およびギルバートマルチプライヤの利得制御部で自由に利得補正することが難しいため、利得の温度特性が大きいという欠点があった。また、ギルバートマルチプライヤを用いる方式をCMOSで形成する場合、Typical,Slow,Fastの製造条件の違いによる利得ばらつきが大きいという欠点があった。なお、ここでいうTypical,Slow,Fastとは、製造条件の違いを示す回路パラメータであり、Typical,Slowとは、製造ばらつきのセンター値を示し、Slowとは、回路動作が遅い方向にシフトするような製造ばらつきを与えるパラメータ、Fastとは、回路動作が速い方向にシフトするような製造ばらつきを与えるパラメータを示す。また、特許文献1にも記載されているように、ギルバートマルチプライヤではトランジスタを縦積みしているために、2V以下での低電圧動作は不可能であった。

[00005]

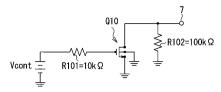

図10は、ドレイン・ソース間の抵抗  $R_{DS}$ を利用してMOSトランジスタによる抵抗減衰器を構成し利得制御を行うようにした回路の一例を示している。この利得制御回路は、MOSトランジスタQ10と、MOSトランジスタQ10のゲートに直列接続された抵抗器 R101と、MOSトランジスタQ10のドレインに並列接続された抵抗器 R102と、出力端子7とを備えている。この利得制御回路では、コントロール電圧V contによりMOS トランジスタQ10のゲート・ソース間の電圧 $V_{GS}$ を変化させることで、ドレイン・ソース間の抵抗  $R_{DS}$ が変化する。

[0006]

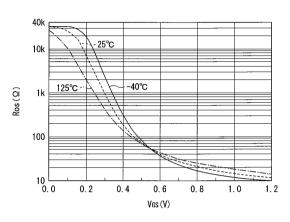

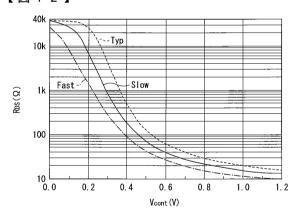

図11は、図10の利得制御回路におけるドレイン・ソース間の抵抗変化の温度特性をSPICE (Simulation Program with Integrated Circuit Emphasis)によりシミュレーションした結果を示している。温度特性として、通常温度(25)、低温時(-40)、および高温時(125))での特性を計算した。また、図12は、図10の利得制御回路において製造時に起こるプロセス状態のTypical,Fast,Slowの各条件での利得特性をSPICEによりシミュレーションした結果を示している。横軸はコントロール電圧Vcont、縦軸はドレイン・ソース間の抵抗R $_{DS}$ を示す。抵抗器R101の抵抗値は10k、、抵抗器R102の抵抗値は100k

[0007]

図11の結果から分かるように、図10のようにバイアスされたドレイン・ソース間抵抗  $R_{DS}$ は、温度により抵抗値が大きく変化する。従って、このような特性の抵抗型減衰器を用いて回路を構成すると、温度によって利得が大幅に変化するという欠点がある。また、図12の結果から分かるように、製造条件の違いによって、同一電圧で得られるドレイン・ソース間抵抗  $R_{DS}$ が大きく異なる。従って、このような特性の抵抗型減衰器を用いて回路を構成すると、製造条件の違いによって、得られる利得が大幅に異なるという欠点がある。

10

20

30

40

このように、MOSトランジスタの電圧制御により利得を制御する方式では、温度変化や製造ばらつきによって、得られる利得にばらつきが生じてしまう。

#### [0008]

本発明はかかる問題点に鑑みてなされたもので、その目的は、温度変化や製造ばらつきによる利得のばらつきを小さくすることができ、かつ低電圧で動作させることができる利得制御回路および利得制御機能を有するアンプ回路を提供することにある。

#### 【課題を解決するための手段】

## [0009]

本発明による利得制御回路は、ゲート・ドレイン間が相互接続された第1のMOSトランジスタと、第1の信号入力端子にソースが接続されると共に、ドレイン・ソース間電位が同一とされ、抵抗素子として機能する第2のMOSトランジスタと、第2の信号入力端子にソースが接続されると共に、ドレイン・ソース間電位が同一とされ、抵抗素子として機能する第3のMOSトランジスタと、第1のMOSトランジスタのドレインに接続され、第1のMOSトランジスタに電流を供給する電流供給手段とを備え、第1のMOSトランジスタでも、第1のMOSトランジスタそれぞれのゲート・ソース間に印加されると共に、第1のMOSトランジスタと第2のMOSトランジスタとがカレントミラーの関係となり、かつ、第1のMOSトランジスタと第3のMOSトランジスタのゲート長が互いに同一となるように構成され、電流供給手段による第1のMOSトランジスタのグタへの供給電流を変化させることにより、第2および第3のMOSトランジスタそれぞれのドレイン・ソース間抵抗の値を変化させ、利得制御がなされるように構成されているものである。

### [0010]

本発明による利得制御機能を有するアンプ回路は、本発明による利得制御回路と、一端が第2のMOSトランジスタのドレインに接続された第1のコンデンサと、一端が第3のMOSトランジスタのドレインに接続された第2のコンデンサと、第1および第2のコンデンサの他端に接続され、第1および第2のコンデンサを介して利得制御回路がカスケード接続されたアンプ回路部とを備えたものである。

## [0011]

本発明による利得制御回路、および利得制御機能を有するアンプ回路では、第1のMOSトランジスタのゲート・ソース間電圧が第2および第3のMOSトランジスタそれぞれのゲート・ソース間に印加される。また、第1のMOSトランジスタへの供給電流を変化させることにより、第2および第3のMOSトランジスタそれぞれのドレイン・ソース間抵抗の値を変化させる。これにより、第2および第3のMOSトランジスタが電流制御による抵抗減衰器として動作することで、従来の電圧制御によって利得制御を行う場合に比べて、温度変化や製造ばらつきによる利得のばらつきが小さくなり、かつ低電圧で動作させることも可能となる。

### [0012]

本発明による利得制御回路において、第2および第3のMOSトランジスタのソース間において、第2および第3のMOSトランジスタに対して並列接続された第1および第2の抵抗器をさらに備えるようにしても良い。

#### [0013]

また、第2および第3のMOSトランジスタのドレイン間において、第2および第3のMOSトランジスタに対して並列接続された第3および第4の抵抗器をさらに備えるようにしても良い。

## [0014]

また、第2および第3のMOSトランジスタのソース間において第2および第3のMOSトランジスタに対して並列接続されると共に、ドレイン・ソース間電位が同一とされ、抵抗素子として機能する第4のMOSトランジスタと、ゲート・ドレイン間が相互接続されると共に、ゲート・ソース間電圧が第4のMOSトランジスタのゲート・ソース間に印

10

20

30

40

加されるように構成された第5のMOSトランジスタと、第1のMOSトランジスタと共にカレントミラー回路を構成すると共に、ドレインが第5のMOSトランジスタのゲートに接続された第6のMOSトランジスタとをさらに備えるようにしても良い。

この構成では、利得制御のレンジにおいて、入力リターンロスに優れた特性が得られる

## [0015]

また、電流供給手段が、入力されたコントロール電圧に応じて出力電流値が変化する電圧・電流変換回路を含み、コントロール電圧に応じて電圧・電流変換回路による第1のMOSトランジスタへの供給電流を変化させることにより、第2および第3のMOSトランジスタそれぞれのドレイン・ソース間抵抗の値を変化させ、利得制御がなされるように構成されていても良い。

この構成では、コントロール電圧での利得制御が電流制御に変換される。

#### 【発明の効果】

## [0016]

本発明の利得制御回路および利得制御機能を有するアンプ回路によれば、第1のMOSトランジスタへの供給電流を変化させることにより、第2および第3のMOSトランジスタそれぞれのドレイン・ソース間抵抗の値を変化させ、利得制御を行うようにしたので、従来の電圧制御によって利得制御を行う場合に比べて、温度変化や製造ばらつきによる利得のばらつきを小さくすることができ、かつ低電圧で動作させることができる。

【発明を実施するための最良の形態】

#### [0017]

以下、本発明の実施の形態について図面を参照して詳細に説明する。

「第1の実施の形態]

#### [0018]

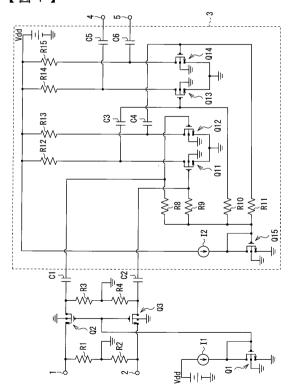

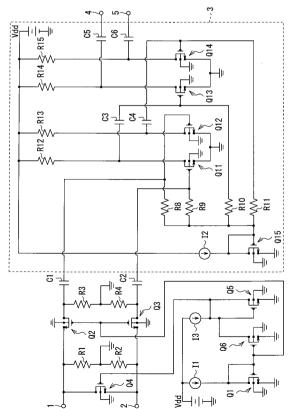

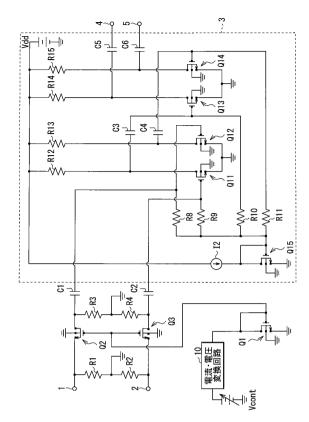

まず、本発明の第1の実施の形態に係る利得制御回路および利得制御機能を有するアンプ回路について説明する。図1は、本実施の形態に係る利得制御機能を有するアンプ回路の一構成例を示している。このアンプ回路は、一対の第1および第2の信号入力端子1,2と、アンプ回路部3と、一対の第1および第2の信号出力端子4,5と、第1および第2のコンデンサC1,C2を介してアンプ回路部3にカスケード接続された利得制御回路とを備えている。なお、本実施の形態では、MOSトランジスタとしてNチャンネルMOSトランジスタを用いた場合のアンプ回路を説明する。

## [0019]

利得制御回路は、電流源 I 1 と、第 1 の M O S トランジスタ Q 1 と、第 2 および第 3 の M O S トランジスタ Q 2 , Q 3 と、第 1 および第 2 の抵抗器 R 1 , R 2 と、第 3 および第 4 の抵抗器 R 3 , R 4 とを備えている。 V d d は電源電圧である。

電流源I1は、本発明における「電流供給手段」の一具体例に対応する。

## [0020]

第1の抵抗器R1の一端は、第2のMOSトランジスタQ2と第1の信号入力端子1との間で第2のMOSトランジスタQ2のソースに接続されている。第2の抵抗器R2の一端は、第3のMOSトランジスタQ3と第2の信号入力端子2との間で第3のMOSトランジスタQ3のソースに接続されている。第1および第2の抵抗器R1,R2の他端は接地されている。これにより、第1および第2の抵抗器R1,R2は、第2および第3のMOSトランジスタQ2,Q3に対して並列接続されている。

## [0021]

第3の抵抗器R3の一端は、第2のMOSトランジスタQ2と第1のコンデンサC1との間で第2のMOSトランジスタQ2のドレインに接続されている。第4の抵抗器R4の一端は、第3のMOSトランジスタQ3と第2のコンデンサC2との間で第3のMOSトランジスタQ3のドレインに接続されている。第3および第4の抵抗器R3,R4は、第2および第3は接地されている。これにより、第3および第4の抵抗器R3,R4は、第2および第3

20

10

30

40

10

20

30

40

50

の M O S トランジスタ Q 2 , Q 3 のドレイン間において、第 2 および第 3 の M O S トランジスタ Q 2 , Q 3 に対して並列接続されている。

#### [0022]

第2および第3のMOSトランジスタQ2,Q3のソースはそれぞれ、第1および第2の信号入力端子1,2に接続されている。第2および第3のMOSトランジスタQ2,Q3はそれぞれ、抵抗素子として動作する。第2および第3のMOSトランジスタQ2,Q3のソースはそれぞれ、第1および第2の抵抗器R1,R2でグランドの電圧が与えられている。また、第2および第3のMOSトランジスタQ2,Q3のドレインはそれぞれ、第3および第4の抵抗器R3,R4でグランドの電圧が与えられている。これにより、MOSトランジスタQ2、Q3は、ドレイン-ソース間電位が同一となるように構成されている。

#### [0023]

第1のMOSトランジスタQ1は、ゲート・ドレイン間が相互接続されている。電流源 I 1 は、第1のMOSトランジスタQ1のドレインに接続され、第1のMOSトランジスタ C 1 のゲートが第2および第3のMOSトランジスタQ2、Q3のゲートに接続され、第1のMOSトランジスタQ1のゲート・ソース間に発生する電圧  $V_{GS}$ が、第2および第3のMOSトランジスタQ2、Q3のそれぞれのゲート・ソース間に印加されるように構成されている。また、電流源 I 1 による第1のMOSトランジスタQ1への供給電流を変化させることにより、第2および第3のMOSトランジスタQ2、Q3それぞれのドレイン・ソース間抵抗  $R_{DS}$ の値が変化するように構成されている。第1のMOSトランジスタQ1、C3のゲート長 L およびゲート幅 W は、通常のカレントミラーと同じ関係になるように設定されている。

#### [0024]

アンプ回路部3は、差動増幅を構成する一対のMOSトランジスタQ11,Q12および一対のMOSトランジスタQ13,Q14と、バイアス用に設けられた抵抗器R8,R9,R10,R11と、MOSトランジスタQ11,Q12,Q13,Q14の各ドレインと電源電圧Vddとの間に負荷抵抗として設けられた抵抗器R12,R13、R14,R15とを有している。アンプ回路部3はまた、電流源I2と、MOSトランジスタQ15と、コンデンサC3,C4,C5,C6とを有している。第1のコンデンサC1の一端は第2のMOSトランジスタQ2のドレインに接続されると共に、他端がMOSトランジスタQ12のゲートに接続されている。第2のコンデンサC2の一端は第3のMOSトランジスタQ3のドレインに接続されると共に、他端がMOSトランジスタQ11のゲートに接続されている。

# [0025]

MOSトランジスタQ15と各MOSトランジスタQ11,Q12,Q13,Q14の間はそれぞれ、カレントミラーの関係となるように構成されている。コンデンサC3,C4,C5,C6は、信号の結合用として設けられている。このアンプ回路部3において、電源電圧Vddとグランド間の1つの回路ルートがMOSトランジスタQ11と抵抗12のみで構成されているので、1.2V以下の低い電源電圧で容易に構成できる。同様に、MOSトランジスタQ12,Q13,Q14も低電圧駆動となっている。電流源I2は、温度依存性があるものが用いられ、アンプ回路部3の利得が温度に対して変化しないように構成されている。

## [0026]

なお、この利得制御機能を有するアンプ回路の特徴は利得制御回路の部分にあり、アンプ回路部3の構成は図示した構成に限定されず、一般的なアンプ回路と同様の構成とすることができる。

### [0027]

次に、この利得制御機能を有するアンプ回路の動作、特に利得制御回路の動作を詳しく説明する。

### [0028]

このアンプ回路では、第1および第2の信号入力端子1,2に入力された信号が、利得制御回路における第2および第3のMOSトランジスタQ2,Q3を通過後、第1および第2のコンデンサC1、C2を介してアンプ回路部3に印加される。そして、アンプ回路部3で増幅された信号が、第1および第2の信号出力端子4,5から取り出される。

### [0029]

このアンプ回路における利得制御回路では、第1のMOSトランジスタQ1のゲート・ソース間電圧 V<sub>GS</sub>が第2および第3のMOSトランジスタQ2,Q3それぞれのゲート・ソース間に印加される。また、電流源 I 1 からの第1のMOSトランジスタQ1への供給電流を変化させることにより、第2および第3のMOSトランジスタQ2,Q3それぞれのドレイン・ソース間抵抗 R<sub>DS</sub>の値が変化する。これにより、第2および第3のMOSトランジスタQ2,Q3が電流制御による抵抗減衰器として動作することで、利得制御の機能を実現する。

## [0030]

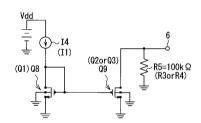

この利得制御の動作を図2、図3および図4を用いて説明する。図2は、この利得制御回路の部分的な等価回路を示している。図2において、MOSトランジスタQ8および電流源I4は、それぞれ、図1の第1のMOSトランジスタQ1および電流源I1に相当する。また、MOSトランジスタQ9および抵抗器R5はそれぞれ、図1の第2のMOSトランジスタQ2および第3の抵抗R3、または第3のMOSトランジスタQ3および第4の抵抗R4に相当する。抵抗器R5はトランジスタQ9のドレインとソースの電位を同じにするためのものである。また、MOSトランジスタQ8とMOSトランジスタQ9はカレントミラーの関係と同一動作をしており、それらの素子のサイズにより、制御する電流値を比例的に変更することができる。

#### [0031]

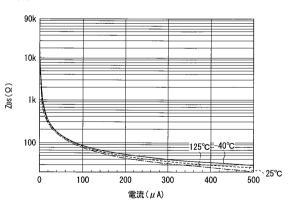

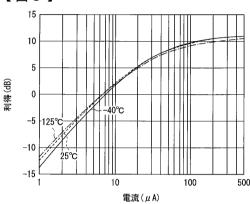

図3は、図2の回路において端子6から見たインピーダンス、すなわち、 $MOSFランジスタQ9のドレイン・ソース間のインピーダンス<math>Z_{DS}$ の温度変化の特性をSPICEによりシミュレーションした結果を示している。温度特性として、通常温度(25)、低温時(-40)、および高温時(125)での特性を計算した。横軸は電流源I4の電流、縦軸はドレイン・ソース間のインピーダンス $Z_{DS}$ を示す。電流源I4を変化させると、 $MOSFランジスタQ9のドレイン・ソース間のインピーダンス<math>Z_{DS}$ が変化する。そのインピーダンス $Z_{DS}$ の温度依存性は、図3から分かるように、図11に示した従来の電圧制御による特性と比較して非常に小さく、優れた特性を示している。

#### [0032]

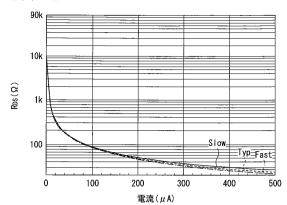

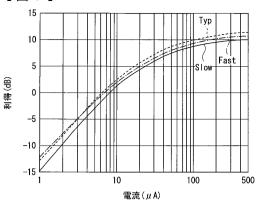

また、図 4 は、図 2 の回路において製造時に起こるプロセス状態のTypical,Fast,Slowの各条件でのドレイン・ソース間抵抗  $R_{DS}$ の特性をSPICEによりシミュレーションした結果を示している。横軸は電流源I4の電流、縦軸はドレイン・ソース間の抵抗  $R_{DS}$ を示す。図 4 の結果から分かるように、図 1 2 に示した従来の電圧制御による特性と比較して、製造条件の違いがあったとしてもドレイン・ソース間抵抗  $R_{DS}$ の値の変化は非常に小さく、優れた特性を示している。

### [0033]

なお、図 3 ,図 4 の計算条件は、図 2 の回路において、M O S トランジスタQ 8 のゲート長 L = 0 . 1 1  $\mu$  m、ゲート幅W = 2  $\mu$  m、マルチM = 1 とし、M O S トランジスタQ 9 のゲート長 L = 0 . 1 1  $\mu$  m、ゲート幅W = 2  $\mu$  m、マルチM = 1 6 とし、抵抗器 R 5 = 1 0 0 k としている。

## [0034]

図2の回路におけるMOSトランジスタQ8,Q9のカレントミラーの関係でMOSトランジスタQ9の等価抵抗を変化させることで、利得の温度特性およびプロセスばらつきに対して優れた特性を実現できる。本実施の形態における利得制御の特性は、この図2の回路の特性を利用している。

## [0035]

10

20

30

10

20

30

40

50

図5に、図1の回路全体での温度に対する利得特性をSPICEによりシミュレーションした結果を示す。温度特性として、通常温度(25 )、低温時(-40 )、および高温時(125 )での特性を計算した。また、図6に、図1の回路全体において製造時に起こるプロセス状態のTypical,Fast,Slowの各条件での利得特性をSPICEによりシミュレーションした結果を示す。横軸は電流源I1の電流、縦軸は利得を示す。図5および図6から明らかなように、図1の回路は、温度変化に対する利得変化が小さく、温度特性およびプロセスばらつきに対して非常に優れた特性を示している。

## [0036]

以上説明したように、本実施の形態に係る利得制御回路および利得制御機能を有するアンプ回路によれば、第1のMOSトランジスタQ1への供給電流を変化させることにより、第2および第3のMOSトランジスタQ2,Q3それぞれのドレイン・ソース間抵抗R<sub>DS</sub>の値を変化させ、利得制御を行うようにしたので、従来の電圧制御によって利得制御を行う場合に比べて、温度変化や製造ばらつきによる利得のばらつきを小さくすることができる。また、利得制御の回路部分を、0Vで動作する抵抗型減衰回路で構成し、アンプ回路部3はその抵抗減衰回路の後にカスケード接続しているので、1~1.2Vの低電圧で動作させることができる。

### 「第2の実施の形態]

## [0037]

次に、本発明の第2の実施の形態に係る利得制御回路および利得制御機能を有するアンプ回路について説明する。図7は、本実施の形態に係る利得制御機能を有するアンプ回路の一構成例を示している。なお、上記第1の実施の形態に係るアンプ回路と実質的に同一の構成部分には同一の符号を付し、適宜説明を省略する。このアンプ回路は、上記第1の実施の形態(図1)の回路構成においてさらに、第4のMOSトランジスタQ4と、第5および第6のMOSトランジスタQ6,Q5と、電流源I3とを備えている。アンプ回路部3の構成は、図1と同様である。

### [0038]

第4のMOSトランジスタQ4のドレインは、第1の抵抗器R1の一端と第1の信号入力端子1との間に接続されている。第4のMOSトランジスタQ4のソースは、第2の抵抗器R2の一端と第2の信号入力端子2との間に接続されている。第4のMOSトランジスタQ4のドレインおよびソスタQ4は抵抗素子として動作する。第4のMOSトランジスタQ4のドレインおよびソースはそれぞれ、第1および第2の抵抗器R1,R2でグランドの電圧が与えられている。これにより、第4のMOSトランジスタは、第2および第3のMOSトランジスタQ2,Q3に対して並列接続されると共に、ドレイン・ソース間電位が同一とされている。

### [0039]

第5のMOSトランジスタQ5は、ゲート・ドレイン間が相互接続されている。第5のMOSトランジスタQ5のゲートは、第4のMOSトランジスタQ4のゲートに接続されている。第5のMOSトランジスタQ5のゲート・ソース間電圧 $V_{GS}$ が第4のMOSトランジスタQ4のゲート・ソース間に印加されるように構成されている。第6のMOSトランジスタQ6は、第1のMOSトランジスタQ1と共にカレントミラー回路を構成している。第6のMOSトランジスタQ6のドレインは、第5のMOSトランジスタのゲートに接続されている。電流源 I3 は固定値に設定されている。

## [0040]

図 7 の回路における利得制御回路では、固定値の電流源 I 3 からカレントミラーの第 6 の M O S トランジスタQ 6 に流れる電流分を引いた値が第 5 の M O S トランジスタQ 5 に流れる。第 5 の M O S トランジスタQ 5 のゲート・ソース間電圧  $V_{GS}$ が、第 4 の M O S トランジスタQ 4 のゲート・ソース間に印加される。第 4 の M O S トランジスタQ 4 のドレイン・ソース間抵抗  $R_{DS}$  が、第 2 および第 3 の M O S トランジスタQ 2 ,Q 3 のドレイン・ソース間抵抗  $R_{DS}$  の値と逆比例する値となる。

## [0041]

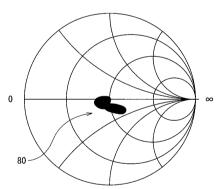

この利得制御回路では、利得制御のレンジにおいて、入力リターンロスに優れた特性が得られる。図 8 は、図 7 の回路において、制御電流(電流源 I 1)を 1  $\mu$  A ~ 5 0 0  $\mu$  A 変化させ、利得を 2 0 d B 以上変化させた場合の入力インピーダンスの変化をスミスチャート上で示したものである。スミスチャートの中心は基準インピーダンス(信号源側のインピーダンス)で、左端はインピーダンスが 0、右端はインピーダンスが となる。インピーダンスが外周上にあるとき反射係数は 1 となり、入力リターンロスが小さくなる。図 8 において、符号 8 0 で示した部分が入力インピーダンスの変化を示す。図 8 に示したように、入力リターンロスが大きく、優れた特性が得られている。

[第3の実施の形態]

## [0042]

次に、本発明の第3の実施の形態に係る利得制御回路および利得制御機能を有するアンプ回路について説明する。図9は、本実施の形態に係る利得制御機能を有するアンプ回路の一構成例を示している。なお、上記第1の実施の形態に係るアンプ回路と実質的に同一の構成部分には同一の符号を付し、適宜説明を省略する。図9の回路は、上記第1の実施の形態(図1)の回路における電流源I1に代えて、電流供給手段として、電圧・電流変換回路10を備えたものである。アンプ回路部3の構成は、図1と同様である。

### [0043]

電圧・電流変換回路 1 0 は、入力されたコントロール電圧 V cont に応じて出力電流値が変化するように構成されている。電圧・電流変換回路 1 0 は、コントロール電圧 V cont に対して、出力電流が例えば自然対数的に増加する。コントロール電圧 V cont に応じて電圧・電流変換回路 1 0 による第 1 の M O S トランジスタ Q 1 への供給電流を変化させることにより、第 2 および第 3 の M O S トランジスタ Q 2 , Q 3 それぞれのドレイン・ソース間抵抗  $R_{DS}$  の値を変化させ、利得制御がなされるように構成されている。

#### [0044]

この利得制御回路では、コントロール電圧 V contでの利得制御が電流制御に変換される。コントロール電圧 V contでの利得制御が、電流制御に変換されているので、従来の電圧制御によって利得制御を行う場合に比べて、温度変化や製造ばらつきによる利得のばらつきを小さくすることができる。

## [0045]

なお、本発明は、以上で説明した各実施の形態に限定されず、さらに種々の変形実施が可能である。例えば、上記各実施の形態では、MOSトランジスタとしてNチャンネルMOSトランジスタを用いた場合について説明したが、PチャンネルMOSトランジスタで構成しても良い。この場合は基準電圧がVddに変わるのみで、利得制御の動作はNチャンネルMOSトランジスタの回路と同様である。

## [0046]

また、第2の実施の形態に係る回路(図7)と第3の実施の形態に係る回路(図9)とを合わせた構成も可能である。すなわち、図7の利得制御回路における電流源I1に代えて、電流供給手段として、電圧・電流変換回路10を備えた構成であっても良い。

【図面の簡単な説明】

#### [0047]

【図1】本発明の第1の実施の形態に係る利得制御機能を有するアンプ回路の構成を示す 回路図である。

【図2】図1のアンプ回路における利得制御回路部分の動作を説明するための回路図である。

【図3】図2に示す利得制御回路におけるドレイン・ソース間の抵抗変化の温度特性を示す特性図である。

【図4】図2に示す利得制御回路におけるドレイン・ソース間の抵抗変化の製造条件のばらつきによる特性を示す特性図である。

【図5】図1に示すアンプ回路における温度変化による利得の特性を示す特性図である。

【図6】図1に示すアンプ回路における製造条件のばらつきによる利得の特性を示す特性

10

20

30

40

図である。

【図7】本発明の第2の実施の形態に係る利得制御機能を有するアンプ回路の構成を示す回路図である。

- 【図8】図7のアンプ回路における入力インピーダンスの特性を示す特性図である。

- 【図9】本発明の第3の実施の形態に係る利得制御回路の構成を示す回路図である。

- 【図10】MOSトランジスタにより電圧制御の抵抗減衰器を構成し、利得制御を行うようにした回路の一例を示す回路図である。

- 【図11】図10に示す利得制御回路におけるドレイン・ソース間の抵抗変化の温度特性を示す特性図である。

- 【図12】図10に示す利得制御回路におけるドレイン-ソース間の抵抗変化の製造条件のばらつきによる特性を示す特性図である。

【符号の説明】

## [0048]

C 1 … 第 1 のコンデンサ、 C 2 … 第 2 のコンデンサ、 I 1 … 電流源、 Q 1 … 第 1 の M O S トランジスタ、 Q 2 … 第 2 の M O S トランジスタ、 Q 3 … 第 3 の M O S トランジスタ、 Q 4 … 第 4 の M O S トランジスタ、 Q 5 … 第 5 の M O S トランジスタ、 Q 6 … 第 6 の M O S トランジスタ、 R 1 … 第 1 の抵抗器、 R 2 … 第 2 の抵抗器、 R 3 … 第 3 の抵抗器、 R 4 … 第 4 の抵抗器、 V cont … コントロール電圧、 1 … 第 1 の信号入力端子、 2 … 第 2 の信号入力端子、 3 … アンプ回路部、 4 … 第 1 の信号出力端子、 5 … 第 2 の信号出力端子、 1 0 … 電流・電圧変換回路。

20

10

## 【図1】

## 【図2】

## 【図3】

【図4】

【図6】

【図5】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

## フロントページの続き

```

(56)参考文献 特開平07-079132(JP,A)

特表2001-516180(JP,A)

```

特開平09-331363(JP,A)

特公平03-003403(JP,B2)

特開平08-222994(JP,A)

特開平08-330871(JP,A)

特開昭63-301610(JP,A)

特開2000-261290(JP,A)

特開2004-328425(JP,A)

特開2003-204247(JP,A)

特開2001-024447(JP,A)

実開昭51-040238(JP,U)

特開昭61-290808(JP,A)

## (58)調査した分野(Int.CI., DB名)

H03G 1/00-3/34