(19) **日本国特許庁(JP)**

# (12) 特許公報(B2)

29/80

21/20

HO1L

HO1L

(11)特許番号

特許第5746927号 (P5746927)

(45) 発行日 平成27年7月8日(2015.7.8)

(24) 登録日 平成27年5月15日(2015.5.15)

(51) Int. Cl. FL

HO1L 21/338 (2006, 01) HO1L 29/778 (2006, 01)

HO1L 29/812 (2006.01)

HO1L 21/20 (2006, 01)

請求項の数 9 (全 12 頁)

特願2011-174364 (P2011-174364) (21) 出願番号

(22) 出願日 平成23年8月9日(2011.8.9) (65) 公開番号 特開2012-60110 (P2012-60110A)

(43) 公開日 平成24年3月22日 (2012.3.22) 審査請求日 平成26年5月23日 (2014.5.23)

(31) 優先権主張番号 特願2010-180308 (P2010-180308) 平成22年8月11日 (2010.8.11) (32) 優先日

(33) 優先権主張国 日本国(JP) ||(73)特許権者 000002093

住友化学株式会社

Н

東京都中央区新川二丁目27番1号

||(74)代理人 110000877

龍華国際特許業務法人

||(74)代理人 100112520

弁理士 林 茂則

|(72)発明者 佐沢 洋幸

茨城県つくば市北原6番 住友化学株式会

补内

(72) 発明者 秦 雅彦

茨城県つくば市北原6番 住友化学株式会

社内

審査官 棚田 一也

最終頁に続く

(54) 【発明の名称】半導体基板、半導体デバイスおよび半導体基板の製造方法

# (57)【特許請求の範囲】

# 【請求項1】

ベース基板と、

前記ベース基板の上または上方に形成された第1結晶層と、

前記第1結晶層の上方に形成された第2結晶層と、

前記第1結晶層と前記第2結晶層との間に形成された第3結晶層と、を有し、

前記第1結晶層は、酸素原子およびシリコン原子からなる群より選択された少なくとも 1つの原子である第1原子と、アクセプタとして機能する少なくとも1つの原子である第 2原子とを含む3-5族化合物半導体層であり、

前記第2結晶層および前記第3結晶層は、3-5族化合物半導体層であり、

前記第3結晶層は、前記第2原子を有し、

前記第3結晶層に含まれる前記第2原子の総数が、前記第1結晶層に含まれる前記第2 原子の総数より少なく、

前記第3結晶層は、空乏状態にある

半導体基板。

# 【請求項2】

前記第2原子が、Mg原子、Zn原子、Be原子およびC原子からなる群より選択され た少なくとも1つの原子である

請求項1に記載の半導体基板。

### 【請求項3】

前記第2結晶層は、半導体能動素子の活性層として機能する 請求項1または請求項2に記載の半導体基板。

#### 【請求項4】

前記第1結晶層、前記第2結晶層および前記第3結晶層が、3-5族窒化物半導体層で ある

請求項1から請求項3の何れか一項に記載の半導体基板。

前記ベース基板の上または上方に形成された阻害層を更に有し、

前記阻害層は開口を有し、

前記阻害層は結晶成長を阻害し、

前記阻害層は前記第1原子を含み、

前記第1結晶層は、前記開口に形成される

請求項1から請求項4の何れか一項に記載の半導体基板。

# 【請求項6】

前記阻害層が、酸化シリコン層、窒化シリコン層または酸窒化シリコン層である 請求項5に記載の半導体基板。

# 【請求項7】

ベース基板と、

前記ベース基板の上または上方に形成された第1結晶層と、

前記第1結晶層の上方に形成された第2結晶層と、

前記第1結晶層と前記第2結晶層との間に形成された第3結晶層と、

を有し、

前記第1結晶層は、酸素原子およびシリコン原子からなる群より選択された少なくとも 1つの原子である第1原子と、アクセプタとして機能する少なくとも1つの原子である第 2原子とを含む3-5族化合物半導体層であり、

前記第2結晶層および前記第3結晶層は、3-5族化合物半導体層であり、

前記第3結晶層は、前記第2原子を有し、

前記第3結晶層に含まれる前記第2原子の総数が、前記第1結晶層に含まれる前記第2 原子の総数より少なく、

前記第3結晶層は、空乏状態にあり、

前記第2結晶層が活性層である

半導体デバイス。

### 【請求項8】

ベース基板の上または上方に、酸素原子およびシリコン原子からなる群より選択された 少なくとも1つの原子である第1原子を含み、結晶の成長を阻害する阻害層を形成する工 程と、

前記阻害層に開口を形成する工程と、

前記開口の内部に、3-5族化合物半導体の第1結晶前駆体層をエピタキシャル成長に より形成する工程と、

40 アクセプタとして機能する少なくとも1つの原子である第2原子で前記第1結晶前駆体 層をドーピングすることにより第1結晶層を形成する工程と、を有する、

半導体基板の製造方法。

# 【請求項9】

前記阻害層が、酸化シリコン層、窒化シリコン層または酸窒化シリコン層である 請求項8に記載の半導体基板の製造方法。

【発明の詳細な説明】

### 【技術分野】

[00001]

本発明は、半導体基板、半導体デバイスおよび半導体基板の製造方法に関する。

【背景技術】

10

20

#### [00002]

GaN、AlGaN等の窒化物半導体は、絶縁破壊電圧が高い、飽和ドリフト速度が大きい、化学的・熱的に安定である、バンドギャップが大きい等の特徴がある。このため、GaN、AlGaN等の窒化物半導体は、当該特徴を生かした、パワースイッチングデバイス、高温で動作が可能なデバイス、青色または緑色の発光デバイス等への用途が見込まれている。

#### [0003]

窒化物半導体をエピタキシャル成長させる場合、結晶成長のベース基板として安価なシリコン基板を用いることが好ましい。しかし、シリコン結晶と窒化物半導体結晶との熱膨張係数の差が大きく、エピタキシャル成長させた結晶層にクラックが発生しやすいという問題がある。この問題の解決方法の一つとして、窒化物半導体結晶層をシリコン基板上の全面に一様に成長するのではなく、部分的に形成する技術が提案されている。

### [0004]

たとえば、特許文献 1 は、A 1 、G a  $_y$  I n  $_1$  .  $_x$  .  $_y$  N (但し、0  $_x$  、  $_y$  1、0  $_x$  +  $_y$  1)からなる 3 族窒化物半導体を S  $_i$  基板上にエピタキシャル成長させる技術を開示する。特許文献 1 には、 S  $_i$  基板上に 3 族窒化物半導体をエピタキシャル成長させる際に、 S  $_i$  基板上に S  $_i$  の熱酸化膜からなるマスクを形成し、 S  $_i$  の露出部に 3 族窒化物半導体を選択エピタキシャル成長させることが記載されている。

特許文献 1 特開平 1 1 - 2 7 4 0 8 2 号公報

# 【発明の概要】

【発明が解決しようとする課題】

#### [0005]

特許文献1に記載のように、シリコン基板上にシリコン酸化膜を形成し、当該シリコン酸化膜の任意の領域にシリコン基板に達する開口を形成すれば、シリコン酸化膜が窒化物半導体結晶のエピタキシャル成長を阻害する阻害層として機能し、開口の内部にのみ選択的に窒化物半導体結晶をエピタキシャル成長させることができる。エピタキシャル成長された窒化物半導体結晶は、シリコン基板の全面ではなく開口内部にのみ形成されるので、窒化物半導体結晶のクラックの発生が抑制されるという効果が期待できる。

# [0006]

しかし、阻害層をマスクにして、阻害層開口の内部に半導体結晶層を選択エピタキシャル成長させる方法では、エピタキシャル成長層内に阻害層を構成する原子が取り込まれる場合がある。半導体結晶層内に取り込まれた原子は不純物として機能することはよく知られており、たとえばGaN結晶あるいはA1GaN結晶にSiまたはOが取り込まれるとn型不純物になる。

# [0007]

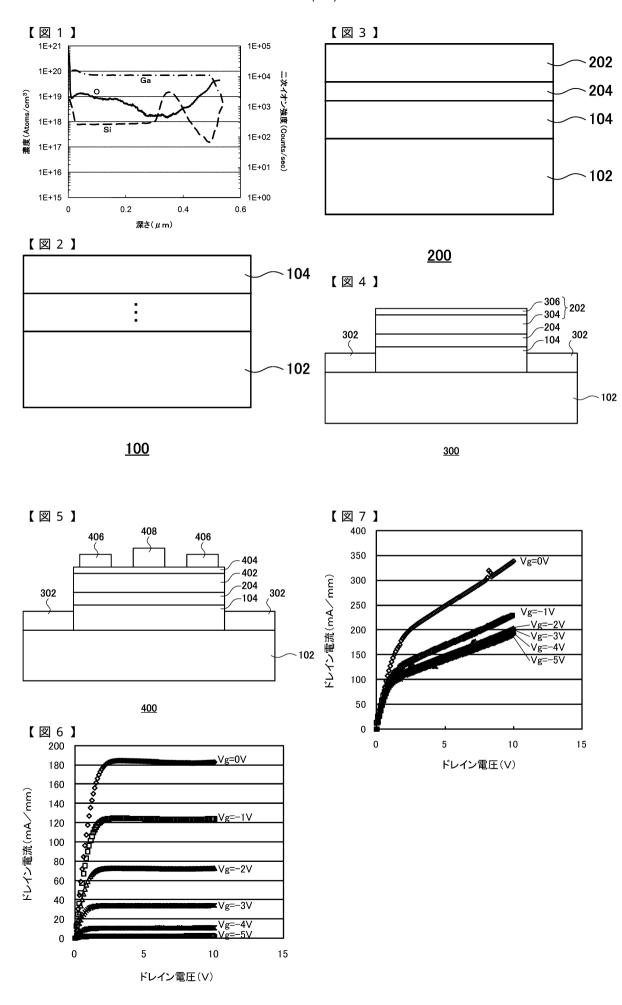

図1は、Si原子およびO原子がGaN層内にどの程度取り込まれるかを評価するために実験した二次イオン質量分析(SIMS)データである。図1は、シリコン酸化膜を阻害層として選択エピタキシャル成長させたGaN層のSIMS深さプロファイルであり、実線がO原子、破線がSi原子、一点鎖線がGa原子の深さプロファイルを示す。O原子およびSi原子については縦軸左側の濃度のスケールが、Ga原子については縦軸右側の二次イオン強度のスケールが相当する。Ga原子の二次イオン強度が低下している深さ0.5μm付近が基板とGaN層との界面である。深さ0.5μm付近から深さ0μmの表面までがGaN層である。GaN層の深さ方向で一様ではないものの、O原子およびSi原子が1×10<sup>18</sup>cm・³以上、深さによっては1×10<sup>20</sup>cm・³近くの不純物原子が取り込まれていることがわかる。

# [0008]

これら不純物原子は結晶層の導電性に明らかに影響を及ぼす。 GaN結晶においては、Si原子あるいはO原子はいずれもn型伝導キャリア(自由電子)を生成するドナーとして作用するので、選択エピタキシャル結晶層の抵抗を高くすることは困難である。また選択エピタキシャル結晶層を、抵抗の精密な制御が必要な電子デバイス用結晶に用いること

10

20

30

40

は困難である。本発明の目的は、阻害層を用いて選択エピタキシャル成長させた窒化物半 導体結晶のように、結晶中にSi原子またはO原子を含んでしまう半導体結晶であっても 、抵抗を高くし、抵抗の精密な制御が必要な電子デバイスにも用いることができる半導体 結晶を提供することにある。

# 【課題を解決するための手段】

# [0009]

上記課題を解決するために、本発明の第1の態様においては、ベース基板と、ベース基板の上または上方に形成された第1結晶層とを有し、第1結晶層が、酸素原子およびシリコン原子からなる群より選択された少なくとも1つの原子である第1原子と、アクセプタとして機能する少なくとも1つの原子である第2原子とを含む3-5族化合物半導体層である半導体基板を提供する。なお、本明細書において、「~の上に」形成とは、~に接して~の上に形成されている様をいい、英語で表現した場合の「on」に対応する。また、「~の上方に」形成されとは、~から離れて~より上に形成されている様をいい、英語で表現した場合の「above」に対応する。

# [0010]

例えば第2原子は、Mg原子、Zn原子、Be原子およびC原子からなる群より選択された少なくとも1つの原子である。半導体基板は、第1結晶層の上方に形成された第2結晶層と、第1結晶層と第2結晶層との間に形成された第3結晶層とを更に有してよい。例えば第2結晶層および第3結晶層は、3-5族化合物半導体層であり、第3結晶層は第2原子を有し、第3結晶層に含まれる第2原子の総数が、第1結晶層に含まれる第2原子の総数より少ない。当該第2結晶層は、当該半導体基板を用いて形成される半導体能動素子の活性層として機能してよい。当該第3結晶層は、空乏状態の結晶層であってよい。

# [0011]

第1結晶層、第2結晶層および第3結晶層は、3-5族窒化物半導体層であってもよい。半導体基板は、ベース基板の上または上方に形成された阻害層を更に有してよい。阻害層は開口を有し、阻害層は結晶成長を阻害し、阻害層は第1原子を含み、第1結晶層は、開口に形成される。阻害層は、酸化シリコン層、窒化シリコン層または酸窒化シリコン層であってよい。

# [0012]

本発明の第2の態様においては、ベース基板と、ベース基板の上または上方に形成された第1結晶層と、第1結晶層の上または上方に形成された活性層とを有し、第1結晶層は、酸素原子およびシリコン原子からなる群より選択された少なくとも1つの原子である第1原子と、アクセプタとして機能する少なくとも1つの原子である第2原子とを含む3・5族化合物半導体層である半導体デバイスを提供する。

# [0013]

本発明の第3の態様においては、ベース基板の上または上方に、酸素原子およびシリコン原子からなる群より選択された少なくとも1つの原子である第1原子を含み、結晶の成長を阻害する阻害層を形成する工程と、阻害層に開口を形成する工程と、開口の内部に、3-5族化合物半導体の第1結晶層を、アクセプタとして機能する少なくとも1つの原子である第2原子を導入しながらエピタキシャル成長により形成する工程とを有する、半導体基板の製造方法を提供する。

# [0014]

本発明の第4の態様においては、ベース基板の上または上方に、酸素原子およびシリコン原子からなる群より選択された少なくとも1つの原子である第1原子を含み、結晶の成長を阻害する阻害層を形成する工程と、阻害層に開口を形成する工程と、開口の内部に、3-5族化合物半導体の第1結晶前駆体層をエピタキシャル成長により形成する工程と、アクセプタとして機能する少なくとも1つの原子である第2原子で第1結晶前駆体層をドーピングすることにより第1結晶層を形成する工程と、を有する半導体基板の製造方法を提供する。半導体基板の製造方法において、阻害層は、酸化シリコン層、窒化シリコン層または酸窒化シリコン層であってよい。

10

20

30

### 【図面の簡単な説明】

# [0015]

【図1】Si原子およびO原子がGaN層内にどの程度取り込まれるかを評価するために実験した二次イオン質量分析(SIMS)データである。

- 【図2】半導体基板100の断面例を示す。

- 【図3】半導体基板200の断面例を示す。

- 【図4】半導体基板300の断面例を示す。

- 【図5】電界効果トランジスタ400の断面例を示す。

- 【図6】ドープトランジスタのIV特性を示す。

- 【図7】非ドープトランジスタのIV特性を示す。

【発明を実施するための形態】

### [0016]

図2は、半導体基板100の断面例を示す。半導体基板100は、ベース基板102および第1結晶層104を有する。ベース基板102と第1結晶層104との間には任意の結晶層が形成されてもよい。

### [0017]

ベース基板102は、その上に形成されるエピタキシャル成長層を支持する支持基板である。ベース基板102として表面がシリコンである基板、サファイア基板、シリコンカーバイド基板、酸化亜鉛基板、GaAs基板が挙げられる。ここで、「表面がシリコン」とは、少なくとも基板の表面がシリコンで構成される領域を有することを意味する。たとえばベース基板102は、Siウェハのように基板全体がシリコンで構成されていてもよく、SOI(silicon‐on‐insulator)ウェハのように絶縁層の上にシリコン層を有する構造であってもよい。ベース基板102は、サファイア基板、ガラス基板、シリコンカーバイド基板、酸化亜鉛基板、GaAs基板等、シリコンと異なる元素からなる基板上にシリコン層が形成されたものでもよい。ベース基板102のシリコンは不純物を含んでよい。ベース基板102の表面のシリコン層に、自然酸化層等の極薄い酸化シリコン層あるいは窒化シリコン層が形成されていてもよい。

### [0018]

第 1 結晶層 1 0 4 は、ベース基板 1 0 2 の上または上方に形成される。つまり第 1 結晶層 1 0 4 は、ベース基板 1 0 2 の表面に接して形成されてよく、ベース基板 1 0 2 の表面との間に他の層を挟んで形成されてもよい。第 1 結晶層 1 0 4 は、3 - 5 族化合物半導体層である。第 1 結晶層 1 0 4 として、GaAs、AlGaAs、InGaAs、InGaAs、InGaAs、InGaAs0 4 に 0 原子および Si0 原子からなる群より選択された少なくとも 1 つの原子である第 1 原子を含む。第 1 原子の第 1 結晶層 1 0 4 における濃度は、 2 × 1 0  $^{1}$ 7 c m  $^{1}$ 3 以上、 1 × 1 0  $^{2}$ 1 c m  $^{3}$ 3 以下である。

# [0019]

第1結晶層104は、アクセプタとして機能する少なくとも1つの原子である第2原子を含む。第2原子として、Mg原子、Zn原子、Be原子およびC原子からなる群より選択された少なくとも1つの原子が挙げられる。第2原子は、第1結晶層104内で正孔を生成するアクセプタとして機能する。第1結晶層104に、ドナーとなる第1原子とアクセプタとなる第2原子とがともに含まれることで、第1原子により生成される電子が第2原子により生成される正孔で補償され、第1結晶層104の抵抗率を高くできる。第1結晶層104の抵抗率を高くできる結果、第1結晶層104に流れる電流が抑えられ、第1結晶層104またはその上に形成されるデバイスの特性を改善できる。たとえば電界効果トランジスタの場合、ピンチオフ特性あるいは耐圧が向上する。

# [0020]

第1結晶層104に含む第2原子の濃度は、混入した第1原子を補償するのに十分な過剰な濃度であることが好ましい。過剰な濃度とは第1原子を補償することに加えて、トランジスタ動作時の電圧印加により新たに発生するキャリア(電子)をも捕獲し、当該トラ

10

20

30

40

10

20

30

40

50

ンジスタ動作時に第 1 結晶層 1 0 4 を高絶縁性に保てる濃度である。このような濃度にすることにより、トランジスタのピンチオフ性の向上、および、オンオフ比の向上が期待できる。一般的に第 2 原子の濃度は、 1  $\times$  1 0  $^{1}$   $^{4}$  c m  $^{-3}$  から 1  $\times$  1 0  $^{2}$   $^{1}$  c m  $^{-3}$  の範囲で決定できる。

# [0021]

なお、第1結晶層104に含む第2原子の濃度は、混入した第1原子を補償するのに丁度良い濃度、第1原子を補償するには少し足りない程度の濃度、あるいは、第1原子を補償し過ぎるものの過剰量が僅かとなるような濃度であってもよい。これらの場合、第1結晶層104は絶縁性、若しくは、導電性の低いn型またはp型の導電型となり、このような場合であっても効果は期待できる。

# [0022]

図3は、半導体基板200の断面例を示す。半導体基板200は、ベース基板102、第1結晶層104、第2結晶層202および第3結晶層204を有する。半導体基板200におけるベース基板102および第1結晶層104は、半導体基板100におけるベース基板102および第1結晶層104と同様である。

### [0023]

第2結晶層202は、第1結晶層104の上方に形成される。第2結晶層202は、半導体能動素子の活性層として機能する。当該半導体能動素子は、半導体基板200を用いて半導体能動素子を指す。つまり、第2結晶層202は、半導体基板200を用いて半導体能動素子を形成した場合に、当該半導体能動素子の活性層として機能できる特性を有する。第3結晶層204は、第1結晶層104と第2結晶層202との間に形成される。第2結晶層202および第3結晶層204は、3-5族化合物半導体層である。第2結晶層202は、3-5族化合物半導体層である。第2結晶層202は、単一層でなくてもよい。たとえばGaNまたはGaNが挙げられる。第2結晶層202は、単一層でなくてもよい。たとえばGaAs/InGaNが挙げられるのヘテロ接合結晶層であってもよい。第3結晶層204として、GaAs、AlGaAs、AlGaAs、AlN、GaNまたはAlGaNが挙げられる

# [0024]

第3結晶層204に含まれる第2原子の総数は、第1結晶層104に含まれる第2原子の総数より少ない。結晶層に複数種類の第2原子が含まれる場合、第2原子の総数とは各第2原子の数の和を指す。第3結晶層204は、空乏状態にある。ここで「空乏状態」とは、第3結晶層204内の自由電子と正孔が同数程度存在する結果、自由電子と正孔とが再結合して打ち消しあい、キャリアが実質的に存在しなくなっている状態をいう。たとえば第3結晶層204に存在するドナーおよびアクセプタから生成する自由電子および正孔がほぼ同数である場合が挙げられる。

# [0025]

前述した通り、第1結晶層104に含まれる第2原子の濃度は、混入した第1原子を補償するのに十分な過剰な濃度であることが好ましい。しかし、第1結晶層104に含まれる第2原子の濃度が過剰になると、第1結晶層104上に形成される層のキャリアをも捕獲してしまう。このため、第1結晶層104上に、活性層として機能する第2結晶層を形成すると、第2結晶層においてチャネルを形成するべきキャリアが、第1結晶層104に過剰に含まれる第2原子により捕獲され、トランジスタの変調特性に悪い影響を与える可能性もある。これに対して半導体基板200では、第1結晶層104と第2結晶層202の間に、補償不純物である第2原子の濃度が第1結晶層104よりも低い第3結晶層204を挿入する。一般に第1原子の濃度は図1のSIMS深さプロファイルに示すように、上層(層の表面側)において、より一定した濃度プロファイルを示しやすい傾向がある。このため、第1結晶層104よりも上層側の第3結晶層204では、第2原子を過剰にドープ量を、第1原子を補償するとともに、第2原子によって発生するホールの濃度が極め

て低いレベルとなるように調整することで、第 3 結晶層 2 0 4 を空乏状態にすることができる。第 3 結晶層 2 0 4 のキャリア濃度は、 $1 \times 10^{-1.7}$  c m  $^{-3}$  以下、好ましくは  $1 \times 10^{-1.6}$  c m  $^{-3}$  以下、特に好ましくは  $1 \times 10^{-1.4}$  c m  $^{-3}$  以下である。キャリア濃度は、S I M S により測定した場合のキャリア濃度をいう。第 3 結晶層 2 0 4 の厚みは 5 0 n m以上が好ましい。

### [0026]

空乏状態にある第3結晶層204が第1結晶層104と第2結晶層202の間に存在することにより、第2結晶層202を走行する電子またはホールが第1結晶層104に存在する電子またはホールと相互作用することがなくなる。この結果、第2結晶層202を活性層として電界効果トランジスタを形成した場合、当該電界効果トランジスタの電流・電圧曲線(IV曲線)にキンクが出るなどの素子の異常動作を防ぐことができる。

### [0027]

なお、第1結晶層104とベース基板102との間に、界面の性状をコントロールする目的で、界面制御層を形成してもよい。たとえばベース基板102としてSiを用い、第1結晶層104としてGaN層を形成する場合、GaとSiが反応してGaNの結晶性を劣化させる場合がある。このような場合、界面制御層としてA1Nを配置しても良い。

# [0028]

図4は、半導体基板300の断面例を示す。半導体基板300は、ベース基板102、第1結晶層104、第3結晶層204、阻害層302、第4結晶層304および第5結晶層306を有する。半導体基板300のベース基板102、第1結晶層104および第3結晶層204は、半導体基板100および半導体基板200のベース基板102、第1結晶層104および第3結晶層204は、電界効果トランジスタのチャネル層に適用できる結晶層である。第4結晶層304は、電界効果トランジスタのショットキ層に適用できる結晶層である。第4結晶層304および第5結晶層304および第5結晶層306は、図3の半導体基板200における第2結晶層202に対応する。本例において第4結晶層304は第3結晶層204上に形成され、第5結晶層306は第4結晶層上に形成される。また、図4においては第1結晶層104の下部が開口内部に形成され、上部が開口から突出して形成される。

# [0029]

第1結晶層104、第3結晶層204、第4結晶層304および第5結晶層306は、ベース基板102上に部分的に形成されている。ここで言う部分的に形成されるとは、ベース基板102の全面ではなく、ある限られた範囲に結晶が成長されている様子を示す。すなわち、ベース基板102の上または上方に阻害層302が形成され、阻害層302に形成した開口の内部に第1結晶層104、第3結晶層204、第4結晶層304および第5結晶層306が形成されている。

# [0030]

阻害層302は、結晶の成長を阻害する。阻害層302は、第1結晶層104に含まれる第1原子と同一の原子を含む。阻害層302として、酸化シリコン層、窒化シリコン層または酸窒化シリコン層が挙げられる。

# [0031]

第4結晶層304は、電界効果トランジスタを作製したときに電界効果トランジスタのチャネルを構成する。第4結晶層304の材料として、GaAs、AlGaAs、InGaAs、InGaAs、InGaAs、InGaAs、InGaAs、InGaAs、InGaAs、InGaAs、InGaAs、InGaAs、InGaAs、InGaAs、InGaAs、InGaAs、InGaAs、InGaAs、InGaAs。第4結晶層304の厚みは、100nmから1000nmの範囲であってよい。

# [0032]

第 5 結晶層 3 0 6 は、第 4 結晶層 3 0 4 とヘテロ界面を構成し、電界効果トランジスタを作製したとき当該ヘテロ界面にチャネル電荷を誘起する。第 5 結晶層 3 0 6 として、第 4 結晶層 3 0 4 とヘテロ界面が構成できる材料、たとえば G a A s 、 A 1 G a A s 、 I n G a A s 、 I n G a A s 、 I n G a P 、 G a N 、 A 1 G a N 、 I n A 1 N 、 A 1 N 、 I n A 1 G a N が挙 げられる。第 5 結晶層 3 0 6 の厚みは、ヘテロ接合結晶に発生する格子定数差による応力

10

20

30

40

が結晶の弾性限界内に保たれる範囲内で、トランジスタのオン抵抗、耐圧などを勘案し決定できる。第5結晶層306の厚みとして、1nmから300nmの範囲が例示できる。

# [0033]

半導体基板300の製造方法を説明する。まず、ベース基板102に接して阻害層302を形成する。阻害層302として、たとえば酸化シリコン層、窒化シリコン層あるいは酸窒化シリコン層を蒸着法、スパッタ法、熱CVD法、プラズマCVD法などにより形成し、エッチングにより開口を形成する。開口は、ベース基板102に達する深さで形成する。あるいは、ベース基板102上にNiなどからなるマスクを形成し、マスク開口の底に露出したSi面を酸化、窒化または酸窒化することにより阻害層302が形成できる。酸化は熱酸化、プラズマ酸化などが利用できる。窒化はアンモニアなどの窒素源をベース基板102の表面に導入し、熱窒化またはプラズマ窒化により実施できる。

### [0034]

次に、阻害層302の開口底部のベース基板102上に、第1結晶層104、第3結晶層204、第4結晶層304、第5結晶層306をこの順に積層する。これらの結晶層は、エピタキシャル成長で形成されることが好ましい。エピタキシャル成長法として、たとえば有機金属気相成長法(以下においてMOCVD法と記載することがある)、分子線エピタキシー法(以下においてMBE法と記載することがある)、ハライド気相成長法(HVPE法)が挙げられる。なお、エピタキシャル成長の過程で、阻害層302上には、結晶層が形成されない。このため、第1結晶層104、第3結晶層204、第4結晶層304、第5結晶層306は、阻害層302の開口にのみ形成される。

### [0035]

MOCVD法で形成する場合、3族元素原料として、トリメチルガリウム(TMG)およびトリメチルアルミニウム(TMA)、トリメチルインジウム(TMI)等を用いることができる。窒素原料としてアンモニア(NH<sub>3</sub>)等を用いることができる。原料のキャリアガスとして、高純度水素、高純度窒素を用いることができる。エピタキシャル成長条件は、例えば、反応炉内圧力 0 . 1 a t m、成長温度 1 0 0 0 、成長速度 0 . 1 μ m / h r 以上 3 μ m / h r 以下である。

### [0036]

前述したエピタキシャル成長させる工程において、第1結晶層104および第3結晶層204を成長させる際に、同時に、Mg原子、Zn原子、Be原子およびC原子からなる群より選択された少なくとも1つの原子を不純物原子としてドープする。つまり、第2原子をドーピングしながら、結晶層をエピタキシャル成長により形成する。この際、3族原料および5族原料とともに反応炉内にドープ原料ガスを導入すればよい。ドープ原料としては、ビスシクロペンタジエニルマグネシウム、四塩化炭素、ジエチルジンク、ビスメチルシクロペンタジエニルマリウムなどを用いることができる。なお、不純物原子である第2原子を含まない第1結晶前駆体層および第3結晶前駆体層をエピタキシャル成長で形成した後に、不純物原子をイオン注入または熱拡散等により当該前駆体層にドーピングすることで、第1結晶層104および第3結晶層204を形成してもよい。

# [0037]

図5は、電界効果トランジスタ400の断面例を示す。電界効果トランジスタ400は、ベース基板102、第1結晶層104、第3結晶層204、阻害層302、チャネル層402、ショットキ層404、オーミック電極406およびゲート電極408を有する。電界効果トランジスタ400のベース基板102、第1結晶層104、第3結晶層204および阻害層302は、半導体基板100、半導体基板200および半導体基板300のベース基板102、第1結晶層104、第3結晶層204および阻害層302と同様である。

### [0038]

チャネル層 4 0 2 およびショットキ層 4 0 4 は、半導体基板 3 0 0 における第 4 結晶層 3 0 4 および第 5 結晶層 3 0 6 と同様であり、オーミック電極 4 0 6 およびゲート電極 4 0 8 を形成することで、第 4 結晶層 3 0 4 および第 5 結晶層 3 0 6 が各々チャネル層 4 0

10

20

30

40

2 およびショットキ層 4 0 4 になる。オーミック電極 4 0 6 は電界効果トランジスタ 4 0 0 と外部回路とを接続する。オーミック電極 4 0 6 として、ショットキ層 4 0 4 側から T i / A u の積層金属構造が例示できる。ゲート電極 4 0 8 は電界効果トランジスタ 4 0 0 に信号を入力する。ゲート電極 4 0 8 として、ショットキ層 4 0 4 側から N i / A u の積層金属構造が例示できる。

### [0039]

電界効果トランジスタ400の製造方法を説明する。電界効果トランジスタ400は、 半導体基板300を用いて製造する。半導体基板300における第5結晶層306の上に 、ゲート電極408と、ゲート電極408から離してゲート電極408を挟むようにして 二つのオーミック電極406を形成する。

### [0040]

オーミック電極406およびゲート電極408を構成する金属は、たとえば蒸着法、スパッタ法またはCVD法で形成される。所望の形状に形成するにはフォトリソグラフィ法を用いることができる。フォトリソグラフィ法とリフトオフ法の組み合わせでオーミック電極406およびゲート電極408が形成できる。オーミック電極406は、よりよいオーミック接触性を得るためにアニールされることが好ましい。アニール条件として、窒素雰囲気中で800 、30秒の熱処理を挙げることができる。

# 【実施例】

# [0041]

ベース基板102として(111)面が主面の2インチSi基板を準備した。Si基板上の全面に、阻害層302として酸化シリコン層を堆積した。酸化シリコン層は、スパッタ法にて150nmの厚みで堆積した。酸化シリコン層の上に100μm角の開口を有する感光性樹脂をフォトリソグラフィにより形成し、感光性樹脂をマスクとして酸化シリコン層と自然酸化膜をウェットエッチングしてSi基板を露出させた。

# [0042]

感光性樹脂を除去した後、Si基板をエピタキシャル成長炉に搬入し、表面前処理の後、炉内に原料ガスを供給して、界面制御層、第1結晶層104としてのバッファ層、第3結晶層204としての空乏結晶層、チャネル層402およびショットキ層404をエピタキシャル成長で形成した。各層の組成、厚み、Mg原子のドーピング濃度を表1に示す。

# 【表1】

| 結晶層    | 組成                                       | 厚み(nm) | Mg濃度(cm <sup>-3</sup> ) |

|--------|------------------------------------------|--------|-------------------------|

| ショットキ層 | Al <sub>0.2</sub> Ga <sub>0.8</sub> N    | 20     |                         |

| チャネル層  | GaN                                      | 500    |                         |

| 空乏結晶層  | A I <sub>0. 3</sub> Ga <sub>0. 7</sub> N | 150    | 2×10 <sup>19</sup>      |

| バッファ層  | A I <sub>0. 3</sub> Ga <sub>0. 7</sub> N | 500    | 5×10 <sup>20</sup>      |

| 界面制御層  | Al <sub>0.7</sub> Ga <sub>0.3</sub> N    | 10     |                         |

# [0043]

比較のため、表1に記載と同様の結晶構造を有し、バッファ層および空乏結晶層に対応する層にMg原子がドープされていない基板を作製した。以下、Mg原子がドープされた基板を「ドープ基板」、Mg原子がドープされていない基板を「非ドープ基板」と呼称する。

# [0044]

原料ガスとして、トリメチルガリウム(TMG)、トリメチルアルミニウム(TMA) 、ビスシクロペンタジエニルマグネシウムおよびアンモニア(NH<sub>3</sub>)を用いた。成長炉 10

20

30

内の圧力は30kPaに保った。原料ガスのキャリアガスとして、水素を用いた。各層の成長においては、各原料の供給量、基板温度を制御しながら行った。

### [0045]

ドープ基板および非ドープ基板の結晶層をSIMSにより分析したところ、バッファ層および空乏結晶層には、 $5 \times 10^{-1}$  c m  $^{-3}$  から  $1 \times 10^{-1}$  8 c m  $^{-3}$  の Si原子および  $5 \times 10^{-1}$  7 c m  $^{-3}$  から  $1 \times 10^{-1}$  8 c m  $^{-3}$  の O 原子が混入していた。

### [0046]

ドープ基板および非ドープ基板にオーミック電極、素子分離、ゲート電極をこの順番で形成し、電界効果トランジスタを作製した。オーミック電極は、結晶側から、Ti(10nm)/Al(150nm)/Al(300nm)とした。オーミック電極は、蒸着法、フォトリソグラフィおよびリフトオフ法を用いて形成した。オーミック電極は、形成後に800 で60秒間、窒素雰囲気中でのアニールを実施した。

# [0047]

素子分離は窒素イオンを打ち込むことで行った。打ち込みの加速電圧は20 KeVおよび 100 KeVとした。窒素イオンのドーズ量は、どちらも  $1\times10^{-1.4} cm^2$ とした。ゲート電極は、結晶側から、Ni(15nm)/Au(200nm)とした。ゲート電極は、蒸着法、フォトリソグラフィおよびリフトオフ法を用いて形成した。作製したトランジスタは、ドープ基板を使用したものをドープトランジスタ、非ドープ基板を用いたものを非ドープトランジスタと呼称する。

# [0048]

図6は、ドープトランジスタのIV特性を示す。図7は、非ドープトランジスタのIV特性を示す。IV特性は、オーミック電極の一つ(ソース)をグランドとし、もう一つのオーミック電極(ドレイン)に与える電圧を0Vから10Vまで変化させ、その間にドレインに流れる電流を評価した。また、ゲート電圧Vgを0Vから-5Vまで、1Vステップで変化させてIV特性を評価した。

# [0049]

非ドープトランジスタでは、ゲート電圧を変化させた 0 V ~ - 5 V の範囲のうち、限られた電圧範囲でしかドレイン電流の変調は見られなかった。また、非ドープトランジスタでは、ゲート電圧として負電圧を印加しても、ドレイン電圧はピンチオフしなかった。

# [0050]

これに対し、ドープトランジスタでは、印加したゲート電圧の範囲(0V~-5V)の全域でドレイン電流の変調が観察できた。これはゲート電圧によるドレイン電流の良好な制御性を示す。またドープトランジスタでは、ドレイン電圧はピンチオフし、良好なピンチオフ性を示した。このような非ドープトランジスタとドープトランジスタの性能の差は、バッファ層と空乏結晶層にMg原子をドープしたことにより得られた効果である。

# [0051]

なお、前述した実施の形態では、半導体デバイスとして電界効果トランジスタを例示しているが、バイポーラトランジスタ、LED等他の能動デバイスであってもよい。

# 【符号の説明】

# [0052]

100…半導体基板、102…ベース基板、104…第1結晶層、200…半導体基板、202…第2結晶層、204…第3結晶層、300…半導体基板、302…阻害層、304…第4結晶層、306…第5結晶層、400…電界効果トランジスタ、402…チャネル層、404…ショットキ層、406…オーミック電極、408…ゲート電極

10

20

30

# フロントページの続き

(56)参考文献 特開2006-332367(JP,A)

特開2003-257997(JP,A)

特表2012-523702(JP,A)

(58)調査した分野(Int.CI., DB名)

H01L 21/337-338

H01L 27/095-098

H01L 21/20

H01L 29/778

H01L 29/80-812