# (12) UK Patent Application (19) GB (11) 2 317 270 (13) A

(43) Date of A Publication 18.03.1998

- (21) Application No 9718654.8

- (22) Date of Filing 04.09.1997

- (30) Priority Data

(31) 9618620.0

(32) 06.09.1996

.**1996** (33

(33) **GB**

(71) Applicant(s)

**Trikon Equipments Limited**

(Incorporated in the United Kingdom)

Coed Rhedyn, Ringland Way, NEWPORT, Gwent, NP6 2TA, United Kingdom

(72) Inventor(s)

**Christopher David Dobson**

(74) Agent and/or Address for Service

Wynne-Jones, Lainé & James 22 Rodney Road, CHELTENHAM, Gloucestershire, GL50 1JJ, United Kingdom

- (51) INT CL<sup>6</sup>

H01L 21/20 21/68

- (52) UK CL (Edition P )

H1K KLDX K3P5 K8VD

- (56) Documents Cited US 5275683 A

- (58) Field of Search

UK CL (Edition O ) H1K KLDX KLX KMBC

INT CL<sup>6</sup> H01L

ON LINE,W.P.I.

#### (54) Forming a layer on a pre-stressed semiconductor wafer

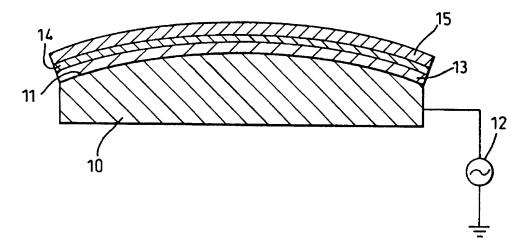

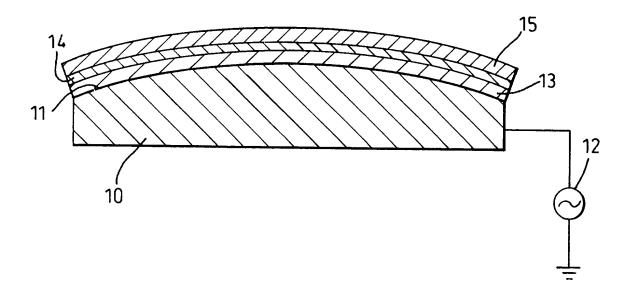

(57) A method of forming a layer 15 on a semiconductor wafer 13 comprises applying tensile stress to the wafer, depositing the layer on the wafer, and releasing the wafers from the stressed condition. A seed layer 14 is deposited on the wafer before the wafer is stressed by means of an electrostatic chuck 10 with a convex surface 11. The layer 15 is then deposited on the wafer and allowed to harden or set. On release from the chuck, the wafer flattens to compress the layer 15 and prevent the formation of cracks.

#### A Method of Forming a Layer

This invention relates to a method of forming a layer on a semiconductor wafer.

In a number of manufacturing processes involving semiconductor wafers, it is known to deposit a generally liquid 5 layer on to the surface of the wafer and there is then a need to remove moisture from that layer, before further layers can be deposited or other processing steps carried out. Examples of such process are the spin-on glass process or planarisation processes such as the one described in 10 International Patent Application No. PCT/GB93/01368. layers (which 'term includes films) are generally tensile layers and the resultant internal forces often lead to the layers becoming cracked as the moisture is removed, unless great care is taken. Sometimes other processing steps have 15 to take place, for example the deposition of a water permeable capping layer prior to any drying process.

From one aspect the present invention consists in a method of forming a layer on a semi-conductor wafer, comprising applying tensile stress to the wafer, depositing a tensile layer on the stressed wafer and releasing the wafer from the stressed condition.

20

25

The result of the release of the wafer from the stressed condition will be to create a compressive stress within the layer which will serve to counterbalance the tensile nature of the layer and hence remove or reduce the

likelihood of cracking.

5

10

15

20

25

In a preferred embodiment the wafer is stressed by bending and this may, for example, be achieved by clamping the wafer to an electrostatic chuck having a convex curved support surface.

Preferable the layer is allowed to harden or is hardened or set in some other way prior to the release of the stress. It is particularly preferred that a seed layer is deposited on the wafer prior to the wafer being stressed.

The invention also consists in apparatus for bending a wafer including an electrostatic chuck having a convex curved support surface.

Although the invention has been defined above, it is to be understood that it includes any inventive combination of the features set out above or in the following description.

The invention may be performed in various ways and specific embodiments will now be described, by way of example, with reference to the accompanying drawing which is a schematic cross section through a wafer clamped to an electrostatic chuck.

In the figure, an electrostatic chuck 10 has a convex upper surface 11 and is powered from power source 12. The general operation of an electrostatic chuck is well known and is conveniently summarised in an article by Larry D Hartsough in Solid State Technology which appears on page 87 of the January 1993 issue. More detailed constructions and operations are described in the references to that article and they and the article are hereby incorporated by refer-

ence. The normal purpose of such chucks is to create an electrostatic distribution on the top of a dielectric support so that the wafer is held flat relative to the support so that a gas heat transfer medium trapped between the two can create a uniform heat transfer over the entire surface of the wafer. However, in this case the upper surface 11 is clearly convex so that when the wafer 13 is clamped to the chuck 10 it is subjected to tensile stress.

5

Preferable, prior to the wafer being so stressed, a seed layer 14 is deposited on the wafer 13. Once the wafer 10 13 is stressed, a tensile film or layer 15 is deposited using the appropriate techniques, such as those mentioned The layer 15 is then hardened or allowed to harden or set or partially set. When it is in the desired condi-15 tion, the wafer 11 is released from the chuck 10 and it returns to its normally flat condition. In doing so it places the layer 15 under a compressive load and this serves to resist the tensile forces within the layer 15, which would otherwise cause it to crack as moisture is removed 20 from it. Traditionally precautions taken during the moisture removing steps can therefore either be reduced or dispensed with altogether.

It will be understood that other methods of bending the wafer maybe used; the attraction of the electrostatic chuck is that it avoids the need for any engagement of the upper surface of the wafer 13. It will be further understood that the operation may occur on a number of occasions as the semi-conductor device is built up on the wafer by oper-

ations, but care may need to be taken that subsequent bending of the wafer does not cause damage to layers deposited earlier. It may, for example, be desirable to use chucks with successively shallower curves as the device builds up.

#### Claims

- 1. A method of forming a layer on a semiconductor wafer, comprising, applying tensile stress to the wafer, depositing a tensile layer on the stressed wafer and releasing the wafer from the stressed condition.

- 2. A method as claimed in claim 1 wherein the wafer is stressed by bending.

- A method as claimed in claim 2 wherein the wafer is stressed by clamping the wafer to an electronic chuck having

a convex curved support surface.

- 4. A method as claimed in any one of the preceding claims wherein the layer is allowed to harden or is hardened or set prior to the release of the stress.

- 5. A method as claimed in any one of the preceding claims wherein a seed layer is deposited on the wafer prior to the wafer being stressed.

- 6. A method of forming a layer on a semiconductor wafer substantially as herein before described with reference to the accompanying drawings.

- 7. Apparatus for bending a semiconductor wafer including an electrostatic chuck having a convex support surface.

8. Apparatus for bending a semiconductor wafer substantially as herein before described.

7

**Application No:**

GB 9718654.8

Claims searched: All

Examiner:

C.D.Stone

Date of search:

12 January 1998

## Patents Act 1977 Search Report under Section 17

#### Databases searched:

UK Patent Office collections, including GB, EP, WO & US patent specifications, in:

UK Cl (Ed.P): H1K(KLX,KMBC,KLDX)

Int Cl (Ed.6): H01L

Other: ON LINE, W.P.I.

### Documents considered to be relevant:

| Category | Identity of document and relevant passage |                                    | Relevant<br>to claims |

|----------|-------------------------------------------|------------------------------------|-----------------------|

| X        | US 5275683                                | TOKYO ELECTRON (See col.7 line 20) | 1,7                   |

- Document indicating lack of novelty or inventive step

Document indicating lack of inventive step if combined with one or more other documents of same category.

- & Member of the same patent family

- A Document indicating technological background and/or state of the art.

P Document published on or after the declared priority date but before the filing date of this invention.

- E Patent document published on or after, but with priority date earlier than, the filing date of this application.