# (10) **DE 10 2006 017 768 A1** 2007.10.18

(12)

# Offenlegungsschrift

(21) Aktenzeichen: 10 2006 017 768.1

(22) Anmeldetag: 15.04.2006(43) Offenlegungstag: 18.10.2007

(71) Anmelder:

Infineon Technologies AG, 81669 München, DE

(74) Vertreter:

Wilhelm & Beck, 80639 München

(72) Erfinder:

Wallner, Paul, 83209 Prien, DE; Dietrich, Stefan, 82299 Türkenfeld, DE; Gregorius, Peter, 81476 München, DE

(51) Int CI.8: **G11C** 7/10 (2006.01)

**G11C** 7/22 (2006.01)

(56) Für die Beurteilung der Patentfähigkeit in Betracht gezogene Druckschriften:

US 61 25 078 A

JEDEC Standard, Double Data Rate (DDR) SDRAM SPECIFICATION, JESD79D, (Revision of JESD79C).

JEDEC SOLID STATE TECHNOLOGY ASSOCIATION. 2500

Wilson Boulevard, Arlington, VA 22201-3834,

January 2004, S.1,5;

128/144-Mbit RDRAM Datasheet (32 Split Bank Architecture), Preliminary Information Version 1.11, Rambus Inc., 2465 Latham Street, Mountain View, California, USA, 94040, 2000, S.1,4;

Die folgenden Angaben sind den vom Anmelder eingereichten Unterlagen entnommen

Prüfungsantrag gemäß § 44 PatG ist gestellt.

(54) Bezeichnung: Integrierter Speicherbaustein sowie Verfahren zum Betrieb eines integrierten Speicherbausteins

(57) Zusammenfassung: Integrierter Speicherbaustein, der ein Speicherzellenfeld zum Auslesen von Daten, eine Eingangsschaltung zum Empfangen von Kommandodaten und zum Bereitstellen von Ansteuersignalen für das Speicherzellenfeld, einen Ausgangspuffer zum Puffern von aus dem Speicherzellenfeld ausgelesenen Daten, und einen Zeitgeber, der gestaltet ist, den Ausgangspuffer so anzusteuern, dass eine festgelegte Zeitspanne nach dem Bereitstellen der Ansteuersignale die gepufferten Daten an einem Ausgang bereitgestellt werden, umfasst.

### **Beschreibung**

**[0001]** Die Erfindung betrifft einen integrierten Speicherbaustein mit einem Speicherzellenfeld, sowie ein Verfahren zum Betrieb eines integrierten Speicherbausteins mit einem Speicherzellenfeld.

**[0002]** Moderne Computersysteme und Datenverarbeitungsanlagen stellen hohe Ansprüche an die dort zum Einsatz kommenden Datenspeicher. Diese müssen in der Lage sein, umfangreiche Daten innerhalb einer möglichst kurzen Zugriffszeit zur Verfügung zu stellen. Schnelle Datenspeicher, die diesen Anforderungen gerecht werden, sind Datenspeicher mit elektronischen integrierten Speicherbausteinen, wie beispielsweise sog. DRAM-Bausteinen (Dynamic Random Access Memory).

[0003] Oft werden jedoch Speicherkapazitäten gefordert, die in der Regel nicht von einem einzelnen Baustein erfüllt werden können. Man bettet daher in bekannter Weise mehrere integrierte Speicherbausteine in ein Speichersystem hoher Kapazität ein. Der einzelne integrierte Speicherbaustein muss daher mit Speichercontrollern und/oder anderen Speicherbausteinen zusammenarbeiten um eine störungsfreie und zeiteffiziente Koordination des Datenflusses zu gewährleisten.

[0004] Bei bekannten Speichersystemen mit mehreren integrierten Speicherbausteinen wird so beispielsweise eine Leseanforderung an alle Speicherbausteine, an eine Gruppe von Speicherbausteinen oder an einen einzelnen Speicherbaustein abgegeben, wobei der entsprechende Speicherbaustein dann die angeforderten Daten nach einer sog. Latenzzeit nach dem Empfangen der Leseanforderung ausgibt. Die Latenzzeit ist hier also im Sinne der Zeitspanne definiert, die sich von dem Absetzen einer Leseanforderung bis zum Empfang der angeforderten Daten erstreckt. Die Speichersysteme umfassen dabei viele einzelne Speicherbausteine, die mithilfe komplexer und hoch entwickelter Herstellungsprozesse in hohen Stückzahlen hergestellt werden.

[0005] Trotz der hohen und optimierten Reproduzierbarkeit etablierter Herstellungsprozesse ist die Herstellung identischer Bausteine unmöglich. Vielmehr unterliegen die einzelnen Bausteine prozessbedingter Varianzen, die sich vor allem hinsichtlich einer von Baustein zu Baustein variierenden Latenzzeit bemerkbar machen. Ferner führen während des Betriebs auch Schwankungen der Versorgungsspannung und der Umgebungstemperatur zu einer Veränderung der Latenzzeit. Die genannten Varianzen werden zusammenfassend auch als PVT-Varianz (Process Voltage Temperature) bezeichnet. Die Zeitspanne zwischen der Anforderung und dem Erhalt der Daten variiert somit und ist auch nicht exakt einstellbar.

[0006] Die variierende Latenzzeit bekannter Speicherbausteine führt beim Zusammenspiel mehrerer Speicherbausteine hinsichtlich der zeitlichen Effizienz zu gewissen Einschränkungen: Um die Anzahl der integrierten Speicherbausteine in einem Speichersystem - und damit auch die Gesamtspeicherkapazität - bei gleichzeitiger Minimierung der Zugriffszeit zu erhöhen, muss der einzelne integrierte Speicherbaustein in der Lage sein, in verlässlicher Weise nach einer wohldefinierten und über der gesamten Betrieb konstanten Zugriffszeit die angeforderten Daten bereitzustellen. Benutzen ferner mehrere Speicherbausteine einen gemeinsamen Datenbus zur Ausgabe der Daten, so beispielsweise bei einer Hintereinanderschaltung, so wird es erforderlich, dass der einzelne Speicherbaustein zu einem wohl-definierten und bestimmbaren Zeitpunkt die Daten in einen Datenstrom einfügt. Andernfalls entstehen Kollisionen, wenn ein Speicherbaustein zu einem Zeitpunkt Daten ausgibt, zu dem bereits Datensignale am Ort der Signalmündung anliegen. Ferner führt eine zu großzügig bemessene Wartezeit zwischen zweie aufeinander folgenden Leseanforderungen zu einer zu geringen Auslastung der Signalwege.

[0007] Es ist daher Aufgabe der vorliegenden Erfindung, einen verbesserten integrierten Speicherbaustein bereitzustellen, dessen Zugriffszeit festlegbar und wohldefiniert ist, und ferner konstant über den gesamten Betrieb bleibt. Es ist ferner Aufgabe der vorliegenden Erfindung, ein Verfahren zum Betrieb eines integrierten Speicherbausteins bereitzustellen, das eine festlegbare, wohldefinierte und konstante Zugriffszeit auf angeforderte Daten ermöglicht.

**[0008]** Diese Aufgabe wird durch den integrierten Speicherbaustein gemäß Anspruch 1 und dem Verfahren zum Betrieb eines integrierten Speicherbausteins gemäß Anspruch 16 gelöst. Weitere vorteilhafte Ausgestaltungen der Erfindung sind in den abhängigen Ansprüchen angegeben.

[0009] Gemäß einem ersten Aspekt der vorliegenden Erfindung ist ein integrierter Speicherbaustein vorgesehen, der im folgenden näher beschrieben wird. Zunächst weist der integrierte Speicherbaustein ein Speicherzellenfeld zum Auslesen von Daten auf. Eine Eingangsschaltung empfängt Kommandodaten und stellt Ansteuersignale für das Speicherzellenfeld bereit. Durch das Bereitstellen von Ansteuersignalen können aus dem Speicherzellenfeld Daten ausgelesen werden. Der integrierte Speicherbaustein weist ferner einen Ausgangspuffer zum Puffern von aus dem Speicherzellenfeld ausgelesenen Daten und einen Zeitgeber auf. Der Zeitgeber steuert den Ausgangspuffer so an, dass die gepufferten Daten eine festgelegte Zeitspanne nach dem Bereitstellen des Ansteuersignals an einen Ausgang ausgegeben werden.

[0010] Der erfindungsgemäße integrierte Speicherbaustein erlaubt, durch das Vorsehen eines Ausgangspuffers und eines Zeitgebers, Daten, die aus dem Speicherzellenfeld ausgelesen werden, zum Zeitpunkt des Auslesens aus dem Speicherzellenfeld zu puffern und erst nach Ablauf einer festgelegten Zeitspanne nach dem Anfordern an einem Ausgang bereitzustellen. Hierfür werden zunächst Kommandodaten von einer Eingangsschaltung entgegengenommen und in Ansteuersignale für das Speicherzellenfeld umgewandelt. Diese Umwandlung ist unabhängig vom Speicherzellenfeld, und dauert daher in der Regel immer gleich lang. Der Zeitgeber nimmt das Bereitstellen der Ansteuersignale auf, und kann somit den Beginn der festgelegten Zeitspanne feststellen. Ab dem Bereitstellen der Ansteuersignale werden die auszulesenden Daten aus dem Speicherzellenfeld ausgelesen und nach der Latenzzeit bereitgestellt. Diese durch die Latenzzeit gegebene effektive Zugriffszeit unterliegt der fertigungs- und umgebungsbedingten bereits oben erwähnten PVT-Varianz (Process Voltage Temperature). Diese sind in der Regel nicht vorhersehbar oder kontrollierbar, jedoch lässt sich oft eine zeitliche Obergrenze dafür angegeben. Sobald die ausgelesenen Daten von dem Speicherzellenfeld bereitgestellt werden, werden diese in dem Ausgangspuffer gepuffert. Der Zeitgeber veranlasst jedoch den Ausgangspuffer erst nach dem Ablauf der festgelegten Zeitspanne nach dem Anfordern der Lesedaten die ausgelesenen Daten an den Ausgang weiterzuleiten. Somit ist erfindungsgemäß gewährleistet, dass der integrierte Speicherbaustein eine wohl definierte und zeitlich konstante Latenzzeit aufweist. Die festgelegte Zeitspanne ist dabei derart, dass sie auch maximale PVT-Varianz abdeckt, und es ist gewährleistet, dass die Daten vor der Weitergabe an den Ausgang in jedem Fall in den Ausgangspuffer von dem Speicherzellenfeld geschrieben wurden.

[0011] Gemäß einem zweiten Aspekt der vorliegenden Erfindung ist ein Verfahren zum Betrieb eines Speicherbausteins, insbesondere eines oben beschriebenen integrierten Speicherbausteins, vorgesehen. Das erfindungsgemäße Verfahren umfasst dabei die folgenden Schritte: Zunächst ist ein Bereitstellen von Kommandodaten vorgesehen. Danach ist ein Bereitstellen eines von den Kommandodaten abhängigen Ansteuersignals für ein Speicherzellenfeld vorgesehen. Hierauf erfolgt ein Puffern von aus dem Speicherzellenfeld ausgelesenen Daten. Abschließend erfolgt ein Ausgeben der gepufferten Daten an einen Ausgang nach Ablauf einer festgelegten Zeitspanne nach dem Bereitstellen des Ansteuersignals.

**[0012]** Das erfindungsgemäße Verfahren hat den Vorteil, dass angeforderte Daten eine wohldefinierte und konstante Zeit nach deren Anforderung an einem Ausgang bereitstehen. Das Zusammenspiel mehrerer integrierter Speicherbausteine kann somit zeitlich

effizient gestaltet werden.

[0013] Gemäß einer Ausführungsform der vorliegenden Erfindung weist die Eingangsschaltung eine Parallelisierungseinheit zur Parallelisierung serieller Kommandodaten auf. Die Eingangsschaltung empfängt die Kommandodaten und stellt daraufhin die Ansteuersignale für das Speicherzellenfeld bereit. Das Speicherzellenfeld, üblicherweise in Zeilen und Spalten angeordneten Speicherzellen umfassend, benötigt zur Auswahl der entsprechenden Zellen letztendlich parallelisierte Ansteuersignale. Das Vorsehen einer Parallelisierungseinheit ermöglicht daher auch ein Vorsehen der Kommandodaten in serieller Form und reduziert damit die Anzahl der erforderlichen Zuleitungen des Speicherbausteins auf ein Minimum.

[0014] Gemäß einer weiteren Ausführungsform der vorliegenden Erfindung weist die Eingangsschaltung eine Protokolleinheit zur Dekodierung der Kommandodaten auf. Die Protokolleinheit ist dabei in der Lage, Kommandodaten, die in ein Protokoll eingebettet sind, zu dekodieren, um die Ansteuersignale bereitzustellen. Die erfindungsgemäße Einbettung der Kommandodaten in ein Protokoll erlaubt eine praktisch unbegrenzte Breite der Kommandostruktur bei einer weitestgehend Unabhängigkeit von fest verdrahteten Adress-, Steuer- und Datenleitungen.

[0015] Gemäß einer weiteren Ausführungsform der vorliegenden Erfindung weist die Eingangsschaltung eine Durchleitungseinheit zur Weitergabe der Kommandodaten an einen weiteren Ausgang auf. Der erfindungsgemäße Speicherbaustein ist dadurch in der Lage, die empfangenen Kommandodaten weiteren Komponenten – so beispielsweise einem weiteren integrierten Speicherbaustein – zur Verfügung zu stellen.

[0016] Gemäß einer weiteren Ausführungsform der vorliegenden Erfindung weist der Speicherbaustein einen weiteren Eingang und eine weitere Durchleitungseinheit auf. Der weitere Eingang empfängt dabei Nutzdaten und die weitere Durchleitungseinheit gibt diese Nutzdaten an den Ausgang weiter. Der erfindungsgemäße Speicherbaustein ist dadurch in der Lage, die beispielsweise von anderen Speicherbausteinen ausgelesenen Nutzdaten durchzuleiten, und ermöglicht so auch eine Hintereinanderschaltung mehrerer Speicherbausteine.

[0017] Gemäß einer weiteren Ausführungsform der vorliegenden Erfindung weist der Ausgangspuffer einen FIFO-Puffer auf. Ein derartiger FIFO-Puffer (First In First Out) ist in vorteilhafter Weise in der Lage, auch mehrere empfangene Datensätze zu Puffern, und diese auf Anforderung auszugeben, ohne die ursprüngliche Reihenfolge der ausgelesenen Daten zu stören.

[0018] Gemäß einer weiteren Ausführungsform der vorliegenden Erfindung weist der Ausgangspuffer einen Demultiplexer und wenigstens zwei Pufferregister auf. Der Demultiplexer leitet dabei abhängig von einem Eingangszeiger die ausgelesenen Daten an eines der wenigstens zwei Pufferregister weiter. Das erfindungsgemäße Vorsehen wenigstens zweier Pufferregister erlaubt das erneute Puffern ausgelesener Daten, selbst wenn die zuvor ausgelesenen Daten noch nicht ausgegeben wurden. Der Demultiplexer verteilt dabei die Daten an das entsprechende Pufferregister und wird durch den Eingangszeiger gesteuert.

[0019] Gemäß einer weiteren Ausführungsform der vorliegenden Erfindung weist der Ausgangspuffer eine Steuereinheit zum Bereitstellen des Eingangszeigers auf. Dabei wird der Eingangszeiger abhängig von einem Bereit-Signal, das von dem Speicherzellenfeld bereitgestellt wird, verändert. Das Bereit-Signal des Speicherzellenfelds signalisiert die Ankunft der angeforderten Daten, die nun im Ausgangspuffer gepuffert werden müssen. Die Steuereinheit verändert abhängig von diesem Bereit-Signal den Eingangszeiger und wählt ein nächstes freies Pufferregister zum Puffern der bereitgestellten Daten aus.

**[0020]** Gemäß einer weiteren Ausführungsform der vorliegenden Erfindung weist der Zeitgeber eine weitere Steuereinheit zum Bereitstellen eines Ausgangszeigers für die Pufferregister auf.

**[0021]** Dabei leiten die Pufferregister abhängig von dem Ausgangszeiger die gepufferten Daten an den Ausgang weiter. Der Ausgangszeiger bestimmt, welches Pufferregister die gepufferten Daten ausgibt. Erfindungsgemäß weist der Zeitgeber hierfür die weitere Steuereinheit zum Bereitstellen dieses Ausgangszeigers auf, um nach Ablauf der festgelegten Zeitspanne das entsprechende Pufferregister zur Ausgabe der gepufferten Daten zu veranlassen.

[0022] Gemäß einer weiteren Ausführungsform der vorliegenden Erfindung weist der Zeitgeber eine weitere Steuereinheit zum Bereitstellen des Eingangszeigers für den Demultiplexer und zum Bereitstellen des Ausgangszeigers für die Pufferregister auf. Erfindungsgemäß steuert der Zeitgeber mittels der weiteren Steuereinheit sowohl den Demultiplexer eingangsseitig des Ausgangspuffers als auch die Pufferregister zur Ausgabe der gepufferten Daten an einen Ausgang. Diese Ausführungsform erlaubt die gesamte Steuerung des Ausgangspuffers durch lediglich eine weitere Steuereinheit des Zeitgebers.

[0023] Gemäß einer weiteren Ausführungsform der vorliegenden Erfindung ist die Eingangsschaltung so gestaltet, dass diese das Ansteuersignal synchron zu einem ersten Taktsignal bereitstellt. Damit kann in vorteilhafter Weise der Zeitpunkt an dem das Ansteu-

ersignal abgegeben wird durch eine Flanke des ersten Taktsignals wohl definiert festgestellt werden.

[0024] Gemäß einer weiteren Ausführungsform der vorliegenden Erfindung weist der Zeitgeber eine Zähleinheit zum Zählen von Takten eines zweiten Taktsignals nach dem Bereitstellen des Ansteuersignals auf. Die festgelegte Zeitspanne kann somit in vorteilhafter Weise durch eine Anzahl von Takten des zweiten Taktsignals definiert werden und der Zeitgeber kann durch einfaches Zählen von Takten den Ablauf der festgelegten Zeitspanne feststellen. Vorzugsweise kann die Speichereinrichtung eine Synchronisierungseinheit zur Synchronisation des ersten und des zweiten Taktsignals in Frequenz und Phase aufweisen. Somit entfällt die zusätzliche Wartezeit zur Kompensation einer Phasenverschiebung zwischen dem ersten und dem zweiten Taktsignal. Damit kann die festgelegte Zeitspanne durch eine möglichst niedrige Anzahl von Takten und durch Zählen dieser Takte bestimmt werden. Somit kann die zeitliche Effizienz und die effektive Zugriffszeit des Speicherbausteins in vorteilhafter Weise optimiert werden.

**[0025]** Gemäß einer weiteren Ausführungsform der vorliegenden Erfindung ist der Zeitgeber so gestaltet, das dieser dem Ablauf der festgelegten Zeitspanne an einem Erreichen eines Maximalwertes der Zähleinheit erkennt. Die festgelegte Zeitspanne kann damit durch Einsetzen des Maximalwertes klar und in einfacher Weise definiert werden. Ferner kann der Zeitgeber ein Register aufweisen, in dem der Maximalwert abgespeichert wird.

**[0026]** Bevorzugte Ausführungsformen der vorliegenden Erfindung werden nachfolgend anhand der beigefügten Zeichnungen näher erläutert. Es zeigen:

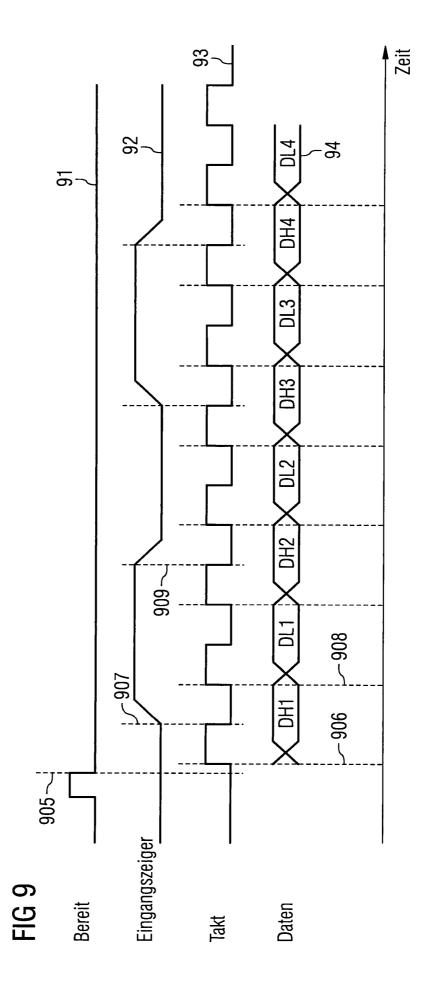

**[0027]** Fig. 1 schematisch einen integrierten Speicherbaustein gemäß einer ersten Ausführungsform der vorliegenden Erfindung;

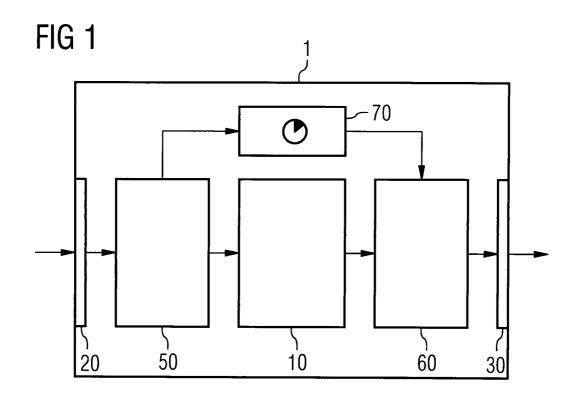

**[0028]** Fig. 2 schematisch einen integrierten Speicherbaustein gemäß einer zweiten Ausführungsform der vorliegenden Erfindung;

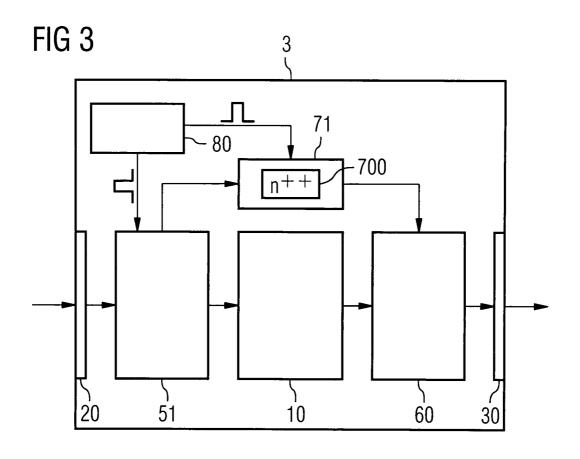

**[0029]** Fig. 3 schematisch einen integrierten Speicherbaustein gemäß einer dritten Ausführungsform der vorliegenden Erfindung;

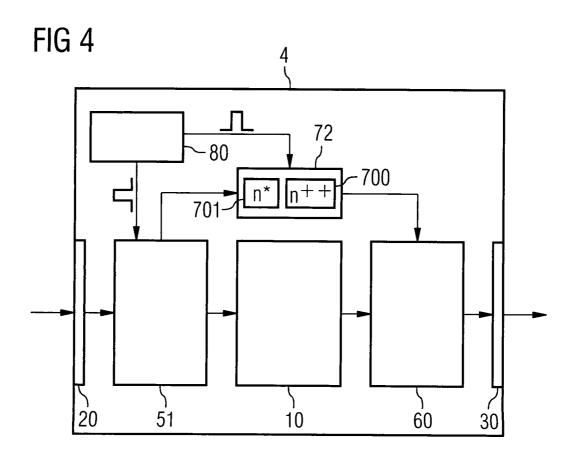

**[0030]** Fig. 4 schematisch einen integrierten Speicherbaustein gemäß einer vierten Ausführungsform der vorliegenden Erfindung;

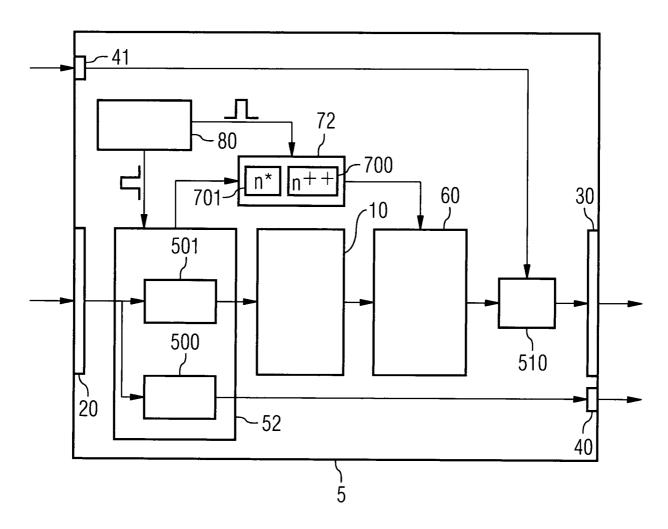

**[0031]** Fig. 5 schematisch einen integrierten Speicherbaustein gemäß einer fünften Ausführungsform der vorliegenden Erfindung;

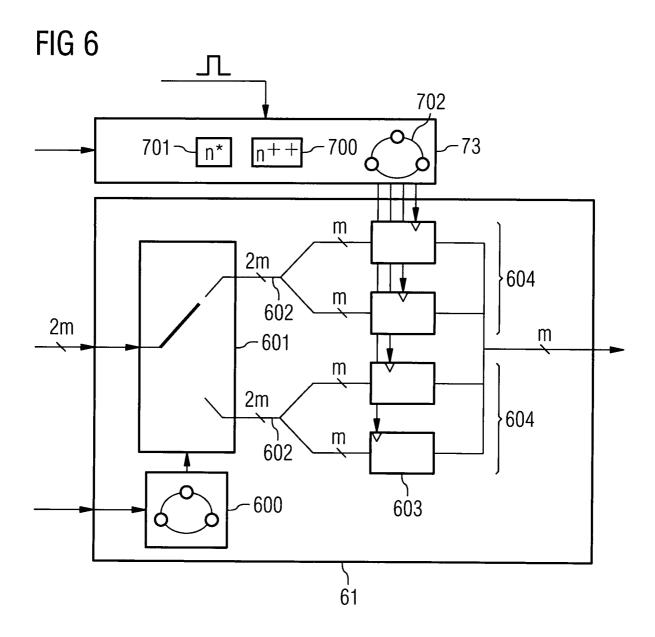

[0032] Fig. 6 schematisch einen Taktgeber und einen Ausgangspuffer gemäß einer sechsten Ausfüh-

rungsform der Erfindung;

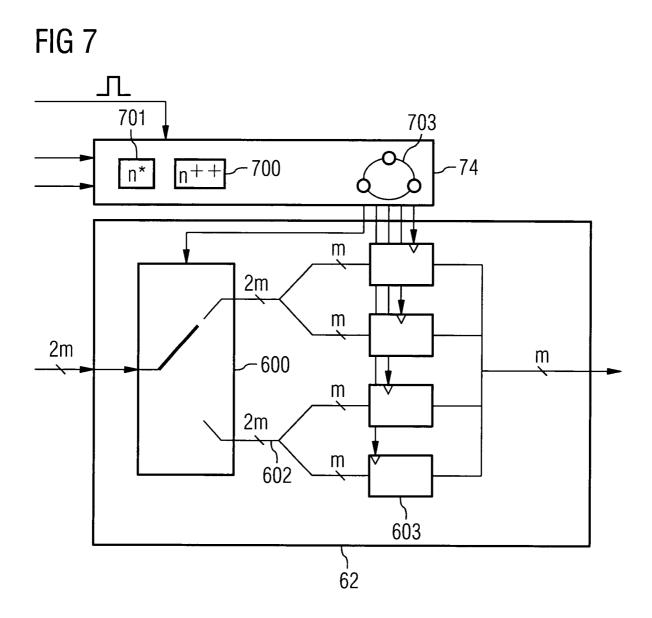

**[0033]** Fig. 7 einen Taktgeber und einen Ausgangspuffer gemäß einer siebten Ausführungsform der vorliegenden Erfindung;

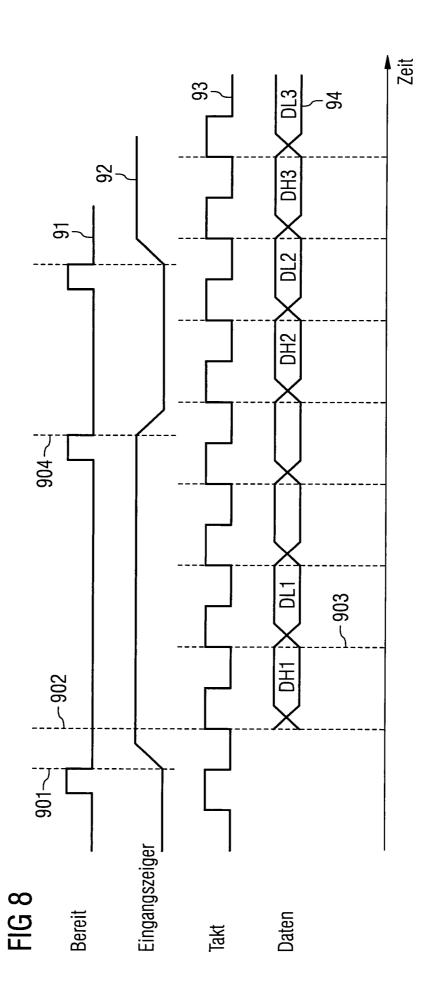

**[0034]** Fig. 8 schematisch einen zeitlichen Signalpegelverlauf gemäß einer achten Ausführungsform der vorliegenden Erfindung; und

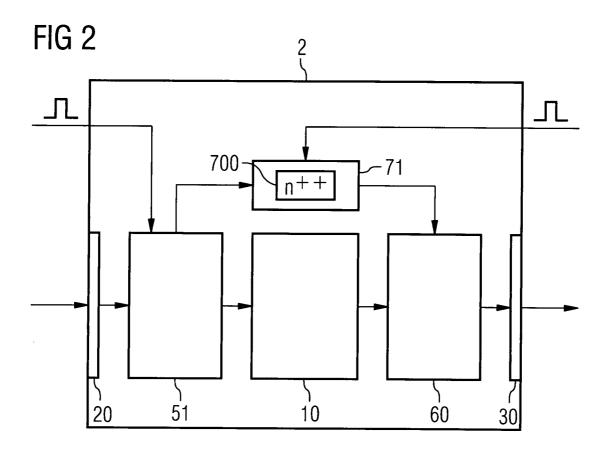

**[0035]** Fig. 9 schematisch einen seitlichen Signalpegelverlauf gemäß einer neunten Ausführungsform der vorliegenden Erfindung.

[0036] Fig. 1 zeigt schematisch einen ersten Speicherbaustein 1 mit einem Speicherzellenfeld 10. Das Speicherzellenfeld 10 speichert die Daten des Speicherbausteins in Speicherzellen ab, wobei eine einzelne Speicherzelle in der Regel zwei oder mehrere logische Zustände einnehmen kann.

[0037] Des erste Speicherbaustein 1 weist einen Eingang 20 zum Entgegennehmen von Kommandodaten auf. Diese Kommandodaten liegen in der Regel in Form von elektrischen Signalen am Eingang 20 an. Die Kommandodaten steuern den Speicherbaustein 1, und dienen so etwa zur Anforderung von aus dem Speicherzellenfeld auszulesenden Daten. Ferner weist der Speicherbaustein 1 eine erste Eingangsschaltung 50 zum Empfangen der Kommandodaten von dem Eingang 20 auf. Der Eingang 20 oder die erste Eingangsschaltung können ferner Mittel zur Signalaufbereitung wie etwa Verstärker oder passive Elemente aufweisen. Die erste Eingangsschaltung 50 stellt Ansteuersignale abhängig von den Kommandodaten für das Speicherzellenfeld 10 bereit, die das Speicherzellenfeld 10 veranlassen entsprechende Speicherzellen auszulesen. Das Speicherzellenfeld 10 schreibt diese ausgelesenen Daten dann ausgangsseitig an einen ersten Ausgangspuffer 60.

[0038] Das Speicherzellenfeld 10 weist dabei eine sogenannte Latenzzeit auf, die sich aus einer nominalen Latenzzeit und einer maximalen PVT-Varianz zusammensetzt. Die nominale Latenzzeit ist gegeben durch die endliche Zeit, die das Speicherzellenfeld 10 benötigt, um die ausgelesenen Daten ausgangsseitig nach dem Empfangen der Ansteuersignale bereitzustellen. Die PVT-Varianz (Process Voltage Temperature) ist die variable, nicht vorhersehbare Zeitdauer, die u. a. herstellungsprozessbedingt variert. Ferner führen Schwankungen der Betriebsspannung und der Betriebstemperatur zu einer unterschiedlichen Zugriffszeit des Speicherzellenfelds 10.

[0039] Erfindungsgemäß umfasst die festgelegte Zeitspanne, die ein erster Zeitgeber 70 von dem Bereitstellen der Ansteuersignale ab bis zum Ansteuern eines Ausgangspuffers 60 wartet, sowohl die nominale Latenzzeit als auch eine Obergrenze einer ma-

ximal zu erwartenden PVT-Varianz. Damit ist gewährleistet, dass die auszulesenden Daten zum Zeitpunkt deren Ausgabe aus dem Ausgangspuffer 60 an einen Ausgang 30 in jedem Fall im Ausgangspuffer 60 bereitstehen.

[0040] Der erste Zeitgeber 70 empfängt eingangsseitig von der ersten Eingangsschaltung 50 Ansteuersignale, und kann dadurch den Zeitpunkt des Absetzens der Ansteuersignale der Eingangsschaltung 50 an das Speicherzellenfeld 10 und damit den Beginn der festgelegten Zeitspanne feststellen. Nach dem Verstreichen der festgelegten Zeitspanne gibt der erste Zeitgeber 70 ein weiteres Ansteuersignal an den Ausgangspuffer 60, der daraufhin die ausgelesenen und gepufferten Daten an den Ausgang 30 ausgibt. Der Ausgangspuffer 60 liest dabei die Daten von dem Speicherzellenfeld 10 zum Zeitpunkt deren Bereitstellung ein, speichert sie, und gibt sie auf Anforderung an den Ausgang 30 weiter.

[0041] Fig. 2 zeigt einen zweiten Speicherbaustein 2, der gemäß einer zweiten Ausführungsform der vorliegenden Erfindung weitergebildet ist. Demnach weist der zweite Speicherbaustein 2 einen zweiten Zeitgeber 71 mit einer Zähleinheit 700 auf. Ferner weist der zweite Speicherbaustein 2 eine zweite Eingangsschaltung 51 auf, die eingangsseitig sowohl die Kommandodaten von dem Eingang 20 entgegennimmt als auch ein erstes Taktsignal. Ausgangsseitig stellt die zweite Eingangsschaltung 51 aus den Kommandodaten wieder Ansteuersignale für das Speicherzellenfeld 10 bereit. Ferner werden diese Ansteuersignale für das Speicherzellenfeld 10 und den zweiten Zeitgeber 71 synchron zu dem ersten Taktsignal abgeben. Der zweite Zeitgeber 71 zählt nach dem Absetzen des Ansteuersignals die Takte eines zweiten Taktsignals, um so die festgelegte Zeitspanne in Einheiten zu Takten des zweiten Taktsignals ab-

[0042] Fig. 3 zeigt einen dritten Speicherbaustein 3 mit einem Taktgeber 80. Der Taktgeber 80 gibt sowohl der zweiten Eingangsschaltung 51 das erste Taktsignal als auch dem zweiten Zeitgeber 71 das zweite Taktsignal. Vorzugsweise synchronisiert der Taktgeber 80 die zwei Taktsignale derart, dass sie sowohl frequenz- als auch phasensynchron an der zweiten Eingangsschaltung 51 und an dem zweiten Zeitgeber 71 bereitgestellt werden. Der Taktgeber 80 kann ferner ein oder mehrere Taktsignale von außerhalb des Speicherbausteins extern erhalten. Die Funktion des Taktgebers 80 kann sich in diesem Falle dann auf eine Signalaufbereitung und eine eventuelle Synchronisation der empfangenen Taktsignale beschränken.

**[0043]** Die frequenz- und phasensynchrone Bereitstellung der Taktsignale kann dabei durch einen phasengeregelten Regelkreis (PLL Phase Locked Loop)

und/oder laufzeitkompensierte Taktsignalleitungen realisiert werden. Liegen die Taktsignale an der zweiten Eingangsschaltung **51** und an dem zweiten Zeitgeber **71** frequenz- und phasensynchron an, so kann die zweite Eingangsschaltung **51** das Ansteuersignal synchron zu dem Taktsignal an den zweiten Zeitgeber **71** weiterleiten, der dann ohne Phasenverzug die festgelegte Zeitspanne in Takten des ihm zur Verfügung gestellten Taktsignals mittels der Zähleinheit **700** bestimmen kann.

[0044] Fig. 4 zeigt einen vierten Speicherbaustein 4 gemäß einer vierten Ausführungsform der vorliegenden Erfindung. Wie eben dort gezeigt, weist ein dritter Zeitgeber 72 neben der Zähleinheit 700 auch ein Register 701 auf, das einen Maximalwert n\* abspeichern kann. Durch die Frequenz- und Phasensynchronisation der Taktsignale, die von dem Taktgeber 80 bereitgestellt werden, muss die festgelegte Zeitdauer lediglich die nominale Latenzzeit und eine maximale PVT-Varianz des Speicherzellenfelds 10 umfassen. Ein weiteres Berücksichtigen einer Phasenverschiebung zwischen den Taktsignalen, die jeweils der zweiten Eingangsschaltung 51 und dem dritten Zeitgeber 72 zur Verfügung gestellt werden, entfällt durch die frequenz- und phasensynchrone Generation der Taktsignale. In dem Register 701 kann daher ein entsprechender minimierter Maximalwert n\* abgelegt werden. Der erfindungsgemäße Speicherbaustein 4 kann daher zuverlässig und in optimierbarer Art und Weise betrieben werden.

[0045] Fig. 5 zeigt einen fünften Speicherbaustein gemäß einer fünften Ausführungsform der vorliegenden Erfindung. Demnach weist eine dritte Eingangsschaltung 52 eine Durchleitungseinheit 500 und eine Protokolleinheit 501 auf. Die dritte Eingangsschaltung 52 dekodiert vermöge der Protokolleinheit 501 die von dem Eingang 20 empfangenen Kommandodaten zur Bereitstellung der Ansteuersignale für das Speicherzellenfeld 10. Das erfindungsgemäße Vorsehen einer Protokolleinheit 501 erlaubt die Einbettung der Kommandodaten in ein Protokoll. Damit sind hinsichtlich dem Umfang und der Komplexizität der verwendbaren Befehle kaum Grenzen gesetzt, und die dritte Eingangsschaltung 52 erlaubt neben dem regulären Ansprechen des Speicherzellenfeld 10 auch die Dekodierung weiterführender Kommandos, so wie etwa ein direktes Ansprechen des Taktgebers 80 oder des Zeitgebers 72.

[0046] Die dritte Eingangsschaltung 52 weist ferner eine Durchleitungseinheit 500 zur Weitergabe der Kommandodaten an einen weiteren Ausgang 40 auf. Damit können die dem Eingang 20 des fünften Speicherbausteins 5 zur Verfügung gestellten Kommandodaten auch an weitere Speicherbausteine und/oder Komponenten weitergeleitet werden. Des Weiteren weist der fünfte Speicherbaustein 5 eine weitere Durchleitungseinheit 510 zur Weitergabe von

Nutzdaten von einem weiteren Eingang 41 an den Ausgang 30 auf. Der fünfte Speicherbaustein 5 erlaubt somit das Weiterreichen von externen Daten. die beispielsweise von einem weiteren Speicherbaustein stammen, und damit auch eine Hintereinanderschaltung mehrerer Speicherbausteine. Ferner kann die weitere Durchleitungseinheit 510 die aus dem Speicherzellenfeld 10 ausgelesenen Daten bitgenau, d. h. ohne Gefahr einer Datenkollision und unter optimaler zeiteffizienter Ausnutzung der Signalwege, in einen Datenstrom, der sich innerhalb des Speicherbausteins von dem weiteren Eingang 41 über die weitere Durchleitungseinheit 510 bis zum Ausgang 30 erstreckt, einfügen. Das Vorsehen einer Durchleitungseinheit 500, eines weiteren Eingangs 41, eines weiteren Ausgangs 30 und einer weiteren Durchleitungseinheit 510 kann auch in Kombination mit anderen Ausführungsformen der vorliegenden Erfindung erfolgen.

[0047] Fig. 6 zeigt einen zweiten Ausgangspuffer 61 und einen vierten Zeitgeber 73 gemäß einer sechsten Ausführungsform der vorliegenden Erfindung. Demnach weist der zweite Ausgangspuffer 61 einen Demultiplexer 601 zur Verteilung von ausgelesenen Daten aus dem Speicherzellenfeld 10 an mehrere Ausgänge 602 des Demultiplexers auf. Der Demultiplexer 601 kann somit die von dem Speicherzellenfeld 10 ausgelesenen Daten auf mehrere Pufferregister 603 verteilen. Dabei kann auch - wie hier gezeigt - ein Aufteilen der ausgelesenen Daten mit einer initialen Datenbreite 2m auf mehrere Pufferregister 603 mit der Datenbreite m aufgeteilt werden. Der jeweilige Ausgang 602 des Demultiplexers 601 wird durch einen Eingangszeiger bestimmt, der dem Demultiplexer 601 von einer Steuereinheit 600 bereitgestellt wird. Die Steuereinheit 600 kann hierfür beispielsweise ein Bereit-Signal des Speicherzellenfelds 10, das das Bereitstehen der ausgelesenen Daten signalisiert, aufnehmen und dann dementsprechend den Eingangszeiger für den Demultiplexer 601 verändern.

[0048] Erfindungsgemäß sind wenigstens zwei Registergruppen 604, bestehend aus je zwei Pufferregistern 603 vorgesehen, um dem zweiten Ausgangspuffer zu ermöglichen, gepufferte Daten zurückzuhalten, obwohl bereits neue Daten aus dem Speicherzellenfeld anliegen. Für diesen – nur als beispielhaft anzusehenden – Fall, ist eine Registergruppe 604 in der Lage die aus dem Speicherzellenfeld 10 ausgelesenen Daten in voller Breite, hier 2m, abzuspeichern, wobei eine Registergruppe 604 dann intern diese Daten auf zwei Pufferregister 603 mit jeweils der Datenbreite m verteilt.

[0049] Gemäß dieser Ausführungsform der vorliegenden Erfindung weist der vierte Zeitgeber 73 ferner eine weitere Steuereinheit 702 auf, die die Pufferregister 603 entsprechend der festgelegten Zeitspanne

## DE 10 2006 017 768 A1 2007.10.18

ansteuert. Der Zeitpunkt dieser Ansteuerung wird mit Hilfe des Zählerstandes der Zähleinheit **700** im Vergleich mit dem Maximalwert n\*, der in dem Register **701** abgespeichert ist, ermittelt. So werden ab dem Bereitstellen der Ansteuersignale für das Speicherzellenfeld **10** die Pufferregister **603** so angesteuert, dass die gepufferten Daten in Form eines ersten und eines zweiten Wortes – hier jeweils mit einer Datenbreite m – an den Ausgang **30** abgegeben werden. Innerhalb der festgelegten Zeitspanne wird der vierte Zeitgeber also zwei der Pufferregister **603** zur Ausgabe der in ihnen gespeicherten gepufferten Daten veranlassen.

[0050] Fig. 7 zeigt einen dritten Ausgangspuffer 62 und einen fünften Zeitgeber 74 gemäß einer siebten Ausführungsform der vorliegenden Erfindung. Demgemäß weist der fünfte Zeitgeber 74 eine zweite weitere Steuereinheit 703 auf, die sowohl den Demultiplexer 600 als auch die Pufferregister 603 eines dritten Ausgangspuffers 62 steuert. Hierfür empfängt der fünfte Zeitgeber 74 sowohl mindestens ein Ansteuersignal für das Speicherzellenfeld als auch ein Bereit-Signal, das das Bereitstehen der ausgelesenen Daten aus dem Speicherzellenfeld 10 signalisiert.

[0051] Fig. 8 zeigt schematisch den zeitlichen Signalpegelverlauf gemäß einer achten Ausführungsform der vorliegenden Erfindung, insbesondere wie er in einem Speicherbaustein gemäß der sechsten Ausführungsform der vorliegenden Erfindung Anwendung finden kann. Ein Bereit-Signal 91 signalisiert zunächst das Bereitstehen der angeforderten Daten aus einem Speicherzellenfeld. Eine fallende Flanke des Bereit-Signals 91 verursacht zu einem Zeitpunkt 901 das Umschalten eines Eingangszeigers 92. Wie hier gezeigt, kann das Eingangszeigersignal 92 zwei Zustände einnehmen – jeweils einen für ein Pufferregister. Der Eingangszeiger wird also nur in Abhängigkeit des Bereit-Signals 91 des Speicherzellenfeldes verändert.

[0052] Die erste steigende Flanke eines Taktsignals 93 nach dem Bereitstehen der Daten verursacht zu einem Zeitpunkt 902 das Ausgeben eines ersten hochwertigen Datenwortes DH1. Da die Daten ab dem Zeitpunkt 901 in doppelter Wortbreite in die Pufferregister geschrieben wurden, erfolgt - beispielsweise – bei der darauf folgenden steigenden Flanke des Taktsignals 93 zu dem Zeitpunkt 903 das Ausgeben des niederwertigen Datenwortes DL1. Das Bereitstehen der nächsten Daten aus dem Speicherzellenfeld wird durch eine nächste fallende Flanke des Bereit-Signals 91 zu einem Zeitpunkt 904 signalisiert. Der Eingangszeiger 92 springt daraufhin um, und eine analoge Datenausgangssequenz des Datensignals 94 folgt für die Wörter DH2 und DL2. Das Ausgeben der Daten ist dabei wieder synchron zu einer steigenden Flanke des Taktsignals 93.

[0053] Fig. 9 zeigt schematisch den zeitlichen Signalpegelverlauf gemäß einer neunten Ausführung der vorliegenden Erfindung, insbesondere wie er in einem Speicherbausteins, gemäß der siebten Ausführungsform der vorliegenden Erfindung Anwendung finden kann. Demnach signalisiert ein Bereit-Signal 91 nur einmal das Bereitstehen ausgelesener Daten aus den Speicherzellenfeld. Dies kann, wie hier gezeigt, zu einem Zeitpunkt 905 erfolgen. Gemäß dieser Ausführungsform wird der Eingangszeiger 92 ab diesem Zeitpunkt 905 periodisch - beispielsweise jeweils jede zweite fallende Flanke des Taktsignals 93 - umgeschaltet, so auch zu den Zeitpunkten 907 und 909. Es genügt hier das einmalige Absetzen des Bereit-Signals 91 zum Zeitpunkt 905, da der Eingangszeiger dann fortlaufend verändert wird. Analog zur vorhergehenden Ausführungsform werden die Daten, beginnend bei einem Zeitpunkt 906, wieder in Form zweier Pakete DHx und DLx als Datensignal 94 ausgegeben. Somit erfolgt zum Zeitpunkt 906, also zum Zeitpunkt der ersten steigenden Flanke des Taktsignals 93 nach dem Bereitsignal 91 zum Zeitpunkt 905, die Ausgabe des hochwertigen Datenwortes DH1. Ein Taktzyklus später, zum Zeitpunkt 908, erfolgt dann die Ausgabe des niederwertigen Datenwortes DL1. In vorteilhafter Weise kann die Steuerung des Speicherbausteins besonders einfach ausgeführt werden, da ein einmaliges Absetzen eines Bereit-Signals eine periodische Veränderung des Eingangszeigers initiiert, und die ausgelesenen Daten automatisiert auf einer Zeitbasis mit einer festgelegten Zeitspanne ausgegeben werden können.

#### Bezugszeichenliste

- 1 Erster Speicherbaustein

- 2 Zweiter Speicherbaustein

- 3 Dritter Speicherbaustein

- 4 Vierter Speicherbaustein

- 5 Fünfter Speicherbaustein

- 10 Speicherzellenfeld

- 20 Eingang

- 30 Ausgang

- 40 Weiterer Ausgang

- 41 Weiterer Eingang

- **50** Erste Eingangsschaltung

- **51** Zweite Eingangsschaltung

- **52** Dritte Eingangsschaltung

- 60 Erster Ausgangspuffer

- **61** Zweiter Ausgangspuffer

- **62** Dritter Ausgangspuffer

- 70 Erster Zeitgeber

- 71 Zweiter Zeitgeber

- 72 Dritter Zeitgeber

- 73 Vierter Zeitgeber

- 74 Fünfter Zeitgeber

- 80 Taktgeber

- 91 Bereit-Signal

- 92 Eingangszeiger

- 93 Taktsignal

## DE 10 2006 017 768 A1 2007.10.18

- **94** Datensignal

- 500 Durchleitungseinheit

- 510 Weitere Durchleitungseinheit

- **501** Protokolleinheit

- 600 Steuereinheit

- 601 Demultiplexer

- 602 Ausgang des Demultiplexers

- 603 Pufferregister

- 604 Registergruppe

- 700 Zähleinheit

- 701 Register

- 702 Erste weitere Steuereinheit

- 703 Zweite weitere Steuereinheit

- 901 Erster Zeitpunkt

- **902** Zweiter Zeitpunkt

- 903 Dritter Zeitpunkt

- 904 Vierter Zeitpunkt

- 905 Fünfter Zeitpunkt

- 906 Sechster Zeitpunkt

- 907 Siebter Zeitpunkt

- 908 Achter Zeitpunkt

- 909 Neunter Zeitpunkt

#### Patentansprüche

- 1. Integrierter Speicherbaustein umfassend:

- Ein Speicherzellenfeld zum Auslesen von Daten,

- eine Eingangsschaltung zum Empfangen von Kommandodaten und zum Bereitstellen von Ansteuersignalen für das Speicherzellenfeld,

- einen Ausgangspuffer zum Puffern von aus dem Speicherzellenfeld ausgelesenen Daten, und

- einen Zeitgeber, der gestaltet ist, den Ausgangspuffer so anzusteuern, dass eine festgelegte Zeitspanne nach dem Bereitstellen der Ansteuersignale die gepufferten Daten an einem Ausgang bereitgestellt werden.

- 2. Speicherbaustein nach Anspruch 1, wobei die Eingangsschaltung eine Parallelisierungseinheit zur Parallelisierung serieller Kommandodaten aufweist.

- 3. Speicherbaustein nach Anspruch 1 oder 2, wobei die Eingangsschaltung eine Protokolleinheit zur Dekodierung der Kommandodaten aufweist, um die Ansteuersignale bereitzustellen.

- 4. Speicherbaustein nach einem der Ansprüche 1 bis 3, wobei die Eingangsschaltung eine Durchleitungseinheit zur Weitergabe der Kommandodaten an einen weiteren Ausgang aufweist.

- 5. Speicherbaustein nach einem der Ansprüche 1 bis 4, wobei der Speicherbaustein einen weiteren Eingang zum Empfangen von Nutzdaten und eine weitere Durchleitungseinheit zur Weitergabe der von dem weiteren Eingang empfangenen Nutzdaten an den Ausgang aufweist.

- 6. Speicherbaustein nach einem der Ansprüche 1

bis 5, wobei der Ausgangspuffer einen FIFO-Puffer aufweist.

- 7. Speicherbaustein nach einem der Ansprüche 1 bis 6, wobei der Ausgangspuffer einen Demultiplexer und wenigstens zwei Pufferregister aufweist, wobei der Demultiplexer die ausgelesenen Daten abhängig von einem Eingangszeiger an eines der wenigstens zwei Pufferregister weiterleitet.

- 8. Speicherbaustein nach Anspruch 7, wobei der Ausgangspuffer eine Steuereinheit zum Bereitstellen des Eingangszeigers aufweist, und die Steuereinheit gestaltet ist, den Eingangszeiger abhängig von einem Bereit-Signal, das von dem Speicherzellenfeld bereitgestellt wird, zu verändern.

- 9. Speicherbaustein nach Anspruch 7 oder 8, wobei der Zeitgeber eine weitere Steuereinheit zum Bereitstellen eines Ausgangszeigers für die Pufferregister aufweist, wobei die Pufferregister abhängig von dem Ausgangszeiger die gepufferten Daten an den Ausgang weiterleiten.

- 10. Speicherbaustein nach Anspruch 7, wobei der Zeitgeber eine weitere Steuereinheit zum Bereitstellen des Eingangszeigers für den Demultiplexer und zum Bereitstellen eines Ausgangszeigers für die Pufferregister aufweist, wobei die Pufferregister abhängig von dem Ausgangszeiger die gepufferten Daten an den Ausgang weiterleiten.

- 11. Speicherbaustein nach einem der Ansprüche 1 bis 10, wobei die Eingangsschaltung so gestaltet ist, dass diese das Ansteuersignal synchron zu einem ersten Taktsignal bereitstellt.

- 12. Speicherbaustein nach Anspruch 11, wobei der Zeitgeber eine Zähleinheit zum Zählen von Takten eines zweiten Taktsignals nach dem Bereitstellen des Ansteuersignals aufweist.

- 13. Speicherbaustein nach Anspruch 12, wobei der Zeitgeber so gestaltet ist, dass dieser den Ablauf der festgelegten Zeitspanne an einem Erreichen eines Maximalwertes der Zähleinheit erkennt.

- 14. Speicherbaustein nach Anspruch 13, wobei der Zeitgeber ein Register aufweist, in dem der Maximalwert abgespeichert ist.

- 15. Speicherbaustein nach einem der Ansprüche 12 bis 14, wobei die Speichereinrichtung eine Synchronisierungseinheit zur Synchronisation in Frequenz und Phase des ersten und des zweiten Taktsignals aufweist.

- 16. Verfahren zum Betrieb eines integrierten Speicherbausteins, insbesondere eines Speicherbausteins gemäß einem der Ansprüche 1 bis 15, um-

fassend die Schritte:

- Bereitstellen von Kommandodaten,

- Bereitstellen von Ansteuersignalen, die von den Kommandodaten abhängen, für ein Speicherzellenfeld.

- Puffern von aus dem Speicherzellenfeld ausgelesenen Daten,

- Ausgeben der gepufferten Daten an einen Ausgang nach Ablauf einer festgelegten Zeitspanne nach dem Bereitstellen der Ansteuersignale.

- 17. Verfahren nach Anspruch 16, zusätzlich umfassend ein Parallelisieren serieller Kommandodaten.

- 18. Verfahren nach Anspruch 16 oder 17, wobei die Kommandodaten zum Bereitstellen der Ansteuersignale dekodiert werden.

- 19. Verfahren nach einem der Ansprüche 16 bis 18, zusätzlich umfassend eine Weitergabe der Kommandodaten an einen weiteren Ausgang.

- 20. Verfahren nach einem der Ansprüche 16 bis 19, zusätzlich umfassend eine Weitergabe von Nutzdaten von einem weiteren Eingang an den Ausgang.

- 21. Verfahren nach einem der Ansprüche 16 bis 20, wobei mit der Verfügbarkeit der ausgelesenen Daten aus dem Speicherzellenfeld ein Eingangszeiger verändert wird, und ein Pufferregister zum Puffern der ausgelesenen Daten abhängig von dem Eingangszeiger bestimmt wird.

- 22. Verfahren nach einem der Ansprüche 16 bis 21, wobei die gepufferten Daten abhängig von einem Ausgangszeiger ausgegeben werden, und der Ausgangszeiger nach dem Ablauf der festgelegten Zeitspanne verändert wird.

- 23. Verfahren nach einem der Ansprüche 16 bis 22, wobei das Bereitstellen der Ansteuersignale synchron mit einem ersten Taktsignal erfolgt.

- 24. Verfahren nach Anspruch 23, wobei die festgelegte Zeitspanne durch ein Zählen von Takten eines zweiten Taktsignals nach dem Bereitstellen der Ansteuersignale erfolgt.

- 25. Verfahren nach Anspruch 24, zusätzlich umfassend ein Synchronisieren der Frequenz und der Phase des ersten und des zweiten Taktsignals.

Es folgen 7 Blatt Zeichnungen

## Anhängende Zeichnungen

FIG 5