# (19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(51) Int. Cl.

**H01L 21/027** (2006.01)

(21) 출원번호

10-2006-0069352

(22) 출원일자

2006년07월24일

심사청구일자 없음

(11) 공개번호 10-2008-0009581

(43) 공개일자 2008년01월29일

(71) 출원인

삼성전자주식회사

경기도 수원시 영통구 매탄동 416

(72) 발명자

김명선

대구 달서구 파호동 삼성명가타운 213동 1801호

김영호

경기도 용인시 풍덕천2동 삼성5차아파트 511동

603호

(뒷면에 계속)

(74) 대리인

권혁수, 송윤호, 오세준

전체 청구항 수 : 총 8 항

#### (54) 반도체 장치의 형성 방법

#### (57) 요 약

반도체 장치의 형성 방법이 제공된다. 기판 상에 코팅막이 형성된다. 상기 코팅막 상에 포토레지스트막이 형성된다. 상기 코팅막 및 상기 포토레지스트막을 패터닝하여 상기 기판을 노출하는 코팅막 패턴 및 포토레지스트 패턴이 형성된다. 상기 노출된 기판이 식각된다. 상기 포토레지스트막은 실리콘을 포함한다.

#### **대표도** - 도2a

#### (72) 발명자

### 이창호

경기 수원시 영통구 망포동 동수원엘지빌리지 109 동 1104호

#### 강경림

경기 성남시 분당구 수내동 10-1 분당트라팰리스 1166호

#### 이정훈

경기 화성시 병점동 한일타운아파트 105동 307호

#### 김영훈

경기 수원시 영통구 영통동 1032-16, 201호

#### 박경실

경기도 성남시 분당구 정자동 한솔마을 415동 180 2호

#### 양주형

경기 수원시 장안구 율전동 359번지 302호

#### 특허청구의 범위

#### 청구항 1

기판 상에 코팅막을 형성하는 단계;

상기 코팅막 상에 제1 포토레지스트막 및 제2 포토레지스트막을 형성하는 단계;

상기 코팅막, 상기 제1 포토레지스트막, 및 상기 제2 포토레지스트막을 패터닝하여 상기 기판을 노출하는 코팅막 패턴, 제1 포토레지스트 패턴 및 제2 포토레지스트 패턴을 형성하는 단계; 및

상기 노출된 기판을 식각하는 단계를 포함하며,

상기 제2 포토레지스트막은 실리콘을 포함하는 반도체 장치의 형성 방법.

#### 청구항 2

제 1 항에 있어서,

상기 코팅막을 형성하는 단계는 스핀 온 하드마스크층을 형성하는 것을 포함하는 반도체 장치의 형성 방법.

#### 청구항 3

제 2 항에 있어서,

상기 스핀 온 하드마스크층은 탄소를 포함하는 반도체 장치의 형성 방법.

#### 청구항 4

제 1 항에 있어서,

상기 제1 및 제2 포토레지스트 패턴을 형성하는 단계는,

상기 제1 및 제2 포토레지스트막에 노광 및 현상 공정을 수행하는 것을 포함하며,

상기 제1 및 제2 포토레지스트 패턴은 동시에 형성되는 반도체 장치의 형성 방법.

#### 청구항 5

제 4 항에 있어서,

상기 노광 공정은 ArF 광원을 이용하는 반도체 장치의 형성 방법.

#### 청구항 6

제 1 항에 있어서,

상기 코팅막 패턴을 형성하는 단계는,

상기 제1 및 제2 포토레지스트 패턴을 식각 마스크로 사용하여 상기 코팅막을 식각하는 것을 포함하는 반도체 장치의 형성 방법.

#### 청구항 7

기판 상에 탄소를 포함하는 스핀 온 하드마스크층을 형성하는 단계;

상기 스핀 온 하드마스크층 상에 실리콘을 포함하는 포토레지스트막을 형성하는 단계;

상기 포토레지스트막에 노광 및 현상 공정을 수행하여 포토레지스트 패턴을 형성하는 단계;

상기 포토레지스트 패턴을 식각 마스크로 사용하여 스핀 온 마스크층을 식각하여 상기 기판을 노출시키는 스핀 온 마스크 패턴을 형성하는 단계; 및

상기 노출된 기판을 식각하는 단계를 포함하는 반도체 장치의 형성 방법.

#### 청구항 8

제 7 항에 있어서,

상기 노광 공정은 ArF 광원을 이용하는 반도체 장치의 형성 방법.

#### 명 세 서

#### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

- <8> 본 발명은 반도체 장치에 관한 것으로, 더욱 상세하게는 식각 공정을 포함하는 반도체 장치의 형성 방법에 관한 것이다.

- (9) 반도체 장치가 고집적화됨에 따라 사진 및 식각 공정에서 미세한 패터닝이 요구된다. 최근 미세한 패터닝을 위해 사진 및 식각 공정에서 높은 해상도를 갖는 노광원인 단파장(λ=193nm)의 ArF 엑시머 레이저가 이용된다. 이러한 단파장의 레이저를 광원으로 사용할 때 포토레지스트막의 두께는 얇아져야 한다. 따라서, 형성된 포토레지스트 패턴을 이용하는 후속의 건식 식각 공정에서, 상기 포토레지스트 패턴의 두께가 얇기 때문에 하드마스 크층이 필요하다. 종래기술에 따르면 하드마스크층으로서 비정질 탄소막(amorphous carbon layer)이 사용된다.

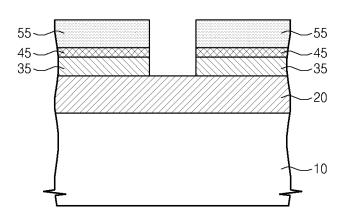

- <10> 도 1a 내지 도 1e는 종래 기술에 따른 반도체 장치의 형성 방법을 설명하기 위한 단면도들이다.

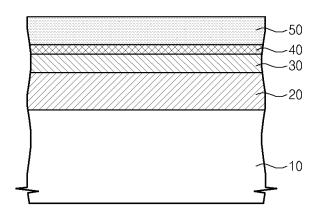

- <11> 도 1a를 참조하면, 기판(10) 상에 비정질 탄소막(20), 무기 반사방지막(30), 유기 반사방지막(40), 및 포토레지스트막(50)이 형성된다. 비정질 탄소막(20)과 무기 반사방지막(30)(예컨대, 실리콘산화질화막)은 화학기상증착 공정을 수행하여 형성되고, 유기 반사방지막(40)과 포토레지스트막(50)은 스핀 코팅 공정을 수행하여 형성된다.

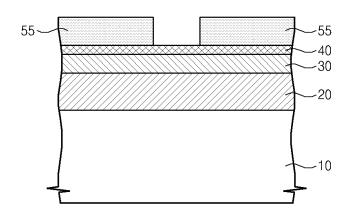

- <12> 도 1b를 참조하면, 노광 및 현상 공정을 수행하여 포토레지스트 패턴(55)이 형성된다.

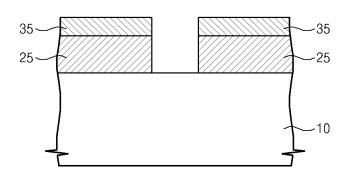

- <13> 도 1c를 참조하면, 포토레지스트 패턴(55)을 식각 마스크로 사용하는 식각 공정을 수행하여 유기 반사방지막 패턴(45)과 무기 반사방지막 패턴(35)이 형성되고, 비정질 탄소막(20)이 노출된다.

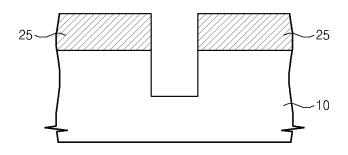

- <14> 도 1d를 참조하면, 식각 공정을 수행하여 비정질 탄소막 패턴(25)이 형성되고, 기판(10)이 노출된다. 상기 식각 공정 동안 포토레지스트 패턴(55)과 유기 반사방지막 패턴(45)은 식각되어 제거될 수 있다.

- <15> 도 1e를 참조하면, 비정질 탄소막 패턴(25)을 식각 마스크로 사용하여 기판(10)이 식각된다. 기판(10)이 식각 될 때, 무기 반사방지막 패턴(35)도 식각되어 제거될 수 있다.

- <16> 상술한 바와 같이 식각 마스크로 사용되는 비정질 탄소막 패턴을 형성하기 위해 두 번의 화학기상증착 공정, 두 번의 스핀 코팅 공정, 및 두 번의 식각 공정을 수행하여야 하는 등 공정이 복잡해진다. 또, 비정질 탄소막이 식각될 때 다량의 파티클이 발생할 수 있다.

#### 발명이 이루고자 하는 기술적 과제

- <17> 본 발명은 이상에서 언급한 상황을 고려하여 제안된 것으로, 본 발명이 이루고자 하는 기술적 과제는 공정이 단순화된 반도체 장치의 형성 방법을 제공하는 것이다.

- <18> 본 발명이 이루고자 하는 다른 기술적 과제는 파티클 발생을 억제할 수 있는 식각 마스크 패턴을 형성하는 것을 포함하는 반도체 장치의 형성 방법을 제공하는 것이다.

#### 발명의 구성 및 작용

- 본 발명의 실시예에 따른 반도체 장치의 형성 방법이 제공된다. 기판 상에 코팅막이 형성된다. 상기 코팅막 상에 제1 포토레지스트막 및 제2 포토레지스트막이 형성된다. 상기 코팅막, 상기 제1 포토레지스트막, 및 상기 제2 포토레지스트막을 패터닝하여 상기 기판을 노출하는 코팅막 패턴, 제1 포토레지스트 패턴 및 제2 포토레지 스트 패턴이 형성된다. 상기 노출된 기판이 식각된다. 상기 제2 포토레지스트막은 실리콘을 포함한다.

- <20> 상기 형성 방법에서, 상기 코팅막은 스핀 온 하드마스크층으로 형성될 수 있다. 상기 스핀 온 하드마스크층은 탄소를 포함할 수 있다.

- <21> 상기 형성 방법에서, 상기 제1 및 제2 포토레지스트 패턴은 상기 제1 및 제2 포토레지스트막에 노광 및 현상 공 정을 수행하여 동시에 형성될 수 있다. 상기 노광 공정은 ArF 광원을 이용할 수 있다.

- <22> 상기 형성 방법에서, 상기 코팅막 패턴은 상기 제1 및 제2 포토레지스트 패턴을 식각 마스크로 사용하여 상기 코팅막을 식각함으로써 형성될 수 있다.

- <23> 본 발명의 실시예에 따른 반도체 장치의 형성 방법이 제공된다. 기판 상에 탄소를 포함하는 스핀 온 하드마스 크층이 형성된다. 상기 스핀 온 하드마스크층 상에 실리콘을 포함하는 포토레지스트막이 형성된다. 상기 포토레지스트막에 노광 및 현상 공정을 수행하여 포토레지스트 패턴이 형성된다. 상기 포토레지스트 패턴을 식각마스크로 사용하여 스핀 온 마스크층을 식각하여 상기 기판을 노출시키는 스핀 온 마스크 패턴이 형성된다. 상기 노출된 기판이 식각된다.

- <24> 상기 형성 방법에서, 상기 노광 공정은 ArF 광원을 이용할 수 있다.

- <25>

- <26> 이하 첨부한 도면들을 참조하여 본 발명의 실시예들을 상세히 설명하기로 한다. 그러나 본 발명은 여기서 설명되는 실시예들에 한정되지 않고 다른 형태로 구체화될 수도 있다. 오히려, 여기서 소개되는 실시예들은 개시된 내용이 철저하고 완전해질 수 있도록 그리고 당업자에게 본 발명의 사상이 충분히 전달될 수 있도록 하기 위해 제공되는 것이다.

- <27> 본 명세서에서 제1, 제2 등의 용어가 포토레지스트막 등을 기술하기 위해서 사용되었지만, 포토레지스트막 등이 이 같은 용어들에 의해서 한정되어서는 안 된다. 이러한 용어들은 단지 어느 소정의 포토레지스트막 등을 다른 다른 포토레지스트막 등과 구별시키기 위해서 사용되었을 뿐이다. 또, 어떤 막이 다른 막 또는 기판 상에 있다고 언급되는 경우에 그것은 다른 막 또는 기판 상에 직접 형성될 수 있거나 또는 그들 사이에 제3의 막이 개재될 수도 있다는 것을 의미한다. 도면들에서, 막 또는 영역들의 두께 등은 명확성을 기하기 위하여 과장되게 표현될 수 있다.

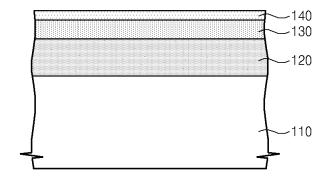

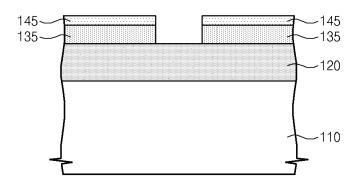

- <28> 도 2a 내지 도 2d는 본 발명의 실시예에 따른 반도체 장치의 형성 방법을 설명하기 위한 단면도들이다.

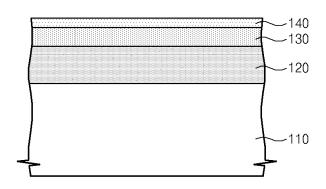

- <29> 도 2a를 참조하면, 기판(110) 상에 코팅막(120), 제1 포토레지스트막(130), 및 제2 포토레지스트막(140)이 형성된다. 기판(110)은 반도체 기판일 수 있으며, 식각의 대상이 되는 피식각층(예컨대, 절연막, 실리콘막, 금속막등)을 포함할 수 있다. 코팅막(120), 제1 포토레지스트막(130), 및 제2 포토레지스트막(140)은 스핀 코팅(spin coating) 방법으로 형성될 수 있다.

- <30> 코팅막(120)은 탄소를 사용하여 스핀 온 하드마스크층(C-SOH:carbon-spin on hardmask)으로 형성될 수 있다. 코팅막(120)은 예컨대, 2000~2500Å의 두께로 형성될 수 있다. 코팅막(120)은 후술하는 바와 같이 패터닝된 후 식각 마스크로 사용되지만, 그 자체가 반사방지 기능도 하기 때문에, 그 상부에 별도의 반사방지막이 형성되지 않을 수 있다.

- <31> 제1 및 제2 포토레지스트막(130,140)은 감광성 유기물로 형성될 수 있다. 다만, 제2 포토레지스트막(140)은 실 리콘을 포함하는 감광성 유기물로 형성된다. 코팅막(120)은 하드마스크층으로 사용되는 다른 막질에 비해 용이 하게 식각될 수 있기 때문에, 코팅막(120)을 식각하기 위해 형성되는 제1 및 제2 포토레지스트막(130,140)은 두 껍게 형성되지 않을 수 있다. 즉, 제1 및 제2 포토레지스트막(130,140)은 한 번의 사진 공정(즉, 노광 및 현상 공정)에 의해 패터닝될 수 있는 두께로 형성될 수 있다. 예컨대, 제1 포토레지스트막(130)은 1300~1800Å, 제2 포토레지스트막(140)은 300~800Å의 두께로 형성될 수 있다.

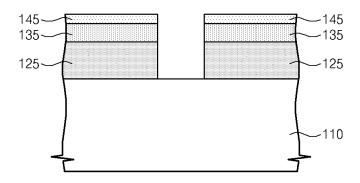

- <32> 도 2b를 참조하면, 노광 및 현상 공정을 수행하여 코팅막(120)을 노출시키는 제1 포토레지스트 패턴(135)과 제2 포토레지스트 패턴(145)이 형성된다. 상기 노광 공정은 ArF 광원을 이용할 수 있다. 전술한 바와 같이 한 번의 노광 및 현상 공정을 수행하여 제1 및 제2 포토레지스트 패턴(135,135)이 형성될 수 있다.

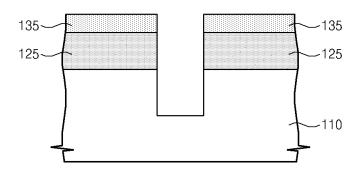

- <33> 도 2c를 참조하면, 제1 및 제2 포토레지스트 패턴(135,145)을 식각 마스크로 사용하여 코팅막(120)을 식각하여 기판(110)을 노출시키는 코팅막 패턴(125)이 형성된다. 코팅막(120)이 식각되는 동안 제2 포토레지스트 패턴 (145)도 식각되어 제거될 수 있다.

- <34> 종래 기술에서 화학기상증착에 의해 형성된 비정질 탄소막은 파티클을 많이 유발하였지만, 본 발명의 실시예에서 스핀 코팅에 의해 형성된 코팅막(예컨대, 탄소 스핀 온 하드마스크층)은 파티클의 발생을 억제할 수 있다.

- <35> 도 2d를 참조하면, 제1 포토레지스트 패턴(135) 및 코팅막 패턴(125)을 식각 마스크로 사용하여 노출된 기판 (110)이 식각된다.

- <36> 본 발명의 실시예에 따르면, 식각 마스크를 형성하기 위해 세 번의 스핀 코팅 공정과 한 번의 식각 공정이 수행된다. 따라서, 두 번의 화학기상증착 공정, 두 번의 스핀 코팅 공정, 두 번의 식각 공정을 수행하여 식각 마스크를 형성하는 종래 기술보다 공정 수가 감소하여 반도체 제조 공정이 단순화될 수 있다.

- <37> 한편, 본 발명의 상세한 설명에서는 구체적인 실시예에 관하여 설명하였으나, 본 발명의 범위에서 벗어나지 않는 한도 내에서 여러 가지 변형이 가능함은 물론이다. 그러므로 본 발명의 범위는 상술한 실시예에 국한되어 정해져서는 안되며 후술하는 특허청구범위뿐만 아니라 이 발명의 특허청구범위와 균등한 것들에 의해 정해져야한다.

#### 발명의 효과

- <38> 본 발명의 실시예에 따르면, 식각 마스크를 형성하기 위한 공정 수가 감소하여 반도체 제조 공정이 단순화될 수 있다.

- <39> 본 발명의 실시예에 따르면, 식각 마스크가 스핀 코팅에 의해 형성된 코팅막이 식각되어 형성되므로, 파티클의 발생이 억제될 수 있다.

#### 도면의 간단한 설명

- <1> 도 1a 내지 도 1e는 종래 기술에 따른 반도체 장치의 형성 방법을 설명하기 위한 단면도들이다.

- <2> 도 2a 내지 도 2d는 본 발명의 실시예에 따른 반도체 장치의 형성 방법을 설명하기 위한 단면도들이다.

- <3> & 도면의 주요부분에 대한 참조번호의 설명 &

- <4> 110 : 기판 120 : 코팅막

- < > 125 : 코팅막 패턴 130 : 제1 포토레지스트막

- <6> 135 : 제1 포토레지스트 패턴 140 : 제2 포토레지스트막

- <7> 145 : 제2 포토레지스트 패턴

### 도면

#### 도면1a

(종래 기술)

# *도면1b*

(종래 기술)

# *도면1c*

(종래 기술)

# 도면1d

(종래 기술)

# 도면1e

(종래 기술)

# 도면2a

# 도면2b

# 도면2c

# 도면2d