(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

FL

(11)特許番号

特許第5806853号 (P5806853)

(45) 発行日 平成27年11月10日(2015.11.10)

(24) 登録日 平成27年9月11日 (2015.9.11)

(51) Int. CL.

GO5F 1/56 (2006.01)

GO5F 1/56 32OB

請求項の数 1 (全 9 頁)

(21) 出願番号 特願2011-107610 (P2011-107610) (22) 出願日 平成23年5月12日 (2011.5.12)

(65) 公開番号 特開2012-238233 (P2012-238233A)

(43) 公開日 平成24年12月6日 (2012.12.6) 審査請求日 平成26年3月4日 (2014.3.4) ||(73)特許権者 000002325

セイコーインスツル株式会社

千葉県千葉市美浜区中瀬1丁目8番地

|(74)代理人 100154863

弁理士 久原 健太郎

(74)代理人 100142837

弁理士 内野 則彰

(74)代理人 100123685

弁理士 木村 信行

(72) 発明者 坂口 薫

千葉県千葉市美浜区中瀬1丁目8番地 セ

イコーインスツル株式会社内

|(72)発明者 井村 多加志

千葉県千葉市美浜区中瀬1丁目8番地 セ

イコーインスツル株式会社内

最終頁に続く

(54) 【発明の名称】 ボルテージレギュレータ

#### (57)【特許請求の範囲】

### 【請求項1】

基準電圧を出力する基準電圧回路と、

前記基準電圧と出力電圧に基づいた電圧とを比較し、前記出力電圧が一定になるよう出力トランジスタのゲート電圧を制御する差動増幅回路と、

前記出力トランジスタに過電流が流れたことを検出し、前記出力トランジスタの電流を 制限する過電流保護回路と、を備えたボルテージレギュレータであって、

前記基準電圧回路は、第一のNMOSデプレッショントランジスタと、第一のNMOSトランジスタと、を備え、

前記過電流保護回路は、前記出力トランジスタの出力電流をセンスするセンストランジスタと、前記センストランジスタに流れる電流を流すゲートとドレインを短絡した第二のNMOSデプレッショントランジスタと、カレントミラー接続する第二のNMOSトランジスタを備え、

前記第一のNMOSデプレッショントランジスタと前記第一のNMOSトランジスタは前記基準電圧回路の基準電圧を決定する素子であって、前記前記第二のNMOSデプレッショントランジスタと前記第二のNMOSトランジスタは前記過電流保護回路の最大出力電流または短絡電流を決定する素子であって、

前記第一のNMOSデプレッショントランジスタと前記第二のNMOSデプレッショントランジスタが同じ特性を有し、前記第一のNMOSトランジスタと前記第二のNMOSトランジスタが同じ特性を有することを特徴とするボルテージレギュレータ。

#### 【発明の詳細な説明】

#### 【技術分野】

## [0001]

本発明は、過電流保護回路を備えたボルテージレギュレータに関する。

#### 【背景技術】

## [0002]

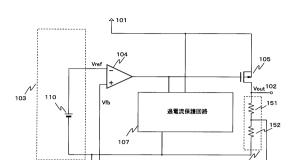

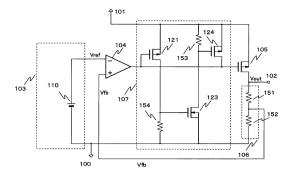

従来のボルテージレギュレータについて説明する。図9は、従来のボルテージレギュレータを示す図である。

従来のボルテージレギュレータは、グラウンド端子100と、電源端子101と、出力端子102と、基準電圧回路103と、差動増幅回路104と、出力トランジスタ105と、分圧回路106と、過電流保護回路107と、を備えている。

#### [00003]

従来のボルテージレギュレータの動作について説明する。

出力端子102の出力電圧Voutが所定電圧よりも高いと、即ち、分圧回路106の分圧電圧Vfbが基準電圧Vrefよりも高いと、差動増幅回路104の出力信号が高くなる。出力トランジスタ105のゲート電圧が高くなるので、出力トランジスタ105はオフしていき、出力電圧Voutは低くなる。また、出力電圧Voutが所定電圧よりも低いと、上記のように、出力電圧Voutは高くなる。つまり、ボルテージレギュレータの出力電圧Voutは、所定電圧で一定に保たれる。

## [0004]

ここで、ボルテージレギュレータの出力電圧Voutが負荷の増大により低下したとすると、出力電流Ioutが多くなり、最大出力電流Imになる。すると、この最大出力電流Imに応じ、出力トランジスタ105とカレントミラー接続するセンストランジスタ121に流れる電流が多くなる。その時、抵抗154に発生する電圧が高くなり、NMOSトランジスタ123がオンしていき、抵抗153に発生する電圧が高くなる。そして、PMOSトランジスタ124がオンしていき、出力トランジスタ105のゲート・ソース間電圧が低くなり、出力トランジスタ105がオフしていく。よって、出力電圧Voutが低くなる。ここで、抵抗154に発生する電圧により、出力トランジスタ105のゲート・ソース間電圧が低くなり、出力トランジスタ105がオフしていき、出力電流Ioutが最大出力電流Imに固定されるので、最大出力電流Imは抵抗154及びトランジスタ123の閾値によって決定される(特許文献1参照)。

#### [0005]

最大出力電流 I mを精度よくするためには、抵抗 1 5 4 及びトランジスタ 1 2 3 の閾値を精度よく調整する必要がある。調整するためには抵抗 1 5 4 やトランジスタ 1 2 3 の特性を評価した後、トリミングを行なう。評価は抵抗 1 5 4 及びトランジスタ 1 2 3 と同じ特性を有する代替素子に対して行なう。

#### [0006]

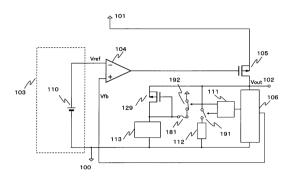

図10は、従来のテスト回路を備えたボルテージレギュレータを示す図である。従来のテスト回路を備えたボルテージレギュレータは、更に、電圧ディテクタ111と、第1のスイッチ191と、第2のスイッチ192と、評価対象の代替素子112を備える。

#### [0007]

分圧回路106の出力が電圧ディテクタ111に入力されると、電圧ディテクタ111の出力によって第1のスイッチ191が制御され、短絡状態となると評価対象の代替素子112に出力端子102から電流が流れる。電圧ディテクタ111の出力によって制御される第2のスイッチ192が短絡状態になると、PMOSトランジスタ129がオフしていき、内部回路素子113に出力端子102から電流が流れない。よって、図10の構成を用いると評価対象の代替素子112の電気的特性を精度よく評価することが出来る(特許文献2参照)。

### 【先行技術文献】

20

10

30

#### 【特許文献】

[0008]

【特許文献 1 】特開 2 0 0 5 - 2 9 3 0 6 7 号公報

【特許文献2】特開2008-140113号公報

【発明の概要】

【発明が解決しようとする課題】

[0009]

しかしながら、従来の技術では、ボルテージレギュレータの最大出力電流Imを正確に設定する過電流保護トリミングを行うために、Imを決定する素子を評価するための特有のテスト回路が必要であった。テスト回路はボルテージレギュレータが製品として機能する時は必要無いものであり、テスト回路があることでボルテージレギュレータICのチップ面積は大きくなり、チップ面積が大きいとウェハ1枚当たりのチップ数が少ないため、コスト面で不利である。また、評価対象の代替素子の電気的特性を評価するテスト工程の存在はICの製造原価を高めるため、コスト面で不利である。

[0010]

本発明では、上記課題を鑑みて、最大出力電流を精度よく定めるためのテスト回路及び テスト工程を省いたボルテージレギュレータを提供する。

【課題を解決するための手段】

[0011]

従来の課題を解決するために、本発明のボルテージレギュレータでは基準電圧回路における基準電圧Vrefを決定する素子と過電流保護回路において最大出力電流Imを決定する素子に同一の特性を有する素子を用いる構成とした。

【発明の効果】

[0012]

本発明のボルテージレギュレータでは、テスト回路で過電流保護回路の評価対象の代替素子を評価することなく、最大出力電流Imを推定することが出来る。トリミング前の出力電圧Voutは、基準電圧回路における基準電圧Vrefを決定する素子の特性値によって決定される。一方、最大出力電流Imを決定する過電流保護回路中の素子が基準電圧Vrefを決定する素子と同じであることから、出力電圧Voutと最大出力電流Imの製造上のばらつきに相関が生まれ、最大出力電流Imを決定する素子のテスト回路及びテスト工程無しでImを把握できる。よって、本発明のボルテージレギュレータは、テスト回路を用いないためチップ面積を縮小することが出来、テスト工程を省くこと出来るので、製造コストを低減するという効果がある。

【図面の簡単な説明】

[0013]

【図1】本実施形態のボルテージレギュレータを示す回路図である。

- 【図2】本実施形態のボルテージレギュレータの一例を示す回路図である。

- 【図3】本実施形態のボルテージレギュレータの他の例を示す回路図である。

- 【図4】本実施形態のボルテージレギュレータの他の例を示す回路図である。

- 【図5】本実施形態のボルテージレギュレータの他の例を示す回路図である。 【図6】本実施形態のボルテージレギュレータの他の例を示す回路図である。

- 【図7】本実施形態のボルテージレギュレータの他の例を示す回路図である。

- 【図8】本実施形態のボルテージレギュレータの他の例を示す回路図である。

- 【図9】従来のボルテージレギュレータを示す回路図である。

- 【図10】従来のテスト回路を備えたボルテージレギュレータを示す回路図である。ある

【発明を実施するための形態】

[0014]

図1は、本実施形態のボルテージレギュレータを示す回路図である。 本実施形態のボルテージレギュレータは、基準電圧回路103と、差動増幅回路104 10

20

30

30

40

と、出力トランジスタ105と、抵抗151と抵抗152を備えた分圧回路106と、過電流保護回路107を備えている。

#### [0015]

差動増幅回路104は、反転入力端子に基準電圧回路103の出力端子を接続し、非反転入力端子に分圧回路106の出力端子を接続し、出力端子は過電流保護回路107及び出力トランジスタ105のゲートに接続する。出力トランジスタ105は、ソースに電源端子101を接続し、ドレインに出力端子102を接続する。分圧回路106は、出力端子102とグラウンド端子100の間に接続され、抵抗151と抵抗152の接続点を差動増幅回路104の非反転入力端子に接続する。

### [0016]

ここで、本実施形態のボルテージレギュレータは、基準電圧回路103の基準電圧Vrefを決定する素子と、過電流保護回路107の最大出力電流Imを決定する素子を同じ特性を有する素子で構成する。このようにすると、基準電圧Vrefと最大出力電流Imに正の相関が生じる。または、基準電圧回路103の基準電圧Vrefを決定する素子と、過電流保護回路107の出力電圧Voutが0Vになった時の出力電流、即ち短絡電流Isを決定する素子を同じ特性を有する素子で構成する。このようにすると、基準電圧Vrefと短絡電流Isに正の相関が生じる。特に、半導体集積回路では同一の特性を有する素子は、相対精度が高いため、比較的強い相関を持つ。

#### [0017]

出力電圧Voutは、基準電圧Vrefと分圧回路106の抵抗151と抵抗152の分圧比によって決定される。即ち、抵抗151と152の分圧比が既知であれば、出力電圧Voutから基準電圧Vrefを推定することが出来る。半導体集積回路において抵抗比の精度は高いため、実際の抵抗の分圧比はほぼ設計値通りであると考えられる。従って、出力電圧Voutから基準電圧Vrefを推定可能である。即ち、出力電圧Voutから最大出力電流Imも推定可能となる。

#### [0018]

従来の構成では、最大出力電流Imまたは短絡電流Isを正確に定めるために、最大出力電流Imまたは短絡電流Isを評価するテスト回路が必要であったが、本実施形態の構成を用いることでテスト回路は不要となりチップ面積を縮小できる。更に、本実施形態の構成を用いるとテスト回路の測定の工程を省くことが出来る。

以上記載したように、本実施形態のボルテージレギュレータは、チップ面積の縮小、及び、テスト工程の短縮が出来るため、製造コストを低減する効果を得ることが出来る。

#### [0019]

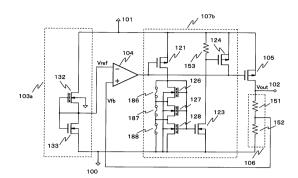

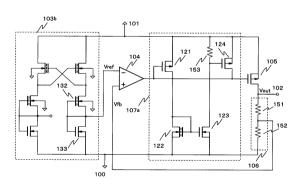

図 2 は、本実施形態のボルテージレギュレータの一例を示す回路図である。過電流保護回路 1 0 7 と基準電圧回路 1 0 3 の一具体例を示す。

図2の基準電圧回路103aは、NMOSデプレッショントランジスタ132とNMOSトランジスタ133を備え、ED型基準電圧回路を構成している。

# [0020]

また、図2の過電流保護回路107aは、出力トランジスタ105とカレントミラー接続するセンストランジスタ121と、NMOSデプレッショントランジスタ122と、NMOSトランジスタ123と、抵抗153と、PMOSトランジスタ124を備えている。従来のボルテージレギュレータと異なる点は、抵抗154の代わりに非飽和動作するNMOSデプレッショントランジスタ122を用いている点である。

## [0021]

NMOSデプレッショントランジスタ132は、ドレインを電源端子101と接続し、ゲート及びソースを差動増幅回路104の反転入力端子と接続する。NMOSトランジスタ133は、ゲート及びドレインをNMOSデプレッショントランジスタ132のソースと接続し、ソースをグラウンド端子100に接続する。

#### [0022]

センストランジスタ121は、ゲートを出力トランジスタ105のゲートに接続し、ド

10

20

30

40

10

20

30

40

50

レインをNMOSデプレッショントランジスタ122のドレインに接続し、ソースは電源端子101に接続する。NMOSデプレッショントランジスタ122は、ゲートをドレインとNMOSトランジスタ123のゲートに接続し、ソースをグラウンド端子100に接続する。NMOSトランジスタ123は、ソースはグラウンド端子に接続し、ドレインは抵抗153の一方の端子に接続する。抵抗153は、他方の端子を電源端子101に接続する。PMOSトランジスタ124は、ゲートを抵抗153の一方の端子に接続し、ソースは電源端子に接続し、ドレインは出力トランジスタ105のゲートに接続する。

### [0023]

以上のような構成のボルテージレギュレータにおいて、過電流保護特性はNMOSデプレッショントランジスタ122とNMOSトランジスタ123の特性によって決定し、基準電圧VrefはNMOSデプレッショントランジスタ132とNMOSトランジスタ133の特性によって決定する。従って、これらのトランジスタを、同じ特性を有する素子を用いることで、基準電圧Vrefと最大出力電流Imとの間には強い相関が生じることから、出力電圧Voutから最大出力電流Imが推定可能となる。ここでは、NMOSデプレッショントランジスタ122とNMOSデプレッショントランジスタ132に同じ閾値を有し、NMOSトランジスタ123とNMOSトランジスタ133に同じ閾値を有する。

#### [0024]

本実施形態のボルテージレギュレータは、以上記載したような構成を用いることで、テスト回路は不要となりチップ面積を縮小でき、更にテスト回路の測定の工程を省くことが出来ので、製造コストを低減する効果を得ることが出来る。

#### [0025]

なお、図3の過電流保護回路107bに示すように、過電流保護回路107aのNMOSデプレッショントランジスタ122を、Nchデプレッショントランジスタ126、127、128を用い直列に接続し、ヒューズ186、187、188でトリミングするように構成しても良い。過電流保護回路107をこのように構成し、NMOSデプレッショントランジスタをトリミングすることによって、過電流保護回路の特性を最適に補正することが出来る。

### [0026]

ここで、N c h デプレッショントランジスタ 1 3 2 、 1 2 6 、 1 2 7 、 1 2 8 は、全て同じ閾値を有する。

但し、Nchデプレッショントランジスタとヒューズの構成は、この回路や数に限定されるものではない。

### [0027]

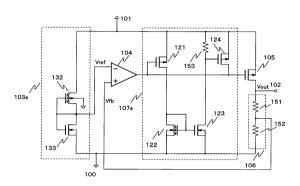

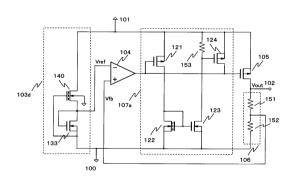

また、図4は、本実施形態のボルテージレギュレータの他の例を示す回路図である。過電流保護回路107の他の具体例を示す。

図4の過電流保護回路107cと図2の過電流保護回路107aとの違いは、NMOSトランジスタ123の代わりにソースを出力端子102と接続した点のみが異なるNMOSトランジスタ125を用いることである。図2の過電流保護回路107aが垂下型であるのに対して、図4の過電流保護回路107cはフ字型である。

## [0028]

図4の過電流保護回路107cにおいても、出力電圧Vout が0Vになった時の出力電流、即ち短絡電流 Is はNMOS トランジスタ125NMOS デプレッショントランジスタ122の特性によって決定される。従って、短絡電流 Is は基準電圧Vre f と相関を持つので、同様の効果を得ることが出来る。

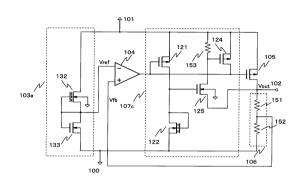

## [0029]

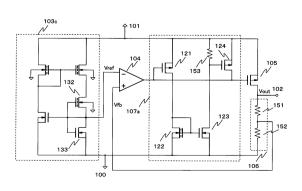

また、図5から図8に、本実施形態のボルテージレギュレータの他の例を示す回路図である。基準電圧回路103の他の具体例を示す。

図 5 の基準電圧回路 1 0 3 b においては、NMOSデプレッショントランジスタ 1 2 2 とNMOSデプレッショントランジスタ 1 3 2 は同じ閾値を有し、NMOSトランジスタ

123とNMOSトランジスタ133は同じ閾値を有する。

#### [0030]

また、図6の基準電圧回路103cにおいては、NMOSデプレッショントランジスタ122とNMOSデプレッショントランジスタ132は同じ閾値を有し、NMOSトランジスタ123とNMOSトランジスタ133は同じ閾値を有する。

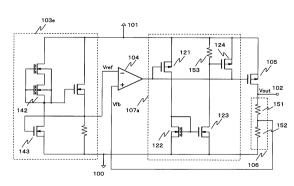

### [0031]

また、図 7 の基準電圧回路 1 0 3 d においては、N M O S デプレッショントランジスタ 1 2 2 と N M O S デプレッショントランジスタ 1 4 0 は同じ閾値を有し、N M O S トランジスタ 1 2 3 と N M O S トランジスタ 1 3 3 は同じ閾値を有する。

[0032]

また、図 8 の基準電圧回路 1 0 3 e においては、NMOSデプレッショントランジスタ 1 2 2 とNMOSデプレッショントランジスタ 1 4 2 は同じ閾値を有し、NMOSトランジスタ 1 2 3 とNMOSトランジスタ 1 4 3 は同じ閾値を有する。

## [0033]

これらのようなNMOSデプレッショントランジスタとNMOSトランジスタの特性によって決定する基準電圧Vrefであれば、同様に本発明の効果を得ることが出来る。

## 【符号の説明】

### [0034]

- 103 基準電圧回路

- 104 差動増幅回路

- 105 出力トランジスタ

- 106 分圧回路

- 107 過電流保護回路

- 110 基準電圧源

- 1 1 1 電圧ディテクタ

- 112 評価対象の代替素子

- 1 1 3 内部回路

10

# 【図1】

# 【図3】

# 【図2】

# 【図4】

# 【図5】

【図7】

【図6】

【図8】

# 【図9】

# 【図10】

## フロントページの続き

審査官 神山 貴行

(56)参考文献 特開2008-047158(JP,A) 特開2003-186554(JP,A)

(58)調査した分野(Int.CI., DB名) G05F 1/56