#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

### (19) World Intellectual Property Organization

International Bureau

(10) International Publication Number WO 2016/128853 A1

(43) International Publication Date 18 August 2016 (18.08.2016)

(21) International Application Number:

PCT/IB2016/050388

(22) International Filing Date:

27 January 2016 (27.01.2016)

(26) Publication Language:

English English

JP

(30) Priority Data:

(25) Filing Language:

2015-022933 9 February 2015 (09.02.2015)

- (71) Applicant: SEMICONDUCTOR ENERGY LABORAT-ORY CO., LTD. [JP/JP]; 398, Hase, Atsugi-shi, Kanagawa 2430036 (JP).

- (72) Inventors: TAMURA, Hikaru; c/o SEMICONDUCTOR ENERGY LABORATORY CO., LTD., 398, Hase, Atsugishi, Kanagawa 2430036 (JP). TSUTSUI, Naoaki. ISOBE, Atsuo.

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IR, IS, KE, KG, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, ST, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

#### Published:

— with international search report (Art. 21(3))

(54) Title: SEMICONDUCTOR DEVICE, ELECTRONIC COMPONENT, AND ELECTRONIC DEVICE

(57) Abstract: To provide a semiconductor device including element layers that are stacked. A first wiring layer and a second wiring layer are stacked between a first element layer and a second element layer. A third wiring layer and a fourth wiring layer are stacked over the second element layer. Transistors of logic cells are provided in the first element layer. Wirings of the logic cells are provided in the first wiring layer or the second wiring layer. Input ports and output ports of the logic cells are provided in the third wiring layer. The input port of one of the logic cells is connected to the output port of another logic cell through the wiring of the third wiring layer or the fourth wiring layer. Connecting the logic cells through the wiring layers over the second element layer improves the efficiency of steps of arranging and connecting the logic cells.

#### **DESCRIPTION**

# SEMICONDUCTOR DEVICE, ELECTRONIC COMPONENT, AND ELECTRONIC DEVICE

5

15

#### TECHNICAL FIELD

[0001]

The specification, drawings, and claims of this application (hereinafter referred to as "this specification and the like") disclose, for example, a semiconductor device, an electronic component, an electronic device, operating methods thereof, and manufacturing methods thereof. Examples of a technical field of one embodiment of the present invention include a semiconductor device, a storage device, a processing unit, a switch circuit (e.g., a power switch and a wiring switch), a display device, a liquid crystal display device, a light-emitting device, a lighting device, a power storage device, an input device, an imaging device, a driving method thereof, and a manufacturing method thereof.

#### **BACKGROUND ART**

[0002]

An example of a method for designing a semiconductor device such as SOC is a standard cell method. In this designing method, a plurality of cells (also referred to as logic cells or standard cells, for example) are prepared for individual functions, and a semiconductor device is fabricated using them as its components. In the case of a standard cell method, steps of arranging cells and connecting wirings between the cells are performed with an automatic placer and router.

25 [0003]

A variety of semiconductor devices that take advantage of the extremely low off-state current of a transistor whose semiconductor region is formed using an oxide semiconductor (hereinafter, such a transistor may be referred to as an OS transistor) have been proposed.

[0004]

For example, Patent Documents 1 and 2 each disclose a storage circuit using an OS transistor. Non-Patent Document 1 discloses a processor that is capable of power gating and in which backup circuits using OS transistors are provided in a flip-flop and an SRAM. Patent Document 3 discloses a semiconductor device using a combination of a standard cell including a Si transistor and an OS transistor and a standard cell including a Si transistor.

## 35 [Reference]

[Patent Documents]

[0005]

[Patent Document 1] Japanese Published Patent Application No. 2011-187950

[Patent Document 2] Japanese Published Patent Application No. 2013-008437

[Patent Document 3] Japanese Published Patent Application No. 2013-243351

[Non-Patent Document]

[0006]

[Non-Patent Document 1] H. Tamura et al., "Embedded SRAM and Cortex-M0 Core with Backup Circuits Using a 60-nm Crystalline Oxide Semiconductor for Power Gating," IEEE COOL Chips XVII, Apr. 2014.

#### DISCLOSURE OF INVENTION

[0007]

15

30

A novel semiconductor device, an operating method for the novel semiconductor device, or a manufacturing method for the novel semiconductor device is provided. Alternatively, a novel semiconductor device including at least two element layers that are stacked, an operating method for the novel semiconductor device, or a manufacturing method for the novel semiconductor device is provided. Alternatively, a semiconductor device capable of power gating or an operating method for the semiconductor device is provided. Alternatively, a method that allows efficient designing of a semiconductor device is provided.

[8000]

Note that the description of a plurality of objects does not preclude the existence of each object. Note that one embodiment of the present invention does not necessarily achieve all the objects listed above. Other objects will be apparent from and can be derived from the description of the specification, the drawings, the claims, and the like, and such objects could be objects of one embodiment of the present invention. [0009]

(1) One embodiment of the present invention is a semiconductor device including a plurality of logic cells. The semiconductor device includes a first element layer, a second element layer, and first to k-th wiring layers (k is an integer of greater than 3). Each of the first element layer and the second element layer is provided with a plurality of transistors. to k-th wiring layers are stacked in this order. The first element layer is provided under the first wiring layer. The second element layer is provided between the second wiring layer and the The transistors of the logic cells are provided in the first element layer. third wiring layer.

Wirings of the logic cells are provided in the first wiring layer or the second wiring layer. An 35

input port and an output port of the logic cell are provided in the third wiring layer.

[0010]

In the above embodiment (1), the input port of one of the logic cells may be electrically connected to the output port of another logic cell through the wiring of the third wiring layer or through the wiring of the third wiring layer and the wiring of a fourth wiring layer.

[0011]

In the above embodiment (1), the resistivities of the third to k-th wiring layers can be lower than those of the first wiring layer and the second wiring layer. Alternatively, the wirings of the first wiring layer and the second wiring layer may contain a conductor containing tungsten, and the wirings of the third to k-th wiring layers may contain a conductor containing copper or aluminum.

[0012]

10

In the above embodiment (1), the plurality of transistors of the second element layer may each include an oxide semiconductor layer where a channel is formed.

15 [0013]

In the above embodiment (1), the length of a wiring grid interval of the third wiring layer is 1.5 times or 2 times that of a wiring grid interval of the second wiring layer.

[0014]

In the above embodiment (1), no second wiring layer may be provided.

20 [0015]

25

Note that in this specification and the like, a semiconductor device refers to a device that can function by utilizing semiconductor characteristics, and means a circuit including a semiconductor element (e.g., a transistor, a diode, or a photodiode), a device including the circuit, or the like. A chip including an integrated circuit, and an electronic component, a storage device, a display device, a light-emitting element, a lighting device, and an electronic device each including a chip in a package are examples of semiconductor devices and may include semiconductor devices.

[0016]

In this specification and the like, the description "X and Y are connected" means that X and Y are electrically connected, X and Y are functionally connected, and X and Y are directly connected. Accordingly, without limitation to a predetermined connection relation, for example, a connection relation shown in drawings or text, another connection relation is included in the drawings or the text. Here, each of X and Y denotes an object (e.g., a device, an element, a circuit, a wiring, an electrode, a terminal, a conductive film, or a layer).

35 [0017]

A transistor includes three nodes (terminals) called a gate, a source, and a drain. A gate is a node that controls the conduction state of a transistor. Depending on the channel type of the transistor or the levels of potentials supplied to the terminals, one of nodes (an input node and an output node) functions as a source and the other functions as a drain. Therefore, the terms "source" and "drain" are interchangeable in this specification and the like. Furthermore, the two terminals other than the gate may be referred to as a first terminal and a second terminal in this specification and the like.

[0018]

10

A node can be referred to as a terminal, a wiring, an electrode, a conductive layer, a conductor, an impurity region, or the like, depending on a circuit configuration, a device structure, and the like. Furthermore, a terminal, a wiring, or the like can be referred to as a node.

[0019]

Note that in many cases, a voltage refers to a potential difference between a certain potential and a reference potential (e.g., a ground potential (GND) or a source potential). A voltage can be referred to as a potential and vice versa. Note that a potential has a relative value. Thus, "GND" does not necessarily mean 0 V.

[0020]

In this specification and the like, ordinal numbers such as "first," "second" and "third" are used to show the order in some cases. Alternatively, ordinal numbers such as "first," "second" and "third" are used to avoid confusion among components in some cases, and do not limit the number of components or do not limit the order. For example, it is possible to replace the term "first" with the term "second" or "third" in describing one embodiment of the present invention.

25 [0021]

Other matters regarding the description of this specification and the like will be described in Embodiment 4.

[0022]

30

35

A novel semiconductor device, an operating method for the novel semiconductor device, or a manufacturing method for the novel semiconductor device can be provided. Alternatively, a novel semiconductor device including at least two element layers that are stacked, an operating method for the novel semiconductor device, or a manufacturing method for the novel semiconductor device can be provided. Alternatively, a semiconductor device capable of power gating or an operating method for the semiconductor device can be provided. Alternatively, a semiconductor device can be efficiently designed.

[0023]

5

20

Note that the description of the plurality of effects does not disturb the existence of other effects. In one embodiment of the present invention, there is no need to achieve all the effects described above. In one embodiment of the present invention, an object other than the above objects, an effect other than the above effects, and a novel feature will be apparent from the description of the specification and the drawings.

#### **BRIEF DESCRIPTION OF DRAWINGS**

[0024]

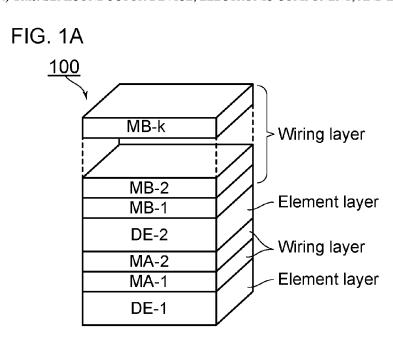

- FIGS. 1A to 1D are schematic diagrams illustrating structural examples of a semiconductor device and logic cells.

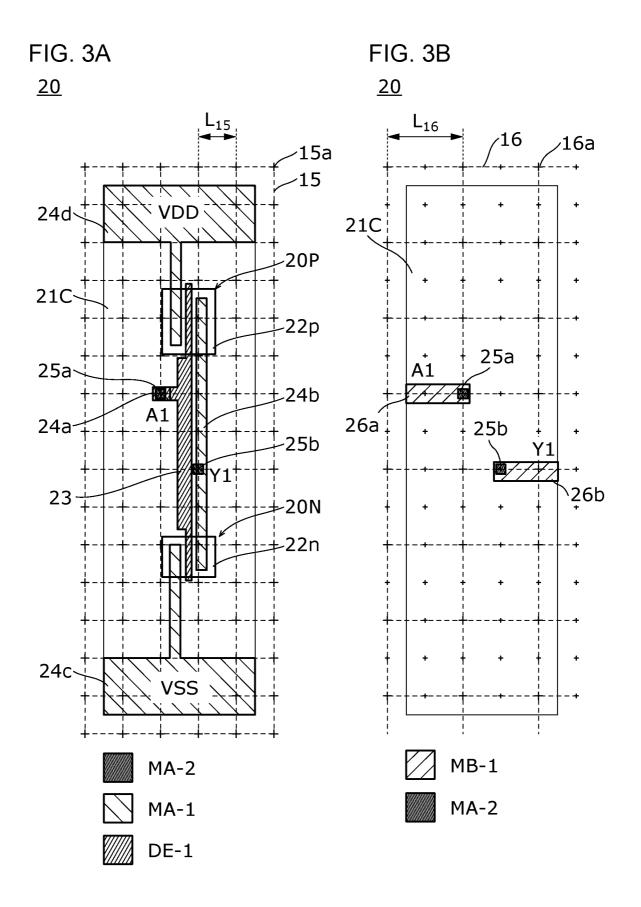

- FIGS. 2A to 2D are schematic diagrams illustrating structural examples of a semiconductor device and logic cells.

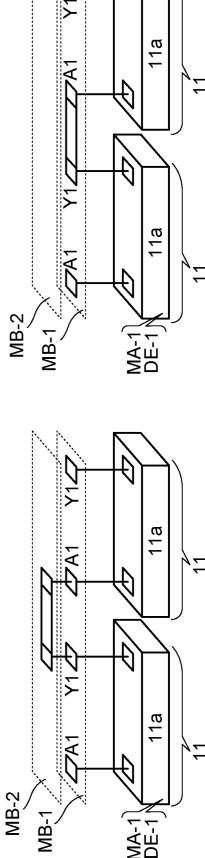

- FIGS. 3A and 3B each illustrate a layout example of an inverter cell.

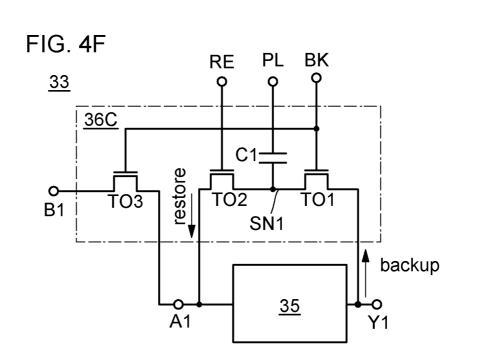

- FIGS. 4A to 4F are circuit diagrams each illustrating a combination example of a logic circuit and an oxide semiconductor transistor (oxide semiconductor transistors).

- FIG. 5 is a cross-sectional view schematically illustrating a layered structure of a semiconductor device.

- FIG. 6 is a block diagram illustrating a configuration example of a processing unit.

- FIG. 7 is a block diagram illustrating a configuration example of a processor core.

- FIG. 8 is a circuit diagram illustrating a configuration example of a flip-flop.

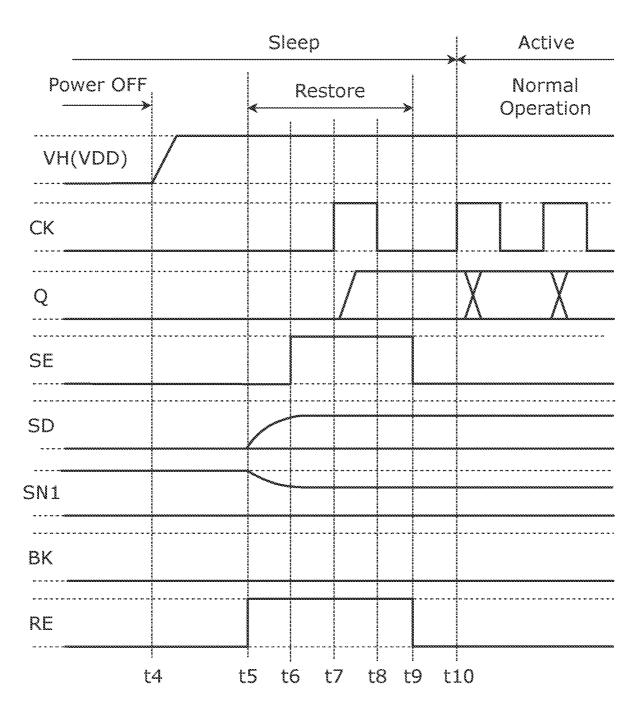

- FIG. 9 is a timing chart showing an operation example of a flip-flop.

- FIG. 10 is a timing chart showing an operation example of a flip-flop.

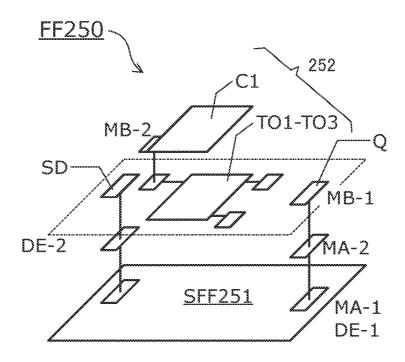

- FIG. 11 schematically illustrates a device structure example of a flip-flop.

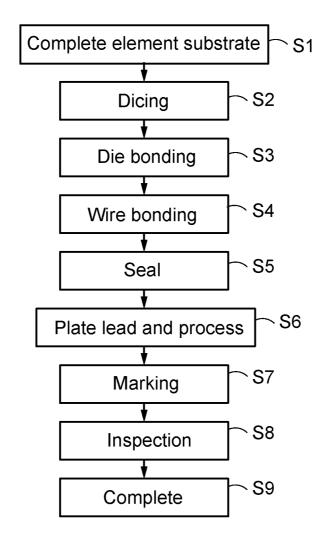

- FIG. 12A is a flow chart showing an example of a method for manufacturing an electronic component, and FIG. 12B is a perspective schematic diagram illustrating a structural example of the electronic component.

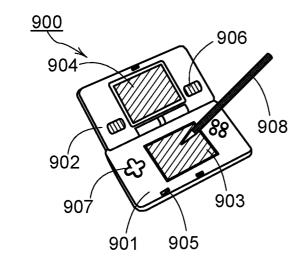

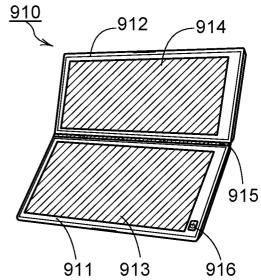

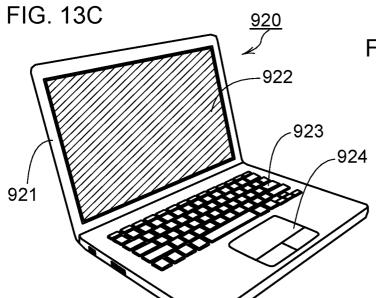

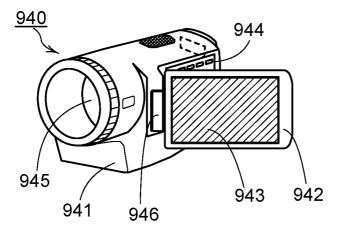

- FIGS. 13A to 13F each illustrate a structural example of an electronic device.

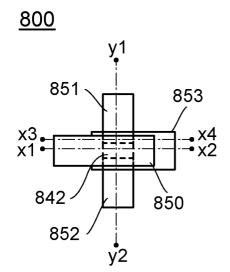

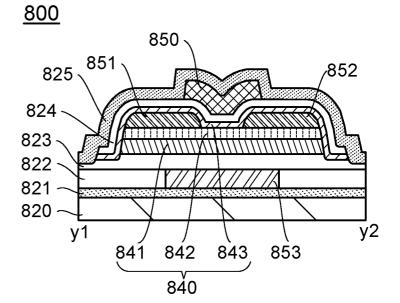

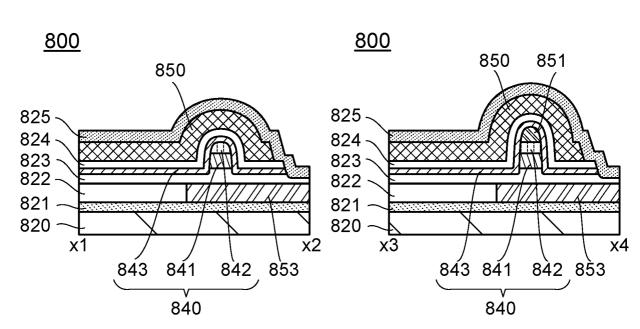

- FIG. 14A is a top view illustrating a structural example of an OS transistor, FIG. 14B is a cross-sectional view along y1-y2 in FIG. 14A, FIG. 14C is a cross-sectional view along x1-x2 in FIG. 14A, and FIG. 14D is a cross-sectional view along x3-x4 in FIG. 14A.

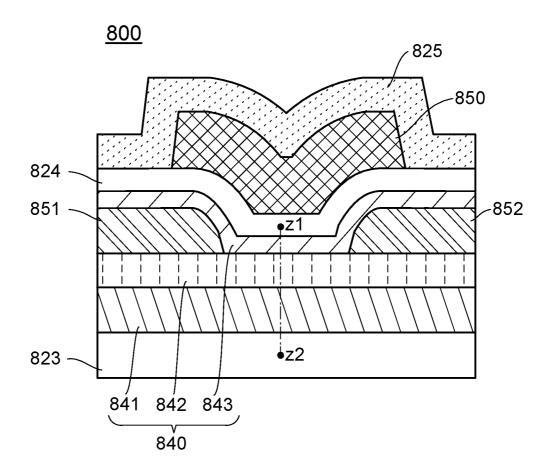

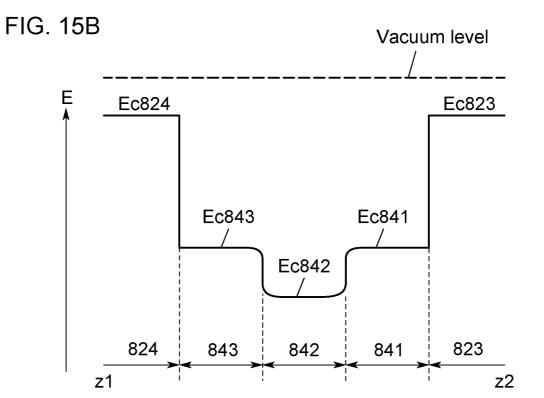

- FIG. 15A is a partly enlarged view of FIG. 14B, and FIG. 15B is an energy band diagram of an OS transistor.

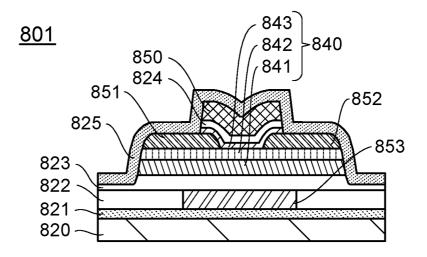

- FIGS. 16A to 16C are cross-sectional views each illustrating a structural example of an OS transistor.

FIGS. 17A and 17B are cross-sectional views illustrating a structural example of a transistor.

#### BEST MODE FOR CARRYING OUT THE INVENTION

5 [0025]

Embodiments of the present invention will be described below. Note that one embodiment of the present invention is not limited to the following description. It will be readily appreciated by those skilled in the art that modes and details of the present invention can be modified in various ways without departing from the spirit and scope of the present invention. Therefore, one embodiment of the present invention should not be construed as being limited to the following description of the embodiments.

[0026]

10

15

20

25

30

35

Any of the embodiments described below can be combined as appropriate. In addition, in the case where some structural examples (including a manufacturing method, an operating method, and the like) are given in one embodiment, any of the structural examples can be combined as appropriate, and any of the structural examples can be combined with one or more structural examples described in the other embodiments.

[0027]

[0028]

In this specification, a high power supply potential VDD may be abbreviated to a potential VDD, VDD, or the like, for example. The same applies to other components (e.g., a signal, a voltage, a potential, a circuit, an element, an electrode, and a wiring).

(Embodiment 1)

<< Structural example 1 of semiconductor device>>

Here, a semiconductor device in which two element layers are stacked will be described. FIG. 1A schematically illustrates a layered structure of a semiconductor device. A semiconductor device 100 includes two element layers DE-1 and DE-2, two wiring layers MA-1 and MA-2, and k wiring layers MB-1 to MB-k (k is an integer of greater than 1). The wiring layers MA-1, MA-2, and MB-1 to MB-k are stacked in this order. The element layer DE-2 is stacked over the element layer DE-1. The wiring layers MA-1 and MA-2 are provided between the element layer DE-1 and the element layer DE-2. The wiring layers MB-1 to MB-k are stacked over the element layer DE-1.

[0029]

The wiring layers MA-1, MA-2, and MB-1 to MB-*k* are each provided with a plurality of wirings. The element layers DE-1 and DE-2 are each provided with a plurality of transistors.

The element layers DE-1 and DE-2 can be provided with a resistor, a capacitor, a diode, and the like in addition to the transistors.

[0030]

In the semiconductor device 100, an interlayer insulating layer is provided between two adjacent wiring layers so as to isolate the two layers from each other. To electrically connect the wiring in an upper layer and the wiring in a lower layer, the interlayer insulating layer is provided with a plug. Similarly, an interlayer insulating layer is provided also between the element layer and the wiring layer that are adjacent to each other, and the elements of the element layer and the wirings of the wiring layer are connected to each other by the plug.

10 [0031]

<Element layers>

The element layers DE-1 and DE-2 are formed through different processes; thus, the device structure, materials of components, or the like of the transistor of the element layer DE-1 (hereinafter referred to as a transistor DE1) can be different from that of the transistor of the element layer DE-2 (hereinafter referred to as a transistor DE2).

[0032]

15

For example, the transistor DE1 can be formed over a semiconductor substrate. As the semiconductor substrate, a semiconductor substrate of a Group 14 element such as silicon, germanium, or the like, or a compound semiconductor substrate of silicon carbide, silicon germanium, gallium arsenide, indium phosphide, zinc oxide, or gallium oxide can be used, for example. The semiconductor substrate may be either a bulk semiconductor substrate or a silicon on insulator (SOI) substrate in which a semiconductor substrate is provided with a semiconductor layer with an insulating region therebetween. The crystal structure of the semiconductor substrate is preferably a single crystal structure or a polycrystalline structure. A semiconductor region of the transistor DE1 depends on a material and the crystal structure of the semiconductor substrate.

[0033]

25

30

35

A semiconductor region of the transistor DE2 is formed over the wiring layer MA-2 using a semiconductor deposited by a gas phase method. A semiconductor included in the semiconductor region is roughly divided into a single crystal semiconductor and a non-single-crystal semiconductor. As the non-single-crystal semiconductor, a polycrystalline semiconductor, a microcrystalline semiconductor, an amorphous semiconductor, and the like are given. As a semiconductor material, a Group 14 semiconductor containing one kind or a plurality of kinds of Group 14 elements such as Si, Ge, and C (e.g., silicon, germanium, silicon carbide, or silicon germanium), an oxide semiconductor (e.g., an In-Ga-Zn oxide), a compound

semiconductor, and the like are given.

[0034]

In the case where a semiconductor region of the transistor DE2 is formed of silicon, the semiconductor region can be formed using amorphous silicon deposited by a vapor deposition method, a sputtering method, or the like, or polycrystalline silicon obtained by crystallizing amorphous silicon, for example. For the crystallization of amorphous silicon, heat treatment, laser irradiation treatment, or the like can be used. Alternatively, the semiconductor region of the transistor DE2 can be formed using an oxide semiconductor deposited by a vapor deposition method, a sputtering method, or the like. In this case, the transistor DE2 is an OS transistor.

10 [0035]

5

<Logic cell>

The semiconductor device 100 includes one or more circuits composed of a plurality of logic cells 10. FIG. 1B schematically illustrates the structure of the logic cell 10. The logic cell 10 includes one or more transistors, a plurality of wirings, a port A1, and a port Y1. The port A1 is an input port, and a port Y1 is an output port.

[0036]

15

20

In the logic cell 10, a plurality of transistors are provided in the element layer DE-1. The plurality of transistors are electrically connected through the wiring provided in the wiring layer MA-1 or the wiring layer MA-2 so that a logic circuit 10a with a predetermined processing function is constructed.

[0037]

The logic circuit 10a has a function of processing data of the port A1 and outputting the processed data from the port Y1. There is no particular limitation on the configuration of the logic circuit 10a. For example, a basic logic gate circuit such as an inverter circuit or a NAND circuit, a flip-flop, a latch circuit, a counter, a multiplexer, or the like can be used. Alternatively, a complicated logic circuit such as an arithmetic unit can be used.

[0038]

Although the number of input ports of the logic cell 10 and the number of output port of thereof is each one here, depending on the circuit configuration of the logic cell 10, a plurality of input ports may be provided like the port A1. Furthermore, a plurality of output ports may be provided like the port Y1.

[0039]

30

35

The port A1 and the port Y1 are provided in the wiring layer MB-1. Two logic cells 10 are electrically connected to each other through the wiring of the wiring layer MB-1 or the wiring of the wiring layer MB-2. FIGS. 1C and 1D schematically illustrate the connection

between the two logic cells 10. In an example of FIG. 1C, the port Y1 of the logic cell 10 is electrically connected to the port A1 of another logic cell 10 through the wiring of the wiring layer MB-2. In an example of FIG. 1D, the port Y1 of the logic cell 10 is electrically connected to the port A1 of another logic cell 10 through the wiring of the wiring layer MB-1. In the semiconductor device 100, the logic circuit 10a is composed of the transistors DE1 and the wirings that are provided in the layers below the element layer DE-2, and the plurality of logic cells 10 (logic circuits 10a) are electrically connected through the wirings in the layers over the element layer DE-2.

[0040]

5

10

15

20

25

30

That is, a circuit portion (logic circuit 10a) of the logic cell 10 is composed of a stack (DE-1, MA-2, and MA-3) under the element layer DE-2, and the input port and the output port of the circuit portion are provided in the wiring layer MB-1 stacked over the element layer DE-2. [0041]

<Wiring layers>

In the semiconductor device 100, electrodes of the transistors DE1 and DE2, the wirings of the wiring layers, the plug that connects the wirings, and the like are preferably formed using a conductor with low resistivity (e.g., aluminum or copper). When the resistance of the wirings and the like is low, parasitic resistance and parasitic capacitance of the wirings are also low; thus, the delay of a signal can be inhibited, leading to reduction in power consumption. Furthermore, a via hole in which the plug is formed can be reduced in size, and this is advantageous for higher integration.

[0042]

(MA-1 and MA-2)

Meanwhile, conductors of the wirings and the like of the wiring layers MA-1 and MA-2, which are formed below the element layer DE-2, need to withstand the treatment temperature in a formation process of the element layer DE-2 (transistor DE2). Unlike a Si transistor formed using a single crystal silicon wafer, a semiconductor region of the transistor DE2 is formed using a semiconductor deposited by a gas phase method. Thus, to improve the characteristics and reliability of the transistor DE2, the semiconductor region may be formed at treatment temperatures higher than or equal to 400 °C. Heat treatment at such high temperatures is performed to improve the crystallinity of polycrystalline silicon, for example, in the case where the transistor DE2 is a polycrystalline silicon transistor. In the case where the transistor DE2 is an OS transistor, heat treatment at such high temperatures is performed to reduce oxygen vacancies in an oxide semiconductor region or to reduce hydrogen (H).

35 [0043]

Therefore, the wirings and the like of the wiring layers MA-1 and MA-2 are preferably formed using a conductor having resistance to heat of approximately 400 °C (e.g., heat in the range from 400 °C to 500 °C). Examples of such a conductor include polycrystalline silicon to which an impurity such as phosphorus is added, silicide, a refractory metal, an alloy of refractory metals, and a compound of a refractory metal. Examples of refractory metals include tungsten, molybdenum, tantalum, titanium, chromium, niobium, vanadium, and platinum. Examples of an alloy of refractory metals that can be used for the wirings of the wiring layers MA-1 and MA-2 include a Ta-W alloy and a Mo-W alloy. Examples of a compound of a refractory metal include titanium nitride and tantalum nitride.

10 [0044]

The wirings and the like of the wiring layers MA-1 and MA-2 are each either a single-layer conductor or a stack of conductors. The wirings of the wiring layers MA-1 and MA-2 and the plug connected to them are preferably formed using tungsten or molybdenum, each of which has both high heat resistance and high conductance, especially, tungsten.

15 [0045]

20

25

30

35

(MB-1 to MB-k)

The wiring layer MB-i (i is an integer of 1 or more and k or less) is stacked over the element layer DE-2; thus, the wiring of the wiring layer MB-j and the plug connected to the wiring can be formed using a conductor having low heat resistance but having low resistance (e.g., a conductor containing aluminum or copper as its main component). Examples of such a low-resistance conductor include aluminum, copper, an aluminum alloy, an aluminum alloy (e.g., an Al-Mo alloy and an Al-Ti alloy) containing an element that prevents a hillock (e.g., Si, Cr, Sc, Ta, and Ti), and a copper alloy (e.g., a Cu-Mo alloy and a Cu-W alloy). The wirings of the wiring layer MB-j and the plug connected to the wirings are each either a single-layer conductor or a stack of conductors. In the case where each of them is a stack of conductors, a stack of the low-resistance conductor and the high heat-resistant conductor may be used. Such a stack can increase heat resistance of the wirings and the plug or can reduce migration. For example, in the case where a stack of conductors is provided, a refractory metal such as titanium, molybdenum, or tungsten or a nitride thereof (titanium nitride, molybdenum nitride, or tungsten nitride) can be provided under and/or over the low-resistance conductor. For example, the wirings and the plug can each be formed using three layers of conductors of titanium nitride, aluminum, and titanium nitride.

[0046]

That is, for the wiring layer MB-*j* stacked over the element layer DE-2, a low-resistance conductor is used to achieve high-speed operation of the semiconductor device 100.

Meanwhile, for the wiring layers MA-1 and MA-2 below the element layer DE-2, which require high heat resistance rather than low resistance, a conductor having higher resistivity than the conductor of the wiring layer MB-*j* is used. It is needless to say that depending on the process temperature for the element layer DE-2, the wirings of the wiring layers MA-1 and MA-2 can be formed using a low-resistance conductor like the wiring of the wiring layer MB-*j*.

[0047]

5

Since all the transistors of the logic cells 10 are provided in the element layer DE-1, all the components of the logic circuits 10a are provided in the stack of the wiring layers MA-1 and MA-2 and the element layer DE-1 below the element layer DE-2 so that the logic circuits 10a can be easily arranged and connected. Furthermore, the port A1 and the port Y1 are provided in the wiring layer MB-1 over the element layer DE-2, whereby a step of arranging the logic cells 10 and a step of connecting wirings between a plurality of logic cells 10 can be easily performed in designing the semiconductor device 100. This enhances the design efficiency of the semiconductor device 100. Furthermore, connecting the plurality of logic cells 10 through the low-resistance wirings of the wiring layers MB-1 and MB-2 allows the logic cell 10 to operate at high frequencies.

[0048]

15

20

30

Note that depending on the arrangement of the logic cells 10, it is better to connect the logic cells 10 through the wiring of the wiring layer MA-2 in some cases. In such logic cell 10, the port A1 and the port Y1 are provided in the wiring layer MA-2.

[0049]

<< Structural example of semiconductor device>>

In the case where the logic circuit 10a of the logic cell 10 can be designed with the use of the transistors DE1 of the element layer DE-1 and the wirings of the wiring layer MA-1, the wiring layer MA-2 is not necessarily provided. FIGS. 2A to 2D illustrate such structural examples.

[0050]

The semiconductor device 101 in FIG. 2A is a modification example of the semiconductor device 100 and is the same as the semiconductor device 100 except that the wiring layer MA-2 is not provided. The semiconductor device 101 includes a circuit composed of a plurality of logic cells 11. FIG. 2B schematically illustrates the configuration example of the logic cell 11. The logic cell 11 is a modification example of the logic cell 10, and a circuit portion (logic circuit 11a) of the logic cell 11 is composed of the element layer DE-1 and the wiring layer MA-1.

35 [0051]

The logic cells 11 are connected like the logic cells 10. FIG. 2C illustrates an example where two logic cells 11 are connected to each other through the wiring of the wiring layer MB-2. FIG. 2D illustrates an example where two logic cells 11 are connected through the wiring of the wiring layer MB-1.

5 [0052]

Although the number of input ports of the logic cell 11 and the number of output ports thereof are each one here, depending on the circuit configuration of the logic cell 11, a plurality of input ports may be provided or a plurality of output ports may be provided. The input port and the output port are placed and routed like the port A1 and the port Y1. The same applies to the logic circuit 10.

[0053]

Specific embodiments of the present invention will be described below using the semiconductor device 100 and the logic cell 10 as an example, and the same applies to the semiconductor device 101 and the logic cell 11.

15 [0054]

<<Layout example of logic cell 10>> [0055]

The layout of the logic cell 10 will be described using an inverter cell as an example. FIGS. 3A and 3B schematically illustrate the layout of the inverter cell 20. FIG. 3A illustrates the layout of a transistor 20P, a transistor 20N, and wirings of the wiring layers MA-1 and MA-2, and FIG. 3B illustrates the layout of wirings of the wiring layers MA-2 and MB-1. FIG. 3A also illustrates a wiring grid 15 and grid points 15a used in designing the element layer DE-1 and the wiring layers MA-1 and MA-2. FIG. 3B also illustrates a wiring grid 16 and grid points 16a used in designing the wiring layers MB-1 and MB-2. Note that L<sub>15</sub> and L<sub>16</sub> are grid intervals.

25 [0056]

20

The transistor 20P is a p-channel transistor, and the transistor 20N is an n-channel transistor. In a region 21C, the inverter cell 20 is formed. Regions 22p and 22n and a wiring 23 are provided in the element layer DE-1. In the region 22p, the transistor 20P is formed, while in the region 22n, the transistor 20N is formed. The regions 22p and 22n include impurity regions forming sources and drains of the transistors 20P and 20N. Part of the wiring 23 forms gates of the transistors 20N and 20P.

[0057]

30

35

The wirings 24a to 24d are provided in the wiring layer MA-1, the wirings 25a and 25b are provided in the wiring layer MA-2, and the wirings 26a and 26b are provided in the wiring layer MB-1. The transistor 20P and the transistor 20N are electrically connected in series

through the wiring 26b. The wiring 24c forms a power supply line (VSS line) for supplying a low power supply potential VSS. The wiring 24d forms a power supply line (VDD line) for supplying a high power supply potential VDD. [0058]

The port A1 is formed using the wiring 26a. The wiring 26a is electrically connected to the wiring 23 through the wirings 24a and 25a. The port Y1 is formed using the wiring 26b. The wiring 26b is electrically connected to the wiring 24b through the wiring 25b. The wirings 25a, 24a, and 23 are provided so as to overlap with one common grid point 15a. Similarly, the wirings 25b and 24b are provided so as to overlap with one common grid point 15a.

10 [0059]

5

Since the wiring layers MB-1 and MB-2 are stacked over the element layer DE-2,  $L_{16}$  is larger than  $L_{15}$  in some cases. In that case,  $L_{16}$  can have the minimum value of the design rule for the element layer DE-2. In the case of such a design rule, however, the grid point 16a of the wiring layers MB-1 and MB-2 does not overlap with the grid point 15a of the wiring layers MA-1 and MA-2. This might decrease the efficiency of designing using an automatic placer and router.

[0060]

15

20

Thus, in the case where  $L_{16}$  is larger than  $L_{15}$ ,  $L_{16}$  is set to 1.5 times or 2 times as large as  $L_{15}$ . Here,  $L_{16}$  is twice as large as  $L_{15}$ . With such a design rule, the wiring grid 15 includes the grid point 15a overlapping with the grid point 16a. Thus, enhancing the efficiency of designing using an automatic placer and router is compatible with reducing an area overhead of the semiconductor device 100. Furthermore, also in the case where a circuit composed of a combination of the logic cell 10 and the transistor DE2 is designed, such a design rule contributes to efficient designing.

25 [0061]

30

35

<< Combination of transistor DE2 and logic cell 10>>

The semiconductor device 100 can be provided with a circuit composed of a combination of one or more transistors DE2 and the logic cell 10. In the case where the transistor DE2 is an OS transistor, the off-state current of the OS transistor is extremely low; thus, the logic circuit 10a of the logic cell 10 can have another function or higher performance. FIGS. 4A to 4F each illustrate an example of a circuit composed of a combination of an OS transistor/OS transistors and a logic circuit. Transistors TO1 to TO3 and TO6 to TO8 in FIGS. 4A to 4F are OS transistors.

[0062]

Here, an off-state current refers to a current that flows between a source and a drain

when a transistor is off. In the case of an n-channel transistor, for example, when the threshold voltage of the transistor is approximately 0 V to 2 V, a current flowing between a source and a drain when a voltage between a gate and the source is negative can be referred to as an off-state current. An extremely low off-state current means, for example, that the off-state current per micrometer of channel width is lower than or equal to 100 zA (z represents zepto and denotes a factor of  $10^{-21}$ ). Since the off-state current is preferably as low as possible, the normalized off-state current is preferably lower than or equal to 10 zA/mm or lower than or equal to 1 zA/mm), more preferably lower than or equal to 10 yA/mm (y represents youto and denotes a factor of  $10^{-24}$ ).

10 [0063]

15

20

25

5

An oxide semiconductor has a bandgap of 3.0 eV or higher; thus, an OS transistor has a low leakage current due to thermal excitation and, as described above, an extremely low off-state current. A channel formation region of an OS transistor is preferably formed using an oxide semiconductor containing at least one of indium (In) and zinc (Zn). Typical examples of such an oxide semiconductor include an In-Ga-Zn oxide and an In-Sn-Zn oxide. By reducing impurities serving as electron donors, such as moisture or hydrogen, and also reducing oxygen vacancies, an i-type (intrinsic) or a substantially i-type oxide semiconductor can be obtained. Here, such an oxide semiconductor can be referred to as a highly-purified oxide semiconductor. By using a highly purified oxide semiconductor, the off-state current of the OS transistor that is normalized by channel width can be as low as several yoctoamperes per micrometer to several zeptoamperes per micrometer. An OS transistor and an oxide semiconductor will be described in Embodiments 3 and 4.

[0064]

A circuit 30 in FIG. 4A includes a logic circuit 34 and the transistor TO6. The logic circuit 34 corresponds to the logic circuit 10a of the logic cell 10. The transistor TO6 functions as a power switch for stopping supply of VSS. On/off of the transistor TO6 is controlled by a signal slp.

[0065]

As illustrated in FIGS. 4B and 4C, the transistor TO6 may be provided with a back gate.

In a circuit 30-1 in FIG. 4B, a back gate of a transistor TO7 is electrically connected to a port OBG. The threshold voltage of the transistor TO7 can be controlled by the potential of the port OBG. In the case where a charge storage layer is provided over an insulating layer between the back gate and a channel formation region of the transistor TO7, in fabricating the circuit 30-1, a step of introducing charge into a charge storage layer of the transistor TO7 can be performed with the use of the port OBG. In the case where the step is performed, the circuit 30-1 can be

operated with the back gate of the transistor TO7 brought into an electrically floating state without control of the potential of the port OBG.

[0066]

In a circuit 30-2 in FIG. 4C, a back gate of the transistor TO8 is electrically connected to a gate thereof. Such a device structure can improve the on-state current characteristics of the transistor TO8. Note that the back gate of the transistor TO8 may be electrically connected to a source or a drain thereof.

[0067]

FIGS. 4D to 4F each illustrate an example of a circuit composed of a combination of a logic circuit and a backup circuit using an OS transistor/OS transistors. Providing the circuit for backing up data (state) of the logic circuit enables power gating of a semiconductor device including the logic circuit. The backup circuit described below can retain data for a long time in clock gating and in power gating owing to the extremely low off-state current of the OS transistor/OS transistors.

15 [0068]

A circuit 31 in FIG. 4D includes a logic circuit 35 and a backup circuit 36A. The logic circuit 35 corresponds to the logic circuit 10a of the logic cell 10. The backup circuit 36A includes a node SN1, the transistor TO1, and a capacitor C1. The backup circuit 36A has a configuration similar to that of a DRAM memory cell. The node SN1 is a storage node and brought into an electrically floating state when the transistor TO1 is turned off. The capacitor C1 is a storage capacitor for holding the potential of the node SN1 and is electrically connected to the node SN1 and the port PL. A gate of the transistor TO1 is electrically connected to a port BK. A signal for controlling the backup operation is input to the port BK. When the transistor TO1 is turned on, data of a node N35 is backed up or data held in the node SN1 is written to the node N35. The node N35 is an internal node, an input node, or an output node of the logic circuit 35.

[0069]

30

35

A circuit 32 in FIG. 4E includes the logic circuit 35 and a backup circuit 36B. The backup circuit 36B is different from the backup circuit 36A in that the transistor TO2 is additionally provided. The transistor TO1 and the transistor TO2 are electrically connected in series, and when the transistors TO1 and TO2 are turned off, the node SN1 is brought into an electrically floating state. A gate of the transistor TO2 is electrically connected to a port RE. A signal for controlling the restoration operation is input to the port RE.

[0070]

In the backup operation, the transistor TO1 is turned on, whereby data of the output

node (port Y1) of the logic circuit 35 is written to the node SN1. In the restoration operation, the transistor TO2 is turned on, whereby data of the node SN1 is written to the input node (port A1) of the logic circuit 35. Note that a node of which data is backed up is either the internal node or the output node of the logic circuit 35. Furthermore, a node to which data is restored is either the internal node or the output node of the logic circuit 35.

[0071]

5

10

20

25

30

35

A circuit 33 in FIG. 4F includes the logic circuit 35, a port B1, and a backup circuit 36C. The backup circuit 36C is different from the backup circuit 36B in that the transistor TO3 is additionally provided. The transistor TO3 is a pass transistor that controls the electrical continuity between the port B1 and the port A1. A gate of the transistor TO3 is electrically connected to the port BK.

[0072]

Note that the transistors TO1 to TO3 may be provided with back gates like the transistors TO7 and TO8.

15 [0073]

(Retention time)

Since the transistors TO1 to TO3 are OS transistors, the backup circuits 36A to 36C can retain data for a long time. For example, in the case where a power supply voltage is in the range from 2V to 3.5 V, the storage capacitance of the node SN1 (capacitance of C1) is 21 fF, and the allowable variation in the held potential of the node SN1 is less than 0.5 V in the backup circuit 36A, the leakage current from the node SN1 needs to be less than  $33 \times 10^{-24}$  A so that the variation in the held potential for 10 years at 85 °C is less than the allowable variation. In the case where the leakage current of other components is lower than the above and a leakage current flows almost exclusively in the transistor TO1, the transistor TO1 with a channel width of 350 nm preferably has a leakage current per channel width of lower than  $93 \times 10^{-24}$  A/µm. That is, the use of an OS transistor as the transistor TO1 allows the backup circuit 36A to retain data for 10 years at 85 °C.

[0074]

In storage circuits that utilize the off-state current characteristics of an OS transistor, for example, the backup circuits 36A to 36C, a predetermined potential keeps being supplied to the OS transistor in a retention period in some cases. For example, a potential that completely turns off the OS transistor may keep being supplied to a gate of the OS transistor. Alternatively, a potential that makes the OS transistor in a normally-off state may keep being supplied to a back gate of the OS transistor. In such a case, the voltage is supplied to the storage circuit in the retention period. However, little power is consumed because almost no current flows.

Because of little power consumption, even if a predetermined voltage is applied to the storage circuit, the storage circuit using the OS transistor can be regarded as being substantially nonvolatile.

[0075]

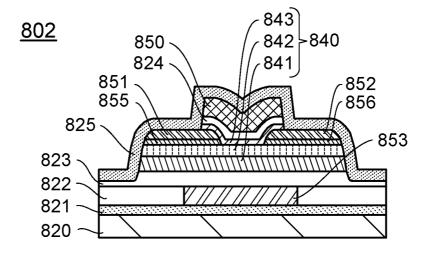

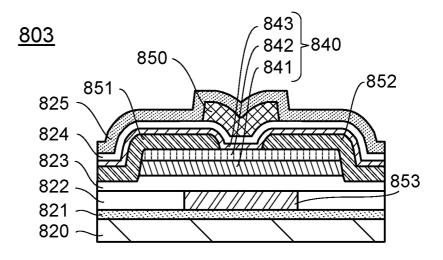

<< Example of layered structure of semiconductor device 100>>

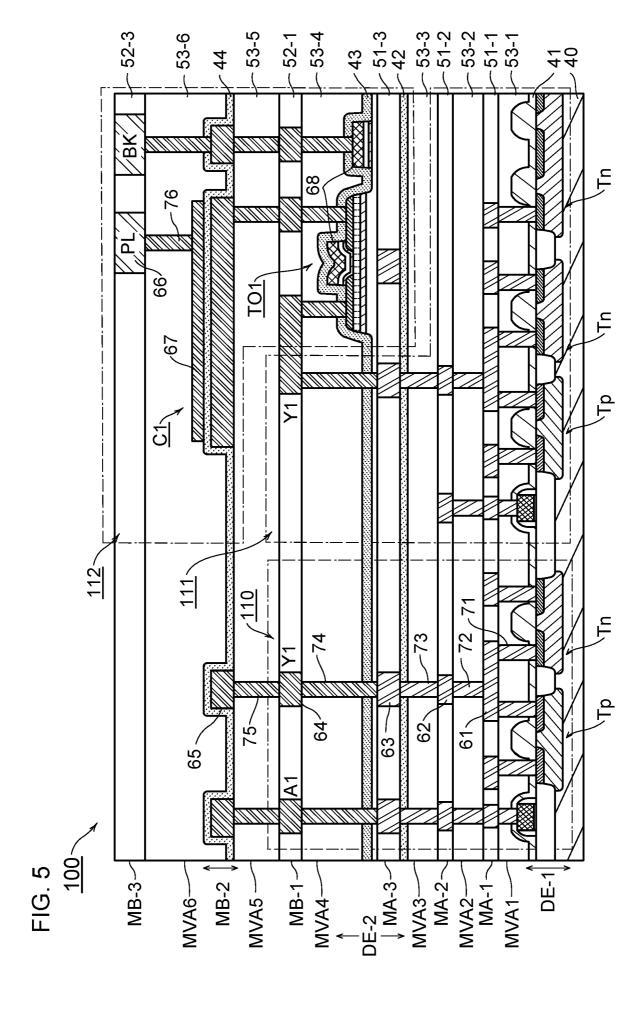

FIG. 5 schematically illustrates a layered structure of the semiconductor device 100. A logic cell 110, a logic cell 111, and a circuit 112 are illustrated in FIG. 5. The circuit 112 is stacked over the logic cell 111. The circuit 112 corresponds to each of the backup circuits illustrated in FIGS. 4C to 4E and is connected to the logic cell 111 so that data in the logic cell 111 can be backed up. The transistor TO1 and the capacitor C1 provided in the circuit 112 are illustrated in FIG. 5.

[0076]

10

15

30

The semiconductor device 100 in FIG. 5 is formed in and over a single crystal silicon wafer 40. A plurality of Si transistors Tp and a plurality of Si transistors Tn are formed in the element layer DE-1. These Si transistors are covered with an insulating layer 41. The logic cell 110 is an inverter cell. The logic cell 111 is a logic circuit in which an output node of an inverter is electrically connected to the port Y1. Here, the Si transistor Tp is a p-channel transistor., and the Si transistor Tn is an n-channel transistor. [0077]

20 In each of layers MVA1 to MVA6, a plug for the connection between a conductor in an upper layer and a conductor in a lower layer is formed. The layers MVA1 to MVA6 include a plurality of plugs 71 to 76 provided in insulating layers 53-1 to 53-6. [0078]

The wiring layers MA-1 and MA-2 include a plurality of wirings 61 and 62 provided in the insulating layers 51-1 and 51-2, respectively. The wiring layers MB-1 to MB-3 include a plurality of wirings 64 to 66, respectively. The wirings 64 and 66 are provided in the insulating layers 52-1 and 52-3, respectively. The wiring 65 is formed over the insulating layer 53-5. The wiring 65 is covered with an insulating layer 44. [0079]

In the circuit 112, a wiring 67 overlapping with the wiring 65 with the insulating layer 44 therebetween is provided, whereby the capacitor C1 is formed. Note that an electrode of the capacitor C1 is not limited to an electrode formed in the wiring layer MB-2. The electrode of the capacitor C1 needs to be formed in any of the wiring layers included in the semiconductor The ports PL and BK are provided in the wiring layer MB-3. A gate (wiring 68)

of the transistor TO1 is connected to the port BK. 35

[0800]

Although an example in which three wiring layers are provided over the element layer DE-2 is described here, this example is not necessarily employed. Two or more wiring layers need to be provided over the element layer DE-2.

5 [0081]

A plurality of OS transistors are formed in the element layer DE-2. The OS transistor is formed over an insulating layer 42 and is covered with an insulating layer 43. The insulating layers 42 and 43 are passivation layers for the OS transistors. In FIG. 5, the transistor TO1 among the OS transistors provided in the element layer DE-2 is illustrated. The transistor TO1 has a device structure similar to that of the OS transistor 800 (FIGS. 14A to 14D) described in Embodiment 3. An OS transistor with a back gate is provided in the element layer DE-2; thus, the element layer DE-2 includes the wiring layer MA-3 provided with the back gate. The wiring layer MA-3 includes a plurality of wirings 63 provided in an insulating layer 51-3.

In FIG. 5, the port A1 and the port Y1 of the logic cell 110 are connected to the wiring 65 through a plug 75. In the case where the wiring layer MA-3 is provided, a wiring for connecting logic circuits composed of the layers (DE-1, MA-1, and MA-2) in the logic cells 110 and 111 to an input port and an output port can also be provided in the wiring layer MA-3.

[0083]

In FIG. 5, the conductor having high heat resistance (e.g., tungsten) is used for the wirings 61 to 63 and the plugs 71 to 73. Meanwhile, for the wirings 64 to 67 and the plugs 74 to 76, which are formed after the element layer DE-2, a conductor having a lower melting point and lower resistivity than the wiring 61 and the like (e.g., Cu or Al) is preferably used.

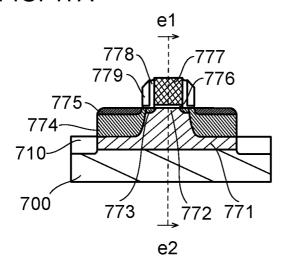

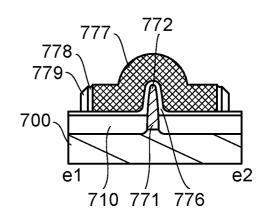

[0084]

The transistors Tp and Tn of the element layer DE-1 are, but not limited to, planar type transistors. The transistor Tp and Tn may have three-dimensional structures (e.g., a FIN-type structure or a Tri-Gate type structure). FIGS. 17A and 17B illustrate an example of a FIN-type transistor. FIG. 17A is a cross-sectional view of the transistor in the channel length direction, and FIG. 17B is a cross-sectional view along e1-e2 in FIG. 17A.

30 [0085]

20

25

35

In the transistor illustrated in FIGS. 17A and 17B, an active layer (also referred to as a channel formation region) 772 has a projected shape, and a gate insulating layer 776 and a gate electrode 777 are provided along the side surfaces and top surface thereof. Reference numeral 710 denotes an element isolation layer. Reference numerals 771, 773, 774 denote a well, a low concentration impurity region, and a high concentration impurity region, respectively.

Reference numeral 775 denotes a conductive region. Reference numerals 778 and 779 denote sidewall insulating layers. Although FIGS. 17A and 17B illustrate the case where a projection is formed by processing a single crystal silicon wafer 700, a semiconductor region with a projected shape can be formed by processing an SOI substrate.

5 [0086]

10

15

25

35

<< Configuration example of processing unit>>

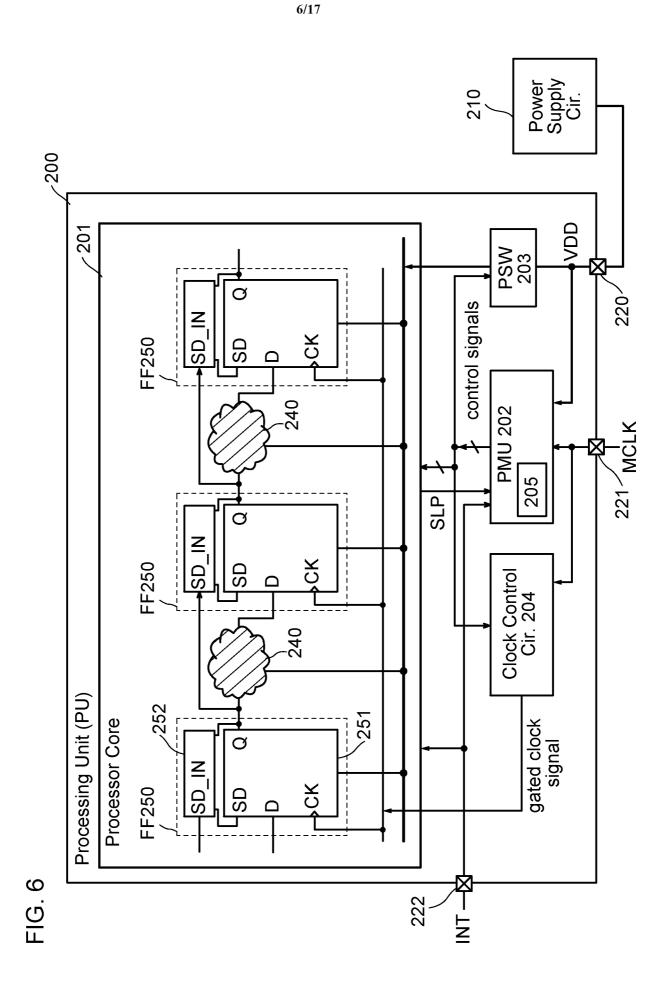

Here, a processing unit will be described as a specific example of a semiconductor device designed using logic cells as elements. A semiconductor device in FIG. 6 includes a processing unit (PU) 200 and a power supply circuit 210. The PU 200 has a function of executing an instruction. The PU 200 includes a plurality of functional circuits integrated on one chip. The PU 200 further includes a processor core 201, a power management unit (PMU) 202, a power switch (PSW) 203, and a clock control circuit 204. FIG. 6 illustrates an example in which the power supply circuit 210 is provided on a chip different from a chip on which the PU 200 is provided. A terminal 220 is a power supply potential terminal, and a power supply potential VDD is input from the power supply circuit 210 to the terminal 220. Terminals 221 and 222 are signal input terminals. A master clock signal MCLK is input to the terminal 221. A signal INT is input to the terminal 222. The signal INT is an interrupt signal for requesting interrupt processing. The signal INT is input to the processor core 201 and the PMU 202 in the PU 200.

20 [0087]

<Processor core>

The processor core 201 is capable of executing an instruction and can also be referred to as an arithmetic processing circuit or a processor (processing unit). The processor core 201 contains a logic cell as a basic element. The processor core 201 includes a logic circuit 240, a flip-flop (FF) 250, and the like, and a variety of functional circuits are formed using these circuits. For example, the logic circuit 240 can be a combinational circuit. The FF 250 is included in a register.

[0088]

The FF 250 includes a scan flip-flop (SFF) 251 and a backup circuit 252. The SFF 251 is composed of a logic cell. The backup circuit 252 is a circuit for backing up data of the SFF 251. That is, the FF 250 can be called a scan flop-flop having a backup function. A port Q of the FF 250 is electrically connected to an input terminal of the logic circuit 240 and is also electrically connected to a port SD\_IN of another FF 250 to form a scan chain. Providing the FF 250 enables clock gating and power gating of the processor core 201; thus, the power consumption of the PU 200 can be reduced.

[0089]

FIG. 7 illustrates a configuration example of the processor core 201. The processor core 201 in FIG. 7 includes a control unit 231, a program counter 232, a pipeline register 233, a pipeline register 234, a register file 235, an arithmetic logic unit (ALU) 236, and a data bus 237. Data is transmitted between the processor core 201 and a peripheral circuit such as the PMU 202 or a cache through the data bus 237. [0090]

The control unit 231 has a function of decoding and executing instructions contained in a program such as input applications by controlling the overall operations of the program counter 232, the pipeline register 233, the pipeline register 234, the register file 235, the ALU 236, and the data bus 237. The ALU 236 has a function of performing a variety of arithmetic operations such as four arithmetic operations and logic operations. The program counter 232 is a register having a function of storing the address of an instruction to be executed next.

The pipeline register 233 has a function of temporarily storing instruction data. The register file 235 includes a plurality of registers including a general-purpose register and can store data read from a main memory, data obtained as a result of arithmetic operations in the ALU 236, or the like. The pipeline register 234 has a function of temporarily storing data used for arithmetic operations performed in the ALU 236, data obtained as a result of arithmetic operations in the ALU 236, or the like.

[0092]

25

30

35

<Circuit configuration example of flip-flop>

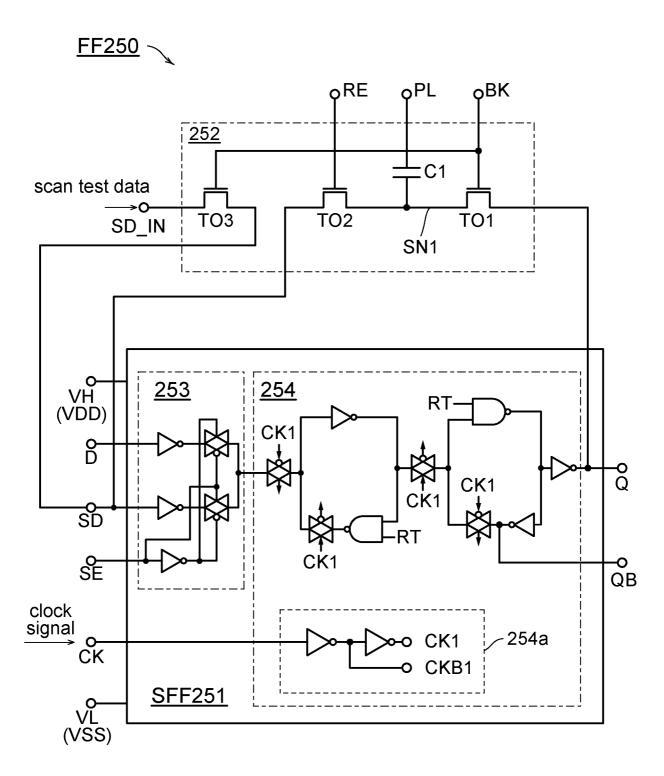

FIG. 8 is a circuit configuration example of the FF 250. The backup circuit 252 in FIG. 8 has a configuration similar to that of the backup circuit 36C. The SFF 251 in FIG. 8 includes a selector (SEL) 253, an FF 254, and ports VH, VL, D, Q, QB, SD, SD\_IN, SE, CK, and RT. [0093]

The port VH is a power supply port for high power supply voltage VDD, and the port VL is a power supply port for low power supply voltage VSS. VDD and VSS are applied to inverters of the SEL 253, and inverters and NAND circuits (hereinafter referred to as NAND) of the FF 254. VDD is input to the port VH through a power switch.

[0094]

The ports D and SD are data input ports of the SFF 251. The port D is electrically connected to a data output port of a logic circuit (e.g., a combinational circuit), and data is input to the port D. Restore data or scan test data is input to the port SD through the backup circuit 252. The port Q is an output port. The port Q is electrically connected to a port SD IN of

another FF 250 and a data input port of the logic circuit. The port QB outputs data whose logic is inverted from the logic of the port Q. The port QB is electrically connected to a data input port of another logic circuit. The port QB is provided as necessary.

[0095]

The ports SE, CK, and RT are input ports for control signals. A scan enable signal is input to the port SE. The port SE is electrically connected to the SEL 253. A clock signal is input to the port CK. The port CK is electrically connected to a circuit 254a. A reset signal is input to the port RT. The port RT is electrically connected to the NAND of the FF 254.

The SEL 253 has a function of selecting one of the ports D and SD in accordance with the logic of the port SE and inputting data of the selected port to the FF 254. When a scan test is performed, the logic of the port SE is set to "H" so that data of the port SD is input to the FF 254. When the FF 250 normally operates, the logic of the port SE is set to "L", and the port D is electrically connected to the input port of the FF 254.

15 [0097]

5

The FF 254 in FIG. 8 includes a master latch circuit and a slave latch circuit. The circuit 254a is a circuit for inputting clock signals, which includes ports CK1 and CKB1. The port CK1 outputs a non-inverted clock signal. The port CKB1 outputs an inverted clock signal. An analog switch of the FF 254 is electrically connected to the ports CK1 and CKB1.

20 [0098]

25

35

<Operation example of scan flip-flop>

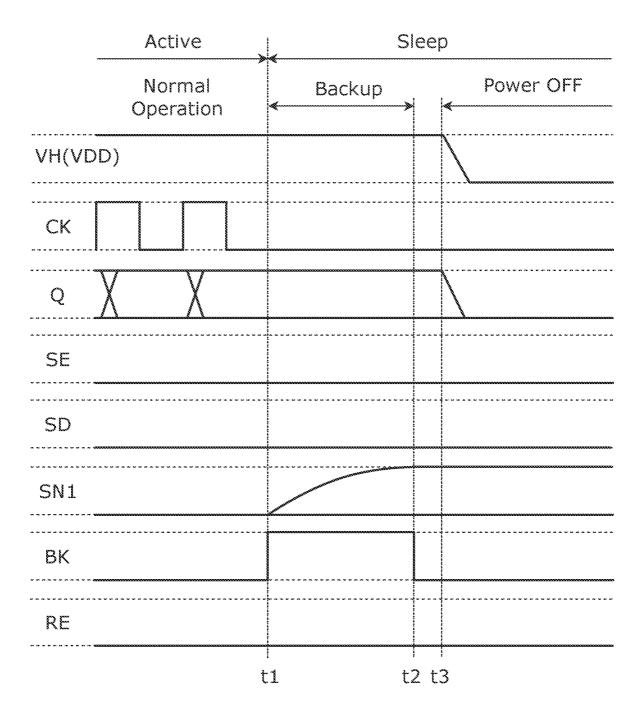

FIG. 9 and FIG. 10 are timing charts each illustrating an operation example of the FF 250. FIG. 9 illustrates an operation example of the FF 250 when the PU 200 is transferred from an active mode to a sleep mode. FIG. 10 illustrates an operation example of the FF 250 when the PU 200 is transferred from the sleep mode to the active mode. FIG. 9 and FIG. 10 illustrate changes in the voltages (logics) of the ports VH, CK, Q, SE, SD, BK, and RE, and the node SN1. VSS is input to the port PL. In FIG. 9 and FIG. 10, the maximum voltage is VDD and the minimum voltage is VSS.

[0099]

30 <Active mode (normal operation mode)>

In the active mode, the FF 250 performs normal operation. The FF 250 functions as a flip-flop that temporarily retains data output from the logic circuit. Here, data output from the logic circuit is input to the port D. In normal operation, the ports RE and BK are at "L" and the transistors TO1 to TO3 are off. The port SE is at "L," and data of the port D is input to the FF 254 by the SEL 253. The port RT is at "H." A clock signal is input to the port CK. In

conjunction with the change of the port CK into "H," the voltage (logic) of the port Q is changed. [0100]

<Scan mode>

In the scan mode, a plurality of SFFs 251 are electrically connected in series to form a scan chain. In the backup circuit 252, the transistors TO1 and TO3 are turned on and the transistor TO2 is turned off. Since the port SE is at "H," data of the port SD is input to the FF 254 by the SEL 253. In other words, in the scan mode, data output from the port Q of the FF 250 is input to the port SD of the FF 250 in the next stage.

[0101]

5

15

10 (Scan test)

In order to perform the scan test, the mode is set to the scan mode, and the scan test data is input to the port SD\_IN of the FF 250 in the first stage of the scan chain. The shift operation of the scan chain is performed by input of a clock signal, and the scan test data is written to each FF 250. Next, the FF 250 performs normal operation to retain data output from the logic circuit 240. The mode is set to the scan mode again to perform the shift operation of the scan chain. Whether the logic circuit 240 and the FF 250 fail to operate properly can be determined from data output from the port Q of the FF 250 in the last stage.

[0102]

(Backup sequence)

Backup sequence is performed by transfer from the active mode to the sleep mode. In the backup sequence, clock gating (clock stop), data backup, and power gating (power-off) are performed. The mode is set to the sleep mode by stopping supply of clocks.

[0103]

In the example of FIG. 9, clock gating of the FF 250 is started at t1, and backup operation is started in the backup circuit 252. Specifically, the port CK is set to "L" and the port BK is set to "H" at t1. A period during which the port BK is at "H" is a backup operation period.

[0104]

When the port BK is set to "H," the transistor TO1 electrically connects the node SN1 to the port Q. Thus, the node SN1 remains at "L" when the port Q is at "0," and the voltage of the node SN1 rises to "H" when the port Q is at "1." In other words, in the period during which the port BK is at "H," the logic of the node SN1 can be the same as the logic of the port Q. The period during which the port BK is at "H" may be determined so that the voltage of the node SN1 rises to a "1" logical level. At t2, the port BK is set to "L" to turn off the transistors TO1 and TO3, so that the node SN1 becomes in an electrically floating state and the backup circuit

252 retains data.

[0105]

At t3, the power is turned off to set the port RT to "L". The voltage of the port VH gradually drops from VDD to VSS. The power may be turned off at t2. Furthermore, the power is turned off as necessary. Depending on the power domain of the PU 200, the sleep mode time, or the like, power required to return from the sleep mode to the active mode might be higher than power that can be reduced by power-off. In that case, the effect of power gating cannot be obtained; thus, in the sleep mode, it is preferable that the power be not turned off and only supply of clock signals be stopped.

10 [0106]

5

(Restore sequence)

In a restore sequence where the mode is transferred from the sleep mode to the active mode, power is turned on, data is restored, and clocks are supplied. The mode is transferred to the active mode by starting supply of clocks.

15 [0107]

20

25

The power is turned on at t4. The voltage of the port VH gradually increases from VSS to VDD. Restoration operation is started after the port VH becomes at VDD. The ports SE and RE are set to "H" at t5. In addition, the port RT is set to "H". Restoration operation is performed while the port RE is at "H". The transistor TO2 is turned on and the node SN1 is connected to the port SD. When the node SN1 is at "L," the port SD remains at "L." When the node SN1 is "H," the voltage of the port SD increases to "H." The port SE is set to "H" at t6. The port SD is electrically connected to the input port of the FF 254 by the SEL 253. In other words, data retained in the node SN1 is written to the port SD.

Note that at t5, the port SE as well as the port RE can be set to "H". As illustrated in FIG. 10, in the case where the node SN1 is at "H," the port SE is preferably set to "H" after the voltage of the port SD rises to the "1" logical level. This driving prevents flow-through current from flowing through the FF 250.

[0109]

After the logic of the port SD becomes the same as the logic of the node SN1, the port CK is at "H" for a certain period (from t7 to t8). In the example of FIG. 10, one clock is input to the port CK. When the port CK is set to "H" at t7, data of the master latch circuit is written to the slave latch. The port Q is set to "0" when the port SD is at "0" at t7, and the port Q is set to "1" when the port SD is at "1". In other words, data of the node SN1 is written to the port Q, and the FF 250 returns to a state immediately before clock gating is performed (i.e., the mode is

set to the sleep mode). The restoration operation is terminated at t9 by setting the ports SE and RE to "L". The port D is electrically connected to the input port of the FF 254 by the SEL 253. In the backup circuit 252, the transistor TO3 is turned off and the node the node SN1 becomes in a floating state.

5 [0110]

After SE and RE are set to "L," the input of a clock signal is restarted at t10 after a lapse of a certain period (e.g., one clock period) to set the FF 250 in the active mode. The FF 250 resumes normal operation.

[0111]

As described above, the FF 250 is capable of backing up and restore data at high speed, and for example, is capable of completing backup operation and restoration operation within several clocks (2 to 5 clocks). In write operation of the backup circuit 252, the node SN1 is charged or discharged by switching operation of the transistors TO1 to TO3. In read operation of the backup circuit 252, the port SD is charged or discharged by switching operation of the transistors TO1 to TO3. Energy required for these operations is as low as energy required for a DRAM cell. There is no need to supply power to the backup circuit 252 for data retention; thus, standby power of the FF 250 can be reduced. Similarly, there is no need to supply power to the backup circuit 252 does not lead to a substantial increase in dynamic power of the FF 250.

20 [0112]

Providing the backup circuit 252 adds parasitic capacitance of the transistor TO1 to the port Q. However, this parasitic capacitance is lower than the parasitic capacitance of a logic circuit connected to the port Q. Consequently, the normal operation of the FF 250 is not influenced, and providing the backup circuit 252 does not lead to a substantial decrease in the performance of the FF 250 in the active mode. In other words, the backup circuit 252 does not influence the operation of the PU 200.

[0113]

25

<Power management>

The PMU 202 has a function of controlling power gating, clock gating, and the like.

Specifically, the PMU 202 is capable of controlling the processor core 201, the PSW 203, and the clock control circuit 204. The PMU 202 has a function of outputting control signals to be input to the ports BK, RE, and SE to the processor core 201.

[0114]

The PMU 202 includes a circuit 205. The circuit 205 is capable of measuring time.

The PMU 202 is capable of performing power management on the basis of data on time obtained

by the circuit 205. For example, when the circuit 205 is a timer circuit, the PMU 202 may generate a timer interrupt request signal. The circuit 205 is provided as necessary.

[0115]

The PSW 203 is capable of controlling supply of VDD to the PU 200 in response to a control signal of the PMU 202. In the example of FIG. 6, the processor core 201 may include a plurality of power domains. In that case, supply of power to the plurality of power domains may be controlled independently by the PSW 203. In addition, the processor core 201 may include a power domain that is not power-gated. In that case, VDD may be applied to this power domain without passing through the PSW 203.

10 [0116]

The clock control circuit 204 has a function of generating and outputting a gated clock signal from the signal MCLK. The clock control circuit 204 is capable of stopping supply of a clock signal to the processor core 201 in response to a control signal of the PMU 202. The power supply circuit 210 may be capable of changing the magnitude of VDD in response to a control signal of the PMU 202.

[0117]

15

A signal SLP is output from the processor core 201 to the PMU 202. The signal SLP is a trigger signal for transferring the processor core 201 to the sleep mode. In the processor core 201, the backup sequence of the FF 250 is executed in response to the signal SLP. When the signal SLP is input to the PMU 202, the PMU 202 outputs a control signal for transition from the active mode to the sleep mode to a functional circuit to be controlled. The PMU 202 controls the clock control circuit 204 and stops supply of a clock signal to the processor core 201. In addition, the PMU 202 controls the PSW 203 and stops supply of power to the processor core 201.

25 [0118]

30

35

Processing for returning the processor core 201 from the sleep mode to the active mode is executed by input of the signal INT. In the processor core 201, the restore sequence of the FF 250 is executed in response to the signal INT. When the signal INT is input to the PMU 202, the PMU 202 outputs a control signal for transition from the sleep mode to the active mode to a functional circuit to be controlled. The PMU 202 controls the PSW 203 and restarts supply of power to the processor core 201. In addition, the PMU 202 controls the clock control circuit 204 and restarts supply of a clock signal to the processor core 201.

The backup sequence may be executed using the signal INT or an interrupt request signal of the PMU 202 as a trigger. Furthermore, the restore sequence may be executed using

the interrupt request signal of the PMU 202 as a trigger.

[0120]

5

<<Device structure of PU 200 (FF 250)>>

The PU 200 is a device having a layered structure similar to that of the semiconductor device 100 in FIG. 5. FIG. 11 is a schematic diagram illustrating the device structure of the FF 250. The SFF 251 is composed of a logic cell. Transistors of the SFF 251 are provided in the element layer DE-1 and are connected through wirings of the wiring layer MA-1. The ports SD and Q are provided in the wiring layer MB-1 and are connected to the SFF 251 through wirings of the wiring layer MA-2. The same applies to the ports SD\_IN and D. The transistors TO1 to TO3 of the backup circuit 252 are provided in the element layer DE-2. One of a pair of electrodes of the capacitor C1 is provided in the wiring layer MB-2.

[0121]

The number of elements in the backup circuit 252 is much smaller than the number of elements in the SFF 251; thus, there is no need to change the circuit configuration of the logic cell composing the SFF 251 in order to stack the backup circuit 252. In other words, the backup circuit 252 is a backup circuit that has very broad utility. Furthermore, the PU 200 can be designed efficiently.

[0122]

15

The backup circuit 252 consumes almost no power in normal operation and requires significantly low power for backup operation and restoration operation. Thus, the FF 250 provided with the backup circuit 252 is highly suitable for normally-off computing. Even when the FF 250 is included, the dynamic power of the PU 200 can hardly be increased and the performance of the PU 200 can hardly be decreased. Thus, the PU 200 including the FF 250 can reduce power consumption effectively by power gating while keeping the performance.

25 [0123]

35

(Embodiment 2)

In this embodiment, an electronic component and electronic devices and the like including the electronic component will be described as examples of semiconductor devices.

[0124]

30 <Electronic component>

FIG. 12A is a flow chart showing an example of a method for fabricating an electronic component. The electronic component is also referred to as a semiconductor package or an IC package. This electronic component has a plurality of standards and names depending on a terminal extraction direction and a terminal shape. Examples of the electronic component will be described in this embodiment.

[0125]

5

15

20

25

30

35

A semiconductor device including a transistor is completed using detachable components integrated on a printed wiring board through an assembly process (post-process). The post-process can be finished through steps in FIG. 12A. Specifically, after an element substrate obtained in the preceding process is completed (Step S1), a dicing step for separating the substrate into a plurality of chips is performed (Step S2). The rear surface of the substrate is ground before Step S2. The substrate is thinned in this step to reduce warpage or the like of the substrate in the preceding process and to reduce the size of the component. [0126]

10 The divided chips are separately picked up to be mounted on and bonded to a lead frame in a die bonding step (Step S3). In the die bonding step, the chip is bonded to the lead frame by an appropriate method depending on a product, for example, bonding with a resin or a tape. the die bonding step, the chip may be mounted on an interposer to be bonded. In a wire bonding step, lead of the lead frame is electrically connected to an electrode on the chip with a metal fine line (wire) (Step S4). A silver line or a gold line can be used as the metal fine line. Either ball bonding or wedge bonding can be used as wire bonding.

[0127] A molding step is performed to seal the wire bonded chip with an epoxy resin or the like

(Step S5). With the molding step, the electronic component is filled with the resin. The lead of the lead frame is plated. After that, the lead is cut and processed (Step S6). This plating process prevents rust of the lead and facilitates soldering at the time of mounting the chip on a printed wiring board in a later step. Printing (marking) is performed on a surface of the Through an inspection step (Step S8), the electronic component is package (Step S7). completed (Step S9). When the electronic component includes the semiconductor device described in the above embodiment, low power consumption and reduction in size of the electronic component can be achieved.

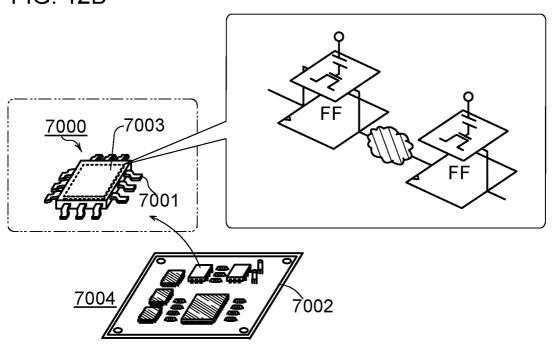

[0128]

FIG. 12B is a schematic perspective view of the completed electronic component. FIG. 12B is a schematic perspective view illustrating a quad flat package (QFP) as an example of the electronic component. As illustrated in FIG. 12B, an electronic component 7000 includes a lead 7001 and a circuit portion 7003. In the circuit portion 7003, various logic circuits such as the FFs described in Embodiment 1 are formed using a plurality of logic cells and the transistors DE2 of the element layer DE-2. The electronic component 7000 is mounted on a printed wiring board 7002, for example. When a plurality of electronic components 7000 are used in combination and electrically connected to each other over the printed wiring board 7002, the

electronic components 7000 can be mounted on an electronic device. A completed circuit board 7004 is provided in the electronic device or the like. The electronic component 7000 can be used as, for example, a random access memory that stores data or a processing unit that executes a variety of processings, such as a CPU, a microcontroller unit (MCU), an FPGA, or a wireless IC. When an electronic device includes the electronic component 7000, the power consumption of the electronic device can be reduced. Alternatively, the electronic device can easily have a smaller size.

[0129]

5

10

15

20

25

The electronic component 7000 can be used as an electronic component (IC chip) of electronic devices in a wide variety of fields, such as digital signal processing, software-defined radio systems, avionic systems (electronic devices used in aircraft, such as communication systems, navigation systems, autopilot systems, and flight management systems), ASIC prototyping, medical image processing, voice recognition, encryption, bioinformatics, emulators for mechanical systems, and radio telescopes in radio astronomy. Examples of such an electronic device include display devices, personal computers (PC), image reproducing devices provided with recording media (devices which reproduce the content of recording media such as DVDs, Blu-ray discs, flash memories, and HDDs, and a device which includes a display portion for displaying images), cellular phones, game machines including portable game machines, portable data terminals, e-book readers, cameras (e.g., video cameras and digital still cameras), wearable display devices (e.g., head mounted display devices, goggle-type display devices, glasses-type display devices, armband display devices, bracelet-type display devices, and necklace-type display devices), navigation systems, audio reproducing devices (e.g., car audio systems and digital audio players), copiers, facsimiles, printers, multifunction printers, automated teller machines (ATMs), and vending machines. FIGS. 13A to 13F illustrate specific examples of such electronic devices.

[0130]

A portable game machine 900 in FIG. 13A includes a housing 901, a housing 902, a display portion 903, a display portion 904, a microphone 905, a speaker 906, an operation key 907, a stylus 908, and the like.

30 [0131]

35

A portable information terminal 910 in FIG. 13B includes a housing 911, a housing 912, a display portion 913, a display portion 914, a joint 915, an operation key 916, and the like. The display portion 913 is provided in the housing 911, and the display portion 914 is provided in the housing 912. The housings 911 and 912 are connected to each other with the joint 915, and an angle between the housings 911 and 912 can be changed with the joint 915. An image

displayed on the display portion 913 may be switched in accordance with the angle between the housings 911 and 912 at the joint 915. A display device with a touch panel may be used as the display portion 913 and/or the display portion 914.

[0132]

5

A laptop 920 in FIG. 13C includes a housing 921, a display portion 922, a keyboard 923, a pointing device 924, and the like.

[0133]

An electric refrigerator-freezer 930 in FIG. 13D includes a housing 931, a refrigerator door 932, a freezer door 933, and the like.

10 [0134]

15

A video camera 940 in FIG. 13E includes a housing 941, a housing 942, a display portion 943, operation keys 944, a lens 945, a joint 946, and the like. The operation keys 944 and the lens 945 are provided in the housing 941, and the display portion 943 is provided in the housing 942. The housings 941 and 942 are connected to each other with the joint 946, and an angle between the housings 941 and 942 can be changed with the joint 946. The direction of an image displayed on the display portion 943 may be changed and display and non-display of an image may be switched in accordance with the angle between the housings 941 and 942, for example.

[0135]

A motor vehicle 950 in FIG. 13F includes a car body 951, wheels 952, a dashboard 953, lights 954, and the like.

[0136]

(Embodiment 3)

In this embodiment, an OS transistor and a semiconductor device including an OS transistor will be described.

[0137]

<< Structural Example 1 of OS transistor>>

FIGS. 14A to 14D illustrate a structural example of an OS transistor. FIG. 14A is a top view illustrating a structural example of an OS transistor. FIG. 14B is a cross-sectional view along y1-y2, FIG. 14C is a cross-sectional view along x1-x2, and FIG. 14D is a cross-sectional view along x3-x4. Here, in some cases, the direction of the line y1-y2 is referred to as the channel length direction, and the direction of the line x1-x2 is referred to as the channel width direction. Note that to clarify the device structure, some components are not illustrated in FIG. 14A.

35 [0138]

An OS transistor 800 illustrated in FIGS. 14A to 14D includes a back gate. The OS transistor 800 is formed over an insulating surface, here, over an insulating layer 821. The insulating layer 821 is formed over a surface of the substrate 820. The insulating layer 821 has a function as a base layer of the OS transistor 800. The OS transistor 800 is covered with an insulating layer 825. Note that the insulating layers 821 and 825 can be regarded as components of the OS transistor 800. The OS transistor 800 includes an insulating layer 822, an insulating layer 823, an insulating layer 824, semiconductor layers 841 to 843, a conductive layer 850, a conductive layer 851, a conductive layer 852, and a conductive layer 853. Here, the semiconductor layers 841 to 843 are collectively referred to as a semiconductor region 840.

10 [0139]

5

The conductive layer 850 functions as a gate electrode, and the conductive layer 853 functions as a back gate electrode. The conductive layers 851 and 852 function as a source electrode and a drain electrode. The insulating layer 821 has a function of electrically isolating the substrate 820 from the conductive layer 853. The insulating layer 824 serves as a gate insulating layer, and the insulating layer 823 serves as a gate insulating layer on the backchannel side.

[0140]

15

20

30

35