## (19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第4698998号 (P4698998)

(45) 発行日 平成23年6月8日(2011.6.8)

(24) 登録日 平成23年3月11日(2011.3.11)

| (51) Int.Cl. | F 1                   | ı         |          |             |          |        |

|--------------|-----------------------|-----------|----------|-------------|----------|--------|

| GO2F 1/136   |                       | GO2F      | 1/1368   |             |          |        |

| GO2F 1/134   |                       | GO2F      | 1/1343   |             |          |        |

| GO2F 1/134   | 5 (2006.01)           | GO2F      | 1/1345   |             |          |        |

| HO1L 21/20   | (2006.01)             | HO1L      | 21/20    |             |          |        |

| HO1L 21/322  | (2006.01)             | HO1L      | 21/322   | G           |          |        |

|              |                       |           |          | 請求項の数 12    | (全 59 頁) | 最終頁に続く |

| (21) 出願番号    | 特願2004-289069 (P2004- | 289069)   | (73) 特許権 | 者 000153878 |          |        |

| (22) 出願日     | 平成16年9月30日 (2004.9    | . 30)     |          | 株式会社半導体     | 本エネルギー研  | 究所     |

| (65) 公開番号    | 特開2006-106118 (P2006- | ·106118A) |          | 神奈川県厚木市     | 5長谷398番  | :地     |

| (43) 公開日     | 平成18年4月20日 (2006.4    | . 20)     | (74) 代理人 | 100116159   |          |        |

| 審査請求日        | 平成19年9月20日 (2007.9    | 0. 20)    |          | 弁理士 玉城      | 信一       |        |

|              |                       |           | (72) 発明者 | 山崎 舜平       |          |        |

|              |                       |           |          | 神奈川県厚木市     | 5長谷398番  | 地 株式会社 |

|              |                       |           |          | 半導体エネルコ     | ドー研究所内   |        |

|              |                       |           | (72)発明者  |             |          |        |

|              |                       |           |          | 神奈川県厚木市     |          | 地 株式会社 |

|              |                       |           |          | 半導体エネルギ     | ドー研究所内   |        |

|              |                       |           | <br> 審査官 | 奥田 雄介       |          |        |

|              |                       |           |          | 天山 海川       |          |        |

|              |                       |           |          |             |          |        |

|              |                       |           |          |             | 終頁に続く    |        |

(54) 【発明の名称】液晶表示装置の作製方法

# (57)【特許請求の範囲】

# 【請求項1】

絶縁表面上に導電層を形成し、

前記導電層上にレジストを形成し、

前記レジストをレーザ光で露光してパターニングし、マスクを形成し、

前記マスクを用いて前記導電層をパターニングし、ゲート電極層及び画素電極層を形成し、

前記ゲート電極層及び前記画素電極層上にゲート絶縁層を形成し、

前記ゲート絶縁層上に半導体の結晶化を助長する金属元素を含む金属膜を形成し、

前記金属膜上に半導体層を形成し、

前記半導体層に接して一導電型を有する半導体層を形成し、

前記半導体層及び前記一導電型を有する半導体層を加熱<u>することにより、前記半導体層</u> を結晶化するとともに、前記半導体層の結晶化を助長する前記金属元素を、前記一導電型 を有する半導体層に移動して低減または除去し、

前記一導電型を有する半導体層上に、導電性材料を含む組成物を吐出して選択的にソース電極層及びドレイン電極層を形成し、

前記一導電型を有する半導体層をパターニングし、ソース領域及びドレイン領域を形成し、

前記ソース電極層、前記ドレイン電極層及び前記ゲート絶縁層上に絶縁層を形成し、 前記絶縁層に前記ソース電極層または前記ドレイン電極層に達する第1の開口部、及び

前記絶縁層と前記ゲート絶縁層に前記画素電極層に達する第2の開口部を形成し、

前記第1の開口部及び前記第2の開口部に、前記ソース電極層または前記ドレイン電極 層及び前記画素電極層を電気的に接続する配線層を形成することを特徴とする液晶表示装 置の作製方法。

## 【請求項2】

絶縁表面上に導電層を形成し、

前記導電層上にレジストを形成し、

前記レジストをレーザ光で露光してパターニングし、マスクを形成し、

前記マスクを用いて前記導電層をパターニングし、ゲート電極層及び画素電極層を形成

前記ゲート電極層及び前記画素電極層上にゲート絶縁層を形成し、

前記ゲート絶縁層上に半導体層を形成し、

前記半導体層に半導体の結晶化を助長する金属元素を含む金属膜を形成し、

前記金属膜に接して一導電型を有する半導体層を形成し、

前記半導体層及び前記一導電型を有する半導体層を加熱することにより、前記半導体層 を結晶化するとともに、前記半導体層の結晶化を助長する前記金属元素を、前記一導電型 を有する半導体層に移動して低減または除去し、

前記一導電型を有する半導体層上に導電性材料を含む組成物を吐出して選択的にソース 電極層及びドレイン電極層を形成し、

前記一導電型を有する半導体層をパターニングし、ソース領域及びドレイン領域を形成

前記ソース電極層、前記ドレイン電極層及び前記ゲート絶縁層上に絶縁層を形成し、

前記絶縁層に前記ソース電極層または前記ドレイン電極層に達する第1の開口部、及び 前記絶縁層と前記ゲート絶縁層に前記画素電極層に達する第2の開口部を形成し、

前記第1の開口部及び前記第2の開口部に、前記ソース電極層または前記ドレイン電極 層及び前記画素電極層を電気的に接続する配線層を形成することを特徴とする液晶表示装 置の作製方法。

### 【請求項3】

絶縁表面上に導電層を形成し、

前記導電層上にレジストを形成し、

前記レジストをレーザ光で露光してパターニングし、マスクを形成し、

前記マスクを用いて前記導電層をパターニングし、ゲート電極層及び画素電極層を形成

前記ゲート電極層及び前記画素電極層上にゲート絶縁層を形成し、

前記ゲート絶縁層上に半導体の結晶化を助長する金属元素を含む金属膜を形成し、

前記金属膜上に半導体層を形成し、

前記半導体層上に選択的にチャネル保護層を形成し、

前記半導体層及び前記チャネル保護層に接して一導電型を有する半導体層を形成し、

前記半導体層、前記チャネル保護層、及び前記一導電型を有する半導体層を加熱するこ とにより、前記半導体層を結晶化するとともに、前記半導体層の結晶化を助長する前記金 属元素を、前記一導電型を有する半導体層に移動して低減または除去し、

前記一導電型を有する半導体層上に、導電性材料を含む組成物を吐出して選択的にソー ス電極層及びドレイン電極層を形成し、

前記一導電型を有する半導体層をパターニングし、ソース領域及びドレイン領域を形成

前記ソース電極層、前記ドレイン電極層及び前記ゲート絶縁層上に絶縁層を形成し、

前記絶縁層に前記ソース電極層または前記ドレイン電極層に達する第1の開口部、及び 前記絶縁層と前記ゲート絶縁層に前記画素電極層に達する第2の開口部を形成し、

前記第1の開口部及び前記第2の開口部に、前記ソース電極層または前記ドレイン電極 層及び前記画素電極層を電気的に接続する配線層を形成することを特徴とする液晶表示装 10

20

30

40

### 置の作製方法。

## 【請求項4】

絶縁表面上に導電層を形成し、

前記導電層上にレジストを形成し、

前記レジストをレーザ光で露光してパターニングし、マスクを形成し、

前記マスクを用いて前記導電層をパターニングし、ゲート電極層及び画素電極層を形成 し、

前記ゲート電極層及び前記画素電極層上にゲート絶縁層を形成し、

前記ゲート絶縁層上に半導体層を形成し、

前記半導体層上に半導体の結晶化を助長する金属元素を含む金属膜を形成し、

前記金属膜上に選択的にチャネル保護層を形成し、

前記金属膜及び前記チャネル保護層に接して一導電型を有する半導体層を形成し、

前記半導体層、前記チャネル保護層、及び前記一導電型を有する半導体層を加熱<u>することにより、前記半導体層を結晶化するとともに、前記半導体層の結晶化を助長する前記金</u>属元素を、前記一導電型を有する半導体層に移動して低減または除去し、

前記一導電型を有する半導体層上に、導電性材料を含む組成物を吐出して選択的にソース電極層及びドレイン電極層を形成し、

前記一導電型を有する半導体層をパターニングし、ソース領域及びドレイン領域を形成し、

前記ソース電極層、前記ドレイン電極層及び前記ゲート絶縁層上に絶縁層を形成し、 前記絶縁層に前記ソース電極層または前記ドレイン電極層に達する第1の開口部、及び 前記絶縁層と前記ゲート絶縁層に前記画素電極層に達する第2の開口部を形成し、

前記第1の開口部及び前記第2の開口部に、前記ソース電極層または前記ドレイン電極層及び前記画素電極層を電気的に接続する配線層を形成することを特徴とする液晶表示装置の作製方法。

### 【請求項5】

絶縁表面上に、ゲート電極層及び画素電極層を形成し、

前記ゲート電極層及び前記画素電極層上にゲート絶縁層を形成し、

前記ゲート絶縁層上に半導体の結晶化を助長する金属元素を含む金属膜を形成し、

前記金属膜上に半導体層を形成し、

前記半導体層に接して一導電型を有する半導体層を形成し、

前記半導体層及び前記一導電型を有する半導体層を加熱<u>することにより、前記半導体層</u> を結晶化するとともに、前記半導体層の結晶化を助長する前記金属元素を、前記一導電型 を有する半導体層に移動して低減または除去し、

前記一導電型を有する半導体層上に導電性材料を含む組成物を吐出して選択的に導電層を形成し、

前記導電層上にレジストを形成し、

前記レジストをレーザ光で露光してパターニングし、マスクを形成し、

前記マスクを用いて前記導電層及び前記一導電型を有する半導体層をパターニングし、 ソース電極層、ドレイン電極層、ソース領域及びドレイン領域を形成し、

前記ソース電極層、前記ドレイン電極層及び前記ゲート絶縁層上に絶縁層を形成し、

前記絶縁層に前記ソース電極層または前記ドレイン電極層に達する第1の開口部、及び前記絶縁層と前記ゲート絶縁層に前記画素電極層に達する第2の開口部を形成し、

前記第1の開口部及び前記第2の開口部に、前記ソース電極層または前記ドレイン電極層及び前記画素電極層を電気的に接続する配線層を形成することを特徴とする液晶表示装置の作製方法。

### 【請求項6】

絶縁表面上に、ゲート電極層及び画素電極層を形成し、

前記ゲート電極層及び前記画素電極層上にゲート絶縁層を形成し、

前記ゲート絶縁層上に半導体層を形成し、

10

20

30

40

前記半導体層に半導体の結晶化を助長する金属元素を含む金属膜を形成し、

前記金属膜に接して一導電型を有する半導体層を形成し、

前記半導体層及び前記一導電型を有する半導体層を加熱<u>することにより、前記半導体層</u> を結晶化するとともに、前記半導体層の結晶化を助長する前記金属元素を、前記一導電型 を有する半導体層に移動して低減または除去し、

前記一導電型を有する半導体層上に導電性材料を含む組成物を吐出して選択的に導電層を形成し、

前記導電層上にレジストを形成し、

前記レジストをレーザ光で露光してパターニングし、マスクを形成し、

前記マスクを用いて前記導電層及び前記一導電型を有する半導体層をパターニングし、 ソース電極層、ドレイン電極層、ソース領域及びドレイン領域を形成し、

前記ソース電極層、前記ドレイン電極層及び前記ゲート絶縁層上に絶縁層を形成し、

前記絶縁層に前記ソース電極層または前記ドレイン電極層に達する第1の開口部、及び前記絶縁層と前記ゲート絶縁層に前記画素電極層に達する第2の開口部を形成し、

前記第1の開口部及び前記第2の開口部に、前記ソース電極層または前記ドレイン電極層及び前記画素電極層を電気的に接続する配線層を形成することを特徴とする液晶表示装置の作製方法。

## 【請求項7】

絶縁表面上に、ゲート電極層及び画素電極層を形成し、

前記ゲート電極層及び前記画素電極層上にゲート絶縁層を形成し、

前記ゲート絶縁層上に半導体の結晶化を助長する金属元素を含む金属膜を形成し、

前記金属膜上に半導体層を形成し、

前記半導体層上に選択的にチャネル保護層を形成し、

前記半導体層及び前記チャネル保護層に接して一導電型を有する半導体層を形成し、

前記半導体層、前記チャネル保護層、及び前記一導電型を有する半導体層を加熱<u>することにより、前記半導体層を結晶化するとともに、前記半導体層の結晶化を助長する前記金</u>属元素を、前記一導電型を有する半導体層に移動して低減または除去し、

前記一導電型を有する半導体層上に導電性材料を含む組成物を吐出して選択的に導電層を形成し、

前記導電層上にレジストを形成し、

前記レジストをレーザ光で露光してパターニングし、マスクを形成し、

前記マスクを用いて前記導電層及び前記一導電型を有する半導体層をパターニングし、 ソース電極層、ドレイン電極層、ソース領域及びドレイン領域を形成し、

前記ソース電極層、前記ドレイン電極層及び前記ゲート絶縁層上に絶縁層を形成し、

前記絶縁層に前記ソース電極層または前記ドレイン電極層に達する第1の開口部、及び前記絶縁層と前記ゲート絶縁層に前記画素電極層に達する第2の開口部を形成し、

前記第1の開口部及び前記第2の開口部に、前記ソース電極層または前記ドレイン電極層及び前記画素電極層を電気的に接続する配線層を形成することを特徴とする液晶表示装置の作製方法。

### 【請求項8】

絶縁表面上に、ゲート電極層及び画素電極層を形成し、

前記ゲート電極層及び前記画素電極層上にゲート絶縁層を形成し、

前記ゲート絶縁層上に半導体層を形成し、

前記半導体層上に半導体の結晶化を助長する金属元素を含む金属膜を形成し、

前記金属膜上に選択的にチャネル保護層を形成し、

前記金属膜及び前記チャネル保護層に接して一導電型を有する半導体層を形成し、

前記半導体層、前記チャネル保護層、及び前記一導電型を有する半導体層を加熱<u>することにより、前記半導体層を結晶化するとともに、前記半導体層の結晶化を助長する前記金</u>属元素を、前記一導電型を有する半導体層に移動して低減または除去し、

前記一導電型を有する半導体層上に導電性材料を含む組成物を吐出して選択的に導電層

20

10

30

30

40

### を形成し、

前記導電層上にレジストを形成し、

前記レジストをレーザ光で露光してパターニングし、マスクを形成し、

前記マスクを用いて前記導電層及び前記一導電型を有する半導体層をパターニングし、 ソース電極層、ドレイン電極層、ソース領域及びドレイン領域を形成し、

前記ソース電極層、前記ドレイン電極層及び前記ゲート絶縁層上に絶縁層を形成し、

前記絶縁層に前記ソース電極層または前記ドレイン電極層に達する第1の開口部、及び前記絶縁層と前記ゲート絶縁層に前記画素電極層に達する第2の開口部を形成し、

前記第1の開口部及び前記第2の開口部に、前記ソース電極層または前記ドレイン電極層及び前記画素電極層を電気的に接続する配線層を形成することを特徴とする液晶表示装置の作製方法。

### 【請求項9】

請求項1乃至8のいずれか一項において、前記絶縁層は、絶縁性材料を含む組成物を吐出して選択的に形成することを特徴とする液晶表示装置の作製方法。

### 【請求項10】

請求項1乃至9のいずれか一項において、前記金属元素として鉄、ニッケル、コバルト、ルテニウム、ロジウム、パラジウム、オスニウム、イリジウム、白金、チタン、銅及び金から選ばれた一つ又は複数を用いることを特徴とする液晶表示装置の作製方法。

#### 【請求項11】

請求項1乃至請求項10のいずれか一項において、前記ゲート絶縁層として、前記ゲート電極層及び前記画素電極層上に第1のゲート絶縁層を形成し、

前記第1のゲート絶縁層上に第2のゲート絶縁層を形成し、

前記第2のゲート絶縁層上に膜厚0.1nm以上10nm以下の第3のゲート絶縁層を 形成することを特徴とする液晶表示装置の作製方法。

### 【請求項12】

請求項11において、前記第1のゲート絶縁層として窒化酸化珪素膜を形成し、前記第 2のゲート絶縁層として酸化窒化珪素膜を形成し、前記第3のゲート絶縁層として窒化珪 素膜を形成することを特徴とする液晶表示装置の作製方法。

## 【発明の詳細な説明】

## 【技術分野】

[0001]

本発明は、液晶表示装置の作製方法に関する。

### 【背景技術】

## [0002]

近年、液晶ディスプレイ(LCD)に代表されるフラットパネルディスプレイ(FPD)は、これまでのCRTに替わる表示装置として注目を集めている。特にアクティブマトリクス駆動の大型液晶パネルを搭載した大画面液晶テレビジョン装置の開発は、液晶パネルメーカーにとって注力すべき重要な課題になっている。

# [0003]

従来の液晶表示装置において、各画素を駆動する半導体素子としてはアモルファスシ リコンを用いた薄膜トランジスタ(以下、TFTとも示す。)が用いられている。

### [0004]

一方、従来の液晶テレビにおいては、視野角特性の限界、液晶材料等が原因の高速動作の限界による画像のぼやけが欠点であったが、近年それを解消する新たな表示モードとして、OCB(optically compensated bend)モードが提案されている(非特許文献1)。

### [0005]

【非特許文献 1 】長広恭明他編、「日経マイクロデバイス別冊 フラットパネル・ディスプレイ 2 0 0 2 」、日系 B P 社、 2 0 0 1 年 1 0 月、 P 1 0 2 - 1 0 9

# 【発明の開示】

40

10

20

30

### 【発明が解決しようとする課題】

## [0006]

しかしながら、非晶質半導体膜を用いたTFTを直流駆動した場合は、しきい値がずれやすく、それに伴いTFTの特性バラツキが生じやすい。このため、非晶質半導体膜を用いたTFTを画素のスイッチングに用いた表示装置は、輝度ムラが発生する。このような現象は、対角30インチ以上(典型的には40インチ以上)の大画面テレビジョン装置であるほど顕著であり、画質の低下が深刻な問題である。

### [0007]

一方、LCDの画質を向上させるために高速動作が可能なスイッチング素子が必要とされている。しかしながら、非晶質半導体膜を用いたTFTでは限界がある。例えば、OCBモードの液晶表示装置を実現することが困難となる。

[0008]

本発明は、このような状況に鑑みなされたものであり、少ないフォトマスク数で、しきい値のずれが生じにくく、高速動作が可能なTFTを有する液晶表示装置の作製方法を提供する。また、スイッチング特性が高く、コントラストがすぐれた表示が可能な液晶表示装置の作製方法を提供する。

【課題を解決するための手段】

[0009]

上述した従来技術の課題を解決するために、本発明においては以下の手段を講じる。

[0010]

本発明は、非晶質半導体膜に触媒元素を添加し加熱して、結晶性半導体膜を形成するとともに該結晶性半導体膜から触媒元素を除去した後、逆スタガ型薄膜トランジスタを作製する。また本発明は、薄膜トランジスタのゲート電極層と画素電極層を同工程同材料を用いて形成し、工程の簡略化と、材料のロスの軽減を達成する。

### [0011]

非晶質半導体膜に、結晶化を促進又は助長させる元素(以下、主に金属元素を指すことから金属元素、触媒元素ともいう)を添加し、該結晶性半導体膜に15族元素を有する半導体膜または希ガス元素を有する半導体膜

を形成し加熱して、結晶性半導体膜を形成するとともに金属元素を結晶性半導体膜から除去した後、逆スタガ型薄膜トランジスタを形成することを要旨とする。なお、該結晶性半 導体膜に15族元素を有する半導体膜を形

成した場合、15族元素を有する半導体膜をソース領域及びドレ

イン領域として用いて、nチャネル型薄膜トランジスタを形成する。また、n型を付与する不純物元素として15族元素を有する半導体膜にp

型を付与する不純物元素として13族元素を添加して、pチャネ

ル型薄膜トランジスタを形成する。さらには、希ガス元素を有する半導体膜を形成した場合、加熱の後に希ガス元素を有する半導体膜を除去し、ソース領域及びドレイン領域を形成して、nチャネル型薄膜トランジスタ又はpチャネル型薄膜トランジスタを形成する。

## [0012]

本発明の液晶表示装置の作製方法の一は、絶縁表面上に導電層を形成し、前記導電層上にレジストを形成し、前記レジストをレーザ光で露光してパターニングし、マスクを形成し、前記マスクを用いて前記導電層をパターニングし、ゲート電極層及び画素電極層を形成し、前記ゲート電極層及び前記画素電極層上にゲート絶縁層を形成し、前記ゲート絶縁層を形成し、前記半導体層に接して一導電型を有する半導体層を形成し、前記半導体層をが成し、前記半導体層を加熱することにより、前記半導体層を結晶化するとともに、前記半導体層の結晶化を助長する前記金属元素を、前記一導電型を有する半導体層に移動して低減または除去し、前記一導電型を有する半導体層上に、導電性材料を含む組成物を吐出して選択的にソース電極層及びドレイン領域を形成し、前記ソース電極層

10

20

30

40

20

30

40

50

、前記ドレイン電極層及び前記ゲート絶縁層上に絶縁層を形成し、前記絶縁層に前記ソース電極層または前記ドレイン電極層に達する第1の開口部、及び前記絶縁層と前記ゲート 絶縁層に前記画素電極層に達する第2の開口部を形成し、前記第1の開口部及び前記第2 の開口部に、前記ソース電極層または前記ドレイン電極層及び前記画素電極層を電気的に 接続する配線層を形成する。

### [0013]

本発明の液晶表示装置の作製方法の一は、絶縁表面上に導電層を形成し、前記導電層上 にレジストを形成し、前記レジストをレーザ光で露光してパターニングし、マスクを形成 し、前記マスクを用いて前記導電層をパターニングし、ゲート電極層及び画素電極層を形 成し、前記ゲート電極層及び前記画素電極層上にゲート絶縁層を形成し、前記ゲート絶縁 層上に半導体層を形成し、前記半導体層に半導体の結晶化を助長する金属元素を含む金属 膜を形成し、前記金属膜に接して一導電型を有する半導体層を形成し、前記半導体層及び 前記一導電型を有する半導体層を加熱することにより、前記半導体層を結晶化するととも に、前記半導体層の結晶化を助長する前記金属元素を、前記一導電型を有する半導体層に 移動して低減または除去し、前記一導電型を有する半導体層上に導電性材料を含む組成物 を吐出して選択的にソース電極層及びドレイン電極層を形成し、前記一導電型を有する半 導体層をパターニングし、ソース領域及びドレイン領域を形成し、前記ソース電極層、前 記ドレイン電極層及び前記ゲート絶縁層上に絶縁層を形成し、前記絶縁層に前記ソース電 極層または前記ドレイン電極層に達する第1の開口部、及び前記絶縁層と前記ゲート絶縁 層に前記画素電極層に達する第2の開口部を形成し、前記第1の開口部及び前記第2の開 口部に、前記ソース電極層または前記ドレイン電極層及び前記画素電極層を電気的に接続 する配線層を形成する。

# [0014]

本発明の液晶表示装置の作製方法の一は、絶縁表面上に導電層を形成し、前記導電層上 にレジストを形成し、前記レジストをレーザ光で露光してパターニングし、マスクを形成 し、前記マスクを用いて前記導電層をパターニングし、ゲート電極層及び画素電極層を形 成し、前記ゲート電極層及び前記画素電極層上にゲート絶縁層を形成し、前記ゲート絶縁 層上に半導体の結晶化を助長する金属元素を含む金属膜を形成し、前記金属膜上に半導体 層を形成し、前記半導体層上に選択的にチャネル保護層を形成し、前記半導体層及び前記 チャネル保護層に接して一導電型を有する半導体層を形成し、前記半導体層、前記チャネ ル保護層、及び前記一導電型を有する半導体層を加熱することにより、前記半導体層を結 晶化するとともに、前記半導体層の結晶化を助長する前記金属元素を、前記一導電型を有 する半導体層に移動して低減または除去し、前記一導電型を有する半導体層上に、導電性 材料を含む組成物を吐出して選択的にソース電極層及びドレイン電極層を形成し、前記一 導電型を有する半導体層をパターニングし、ソース領域及びドレイン領域を形成し、前記 ソース電極層、前記ドレイン電極層及び前記ゲート絶縁層上に絶縁層を形成し、前記絶縁 層に前記ソース電極層または前記ドレイン電極層に達する第1の開口部、及び前記絶縁層 と前記ゲート絶縁層に前記画素電極層に達する第2の開口部を形成し、前記第1の開口部 及び前記第2の開口部に、前記ソース電極層または前記ドレイン電極層及び前記画素電極 層を電気的に接続する配線層を形成する。

# [0015]

本発明の液晶表示装置の作製方法の一は、絶縁表面上に導電層を形成し、前記導電層上にレジストを形成し、前記レジストをレーザ光で露光してパターニングし、マスクを形成し、前記マスクを用いて前記導電層をパターニングし、ゲート電極層及び画素電極層を形成し、前記ゲート電極層及び前記画素電極層上にゲート絶縁層を形成し、前記ゲート絶縁層とに半導体層を形成し、前記半導体層上に半導体の結晶化を助長する金属元素を含む金属膜を形成し、前記金属膜上に選択的にチャネル保護層を形成し、前記金属膜及び前記チャネル保護層に接して一導電型を有する半導体層を形成し、前記半導体層、前記チャネル保護層、及び前記一導電型を有する半導体層を加熱することにより、前記半導体層を結晶化するとともに、前記半導体層の結晶化を助長する前記金属元素を、前記一導電型を有す

20

30

40

50

る半導体層に移動して低減または除去し、前記一導電型を有する半導体層上に、導電性材料を含む組成物を吐出して選択的にソース電極層及びドレイン電極層を形成し、前記一導電型を有する半導体層をパターニングし、ソース領域及びドレイン領域を形成し、前記ソース電極層、前記ドレイン電極層及び前記ゲート絶縁層上に絶縁層を形成し、前記絶縁層に前記ソース電極層または前記ドレイン電極層に達する第1の開口部、及び前記絶縁層と前記ゲート絶縁層に前記画素電極層に達する第2の開口部を形成し、前記第1の開口部及び前記第2の開口部に、前記ソース電極層または前記ドレイン電極層及び前記画素電極層を電気的に接続する配線層を形成する。

## [0016]

本発明の液晶表示装置の作製方法の一は、絶縁表面上に、ゲート電極層及び画素電極層を形成し、前記ゲート電極層及び前記画素電極層上にゲート絶縁層を形成し、前記が上に準導体層を形成し、前記半導体層を形成し、前記半導体層を形成し、前記半導体層を形成し、前記半導体層を形成し、前記半導体層を形成し、前記半導体層を形成し、前記半導体層を形成し、前記半導体層を形成し、前記半導体層を活品化を助長することにより、前記半導体層を結晶化を助長する前記金属元素を、前記一導電型を有する半導体層とともに、前記半導体層の結晶化を助長する前記金属元素を、前記一導電型を有する半導体層上に導電性材料を出出して選択的に導電層を形成し、前記導電層上にレジスクを形成し、前記マスクを形成し、前記マスクを形成し、前記マスクを形成し、前記でリース電極層、ドレイン電極層、ソース領域及びドレイン領域を形成し、前記ソース電極層、ドレイン電極層を形成し、前記絶縁層に前記ソース電極層または前記でイン電極層に達する第1の開口部、及び前記絶縁層と前記ゲート絶縁層に前記回素電極層に前記が一ト絶縁層に前記の開口部に、前記がイン電極層に対する配線層を形成し、前記第1の開口部に接続する配線層を形成する電極層に接続する配線層を形成する電極層に対対が表面に接続する配線層を形成する電極層に対対が表面に接続する配線層を形成する電極層を電気的に接続する配線層を形成する電極層を電気的に接続する配線層を形成する電極層を電気的に接続する配線層を形成する電極層を電気的に接続する配線層を形成する配線層を形成する配線層を電気的に接続する配線層を形成する

# [0017]

本発明の液晶表示装置の作製方法の一は、絶縁表面上に、ゲート電極層及び画素電極層を形成し、前記ゲート電極層及び前記画素電極層上にゲート絶縁層を形成し、前記半導体層に半導体の結晶化を助長する金属元素を含む金属膜を形成し、前記半導体層を加熱することにより、前記半導体層を結晶化するとともに、前記半導体層の結晶化を助長することにより、前記半導体層を結晶化するとともに、前記半導体層の結晶化を助長する前記金属元素を、前記一導電型を有する半導体層に移動して低減または除去し、前記一導電型を有する半導体層上に導電性材料を含む組成物を吐出して選択的に導電層を形成し、前記導電層上にレジストを形成し、前記レーザ光で露光してパターニングし、マスクを形成し、前記マスクを用いて前記記ストをレーザ光で露光してパターニングし、マスクを形成し、前記マスクを用いて前記記ストをレーザ光で露光してパターニングし、フス電極層、ドレイン電極層、ソース領域及びドレイン領域を形成し、前記ソース電極層、ドレイン電極層、シース領域及びドレイン領域を形成し、前記シース電極層または前記ドレイン電極層を形成し、前記絶縁層と前記ゲート絶縁層に前記に対して達極層に達する第1の開口部、及び前記絶縁層と前記ゲート絶縁層に前記に対して達極層に達する第1の開口部を形成し、前記第1の開口部及び前記第2の開口部に、前記ソース電極層に達する第2の開口部を形成し、前記第1の開口部及び前記第2の開口部に、前記ソース電極層に達する第2の開口部を形成し、前記第1の開口部及び前記第2の開口部に、前記ソース電極層に達する記録層を形成する。

### [0018]

本発明の液晶表示装置の作製方法の一は、絶縁表面上に、ゲート電極層及び画素電極層を形成し、前記ゲート電極層及び前記画素電極層上にゲート絶縁層を形成し、前記ゲート絶縁層上に半導体の結晶化を助長する金属元素を含む金属膜を形成し、前記半導体層及び前記チャネル保護層を形成し、前記半導体層及び前記チャネル保護層に接して一導電型を有する半導体層を形成し、前記半導体層、前記チャネル保護層、及び前記一導電型を有する半導体層を加熱することにより、前記半導体層を結晶化するとともに、前記半導体層の結晶化を助長する前記金属元素を、前記一導電型を有する半導体層に移動して低減または除去し、前記一導電型を有する半導体層上に導電

性材料を含む組成物を吐出して選択的に導電層を形成し、前記導電層上にレジストを形成し、前記レジストをレーザ光で露光してパターニングし、マスクを形成し、前記マスクを用いて前記導電層及び前記一導電型を有する半導体層をパターニングし、ソース電極層、ドレイン電極層、ソース領域及びドレイン領域を形成し、前記ソース電極層、前記ドレイン電極層及び前記ゲート絶縁層上に絶縁層を形成し、前記絶縁層に前記ソース電極層または前記ドレイン電極層に達する第1の開口部、及び前記絶縁層と前記ゲート絶縁層に前記画素電極層に達する第2の開口部を形成し、前記第1の開口部及び前記第2の開口部に、前記ソース電極層または前記ドレイン電極層及び前記画素電極層を電気的に接続する配線層を形成する。

# [0019]

本発明の液晶表示装置の作製方法の一は、絶縁表面上に、ゲート電極層及び画素電極層 を形成し、前記ゲート電極層及び前記画素電極層上にゲート絶縁層を形成し、前記ゲート 絶縁層上に半導体層を形成し、前記半導体層上に半導体の結晶化を助長する金属元素を含 む金属膜を形成し、前記金属膜上に選択的にチャネル保護層を形成し、前記金属膜及び前 記チャネル保護層に接して一導電型を有する半導体層を形成し、前記半導体層、前記チャ ネル保護層、及び前記一導電型を有する半導体層を加熱することにより、前記半導体層を 結晶化するとともに、前記半導体層の結晶化を助長する前記金属元素を、前記一導電型を 有する半導体層に移動して低減または除去し、前記一導電型を有する半導体層上に導電性 材料を含む組成物を吐出して選択的に導電層を形成し、前記導電層上にレジストを形成し 、前記レジストをレーザ光で露光してパターニングし、マスクを形成し、前記マスクを用 いて前記導電層及び前記一導電型を有する半導体層をパターニングし、ソース電極層、 レイン電極層、ソース領域及びドレイン領域を形成し、前記ソース電極層、前記ドレイン 電極層及び前記ゲート絶縁層上に絶縁層を形成し、前記絶縁層に前記ソース電極層または 前記ドレイン電極層に達する第1の開口部、及び前記絶縁層と前記ゲート絶縁層に前記画 素電極層に達する第2の開口部を形成し、前記第1の開口部及び前記第2の開口部に、前 記ソース電極層または前記ドレイン電極層及び前記画素電極層を電気的に接続する配線層 を形成する。

### 【発明の効果】

## [0020]

本発明により、結晶性半導体膜を有する逆スタガ型薄膜トランジスタを形成することができる。このため少ないマスク数でTFTを形成することができる。また、本発明で形成されるTFTは、結晶性半導体膜で形成されるため非晶質半導体膜で形成される逆スタガ型TFTと比較して移動度が高い。また、ソース領域及びドレイン領域には、p型を付与する不純物元素(アクセプター型元素)又はn型を付与する不純物元素(ドナー型元素)に加え、結晶化を促進する元素である金属元素をも含む。このため、抵抗率の低いソース領域及びドレイン領域が形成できる。この結果、高速動作が必要な液晶表示装置を作製することが可能である。代表的には、OCBモードのような応答速度が速く且つ高視野角な表示が可能な液晶表示装置を製造することが可能である。

## [0021]

また、非晶質半導体膜で形成される薄膜トランジスタと比較して、しきい値のずれが生じにくく、TFT特性のバラツキを低減することが可能である。このため、表示ムラを低減することが可能であり、信頼性の高い液晶表示装置を作製することが可能である。

# [0022]

また、成膜段階で半導体膜中に混入する金属元素をゲッタリングするため、オフ電流を低減することが可能である。このため、このようなTFTを液晶表示装置のスイッチング素子に設けることにより、コントラストを向上させることが可能である。

### [0023]

また本発明によると、材料のロスも少なく、コストダウンも達成できる。よって高性能 、高信頼性の液晶表示装置を歩留まりよく作製することができる。

# 【発明を実施するための最良の形態】

10

20

30

50

### [0024]

## (実施の形態1)

本発明の実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同一部分又は同様な機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。

### [0025]

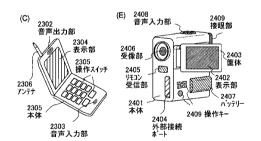

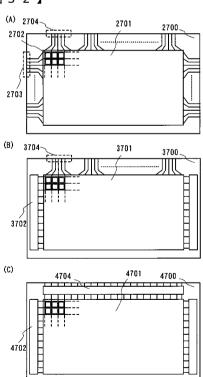

図 3 2 ( A ) は本発明に係る表示パネルの構成を示す上面図であり、絶縁表面を有する基板 2 7 0 0 上に画素 2 7 0 2 をマトリクス上に配列させた画素部 2 7 0 1、走査線側入力端子 2 7 0 3、信号線側入力端子 2 7 0 4 が形成されている。画素数は種々の規格に従って設ければ良く、 X G A であれば 1 0 2 4  $\times$  7 6 8  $\times$  3 ( R G B )、 U X G A であれば 1 6 0 0  $\times$  1 2 0 0  $\times$  3 ( R G B )、 フルスペックハイビジョンに対応させるのであれば 1 9 2 0  $\times$  1 0 8 0  $\times$  3 ( R G B ) とすれば良い。

## [0026]

画素 2 7 0 2 は、走査線側入力端子 2 7 0 3 から延在する走査線と、信号線側入力端子 2 7 0 4 から延在する信号線とが交差することで、マトリクス状に配設される。画素 2 7 0 2 のそれぞれには、スイッチング素子とそれに接続する画素電極が備えられている。スイッチング素子の代表的な一例はTFTであり、TFTのゲート電極側が走査線と、ソース若しくはドレイン側が信号線と接続されることにより、個々の画素を外部から入力する信号によって独立して制御可能としている。

# [0027]

図32(A)は、走査線及び信号線へ入力する信号を、外付けの駆動回路により制御する表示パネルの構成を示しているが、図33(A)に示すように、COG(Chip on Glass)方式によりドライバIC2751を基板2700上に実装しても良い。また他の実装形態として、図33(B)に示すようなTAB(Tape Automated Bonding)方式を用いてもよい。ドライバICは単結晶半導体基板に形成されたものでも良いし、ガラス基板上にTFTで回路を形成したものであっても良い。図33において、ドライバIC2751は、FPC2750と接続している。

### [0028]

また、画素に設けるTFTをSASで形成する場合には、図32(B)に示すように 走査線側駆動回路3702を基板3700上に形成し一体化することもできる。図33( B)において、3701は画素部であり、信号線側駆動回路は、図32(A)と同様に外 付けの駆動回路により制御する。画素に設けるTFTを移動度の高い、多結晶(微結晶) 半導体、単結晶半導体などで形成する場合は、図32(C)は、走査線駆動回路4702 と、信号線駆動回路4704をガラス基板4700上に一体形成することもできる。

### [0029]

本発明は、配線層若しくは電極を形成する導電層や、所定のパターンに形成するためのマスク層など表示パネルを作製するために必要な物体(その目的や機能に応じて膜や層などあらゆる形態で存在する)のうち、少なくとも一つ若しくはそれ以上を、選択的に望な形状にを形成可能な方法により形成して、液晶表示装置を作製することを特徴として、液晶表示装置を構成する、ゲート電極層、ロス電極層、ドレイン電極層などの導電層、半導体層、マスク層、絶縁層など、所定の形状を有して形成される全ての構成要素に対して適用できる。選択的に所望な形状に形成可能な方法として、導電層や絶縁層など形成し、特定の目的に調合された組成物の液消を選択的に吐出(噴出)して所定のパターンに形成することが可能な、液滴吐出(噴出の方式によっては、インクジェット法とも呼ばれる。)を用いる。また、物体が所望のパターンに転写、または描写できる方法、例えば各種印刷法(スクリーン(孔版)印刷、フセット(平版)印刷、凸版印刷やグラビア(凹版)印刷など所望なパターンで形成さ

10

20

30

40

20

30

40

50

れる方法)なども用いることができる。

## [0030]

本実施の形態は、流動性を有する形成する材料を含む組成物を、液滴として吐出(噴出)し、所望なパターンに形成する方法を用いている。形成物の被形成領域に、形成する材料を含む液滴を吐出し、焼成、乾燥等を行って固定化し所望なパターンで物体を形成する。

#### [0031]

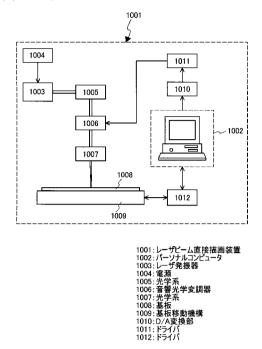

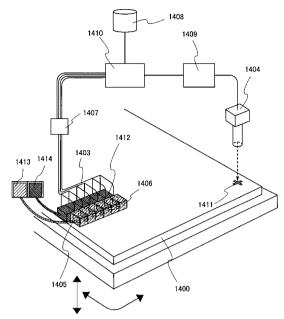

液滴吐出法に用いる液滴吐出装置の一態様を図30に示す。液滴吐出手段1403の個々のヘッド1405、ヘッド1412は制御手段1407に接続され、それがコンピュータ1410で制御することにより予めプログラミングされたパターンに描画することができる。描画するタイミングは、例えば、基板1400上に形成されたマーカー1411を基準に行えば良い。或いは、基板1400の縁を基準にして基準点を確定させても良い。これを撮像手段1404で検出し、画像処理手段1409にてデジタル信号に変換したものをコンピュータ1410で認識して制御信号を発生させて制御手段1407に送る。撮像手段1404としては、電荷結合素子(CCD)や相補型金属酸化物半導体(CMOS)を利用したイメージセンサなどを用いることができる。勿論、基板1400上に形成されるべきパターンの情報は記憶媒体1408に格納されたものであり、この情報を基にして制御手段1407に制御信号を送り、液滴吐出手段1403の個々のヘッド1405、ヘッド1412を個別に制御することができる。吐出する材料は、材料供給源1413、材料供給源1414より配管を通してヘッド1405、ヘッド1412に供給される。

## [0032]

ヘッド1405とヘッド1412のノズルのサイズは異なっており、異なる材料を異なる幅で同時に描画することができる。一つのヘッドで、導電性材料や有機、無機材料などをそれぞれ吐出し、描画することができ、層間膜のような広領域に描画する場合は、スループットを向上させるため複数のノズルより同材料を同時に吐出し、描画することができる。大型基板を用いる場合、ヘッド1405、ヘッド1412は基板上を、矢印の方向に自在に走査し、描画する領域を自由に設定することができ、同じパターンを一枚の基板に複数描画することができる。

## [0033]

本発明では、形成物のパターニング工程においてを感光性のレジストや感光性物質を含む材料に光を照射し、露光する工程を行う。露光に用いる光は、特に限定されず、赤外光、可視光、または紫外光のいずれか一またはそれらの組み合わせを用いることが可能である。例えば、紫外線ランプ、ブラックライト、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、または高圧水銀ランプから射出された光を用いてもよい。その場合、ランプ光源は、必要な時間点灯させて照射してもよいし、複数回照射してもよい。

# [0034]

レーザ光を用いてもよく、レーザ光を用いるとより精密なパターンで被形成領域を露光処理できるので、そこに形成される物体も高繊細化することができる。本発明で用いることのできるレーザ光(レーザビームともいう)を処理領域に描画する、レーザ光描画装置について、図29を用いて説明する。本実施の形態では、レーザ光を照射する領域をマスク等を介して選択するのではなく、処理領域を選択して直接照射して処理するため、レーザ光直接描装置を用いる。図29に示すようにレーザ光直接描画装置1001は、レーザ光を照射する際の各種制御を実行するパーソナルコンピュータ(以下、PCと示す。)1002と、レーザ光を出力するレーザ発振器1003と、レーザ発振器1003の電源1004と、レーザ光を減衰させるための光学系(NDフィルタ)1005と、レーザ光の断面の拡大又の強度を変調するための音響光学変調器(AOM)1006と、レーザ光の断面の拡大又は縮小をするためのレンズ、光路の変更するためのミラー等で構成される光学系1007、スステージ及びYステージを有する基板移動機構1009と、PC1002から出力される制御データをデジタルーアナログ変換するD/A変換部1010と、D/A変換部

ら出力されるアナログ電圧に応じて音響光学変調器 1 0 0 6 を制御するドライバ 1 0 1 1 と、基板移動機構 1 0 0 9 を駆動するための駆動信号を出力するドライバ 1 0 1 2 とを備えている。

## [0035]

レーザ発振器  $1\ 0\ 0\ 3$  としては、紫外光、可視光、又は赤外光を発振することが可能なレーザ発振器を用いることができる。レーザー発振器としては、 $K\ r\ F$ 、 $K\ r\ F$ 、 $X\ e\ C\ 1$ 、 $X\ e\ 等のエキシマレーザ発振器、<math>H\ e$ 、 $H\ e$ - $C\ d$ 、 $A\ r$ 、 $H\ e$ - $N\ e$ 、 $H\ F$ 等の気体レーザ発振器、 $Y\ A\ G$ 、 $G\ d\ V\ O_4$ 、 $Y\ V\ O_4$ 、 $Y\ L\ F$ 、 $Y\ A\ 1\ O_3$ などの結晶に $C\ r$ 、 $N\ d$ 、 $E\ r$ 、 $H\ o$ 、 $C\ e$ 、 $C\ o$ 、 $T\ i\ Z\ d\ T\ m\ e$ ドープした結晶を使った固体レーザー発振器、 $G\ a\ N$ 、 $G\ a\ A\ s$ 、 $G\ a\ A\ 1\ A\ s$ 、 $G\ a\ A\ s$   $G\ a\ b\ s$   $G\ a\ b\$

## [0036]

次に、レーザ光直接描画装置を用いた物質(表面)の露光処理について述べる。基板1008が基板移動機構1009に装着されると、PC1002は図外のカメラによって、基板に付されているマーカの位置を検出する。次いで、PC1002は、検出したマーカの位置データと、予め入力されている描画パターンデータとに基づいて、基板移動機構1009を移動させるための移動データを生成する。この後、PC1002が、ドライバ1011を介して音響光学変調器1006の出力光量を制御することにより、レーザ発振器1003から出力されたレーザ光は、光学系1005によって減衰された後、音響光学変調器1006から出力されたレーザ光は、光学系1007で光路及びレーザ光(ビームスポット)の形状を変化させ、レンズで集光した後、基板上に形成された被処理物に該レーザ光を照射して、被処理物を改質処理する。このとき、PC1002が生成した移動データに従い、基板移動機構1009をX方向及びY方向に移動制御する。この結果、所定の場所にレーザ光が照射され、被処理物の露光処理が行われる。

### [0037]

この結果、レーザ光が照射された領域で、被処理物は露光され、感光される。感光性物質には大きくわけてネガ型とポジ型がある。ネガ型の場合は、露光された部分で化学反応が生じ、現像液によって化学反応が生じた部分のみが残されてパターンが形成される。また、ポジ型の場合は、露光された部分で化学反応が生じ、現像液によって化学反応が生じた部分が溶解され、露光されなかった部分のみが残されてパターンが形成される。レーザ光のエネルギーの一部は被処理物材料で熱に変換され、被処理物の一部を反応させるため、処理された被処理物の領域の幅が、処理するレーザ光の幅より若干大きくなることもある。また、短波長のレーザ光ほど、レーザ光の径を短く集光することが可能であるため、微細な幅に処理領域を形成するためには、短波長のレーザ光を照射することが好ましい

### [0038]

また、レーザ光の膜表面でのスポット形状は、点状、円形、楕円形、矩形、または線状 (厳密には細長い長方形状)となるように光学系で加工されている。

# [0039]

また、図29に示した装置は、基板の表面側からレーザー光を照射して露光する例を示したが、光学系や基板移動機構を適宜変更し、基板の裏面側からレーザー光を照射して露 光するレーザビーム描画装置としてもよい。

### [0040]

なお、ここでは、基板を移動して選択的にレーザ光を照射しているが、これに限定されず、レーザ光をX-Y軸方向に走査してレーザ光を照射することができる。この場合、光学系1007にポリゴンミラーやガルバノミラー、音響光学偏向器(Acoust-Optic Deflector; AOD)を用いることが好ましい。また、レーザビームをX軸又はY軸の一方向に走査し、基板をX軸又はY軸の他の方向に移動して、基板の所定の場所にレーザビーム

10

20

30

40

20

30

40

50

を照射してもよい。

## [0041]

また、光は、ランプ光源による光とレーザ光とを組み合わせて用いることもでき、比較的広範囲なパターニングを行う領域は、マスクを用いてランプによる照射処理を行い、高繊細なパターニングを行う領域のみレーザ光で照射処理を行うこともできる。このように光の照射処理を行うと、スループットも向上でき、かつ高繊細にパターニングされた配線基板などを得ることができる。

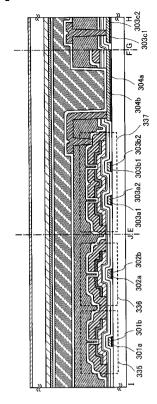

### [0042]

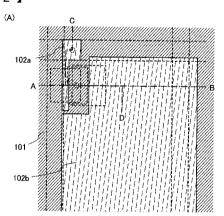

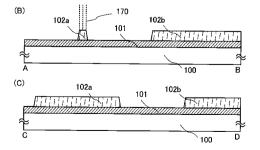

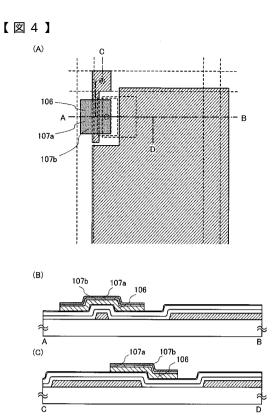

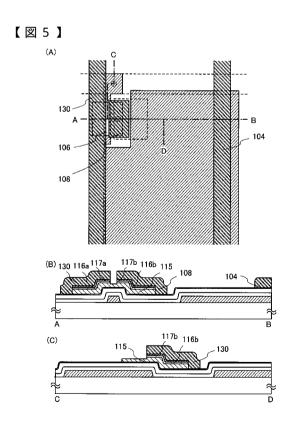

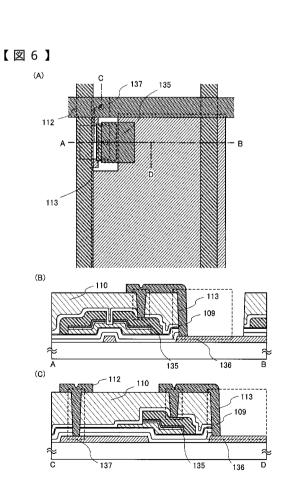

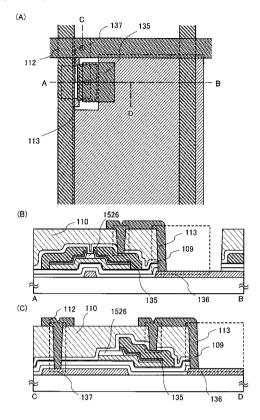

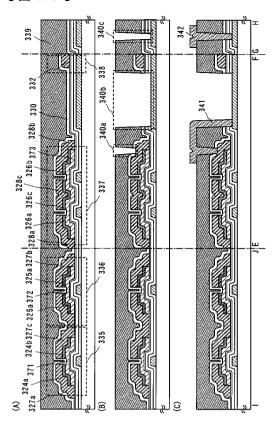

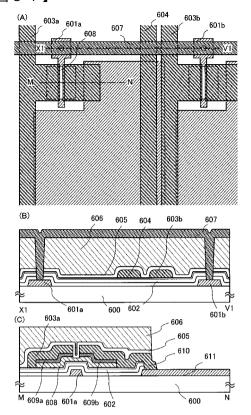

本発明の実施の形態について、図1乃至図9を用いて説明する。より詳しくは、本発明を適用した液晶表示装置の作製方法について説明する。まず、本発明を適用した、チャネルエッチ型の薄膜トランジスタを有する液晶表示装置の作製方法について説明する。図2~図6(A)は液晶表示装置画素部の上面図であり、図2~図6の(B)は、図2~図6(A)における線A Bによる断面図、図2~図6の(C)は、図2~図6(A)における線C-Dによる断面図である。

### [0043]

基板100は、バリウムホウケイ酸ガラス、アルミノホウケイ酸ガラス等からなるガラス基板、石英基板、シリコン基板、金属基板、ステンレス基板又は本作製工程の処理温度に耐えうる耐熱性を有するプラスチック基板を用いる。また、基板100の表面が平坦化されるようにСMP法などによって、研磨しても良い。なお、基板100上に、絶縁層を形成してもよい。絶縁層は、СVD法、プラズマСVD法、スパッタリング法、スピンコート法等の公知の方法により、珪素を含む酸化物材料、窒化物材料を用いて、単層又は積層して形成される。この絶縁層は、形成しなくても良いが、基板100からの汚染物質などを遮断する効果がある。基板100として、320mm×400mm、370mm×470mm、550mm×650mm、600mm×720mm、680mm×880mm、1000mm×1200mm、1150mm×1300mmのような大面積基板を用いることができる。

### [0044]

基板100上に導電膜101を形成する。導電膜101は、パターニングされゲート電極層と画素電極層となる。導電膜101は、印刷法、電界メッキ法、PVD法(Physic al Vapor Deposition)、CVD法(Chemical Vapor Deposition)、蒸着法等の公知の手法により高融点材料を用いて形成することが好ましい。また形成方法としては、液滴吐出法によって所望のパターンに形成することもできる。高融点材料を用いることにより、後の加熱工程が可能となる。高融点材料としては、タングステン(W)、モリブデン(Mo)、ジルコニウム(Zr)、ハフニウム(Hf)、バナジウム(V)、ニオブ(Nb)、タンタル(Ta)、クロム(Cr)、コバルト(Co)、ニッケル(Ni)、白金(Pt)等の金属又はその合金、若しくはその金属窒化物を適宜用いることができる。また、これら複数の層を積層して形成しても良い。代表的には、基板表面に窒化タンタル膜、その上にタングステン膜を積層してもよい。このような反射性を有する金属は、反射型の液晶表示パネルを作製する場合には好ましい。また、珪素に一導電型を付与する不純物元素を添加した材料を用いても良い。例えば、非晶質珪素膜にリン(P)などのn型を付与する不純物元素が含まれたn型を有する珪素膜などを用いることができる。

### [0045]

導電膜101は、画素電極層としても機能するので、透明導電性材料を用いて形成することもできる。画素電極層は、透過型の液晶表示パネルを作製する場合には、インジウム錫酸化物(ITO)、酸化珪素を含むインジウム錫酸化物(ITSO)、酸化亜鉛(ZnO)、酸化スズ(SnO₂)などにより形成してもよい。好ましくは、スパッタリング法によりインジウム錫酸化物(ITO)、酸化珪素を含むインジウム錫酸化物(ITSO)、酸化亜鉛(ZnO)などで形成する。より好ましくは、ITOに酸化珪素が2~10重量%含まれたターゲットを用いてスパッタリング法で酸化珪素を含む酸化インジウムスズを用いる。この他、酸化珪素を含み酸化インジウムに2~20%の酸化亜鉛(ZnO)

20

30

40

50

を混合した酸化インジウム酸化亜鉛合金などの導電性材料を用いても良い。

# [0046]

本実施の形態では、導電膜 1 0 1 は、導電性材料としてインジウム錫酸化物を含む組成物を吐出して、5 5 0 で焼成し、導電膜 1 0 1 を形成する。液滴吐出手段とは、組成物の吐出口を有するノズルや、1 つ又は複数のノズルを具備したヘッド等の液滴を吐出する手段を有するものの総称とする。液滴吐出手段が具備するノズルの径は、0 . 0 2 ~ 1 0 0  $\mu$  m (好適には 3 0  $\mu$  m 以下)に設定し、該ノズルから吐出される組成物の吐出量は 0 . 0 0 1  $\mu$  p 1  $\mu$  c 1 0 0  $\mu$  p 1 (好適には 0 . 1  $\mu$  p 1  $\mu$  c 1  $\mu$  c 2  $\mu$  c 2  $\mu$  d  $\mu$  c 2  $\mu$  c 2  $\mu$  c 2  $\mu$  c 3  $\mu$  c 2  $\mu$  c 3  $\mu$  c 3  $\mu$  c 3  $\mu$  c 3  $\mu$  c 4  $\mu$  c 4  $\mu$  c 5  $\mu$  c 4  $\mu$  c 5  $\mu$  c 6  $\mu$  c 7  $\mu$  c 9  $\mu$  c

### [0047]

吐出口から吐出する組成物は、導電性材料を溶媒に溶解又は分散させたものを用いる。 導電性材料とは、Ag、Au、Cu、Ni、Pt、Pd、Ir、Rh、W、Al等の金属、Cd、Znの金属硫化物、Fe、Ti、Si、Ge、Si、Zr、Baなどの酸化物、ハロゲン化銀の微粒子又は分散性ナノ粒子に相当する。また、透明導電膜として用いられるインジウム錫酸化物(ITO)、インジウム錫酸化物と酸化珪素からなるITSO、有機インジウム、有機スズ、酸化亜鉛、窒化チタン等に相当する。但し、吐出口から吐出する組成物は、比抵抗値を考慮して、金、銀、銅のいずれかの材料を溶媒に溶解又は分散させたものを用いることが好適であり、より好適には、低抵抗な銀、銅を用いるとよい。但し、銀、銅を用いる場合には、不純物対策のため、合わせてバリア膜を設けるとよい。バリア膜としては、窒化珪素膜やニッケルボロン(NiB)を用いるとことができる。

### [0048]

また、導電性材料の周りに他の導電性材料がコーティングされ、複数の層になっている 粒子でも良い。例えば、銅の周りにニッケルボロン(NiB)がコーティングされ、その 周囲に銀がコーティングされている3層構造の粒子などを用いても良い。溶媒は、酢酸ブ チル、酢酸エチル等のエステル類、イソプロピルアルコール、エチルアルコール等のアル コール類、メチルエチルケトン、アセトン等の有機溶剤等を用いる。組成物の粘度は20 mPa・s以下が好適であり、これは、乾燥が起こることを防止したり、吐出口から組成 物を円滑に吐出できるようにしたりするためである。また、組成物の表面張力は、40m N/m以下が好適である。但し、用いる溶媒や、用途に合わせて、組成物の粘度等は適宜 調整するとよい。一例として、ITOや、有機インジウム、有機スズを溶媒に溶解又は分 散させた組成物の粘度は5~20mPa・s、銀を溶媒に溶解又は分散させた組成物の粘 度は5~20mPa・s、金を溶媒に溶解又は分散させた組成物の粘 度は5~20mPa・s、金を溶媒に溶解又は分散させた組成物の粘

## [0049]

また、電極層となる導電膜101は、複数の導電性材料を積層しても良い。また、始めに導電性材料として銀を用いて、液滴吐出法で導電層を形成した後、銅などでめっきを行ってもよい。めっきは電気めっきや化学(無電界)めっき法で行えばよい。めっきは、めっきの材料を有する溶液を満たした容器に基板表面を浸してもよいが、基板を斜め(または垂直)に立てて設置し、めっきする材料を有する溶液を、基板表面に流すように塗布してもよい。基板を立てて溶液を塗布するようにめっきを行うと、工程装置が小型化する利点がある。

# [0050]

各ノズルの径や所望のパターン形状などに依存するが、ノズルの目詰まり防止や高精細なパターンの作製のため、導電体の粒子の径はなるべく小さい方が好ましく、好適には粒径 0 . 1 μ m 以下が好ましい。組成物は、電解法、アトマイズ法又は湿式還元法等の公知の方法で形成されるものであり、その粒子サイズは、一般的に約 0 . 0 1 ~ 1 0 μ m である。但し、ガス中蒸発法で形成すると、分散剤で保護されたナノ分子は約 7 n m と微細であり、またこのナノ粒子は、被覆剤を用いて各粒子の表面を覆うと、溶剤中に凝集がなく

20

30

40

50

、室温で安定に分散し、液体とほぼ同じ挙動を示す。従って、被覆剤を用いることが好ま しい。

### [0051]

組成物を吐出する工程は、減圧下で行うと、組成物を吐出して被処理物に着弾するまでの間に、該組成物の溶媒が揮発し、後の乾燥と焼成の工程を省略することができる。また、減圧下で行うと、導電体の表面に酸化膜などが形成されないため好ましい。また、組成物を吐出後、乾燥と焼成の一方又は両方の工程を行う。乾燥と焼成の工程は、両工程と加熱処理の工程であるが、例えば、乾燥は100度で3分間、焼成は200~350度で15分間~60分間で行うもので、その目的、温度と時間が異なるものである。乾燥の工程、焼成の工程は、常圧下又は減圧下で、レーザ光の照射や瞬間熱アニール、加熱炉なてはより行う。なお、この加熱処理を行うタイミングは特に限定されない。乾燥と焼成の工程を良好に行うためには、基板を加熱しておいてもよく、そのときの温度は、基板等の材質に依存するが、一般的には100~800度(好ましくは200~350度)とする。本工程により、組成物中の溶媒の揮発、又は化学的に分散剤を除去するとともに、周囲の樹脂が硬化収縮することで、ナノ粒子間を接触させ、融合と融着を加速する。

### [0052]

レーザ光の照射は、連続発振またはパルス発振の気体レーザ又は固体レーザを用いれば良い。前者の気体レーザとしては、エキシマレーザ、YAGレーザ等が挙げられ、後者の固体レーザとしては、Cr、Nd等がドーピングされたYAG、YVO4、GdVO4等の結晶を使ったレーザ等が挙げられる。なお、レーザ光の吸収率の関係から、連続発振のレーザを用いることが好ましい。また、パルス発振と連続発振を組み合わせた所謂ハイブリッドのレーザ照射方法を用いてもよい。但し、基板100の耐熱性に依っては、レーザ光の照射による加熱処理は、該基板100が破壊しないように、数マイクロ秒から数十秒の間で瞬間的に行うとよい。瞬間熱アニール(RTA)は、不活性ガスの雰囲気下で、紫外光乃至赤外光を照射する赤外ランプやハロゲンランプなどを用いて、急激に温度を上昇で、数分~数マイクロ秒の間で瞬間的に熱を加えて行う。この処理は瞬間的に行うために、実質的に最表面の薄膜のみを加熱することができ、下層の膜には影響を与えない。つまり、プラスチック基板等の耐熱性が弱い基板にも影響を与えない。

## [0053]

また、液滴吐出法により、導電膜101を組成物を吐出し形成した後、その平坦性を高めるために表面を圧力によってプレスして平坦化してもよい。プレスの方法としては、ローラー状のものを表面に走査することによって、凹凸をならすように軽減したり、平坦な板状な物で表面を垂直にプレスしてもよい。プレスする時に、加熱工程を行っても良い。また溶剤等によって表面を軟化、または融解させエアナイフで表面の凹凸部を除去しても良い。また、CMP法を用いて研磨しても良い。この工程は、液滴吐出法によって凹凸が生じる場合に、その表面の平坦化する場合適用することができる。また、平坦化の工程は、マスク102a、マスク102bによって導電膜101がパターニングされ、ゲート電極層103、画素電極層111が形成された後行っても良い。また、ゲート電極層103に銀や銅などを用いる場合、その上にバリア膜としてNiB膜を形成すると、ゲート電極層103の構成元素の拡散を防ぐ効果、及び表面を平坦化する効果がある。

# [0054]

導電膜101上にレジストからなるマスクを形成する。レジストからなるマスクは、レーザ光170によって露光されることによって微細に加工され、マスク102a、マスク102bを形成する(図2参照。)。レーザ光による加工前のレジストマスクも液滴吐出法を用いて形成することができる。液滴吐出法を組み合わせることで、スピンコート法などによる全面塗布形成に比べ、材料のロスが防げ、コストダウンが可能になる。

### [0055]

マスクは、感光剤を含む市販のレジスト材料を用いてもよく、例えば、代表的なポジ型 レジストである、ノボラック樹脂と感光剤であるナフトキノンジアジド化合物、ネガ型レ ジストであるベース樹脂、ジフェニルシランジオール及び酸発生剤などを用いてもよい。

20

30

40

50

いずれの材料を用いるとしても、その表面張力と粘度は、溶媒の濃度を調整したり、界面活性剤等を加えたりして適宜調整する。また導電膜101に感光性を有する感光性物質を含む導電性材料を用いると、レジストからなるマスクを形成しなくても導電膜101に直接レーザ光を照射し、露光、エッチャントによる除去を行うことで、所望のパターンにパターニングすることができる。この場合、マスクを形成せずともよいので工程が簡略化する利点がある。感光性物質を含む導電性材料は、Ag、Au、Cu、Ni、A1、Ptなどの金属或いは合金と、有機高分子樹脂、光重合開始剤、光重合単量体、または溶剤などからなる感光性樹脂とを含んだものを用いればよい。有機高分子樹脂としては、ノボラック樹脂、アクリル系コポリマー、メタクリル系コポリマー、セルローズ誘導体、環化ゴム系樹脂などを用いる。

[0056]

このように微細に加工されたマスク102a、マスク102bを用いて導電膜101をパターニングし、ゲート電極層103と画素電極層111を形成する(図3参照。)。 【0057】

次に、ゲート電極層103、画素電極層111の上にゲート絶縁層を形成する。ゲート絶縁層は、酸化珪素(SiOx)、窒化珪素(SiNx)、酸化窒化珪素(SiOxNy)(xゝy)などのいずれかで形成される単層、又はこれらの積層を適宜用いることができる。基板側からの不純物及び、ゲート電極層103の構成元素などの拡散を防止するため、ゲート電極に接するゲート絶縁層としては、窒化珪素(SiNx)、窒化酸化珪素(SiNxOy)(xゝy)などを用いて形成することが好ましい。また、後に形成される半導体層に接するゲート絶縁層としてお、絶縁性及び半導体層との界面特性から、酸化珪素(SiOx)、酸化窒化珪素(SiOxNy)(xゝy)を形成することが望ましい。なお、低い成膜温度でゲートリーク電流が少ない緻密な絶縁膜を形成するには、アルゴンなどの希ガス元素を反応ガスに含ませ、形成される絶縁膜中に混入させると良い。更には、ゲート電極層103を陽極酸化して、陽極酸化膜を形成しても良い。

[0058]

本実施の形態では、半導体層に結晶化を促進する金属元素(本実施の形態ではニッケルを用いる)を添加し、その後ゲッタリング処理を行って除去する。酸化珪素膜と珪素膜とは界面状態は良好であるが、界面において珪素膜中の金属元素と酸化珪素中の酸素が反応し、酸化金属物(本実施の形態では酸化ニッケル(NiOx))になりやすく、金属元素がゲッタリングされにくくなる場合がある。また、窒化珪素膜は、窒化珪素膜の応力や、トラップの影響により、半導体層との界面状態に悪影響を与える恐れがある。よって、半導体層に接する絶縁層の最上層に、膜厚  $0.1 \sim 10$  n m、より好ましくは  $1 \sim 3$  n m の窒化珪素膜、あるいは窒化酸化珪素膜を形成する。このような構造であると、半導体の窒化珪素膜の悪影響も軽減できる。本実施の形態では、SiH4、NH3を反応ガスとして窒化珪素膜を膜厚 50 n m でゲート絶縁層 105 a を形成し、SiH4、NH3 を反応ガスとして酸化珪素膜を膜厚 100 n m でゲート絶縁層 105 c を形成し、SiH4、NH3 を反応ガスとして窒化珪素膜を膜厚 100 n m でゲート絶縁層 105 c を形成する。

[0059]

次に、半導体層の詳細な作製方法を図9を用いて説明する。半導体膜の結晶化を助長するための金属膜404をゲート絶縁層上に形成する。金属膜404の形成方法としては、スパッタ法、CVD法、プラズマ処理法(プラズマCVD法も含む)、吸着法、金属塩の溶液を塗布する方法を使用することができる。このうち溶液を用いる方法は簡便であり、金属元素の濃度調整が容易であるという点で有用である。本実施の形態では、結晶化を助長する元素としてNiを用いる。Ni元素を重量換算で10ppmを含有した水溶液をスピンコーティング法により塗布し、金属膜404を形成する(図9(A)参照。)。結晶化を助長する元素としては、この珪素の結晶化を助長する金属元素としては鉄(Fe)、ニッケル(Ni)、コバルト(Co)、ルテニウム(Ru)、ロジウム(Rh)、パラジ

20

30

40

50

ウム(Pd)、オスニウム(Os)、イリジウム(Ir)、チタン(Ti)、白金(Pt)、銅(Cu)及び金(Au)から選ばれた一種又は複数種類を用いることができる。金属膜 404 はその形成条件によっては膜厚が極薄であり、膜として形態を保っていなくてもよい。

# [0060]

次に半導体膜を形成する。半導体膜は  $25 \sim 200$  n m (好ましくは  $30 \sim 150$  n m)の厚さで公知の手段 (スパッタ法、LPCVD法、またはプラズマCVD法等)により成膜すればよい。本実施の形態では、非晶質半導体膜を結晶化し、結晶性半導体膜とするものを用いるのが好ましい。

# [0061]

半導体膜を形成する材料は、シランやゲルマンに代表される半導体材料ガスを用いて気相成長法やスパッタリング法で作製される非晶質半導体(以下「アモルファス半導体:AS」ともいう。)、該非晶質半導体を熱エネルギーを利用して結晶化させた多結晶半導体、或いはセミアモルファス(微結晶若しくはマイクロクリスタルとも呼ばれる。以下「SAS」ともいう。)半導体などを用いることができる。

### [0062]

SASは、非晶質と結晶構造(単結晶、多結晶を含む)の中間的な構造を有し、自由 エネルギー的に安定な第3の状態を有する半導体であって、短距離秩序を持ち格子歪みを 有する結晶質な領域を含んでいる。少なくとも膜中の一部の領域には、0.5~20nm の結晶領域を観測することが出来、珪素を主成分とする場合にはラマンスペクトルが52 0 cm<sup>-1</sup>よりも低波数側にシフトしている。 X 線回折では珪素結晶格子に由来するとされ る(111)、(220)の回折ピークが観測される。未結合手(ダングリングボンド) の中和剤として水素またはハロゲンを少なくとも1原子%またはそれ以上含ませている。 SASは、珪化物気体をグロー放電分解(プラズマCVD)して形成する。珪化物気体と しては、SiH<sub>4</sub>、その他にもSi<sub>2</sub>H<sub>6</sub>、SiH<sub>2</sub>Cl<sub>2</sub>、SiHCl<sub>3</sub>、SiCl<sub>4</sub>、Si  $F_a$ などを用いることが可能である。また $F_a$ 、 $GeF_a$ を混合させても良い。この珪化物 気体をHゥ、又は、HゥとHe、Ar、Kr、Neから選ばれた一種または複数種の希ガス 元素で希釈しても良い。希釈率は2~1000倍の範囲、圧力は概略0.1Pa~133 Paの範囲、電源周波数は1MHz~120MHz、好ましくは13MHz~60MHz である。基板加熱温度は300 以下が好ましく、100~200 の基板加熱温度でも 形成可能である。ここで、主に成膜時に取り込まれる不純物元素として、酸素、窒素、炭 素などの大気成分に由来する不純物は1×10<sup>20</sup>cm<sup>-3</sup>以下とすることが望ましく、特に 、酸素濃度は 5 × 1 0 <sup>19</sup> c m <sup>-3</sup>以下、好ましくは 1 × 1 0 <sup>19</sup> c m <sup>-3</sup>以下となるようにする ことが好ましい。また、ヘリウム、アルゴン、クリプトン、ネオンなどの希ガス元素を含 ませて格子歪みをさらに助長させることで安定性が増し良好なSASが得られる。また半 導体膜としてフッ素系ガスより形成されるSAS層に水素系ガスより形成されるSAS層 を積層してもよい。

### [0063]

本実施の形態では、半導体膜として非晶質半導体膜405を用いる。(図9(B)参照。)、後の結晶化で良質な結晶構造を有する半導体膜を得るためには、非晶質半導体膜405膜中に含まれる酸素、窒素などの不純物濃度を5×10<sup>18</sup>/cm³(以下、濃度はすべて二次イオン質量分析法(SIMS)にて測定した原子濃度として示す。)以下、好ましくは2×10<sup>19</sup>atom/cm³以下に低減させておくと良い。これらの不純物は、触媒元素と反応しやすく、後の結晶化、及び結晶化を助長する元素のゲッタリングを妨害する要因となり、また、結晶化後においても捕獲中心や再結合中心の密度を増加させる要因となる

### [0064]

非晶質半導体膜 4 0 5 に対して、薄膜トランジスタのしきい値電圧を制御するために微量な不純物元素(ボロンまたはリン)のドーピングを行ってもよい。本実施の形態ではジボラン( $B_2H_6$ )を質量分離しないでプラズマ励起したイオンドープ法でボロンを添加

20

30

40

50

する。なお、質量分離を行うイオン注入法を用いてもよい。この後の結晶化のための加熱 処理によって、不純物の活性化を行うことができ、またドーピングの際に生じる欠陥等も 改善することができる。

## [0065]

次に、ソース領域、ドレイン領域及びLDD(Lightly Doped in)領域として機能する半導体膜を、非晶質半導体膜405に接して、半導体膜406 a、半導体膜406bを形成する。(図9(B)参照。)本実施の形態では、半導体膜4 0 6 a 及び半導体膜 4 0 6 b は、非晶質半導体膜の結晶化に用いる触媒金属を吸い込み自 らに取り込むゲッタリングシンクとしても機能する。まず、非晶質半導体膜405上に形 成された酸化膜を洗浄処理によって除去する。次いでプラズマCVD法を用いて、半導体 膜406a、半導体膜406bを形成する。半導体膜406a、半導体膜406bは不純 物元素を有しており、不純物元素としてはn型を付与する不純物元素を用いることができ 、例えばリン(P)、窒素(N)、ヒ素(As)、アンチモン(Sb)、ビスマス(Bi )から選ばれた一種または複数種を用いることができる。n型を付与する不純物元素を含 むn型を有する半導体層に、ヘリウム(He)、ネオン(Ne)、アルゴン(Ar)、K r(クリプトン)、Xe(キセノン)などの希ガス元素が含まれるように形成することも できる。本実施の形態では、半導体膜406aと半導体膜406bには、n型を付与する 不純物元素としてP(リン)が含まれており、半導体膜406aの不純物元素の濃度は、 半導体膜406bより低くなるように形成されている。前記不純物元素は、CVD法など によって、不純物元素を含むように半導体膜を形成しても良いし、半導体膜を形成後に、 イオンドーピング法などによって添加してもよい。

### [0066]

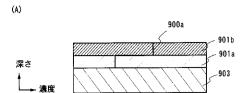

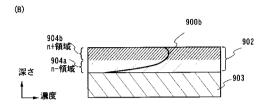

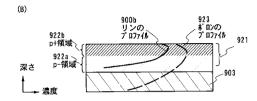

このときのn型を付与する不純物元素が含まれる半導体膜の不純物のプロファイルを図41に示す。図41(A)は、結晶性半導体膜903上に、プラズマCVD法によりn型を付与する不純物元素が含まれる半導体膜901a、901bを形成した時のn型を付与する不純物元素のプロファイル900aを示す。半導体膜901a、半導体膜901bは、半導体膜901bはn型の低濃度不純物領域(n-領域ともいう)として形成され、半導体膜901bはn型の高濃度不純物領域(n+領域ともいう)として形成されている。よって半導体膜901aはn型の高濃等体膜901bのそれぞれの膜において深さ方向に対して一定の濃度のn型を付与するるn型を付与する不純物元素が分布している。n+領域である半導体膜901bは後にソース領域及びドレイン領域として機能し、n-領域である半導体膜901bは後にソース領域及びドレイン領域として機能し、n-領域である半導体膜901bは後にソース領域及びドレイン領域として機能し、n-領域である半導体膜901bは後にソース領域及びドレイン領域として機能し、n-領域である半導体膜901aはLDD(Light)分けているので界面が存在する。n+領域とn-領域の膜厚制御は、それぞれ各濃度の半導体膜の膜厚を制御することによって達成できる。

# [0067]

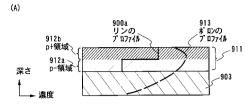

図41(A)で形成した半導体膜901a及び半導体膜901bにp型を付与する不純物元素としてボロンをイオンドープ法又はイオン注入法によって添加して半導体膜911を形成した時のp型を付与する不純物元素のプロファイル913を図42(A)に示す。p型を付与する不純物元素の濃度の方が、n型を付与する不純物元素の濃度より高く、半導体膜911はp型のを有する半導体膜となっているのがわかる。また、p型を付与する不純物元素は、チャネルドープされるため、結晶性半導体膜903にも添加されている。図42(A)に示すように、半導体膜911の表面付近は、p型を付与する不純物元素濃度が比較的が高いp型の不純物領域(p+領域ともいう)912bとなっており、一方、結晶性半導体膜903に近づくにつれ、p型を付与する不純物元素濃度が比較的減少しておりp型の低濃度不純物領域(p-領域ともいう)912aとなっている。

### [0068]

一方、図41(B)は、結晶性半導体膜903上に、非晶質半導体、SAS、微結晶 半導体、及び結晶性半導体から選ばれたいずれかの状態を有する膜の半導体膜を形成し、

20

30

40

50

イオンドープ法又はイオン注入法により該半導体膜に n 型を付与する不純物元素を添加して半導体膜 9 0 2 を形成した時の n 型を付与する不純物元素のプロファイル 9 0 0 b を示す。 図 4 1 ( B ) に示すように、半導体膜 9 0 2 の表面付近は、 n 型を付与する不純物元素濃度が比較的が高い。 n 型を付与する不純物元素濃度が 1 × 1 0 19 / c m 3以上の領域を n 型の高濃度不純物領域(n + 領域ともいう) 9 0 4 b と示す。一方、結晶性半導体膜 9 0 3 に近づくにつれ、 n 型を付与する不純物元素濃度が比較的減少している。 n 型を付与する不純物元素濃度が比較的減少している。 n 型を付与する不純物元素濃度が比較の減少している。 n 型を付与する不純物元素濃度が比較の領域と n 型の低濃度不純物領域(n - 領域ともいう) 9 0 4 a と示す。 n + 領域 9 0 4 b は後にソース領域及びドレン領域として機能し、 n - 領域 9 0 4 a は L D D 領域として機能する。なお、 n + 領域として機能し、 n - 領域 7 の 2 は、添加条件により形成された n 型を付与する不純物元素が含まれる半導体膜 9 0 2 は、添加条件によって濃度プロファイルを制御することが可能であり、 n + 領域と n - 領域の膜厚を適宜制御することが可能である。 n + 領域と n - 領域を有することにより電界の緩和効果が大きくなり、ホットキャリア耐性を高めた薄膜トランジスタを形成することが可能となる。

#### [0069]

図41(B)で形成した半導体膜902にp型を付与する不純物元素としてボロンをイオンドープ法又はイオン注入法によって添加して半導体膜921を形成した時のp型を付与する不純物元素のプロファイル923を図42(B)に示す。p型を付与する不純物元素の濃度の方が、n型を付与する不純物元素の濃度より高く、半導体膜921はp型を有する半導体膜(p型の不純物領域を有する半導体膜ともいえる)となっているのがわる。また、p型を付与する不純物元素は、チャネルドープされるため、結晶性半導体膜903にも添加されている。図42(B)に示すように、半導体膜921の表面付近は9p型を付与する不純物元素濃度が比較的が高いp型の不純物領域(p+領域ともいう)922bとなっており、一方、結晶性半導体膜903に近づくにつれ、p型を付与する不純物元素濃度が比較的減少しておりp型の低濃度不純物領域(p-領域ともいう)922aとなっている。また、n型を付与する不純物元素の添加工程で、その添加条件によって、関表面の不純物元素濃度が高くなっている場合がある。このような場合は、膜表面を薄ングし、高不純物元素濃度領域の膜を除去してから、p型を付与する不純物元素を添加する工程を行えばよい。

### [0070]

本実施の形態では、半導体膜 4 0 6 a、半導体膜 4 0 6 bとして、 n型を付与する不純物元素(ドナー型元素)であるリンを含む n型を有する半導体膜をプラズマ C V D 法によって形成する。また、半導体膜 4 0 6 a、半導体膜 4 0 6 bに含まれる n型を付与する不純物元素の濃度を異ならせているので、半導体膜 4 0 6 a は n型の低濃度不純物領域となり、半導体膜 4 0 6 b は n型の高濃度不純物領域となっている。 n型の低濃度不純物領域の不純物濃度は、1 × 1 0 17 ~ 3 × 1 0 19 / c m³、好ましくは1 × 1 0 18 ~ 1 × 1 0 19 / c m³、 n型の高濃度不純物領域の不純物濃度は、その1 0 倍から1 0 0 倍が好ましく、1 × 1 0 19 ~ 3 × 1 0 21 / c m³とすることができる。また n型の低濃度不純物領域である半導体膜 4 0 6 a の膜厚は 2 0 ~ 2 0 0 n m、代表的には 5 0 ~ 1 5 0 n mであり、本実施の形態では、膜厚 5 0 n mで形成する。 n型の高濃度不純物領域である半導体膜 4 0 6 b の膜厚は 3 0 ~ 1 0 0 n m、代表的には 4 0 ~ 6 0 n mであり、本実施の形態では、膜厚 5 0 n mで形成する。

# [0071]

次に、非晶質半導体膜405を加熱して結晶性半導体膜407を形成するとともに、結晶化を助長する金属を半導体膜408a及び半導体膜408bにより吸い込むことで、結晶性半導体膜407中に含まれる結晶化を助長する金属を低減又は除去する。図9(C)に示すように、加熱処理により結晶化を助長する金属膜に接した半導体膜の部分でシリサイドが形成され、それを核として結晶化が進行する。また、結晶化とともに触媒金属は矢印の方向へ移動し、半導体膜408a、半導体膜408b中にゲッタリングされること

20

30

40

50

で結晶性半導体膜 4 0 7 中の触媒金属の濃度を、デバイス特性に影響を与えない濃度、即ち  $1 \times 1$  0 18 / c m 3 以下、望ましくは  $1 \times 1$  0 17 / c m 3 以下とすることができる。また、ゲッタリング後の金属触媒が移動した半導体膜 4 0 8 a 、半導体膜 4 0 8 b もも加熱処理により結晶化される場合がある。なお、本実施の形態においては、ゲッタリング工程と共に、半導体膜 4 0 8 a 、半導体膜 4 0 8 b 中の n 型を付与する不純物元素(ドナー型元素)の活性化を行っている。本実施の形態では、脱水素化のための熱処理の後、結晶化のための熱処理(5 5 0  $\sim 6$  5 0 で 5 分  $\sim 2$  4 時間)を行う。また、R T A 、G R T A により結晶化を行っても良い。本実施の形態のようにレーザ光照射を行わず結晶化することで、結晶性のばらつきを低減することが可能であり、後に形成される T F T のばらつきを抑制することが可能である。

[0072]

次に結晶性半導体膜407、半導体膜408a、半導体膜408bをマスクを用いてパターニングする。本実施の形態では、フォトマスクを作製し、フォトリソグラフィ法を用いたパターニング処理により、半導体層106、n型を有する半導体層107a、n型を有する半導体層107bを形成する(図4参照。)。フォトマスクはマスク102aを形成したときと同様にレジストをスピンコート法などによる全面塗布、または液滴吐出法によって選択的に形成し、レーザ光照射による露光によって微細なパターンのマスクを形成すればよい。微細なパターンのマスクによって半導体膜は微細かつ精巧に所望な形状にパターニングすることができる。

[0073]

マスクを露光加工せずに組成物を選択的に吐出して形成する場合、エポキシ樹脂、アクリル樹脂、フェノール樹脂、ノボラック樹脂、アクリル樹脂、メラミン樹脂、ウレタン樹脂等の樹脂材料を用いることができる。また、ベンゾシクロブテン、パリレン、フレア、透過性を有するポリイミドなどの有機材料、シロキサン系ポリマー等の重合によってできた化合物材料、水溶性ホモポリマーと水溶性共重合体を含む組成物材料等を用いて液滴吐出法で形成する。いずれの材料を用いるとしても、その表面張力と粘度は、溶媒の濃度を調整したり、界面活性剤等を加えたりして適宜調整する。

[0074]

パターニングの際のエッチング加工は、プラズマエッチング(ドライエッチング)又はウエットエッチングのどちらを採用しても良いが、大面積基板を処理するにはプラズマエッチングが適している。エッチングガスとしては、 $CF_4$ 、 $NF_3$ 、 $SF_6$ 、 $CHF_3$ などのフッ素系又は $C1_2$ 、 $BC1_3$ 、 $SiC1_4$ もしくは $CC1_4$ などを代表とする塩素系ガス、あるいは $O_2$ のガスを用い、He や Ar などの不活性ガスを適宜加えても良い。また、大気圧放電のエッチング加工を適用すれば、局所的な放電加工も可能であり、基板の全面にマスク層を形成する必要はない。

[0075]

導電性材料を含む組成物を吐出して、ソース電極層又はドレイン電極層130、ソース電極層又はドレイン電極層108、容量配線層104を形成し、該ソース電極層又はドレイン電極層108をマスクとして、半導体層106、 n型を有する半導体層107 a 及び n型を有する半導体層107 b をパターン加工して、半導体層115、 n型を有する半導体層116 a、 n型を有する半導体層116 b、 n型を有する半導体層117 a、 n型を有する半導体層117 b を形成する(図5参照。)。ソース電極層又はドレイン電極層130、ソース電極層又はドレイン電極層108を形成したときと同様に形成することができる。ソース電極層又はドレイン電極層130は配線層としても機能する。

[0076]

ソース電極層又はドレイン電極層 1 3 0、ソース電極層又はドレイン電極層 1 0 8 を形成する導電性材料としては、Ag(銀)、Au(金)、Cu(銅)、W(タングステン)、Al(アルミニウム)等の金属の粒子を主成分とした組成物を用いることができる。また、透光性を有するインジウム錫酸化物(ITO)、インジウム錫酸化物と酸化珪素から

20

30

40

なるITSO、有機インジウム、有機スズ、酸化亜鉛、窒化チタンなどを組み合わせても 良い。

## [0077]

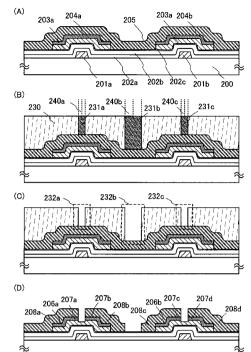

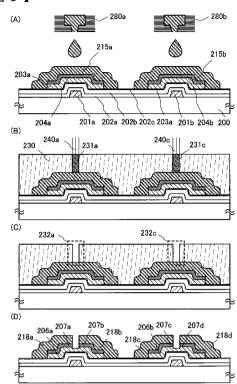

ソース電極層又はドレイン電極層の形成方法を図7及び図8を用いて説明する。ソース電極層又はドレイン電極層130及びソース電極層又はドレイン電極層108は、微細なパターンで形成されており、制御性よく形成しなければ形成不良によるショート等の不良を引き起こす。よって、半導体層上の微細なパターニングはレーザ光による微細な加工によって行う。図7(A)で示すように、基板200上にゲート電極層201a、ゲート電極層201b、ゲート絶縁層202c半導体層201b、ゲート絶縁層202c半導体層203a、半導体層203b、n型を有する半導体層204a、n型を有する半導体層205は蒸着法、CVD法、スパッタ法などによって形成することができる。その後、レジストからなるマスク230を形成する。

# [0078]

レジストからなるマスク230に、レーザ光240a、レーザ光240b、レーザ光2 40 c を照射し、露光することによって領域231 a、領域231 b、領域231 c を感 光する(図7(B)参照。)。本実施の形態ではポジ型の感光性のレジストを用いるため 、露光された領域231a、領域231b、領域231cはエッチャントによって除去さ れ、開口部232a、開口部232b、開口部232cが形成される(図7(C)参照。 )。開口部232a、開口部232b、開口部232cを有するマスクを用いて導電膜2 05をエッチングによりパターニングすることによって、ソース電極層又はドレイン電極 層208a、ソース電極層又はドレイン電極層208b、ソース電極層又はドレイン電極 層208c、ソース電極層又はドレイン電極層208dが形成される。本実施の形態では 、Agを用いて形成されたソース電極層及びドレイン電極層に、HNOョ溶液によるウェッ トエッチングを行い、その後02アッシングを行う。このソース電極層又はドレイン電極 層208a、ソース電極層又はドレイン電極層208b、ソース電極層又はドレイン電極 層 2 0 8 c 、ソース電極層又はドレイン電極層 2 0 8 d をマスクとして半導体層 2 0 3 a 、半導体層203b、n型を有する半導体層204a、n型を有する半導体層204bを エッチングし、半導体層206a、半導体層206b、n型を有する半導体層207a、 n型を有する半導体層207b、n型を有する半導体層207c、n型を有する半導体層 2 0 7 d を形成することができる(図 7 ( D )参照。)。このようにレーザ光による微細 な加工によりマスクを形成し、導電膜のパターニングを行うことで、制御性よく精密に導 電膜をパターニングでき、所望な形状のソース電極層やドレイン電極層を形成することが できる。よって形成不良が生じないために薄膜トランジスタの信頼性も向上する。

# [0079]

図8も図7と同様にレーザ光による露光工程を用いる導電膜のパターニング方法であるが、導電膜205を図7のように全面に形成せず、液滴吐出法によって選択的に形成する方法を示す。図7(A)のように半導体層を形成した後、液滴吐出装置280a、液滴吐出装置280bによって導電膜215a、導電膜215bが選択的に形成される(図8(A)参照。)。その後は同様にレジストをレーザ光によって露光し、微細なマスクを形成する。そのマスクを用いて、半導体チャネル形成領域上における導電膜215a、導電膜215bの微細なパターニングを行う。図8においては液滴吐出法により選択的に導電膜215bの微細なパターニングを行う。図8においては液滴吐出法により選択的に導電を形成する必要がない。また、エッチングによるパターニングを行っていないので得られるソース電極層又はドレイン電極層218a、ソース電極層又はドレイン電極層218b、ソース電極層又はドレイン電極層218bの端部は曲率半径を有するような丸みを帯びた形状となりうる。よって液滴吐出法を用いると、材料の口スも軽減し、工程も簡略化するため、コストが低く生産性が上がるという利点がある。

# [0800]

20

30

40

50

ソース電極層又はドレイン電極層 1 3 0、ソース電極層又はドレイン電極層 1 0 8 を 形成後もゲート電極層 1 0 3 の時と同様、プレス等による平坦化工程を行っても良い。ま た、ソース電極層又はドレイン電極層を液滴吐出法によって吐出し、仮焼成をしてから、 本焼成の間にプレス工程を挟むことによって、電極層の平坦化の他に、電極層に含まれる 酸素が放出され酸素濃度が低下するので、電気抵抗が下がるという効果もある。

## [0081]

ソース電極層又はドレイン電極層、半導体層、ゲート電極層、ゲート絶縁層を覆うようにパッシベーション膜となる絶縁膜109を成膜することが好ましい。絶縁膜109は、プラズマCVD法又はスパッタリング法などの薄膜形成法を用い、窒化珪素、酸化珪素、酸化全化アルミニウム、または酸化アルミニウム、ダイアモンドライクカーボン(DLC)、窒素含有炭素(CN)、その他の絶縁性材料を用いて形成することができる。なお、パッシベーション膜は単層でも積層構造でもよい。ここでは、半導体層115の界面特性から酸化珪素、又は酸化窒化珪素を形成したのち、外部からの不純物が半導体素子内に侵入するのを防ぐため窒化珪素、又は窒化酸化珪素を形成する積層構造が好ましい。本実施の形態では、半導体層115に接して、酸化珪素膜を膜厚150mm形成した後、同チャンバー内でガス切り替えを行い連続的に窒化珪素膜を膜厚200mm形成する積層構造で絶縁膜109を形成する。

## [0082]

この後、半導体層 1 1 5 を水素雰囲気又は窒素雰囲気で加熱して水素化することが好ましい。なお、窒素雰囲気で加熱する場合は、絶縁膜 1 0 9 として水素を含む絶縁膜を形成することが好ましい。

# [0083]

次に、絶縁層110を形成する。本実施の形態では、絶縁層110を全面に形成し、 レジスト等のマスクによって、エッチングしパターニングする。絶縁層110を、直接選 択的に形成できる液滴吐出法や印刷法などを用いて形成する場合は、エッチングによるパ ターニングは必ずしも必要はない。

### [0084]

絶縁層110は、酸化珪素、窒化珪素、酸化窒化珪素、酸化アルミニウム、窒化アルミニウム、酸化窒化アルミニウム、ダイアモンドライクカーボン(DLC)、窒素含有炭素膜(CN)その他の無機絶縁性材料、又はアクリル酸、メタクリル酸及びこれらの誘導体、又はポリイミド(polyimide)、芳香族ポリアミド、ポリベンゾイミダゾール(polybenzimidazole)、ベンゾシクロブテン、ポリシラザンなどの有機絶縁性材料、又はシロキサン系材料を出発材料として形成された珪素、酸素、水素からなる化合物のうちSi・O・Si結合を含む無機シロキサン、珪素上の水素がメチルやフェニルのような有機基によって置換された有機シロキサン系の絶縁材料で形成することができる。アクリル、ポリイミド等の感光性、非感光性の材料を用いて形成してもよい。

# [0085]

本実施の形態では、絶縁層110の材料としては、シリコン(Si)と酸素(O)との結合で骨格構造が構成され、置換基に水素、フッ素、アルキル基、または芳香族炭化水素のうち少なくとも1種を有する材料を用いた塗布膜を用いる。焼成した後の膜は、アルキル基を含む酸化珪素膜(SiOx)とも呼べる。

### [0086]

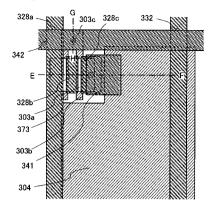

絶縁膜109及び絶縁層110にソース電極層又はドレイン電極層108に達する開口部135と、ゲート絶縁層105a、ゲート絶縁層105b、ゲート絶縁層105c、絶縁膜109、絶縁層110に、画素電極層111に達する開口部136、ゲート電極層103に達する開口部137を形成する。この開口部もレジストからなるマスクを用いてエッチングし形成する。パターニングに用いるマスクは、レーザ光の照射による露光を行うことで微細な形状を有するマスクとすることができる。このようにして形成した開口部135及び開口部137に配線層113を形成し、ソース電極層又はドレイン電極層108と画素電極層111を電気的に接続する。また、開口部137にもゲート電極層103

20

30

40

50

と電気的に接続するようにゲート配線層112を形成する。ゲート配線層112を低抵抗な材料によって形成することで、ゲート電極層103が多少高抵抗の材料であっても、高速動作が可能となり、大きな電流も流すことができる。

### [0087]

以上の工程により、基板100上にボトムゲート型(逆スタガ型ともいう。)の薄膜トランジスタと画素電極が接続された液晶表示パネル用のTFT基板が完成する。また本 実施の形態の薄膜トランジスタはチャネルエッチ型である。

## [0088]

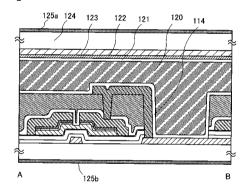

次に、図1に示すように、画素電極層111を覆うように、印刷法やスピンコート法により、配向膜と呼ばれる絶縁層114を形成する。図1は図2乃至6で示した上面図の線ABによる断面図であり、液晶表示パネルの完成図である。なお、絶縁層114は、スクリーン印刷法やオフセット印刷法を用いれば、選択的に形成することができる。その後、ラビングを行う。続いて、シール材を液滴吐出法により画素を形成した周辺の領域に形成する(図示せず。)。

### [0089]

その後、配向膜として機能する絶縁層121、カラーフィルタとして機能する着色層122、対向電極として機能する導電体層123、偏光板125aが設けられた対向基板124と、偏光板125bが設けられたTFTを有する基板100とをスペーサを介して貼り合わせ、その空隙に液晶層120を設けることにより液晶表示パネルを作製することができる(図1参照。)。シール材にはフィラーが混入されていても良く、さらに対向基板124には、遮蔽膜(ブラックマトリクス)などが形成されていても良い。なお、液晶層を形成する方法として、ディスペンサ式(滴下式)や、対向基板124を貼り合わせてから毛細管現象を用いて液晶を注入するディップ式(汲み上げ式)を用いることができる

### [0090]

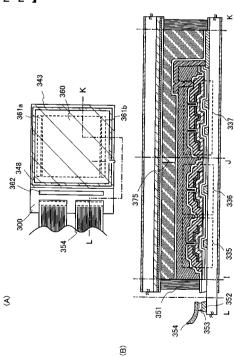

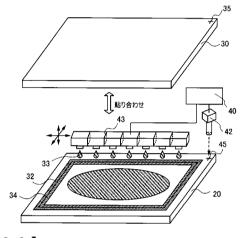

ディスペンサ方式を採用した液晶滴下注入法を図24を用いて説明する。図24において、40は制御装置、42は撮像手段、43はヘッド、33は液晶、35、41はマーカー、34はバリア層、32はシール材、30はTFT基板、20は対向基板である。シール材32で閉ループを形成し、その中にヘッド43より液晶33を1回若しくは複数回滴下する。ヘッド43は複数のノズルを備えており、一度に多量の液晶材料を滴下することができるためスループットが向上する。そのとき、シール材32と液晶33とが反応することを防ぐため、バリア層34を設ける。続いて、真空中で基板を貼り合わせ、その後紫外線硬化を行って、液晶が充填された状態とする。

## [0091]

以上の工程で形成された画素部と外部の配線基板を接続するために接続部を形成する。大気圧又は大気圧近傍下で、酸素ガスを用いたアッシング処理により、接続部の絶縁体層を除去する。この処理は、酸素ガスと、水素、 $CF_4$ 、 $NF_3$ 、 $H_2O$ 、 $CHF_3$ から選択された一つ又は複数とを用いて行う。本工程では、静電気による損傷や破壊を防止するために、対向基板を用いて封止した後に、アッシング処理を行っているが、静電気による影響が少ない場合には、どのタイミングで行っても構わない。

# [0092]

続いて、異方性導電体層を介して、液晶表示装置内の配線層が電気的に接続するように、接続用の配線基板を設ける。配線基板は、外部からの信号や電位を伝達する役目を担い、FPC(Flexible printed circuit)などを用いることができる。上記工程を経て、チャネルエッチ型のスイッチング用TFTと容量素子を含む液晶表示パネルが完成する。容量素子は、容量配線層104とゲート絶縁層105a、ゲート絶縁層105cと画素電極層111とで形成される。

### [0093]

液晶表示装置内の配線層とFPCは端子電極層を用いて接続され、端子電極層はゲート電極層と同材料及び同工程、ソース電極層及びドレイン電極層を兼ねるソース配線層と

同材料及び同工程、ゲート配線層と同材料同工程で、それぞれ作製することができる。 FPCと液晶表示装置内の配線層との接続例を図46を用いて説明する。

### [0094]

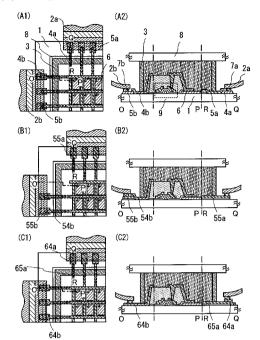

図46において、基板1上に薄膜トランジスタ9及び画素電極層6が形成され、シール材3で対向基板8と張り合わされている。液晶表示装置内から延長してシール材外部に形成される配線層とFPC2b及びFPC2aは異方性導電膜7a、異方性導電膜7bによって接着されている。

## [0095]

図46(A1)、(B1)、(C1)は液晶表示装置の上面図であり、図46(A2)、(B2)、(C2)は図46(A1)、(B1)、(C1)における線O-P、線R-Qの断面図である。図46(A1)、(A2)において、端子電極層5a及び端子電極層5bはゲート電極層と同材料同工程で形成されている。端子電極層5aにシール材外部に延長して形成されたソース配線層4aが接続され、端子電極層5aとFPC2aとが異方性導電膜7aを介して接続されている。一方端子電極層5bにシール材外部に延長して形成されたゲート配線層4bが接続され、端子電極層5bとFPC2bとが異方性導電膜7bを介して接続されている。

### [0096]

図46(B1)、(B2)において、端子電極層55a及び端子電極層55bはソース配線層と同材料同工程で形成されている。端子電極層55aはシール材外部に延長して形成されたソース配線層で形成され、端子電極層55aとFPC2aとが異方性導電膜7aを介して接続されている。一方、端子電極層55bにシール材外部に延長して形成されたゲート配線層54bが接続され、端子電極層55bとFPC2bとが異方性導電膜7bを介して接続されている。

### [0097]

図46(C1)、(C2)において、端子電極層64a及び端子電極層64bはゲート配線層と同材料同工程で形成されている。シール材外部に延長して形成されたソース配線層65aに端子電極層64aが接続され、端子電極層64aとFPC2aとが異方性導電膜7aを介して接続されている。一方、端子電極層64bはシール材外部に延長して形成されたゲート配線層で形成され、端子電極層64bとFPC2bとが異方性導電膜7bを介して接続されている。

### [0098]

本実施の形態では、スイッチングTFTはシングルゲート構造を示したが、ダブルゲート構造などのマルチゲート構造でもよい。

### [0099]

以上の工程により、結晶性半導体膜を有する逆スタガ型薄膜トランジスタを形成することができる。本実施の形態で形成される薄膜トランジスタは、結晶性半導体膜で形成される方とができる。本実施の形態で形成される薄膜トランジスタと比較して移動度(2~50cm²/Vsec程度)が高い。また、ソース領域及びドレイン領域には、一導電型を付与する不純物元素に加え、金属元素をも含む。このため、抵抗率の低いソース領域及びドレイン領域が形成できる。この結果、高速動作が必要な液晶表示装置を作製することが可能である。よってOCBモードのような応答速度が速く且つ高視野角な表示が可能な液晶表示装置を製造することが可能である。

## [0100]

また、非晶質半導体膜で形成される薄膜トランジスタと比較して、しきい値のずれが生じにくく、薄膜トランジスタ特性のバラツキを低減することが可能である。

# [0101]

更には、ゲッタリング工程により、成膜段階で半導体膜中に混入する金属元素をもゲッタリングするため、オフ電流を低減することが可能である。このため、このようなTFTを液晶表示装置のスイッチング素子に設けることにより、コントラストを向上させることが可能である。

10

20

30

### [0102]

また、レーザ光照射の微細な加工により、配線等の細線化も自由に設計できる。本発明により、所望なパターンを制御性よく形成でき、材料のロスも少なく、コストダウンも達成できる。よって高性能、高信頼性の液晶表示装置を歩留まりよく作製することができる。

## [0103]

### (実施の形態2)

本発明の実施の形態について、図10を用いて説明する。本実施の形態は、実施の形態 1 において、結晶化を助長するための金属を、非晶質半導体膜に接し、かつソース領域、ドレイン領域として機能する n 型を有する半導体膜に接して形成した例である。よって、同一部分又は同様な機能を有する部分の繰り返しの説明は省略する。

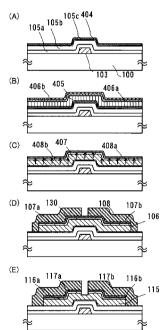

### [0104]

基板1500上にゲート電極層1501を形成し、ゲート電極層1501を覆うようにゲート絶縁層1502を形成する。本実施の形態ではゲート絶縁層1502は、窒化珪素膜、酸化珪素膜、窒化珪素膜の3層構造とするが、酸化珪素(SiOx)、窒化珪素(SiNxOy)(×>y)などの単層、又はこれらの積層構造を用いてもよい。

## [0105]

本実施の形態においては、ゲート絶縁層1502上に非晶質半導体膜1503を形成した後に金属膜1504を形成し、n型を有する半導体膜1505を形成する(図10(A)参照。)。

### [0106]

その後加熱処理により非晶質半導体膜1503を結晶化し、結晶性半導体膜1506を形成する。金属膜1504は、図10(B)の矢印の方向に移動し、結晶化に寄与した後、ゲッタリングシンクとして機能する半導体膜1507中に捕獲される。(図10(B)参照。)よって、結晶化を助長する金属が低減、又は除去された結晶性半導体膜1506を得ることができる。

## [0107]

結晶性半導体膜 1 5 0 6 と n 型を有する半導体膜 1 5 0 7 とをパターニングした後、ソース電極層又はドレイン電極層 1 5 0 8 a、ソース電極層又はドレイン電極層 1 5 0 8 bを形成する(図 1 0 (C)参照。)。

# [0108]

ソース電極層又はドレイン電極層1508a、ソース電極層又はドレイン電極層1508bをマスクとしてn型を有する半導体膜及び結晶性半導体膜をエッチングし、半導体層1509及びソース領域またはドレイン領域として機能するn型を有する半導体層1510bが形成される(図10(D)参照。)。

# [0109]

以上の工程により、実施の形態 1 と同様に、結晶性半導体膜を有する逆スタガチャネルエッチ型薄膜トランジスタを形成することができる。

### [0110]

本実施の形態は、実施の形態1と組み合わせて用いることが可能である。

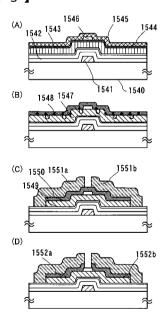

### (実施の形態3)

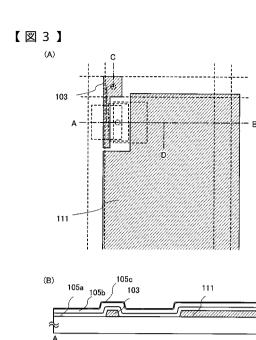

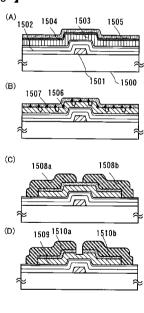

本発明の実施の形態について、図11及び図12を用いて説明する。本実施の形態は、実施の形態1において、チャネル保護膜を用いて、チャネル保護型薄膜トランジスタを形成する例である。よって、同一部分又は同様な機能を有する部分の繰り返しの説明は省略する。

### [0111]

基板1520上にゲート電極層1521を形成し、ゲート電極層1521を覆うようにゲート絶縁層1522を形成する。ゲート絶縁層1522上に金属膜1523を形成し、非晶質半導体膜1524を形成する。本実施の形態ではゲート絶縁層1522は、窒化

10

20

30

40

珪素膜、酸化珪素膜、窒化珪素膜の3層構造とするが、酸化珪素(SiOx)、窒化珪素(SiNx)、酸化窒化珪素(SiOxNy)(x>y)、窒化酸化珪素(SiNxOy)(x>y)などの単層、又はこれらの積層構造を用いてもよい。

#### [0112]

本実施の形態では、チャネル保護層となる絶縁層1525を形成する(図11(A)参照。)。絶縁層1525は、酸化珪素(SiOx)、窒化珪素(SiNx)、酸化窒化珪素(SiOxNy)(×>y)、窒化酸化珪素(SiNxOy)(×>y)などの単層、又は積層構造を適宜用いればよい。その後絶縁層1525をパターニングし、チャネル保護膜1526を形成する(図11(B)参照。)。次に、n型を有する半導体膜1527を形成する。(図11(C)参照)

### [0113]

その後加熱処理により非晶質半導体膜1524を結晶化し、結晶性半導体膜1528を形成する。金属膜1523は、図11(D)の矢印の方向に移動し、結晶化に寄与した後、ゲッタリングシンクとして機能する半導体膜1529中に捕獲される。(図11(D)参照。)よって、金属元素が低減、又は除去された結晶性半導体膜1528を得ることができる。

### [0114]

結晶性半導体膜 1 5 2 8 と n 型を有する半導体膜 1 5 2 9 とをパターニングした後、ソース電極層又はドレイン電極層 1 5 3 2 a、ソース電極層又はドレイン電極層 1 5 3 2 bを形成する(図 1 1 (E)参照。)。

### [0115]

ソース電極層又はドレイン電極層1532a、ソース電極層又はドレイン電極層1532 b をマスクとし、n型を有する半導体膜をエッチングし、ソース領域またはドレイン領域として機能するn型を有する半導体層1533a、n型を有する半導体層1533 b が形成される。チャネル保護膜1526がエッチングストッパとして機能するため、結晶性半導体膜1528はエッチングされない。(図11(F)参照。)

### [0116]

以上の工程により、結晶性半導体膜を有する逆スタガチャネル保護型薄膜トランジスタを形成することができる。実施の形態1と同様に、本実施の形態で形成される薄膜トランジスタは、結晶性半導体膜で形成されるため非晶質半導体膜で形成される薄膜トランジスタと比較して移動度(2~50cm²/Vsec程度)が高く、また、ソース領域及びドレイン領域には、一導電型を付与する不純物元素に加え、金属元素をも含むため、抵抗率の低いソース領域及びドレイン領域が形成できる。この結果、高速動作が必要な液晶表示装置を作製することが可能である。よってOCBモードのような応答速度が速く且つ高視野角な表示が可能な液晶表示装置を製造することが可能である。

### [ 0 1 1 7 ]

本実施の形態は、実施の形態1と組み合わせて用いることが可能である。

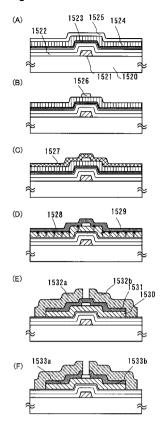

### (実施の形態4)

本発明の実施の形態について、図13を用いて説明する。本実施の形態は、実施の形態 1 において、結晶化を助長するための触媒金属を、非晶質半導体膜に接し、かつソース領域、ドレイン領域に接するように形成し、チャネル保護型薄膜トランジスタを形成する例である。よって、同一部分又は同様な機能を有する部分の繰り返しの説明は省略する。

## [0118]

基板1540上にゲート電極層1541を形成し、ゲート電極層1541を覆うようにゲート絶縁層1542を形成する。本実施の形態ではゲート絶縁層1542は、窒化珪素膜、酸化珪素膜、窒化珪素膜の3層構造とするが、酸化珪素(SiOx)、窒化珪素(SiNx)、酸化窒化珪素(SiOxNy)(×>y)、窒化酸化珪素(SiNxOy)(×>y)などの単層、又はこれらの積層構造を用いてもよい。

## [0119]

次に、本実施の形態においては、ゲート絶縁層1542上に非晶質半導体膜1543

10

20

30

40

を形成し、金属膜1544を形成する。次に実施の形態3と同様に絶縁膜をパターニングすることでチャネル保護層1546を形成する。その後n型を有する半導体膜1545を形成する(図13(A)参照。)。

## [0120]

加熱処理により非晶質半導体膜 1 5 4 3 を結晶化し、結晶性半導体膜 1 5 4 7 を形成する。金属膜 1 5 4 4 は、図 1 3 (B)の矢印の方向に移動し、結晶化に寄与した後、ゲッタリングシンクとして機能する半導体膜 1 5 4 8 中に捕獲される。(図 1 3 (B)参照。)よって、金属元素が低減、又は除去された結晶性半導体膜 1 5 4 7 を得ることができる。

## [0121]

結晶性半導体膜 1 5 4 9 と n 型を有する半導体膜 1 5 5 0 とをパターニングした後、ソース電極層又はドレイン電極層 1 5 5 1 a、ソース電極層又はドレイン電極層 1 5 5 1 bを形成する(図 1 3 (C)参照。)。

# [0122]

ソース電極層又はドレイン電極層 1 5 5 1 a、ソース電極層又はドレイン電極層 1 5 5 1 bをマスクとしn型を有する半導体膜をエッチングし、ソース領域またはドレイン領域として機能するn型を有する半導体層 1 5 5 2 a、n型を有する半導体層 1 5 5 2 bが形成される。(図 1 3 (D)参照。)

### [0123]

以上の工程により、結晶性半導体膜を有する逆スタガチャネル保護型薄膜トランジスタを形成することができる。実施の形態1と同様に、本実施の形態で形成される薄膜トランジスタは、結晶性半導体膜で形成されるため非晶質半導体膜で形成される薄膜トランジスタと比較して移動度(2~50cm²/Vsec程度)が高く、また、ソース領域及びドレイン領域には、一導電型を付与する不純物元素に加え、金属元素をも含むため、抵抗率の低いソース領域及びドレイン領域が形成できる。この結果、高速動作が必要な液晶表示装置を作製することが可能である。

### [0124]

本実施の形態は、実施の形態1と組み合わせて用いることが可能である。

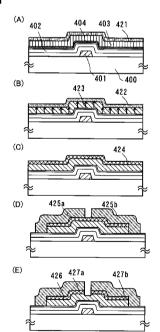

## (実施の形態5)

本発明の実施の形態について、図14を用いて説明する。本実施の形態は、実施の形態1において、結晶性半導体膜のゲッタリング工程が異なる例である。よって、同一部分又は同様な機能を有する部分の繰り返しの説明は省略する。

## [0125]

基板 4 0 0 上にゲート電極層 4 0 1 を形成し、ゲート電極層 4 0 1 を覆うようにゲート絶縁層 4 0 2 を形成する。ゲート絶縁層 4 0 2 上に金属膜 4 0 4 を形成し、非晶質半導体膜 4 0 3 を形成する。本実施の形態ではゲート絶縁層 4 0 2 は、窒化珪素膜、酸化珪素膜、窒化珪素膜の 3 層構造とするが、酸化珪素 (SiOx)、窒化珪素 (SiNx)、酸化窒化珪素 (SiOxNy) (x > y)、窒化酸化珪素 (SiNxOy) (x > y)などの単層、又はこれらの積層構造を用いてもよい。

# [0126]

本実施の形態では、結晶化を助長するための金属元素をゲッタリンするゲッタリングシンクとして、希ガス元素を不純物元素として含む半導体層421を形成する。希ガス元素は、ヘリウム、アルゴン、キセノン、クリプトンなどを用いることができ、本実施の形態ではアルゴンを不純物元素として含んだ半導体膜を形成する。(図14(A)参照)。

### [0127]

その後加熱処理により非晶質半導体膜403を結晶化し、結晶性半導体423を形成するとともに、結晶性半導体膜423中に含まれる金属元素は図14(B)の矢印の方向に移動し、半導体膜422中に捕獲される。よって膜中に含まれる金属元素が軽減された

10

20

30

40

結晶性半導体膜 4 2 3 が形成される。そして、ゲッタリングシンクとなっていた半導体膜 4 2 2、及び半導体膜 4 2 2上に形成された酸化膜をフッ酸等により除去し、金属元素が低減、又は除去された結晶性半導体膜 4 2 3を得ることができる。本実施の形態では、ゲッタリングシンクとなった半導体膜 4 2 2 の除去を T M A H (Tetramethyl ammonium hyd roxide)を用いて行う。結晶性半導体膜 4 2 3上に、図 1 4 (C)に示すように一導電型を有する半導体膜 4 2 4を形成し、パターニングした後、ソース電極層又はドレイン電極層 4 2 5 bを形成する(図 1 4 (D)参照。)。本実施の形態では、一導電型を有する半導体膜 4 2 4 として n 型を有する半導体膜を形成する。

[0128]

5

ソース電極層又はドレイン電極層 4 2 5 a、ソース電極層又はドレイン電極層 4 2 5 bをマスクとして n 型を有する半導体膜及び結晶性半導体膜をエッチングし、半導体層 4 2 6 及びソース領域またはドレイン領域として機能する n 型を有する半導体層 4 2 7 a、n 型を有する半導体層 4 2 7 b が形成される(図 1 4 (E)参照。)。

[0129]

以上の工程で、金属元素により結晶化した結晶性半導体膜にゲッタリングを行い、金属元素の軽減された半導体層を有し、かつソース領域またはドレイン領域として機能する 一導電型を有する半導体層中に金属元素の含まれない薄膜トランジスタを形成することが できる。

[0130]

本実施の形態は、実施の形態1と組み合わせて用いることが可能である。

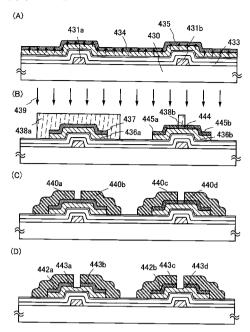

[0131]

(実施の形態6)

本発明の実施の形態として、図15を用いて説明する。本実施の形態は、nチャネル型薄膜トランジスタ及びpチャネル型薄膜トランジスタの2種類の薄膜トランジスタを作製する例である。よって、同一部分又は同様な機能を有する部分の繰り返しの説明は省略する。

[0132]

30

40

50

20

基板 4 3 0 上にゲート電極層 4 3 1 a、ゲート電極層 4 3 1 bを形成しゲート絶縁層 4 3 1 bを形成しゲート絶縁層 4 3 1 bを形成しゲート絶縁層 4 3 1 bを形成しゲート絶縁層 4 3 2 は、窒化珪素膜、酸化珪素膜、窒化珪素膜の 3 層構造とするが、酸化珪素(SiOx)、窒化珪素(SiNx)、酸化窒化珪素(SiOx Ny)(x > y)などの単層、又はこれらの積層構造を用いてもよい。ゲート絶縁層 4 3 3 上に、結晶化を助長する金属元素を添加し、非晶質半導体膜を形成し、n型を有する半導体膜 4 3 5を形成した後、加熱結晶化させ、結晶性半導体膜を形成する。結晶化にともない金属元素は矢印の方向にn型を有する半導体膜 4 3 5 中に移動し捕獲され、結晶性半導体膜中の金属元素が低減又は除去され、結晶性半導体膜 4 3 4 が形成される。(図 1 5 (A)参照。)。

[0133]

結晶性半導体膜434及びn型を有する半導体膜435をパターニングし、半導体層436a、半導体層436bを形成する。その後、半導体層436a及びn型を有する半導体層436b中のチャネル形成領域上のn型を有する半導体層436b中のチャネル形成領域上のn型を有する半導体層444を覆うマスク438bを形成し、p型を付与する不純物元素439をn型を有する半導体層に添加する。n型を有する半導体層は、n型を付与する不純物元素の濃度の2~10倍の濃度となるようにp型を付与する不純物元素を添加することによって、p型を有する半導体層にその導電型が反転し、p型の不純物領域445a、p型の不純物領域445bを形成することができる(図15(B)参照。)。

[0134]

ソース電極層又はドレイン電極層 4 4 0 a、ソース電極層又はドレイン電極層 4 4 0 b、ソース電極層又はドレイン電極層 4 4 0 c、ソース電極層又はドレイン電極層 4 4 0 dを液滴吐出法とレーザ光による微細な露光によって形成する(図 1 5 (C)参照。)。ソ

ース電極層又はドレイン電極層440a、ソース電極層又はドレイン電極層440b、ソース電極層又はドレイン電極層440c、ソース電極層又はドレイン電極層440dをマスクとして、半導体層436a、半導体層436b、n型を有する半導体層437、n型を有する半導体層4448m、半導体層442a、半導体層442b、n型を有する半導体層4438m、更型を有する半導体層443g。)。半導体層及びn型を有する半導体層のエッチングは、ソース電極層又はドレイン電極層のパターニングの際に形成したレジストマスクを設けた状態で行っても良い。また、エッチングはドライエッチングでもウェットエッチングで行っても良く、ソース電極層又はドレイン電極層のエッチングでもウェットエッチングで行っても良く、ソース電極層又はドレイン電極層のエッチングで方っても良い。

10

### [ 0 1 3 5 ]

以上の工程で同一基板上に、nチャネル型薄膜トランジスタ及びpチャネル型薄膜トランジスタを形成することができる。

## [0136]

本実施の形態は、実施の形態 1 乃至 5 それぞれと組み合わせて用いることが可能である。

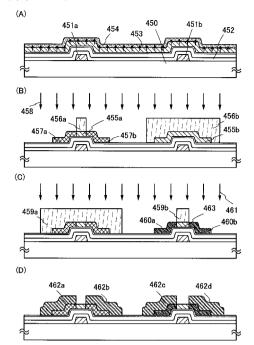

# [0137]

### (実施の形態7)

本発明の実施の形態として、図16を用いて説明する。本実施の形態は、nチャネル型薄膜トランジスタ及びpチャネル型薄膜トランジスタの2種類の薄膜トランジスタを作製する例である。よって、同一部分又は同様な機能を有する部分の繰り返しの説明は省略する。

20

### [0138]

基板 4 5 0 上にゲート電極層 4 5 1 a、ゲート電極層 4 5 1 bを形成しゲート絶縁層 4 5 2 を形成する。本実施の形態ではゲート絶縁層 4 5 2 は、窒化珪素膜、酸化珪素膜、窒化珪素膜の 3 層構造とするが、酸化珪素(SiOx)、窒化珪素(SiNx)、酸化窒化珪素(SiOxNy)(× > y)などの単層、又はこれらの積層構造を用いてもよい。ゲート絶縁層 4 5 2 上に金属元素を添加し、非晶質半導体膜を形成し、希ガス元素を不純物元素として含む半導体膜を形成し、加熱結晶化させる(図 1 6 (A)参照。)。

30

# [0139]

加熱処理により、非晶質半導体膜が結晶化され結晶性半導体膜453が形成されるとともに、結晶化を助長する金属元素は矢印の方向に移動し、希ガス元素を有する半導体膜454中に捕獲される。ゲッタリングシンクとして用いた半導体膜454をエッチングによって除去する。結晶性半導体膜453をパターニングし、チャネル形成領域455aを覆うマスク456bを形成し、n型を付与する不純物元素458を添加し、n型の不純物領域457a、n型の不純物領域457bを形成する(図16(B)参照。)。

[0140]

40

マスク456a、及びマスク456bを除去し、新たにn型の不純物領域457a、チャネル形成領域455a、n型の不純物領域457bを覆うマスク459a、チャネル形成領域463を覆うマスク459bを形成し、p型を付与する不純物元素461を添加する。p型を付与する不純物元素によってp型の不純物領域460a、p型の不純物領域460bを形成する(図16(C)参照。)。n型の不純物領域457a、n型の不純物領域457b、p型の不純物領域460bはソース領域またはドレイン領域として機能する。ソース領域又はドレイン領域に接してソース電極層又はドレイン電極層462a、ソース電極層又はドレイン電極層462dが形成される(図16(D)参照。)。

## [0141]

以上の工程で同一基板上に、 n チャネル型薄膜トランジスタ及び p チャネル型薄膜トランジスタを形成することができる。実施の形態 6 と比べ成膜工程が削減できるため、スループットを向上させることが可能である。

# [0142]

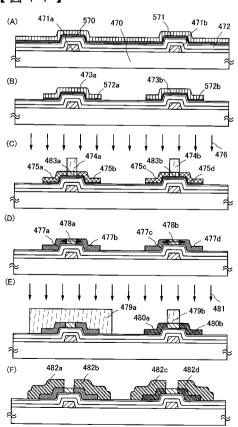

## (実施の形態8)

本発明の実施の形態として、図17を用いて説明する。本実施の形態は、nチャネル型薄膜トランジスタ及びpチャネル型薄膜トランジスタの2種類の薄膜トランジスタを作製する例であり、ゲッタリングの工程が異なる例である。よって、同一部分又は同様な機能を有する部分の繰り返しの説明は省略する。

### [0143]

基板 4 7 0 上にゲート電極層 4 7 1 a、ゲート電極層 4 7 1 bを形成しゲート絶縁層 4 7 2 を形成する。本実施の形態ではゲート絶縁層 4 7 2 は、窒化珪素膜、酸化珪素膜、窒化珪素膜の 3 層構造とするが、酸化珪素(SiOx)、窒化珪素(SiNx)、酸化窒化珪素(SiOx Ny)(x > y)などの単層、又はこれらの積層構造を用いてもよい。ゲート絶縁層 4 7 2 上に、金属膜 5 7 0 を形成し、非晶質半導体膜 5 7 1 を形成する(図 1 7 ( A )参照。)。非晶質半導体膜 5 7 1 及び金属膜 5 7 0 をパターニングし、半導体層 4 7 3 a、半導体層 4 7 3 b、金属層 5 7 2 a、金属層 5 7 2 bを形成する(図 1 7 ( B )参照。)。

# [0144]

チャネル形成領域483aを覆うマスク474a、チャネル形成領域483bを覆うマスク474bを形成し、n型を付与する不純物元素476を添加し、n型の不純物領域475a、n型の不純物領域475c、n型の不純物領域475dを形成する(図17(C)参照。)。その後加熱処理を行う。

### [0145]

加熱処理により、半導体中のチャネル形成領域 4 8 3 a 及びチャネル形成領域 4 8 3 b が結晶化するとともに、半導体層中のチャネル形成領域 4 8 3 a、チャネル形成領域 4 8 3 b に含まれる金属元素はゲッタリングされ、それぞれ矢印の方向に n 型の不純物領域 4 7 7 a、 n 型の不純物領域 4 7 7 c、 n 型の不純物領域 4 7 7 d に移動し捕獲され、金属元素が除去、軽減されたチャネル形成領域 4 7 8 a、チャネル形成領域 4 7 8 b が形成される(図 1 7 (D)参照。)。また、この熱処理によって、添加された n 型を付与する不純物元素の活性化も行うことができる。

### [0146]

n型の不純物領域477a、チャネル形成領域478a、n型の不純物領域477bを覆うマスク479a、チャネル形成領域478bを覆うマスク479bを形成し、p型を付与する不純物元素481を添加する。p型を付与する不純物元素によってp型の不純物領域480a、p型の不純物領域477b、p型の不純物領域477a、n型の不純物領域477b、p型の不純物領域480a、p型の不純物領域480bはソース領域またはドレイン領域として機能する。ソース領域又はドレイン領域に接してソース電極層又はドレイン電極層482a、ソース電極層又はドレイン電極層482a、ソース電極層又はドレイン電極層482dが形成される(図17(F)参照。)。

## [0147]

以上の工程で同一基板上に、 n チャネル型薄膜トランジスタ及び p チャネル型薄膜トランジスタを形成することができる。実施の形態 6 と比べ成膜工程が削減できるため、スループットを向上させることが可能である。

### [0148]

# (実施の形態9)

本実施の形態を、図18乃至23を用いて説明する。本実施の形態は、画素領域を実施の形態1で作製した画素領域で、画素が有する薄膜トランジスタがマルチゲート型である

10

20

30

40

20

30

40

50

場合を適用したものである。また、周辺駆動回路領域も本発明を用いた薄膜トランジスタにより作製され、実施の形態6で作製されるnチャネル型薄膜トランジスタ及びpチャネル型薄膜トランジスタからなるCMOSを適用している。よって、同一部分又は同様な機能を有する部分の繰り返しの説明は省略する。

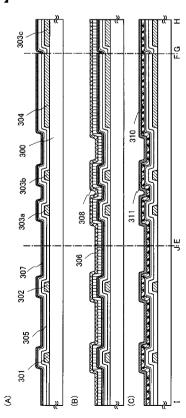

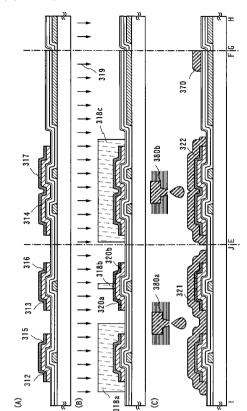

## [0149]

図23は本実施の形態で作製する液晶表示装置の画素領域の上面図であり、図18乃至図21、図22(B)は、各工程の図23におけるの線E-F、G-Hの断面図である。また、図18乃至図21におけるI-Jの領域は、図22(A)の液晶表示装置の周辺駆動回路領域である線I-Jに対応する断面図である。

### [ 0 1 5 0 ]

基板300上に導電膜を形成し、レジストからなるマスクによってパターニングを行い、ゲート電極層301、ゲート電極層302、ゲート電極層303a、ゲート電極層303b、ゲート電極層303c、画素電極層304を形成する。本実施の形態では、ゲート電極層を透明導電膜の単層で形成するが、積層構造としてもよい。積層構造としては、TaN、W、Mo、Cr、前記元素の窒化膜などの積層を用いることはでき、具体的にはTaN、W、TaN、Mo、TaN、Cr、TiN、W、TiN、Mo、TiN、Crなどを用いることができる。本実施の形態では、液滴吐出法によって酸化珪素を含むインジウム錫酸化物(ITSO)を含む組成物を吐出し、焼成してゲート電極層形成領域を含む近傍に導電膜を形成する。この導電膜をレーザ光による露光によって微細に加工されたマスクを用いて、精密にパターニングし、ゲート電極層301、ゲート電極層302、ゲート電極層303a、ゲート電極層303c、画素電極層304を形成する。

# [0151]

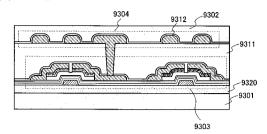

ゲート電極層301、ゲート電極層302、ゲート電極層303a、ゲート電極層303b、ゲート電極層303c、画素電極層304上にゲート絶縁層305を実施の形態1と同様に3層構造で形成し、ゲート絶縁層305上に結晶化を促進、助長する元素として、金属膜307を形成する(図18(A)参照。)。金属膜307は非常に膜厚が薄いため膜としての形状を保っていない場合がある。本実施の形態では、ゲート絶縁層305として、窒化珪素からなる絶縁層をプラズマCVD法により50nm形成し、酸化珪素からなる絶縁層をプラズマCVD法により100nm形成し、窒化珪素からなる絶縁層5nmをプラズマCVD法により形成する。次に、Niを100ppmを含有した水溶液をスピンコーティング法により塗布し、金属膜307を形成する。

### [0152]

次に、非晶質半導体膜306を形成し、n型を有する半導体膜308を形成する。本実施の形態では、非晶質半導体膜306として非晶質珪素膜をプラズマCVD法により200nm形成し、n型を有する半導体膜308として、n型を付与する不純物元素としてリン(P)を含む非晶質珪素膜をプラズマCVD法により100nm形成する。(図18(B)参照。)。

## [0153]

非晶質半導体膜306を加熱し、結晶化させ、結晶性半導体膜310を形成する。加熱処理により、金属元素は結晶化を助長しながら矢印の方向へ移動し、n型を有する半導体膜311中に捕獲されるため、結晶性半導体膜310は、膜中の金属元素が軽減されており、n型を有する半導体膜311は、n型を付与する不純物元素(本実施の形態ではP)と金属元素(本実施の形態ではNi)を含むn型を有する膜となる。(図18(C)参照。)本実施の形態では、550で4時間加熱処理を行い、結晶性半導体膜310を形成する(図18(C)参照。)。

### [0154]

結晶性半導体膜 3 1 0 及び n 型を有する半導体膜 3 1 1 をパターニングし、半導体層 3 1 2、半導体層 3 1 3、半導体層 3 1 4、 n 型を有する半導体層 3 1 5、 n 型を有する半導体層 3 1 7 を形成することができる(図 1 9 ( A

20

30

40

50

)参照。)。これらの半導体層のパターニングも、本発明のレーザ光による露光によって 微細に加工されたマスクを用いて、精密にパターニングすることができる。

### [0155]

次に、半導体層 3 1 2、 n 型を有する半導体層 3 1 5 を覆うマスク 3 1 8 a、半導体層 3 1 6 のチャネル形成領域及び n 型を有する半導体層 3 1 6 のチャネル形成領域を覆うマスク 3 1 8 b、半導体層 3 1 4 及び n 型を有する半導体層 3 1 7 を覆うマスク 3 1 8 cを形成する。 p 型を付与する不純物元素 3 1 9 を添加し、 p 型を有する半導体層 3 1 6 中に、 p 型の不純物領域 3 2 0 bを形成する(図 1 9 ( B )参照。)。本実施の形態では、イオンドーピング法を用いて p 型を付与する不純物元素を添加する。その後、5 5 0 で 4 時間加熱処理を行い、不純物元素の添加領域を活性化する

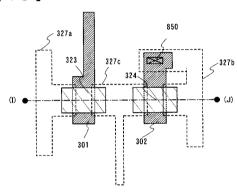

[0156]

次に、駆動回路領域において、CMOS構成を用いてインバーターとして機能させている。PMOSのみ、NMOSのみの構成の場合においては、一部のTFTのゲート電極層とソース電極層又はドレイン電極層とを接続させる。このような例を図43に示す。フォトマスクを用いてゲート絶縁層305の一部をエッチングして、図43に示すようなコンタクトホール850を形成する。本実施の形態では、画素電極層とソース電極層又はドレイン電極層又はドレイン電極層とソース電極層とソース電極層又はドレイン電極層と対って電極層でからないで接続してもよい。この場合、それがでは、電極層に達する開口部を、コンタクトホール850と同時に形成することができる。そのゲート電極層、コンタクトホール850と同時に形成することができる。それゲート電極層、又は画素電極層と電気的に接続する。ソース電極層又はドレイン電極層327ちとゲート電極層302を接続することによってNMOS同士、PMOS同士であってもインバーターとしてきのうさせることができる。前述したように本実施の形態では、薄膜トランジスタ335と薄膜トランジスタ336とはCMOS構成となっているので図43で示す構造としなくてもインバーターとして機能させることができる。

[ 0 1 5 7 ]

マスク318a、マスク318b及びマスク318cを除去した後、半導体層312、半導体層313及び半導体層314上に、導電層321、導電層322を形成する。本実施の形態では、液滴吐出法を用いて、選択的に導電層321、導電層322を形成し、材料の口スを軽減する。導電性材料として銀(Ag)を用い、液滴吐出装置380a、液滴吐出装置380bよりAgを含む組成物を吐出し、300 で焼成して、導電層321、導電層322を形成する(図19(C)参照。)。また、同工程で、容量配線層となる導電層370も、画素電極層304上のゲート絶縁層305上に形成する。

[0158]

## [0159]

以上の工程で、CMOSを構成するnチャネル型薄膜トランジスタ335及びpチャネル型薄膜トランジスタ336、nチャネル型薄膜トランジスタ337、容量素子338を形成することができる(図20(A)参照。)。本実施の形態ではCMOS構造としたが、本発明はそれに限定されず、PMOS構造でもNMOS構造としてもよい。

## [0160]

パッシベーション膜となる絶縁膜330を形成する。本実施の形態では、絶縁膜330を、半導体層に接する側から、膜厚150nmの酸化珪素膜と膜厚200nmの窒化珪素膜との積層膜で形成する。絶縁膜330は、他の珪素を含む膜で形成しても良く、酸化珪素膜の代わりに酸化窒化珪素膜を用い、酸化窒化珪素膜と窒化珪素膜の積層としてもよい。

### [0161]

絶縁膜330には酸素を含ませるように形成し、温度300~500 窒素雰囲気下で加熱処理を行い、半導体層の水素化を行う。

## [0162]

絶縁膜330上に絶縁層339を形成する。本実施の形態では、スリッドコーターを用いて、アルキル基を含む酸化珪素膜を形成する。絶縁層339、絶縁膜330にソース電極層又はドレイン電極層328bに達する開口部340aを、絶縁層339、絶縁膜330、ゲート絶縁層305に、画素電極層304に達する開口部340b及びゲート電極層303cに達する開口部340cを形成する(図20(B)参照。)。開口部を形成するパターニングには、本発明のレーザ光による微細加工を用いることができる。また、本実施の形態では、ドライエッチングにより開口部を形成する。

### [0163]

次にゲート配線層341及びゲート配線層342を形成する。本実施の形態では、ゲート配線層を、Agを用い、液滴吐出法によって形成する。導電性材料としてAgを含む組成物を開口部340a、開口部340b、開口部340cに吐出し、300 で焼成する。以上の工程より、ソース電極層又はドレイン電極層328bと画素電極層304を電気的に接続するゲート配線層341と、ゲート電極層303cと電気的に接続するゲート配線層342を形成する(図20(C)参照。)。

# [0164]

図23に本実施の形態で作製する液晶表示装置の画素領域の上面図を示す。画素領域に設けられる薄膜トランジスタはマルチゲート型である。画素領域には、ゲート電極層303b、画素電極層304、半導体層373、ソース電極層又はドレイン電極層328b、ソース電極層又はドレイン電極層328b、ソース電極層又はドレイン電極層328b、ソース電極層又はドレイン電極層328c、容量配線層332、ゲート配線層342、ゲート配線層341である。

# [0165]

次に、図21に示すように、画素電極層304を覆って、印刷法やスピンコート法により、配向膜と呼ばれる絶縁層343を形成する。なお、絶縁層343は、スクリーン印刷法やオフセット印刷法を用いれば、選択的に形成することができる。その後、ラビング処理を行う。続いて、シール材351を画素を形成した周辺の領域に形成する。

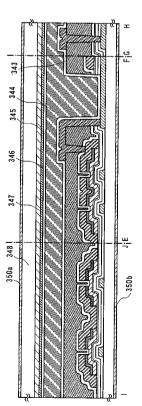

### [0166]

その後、配向膜として機能する絶縁層 3 4 5、カラーフィルタとして機能する着色層 3 4 6、対向電極として機能する導電体層 3 4 7、偏光板 3 5 0 a が設けられた対向基板 3 4 8 と、偏光板 3 5 0 b が設けられた基板 3 0 0 とをスペーサ 3 7 5 を介して貼り合わせ、その空隙に液晶層 3 4 4 を設けることにより液晶表示パネルを作製することができる(図 2 2 参照。)。スペーサは、スペーサは数 μ m の粒子を散布して設ける方法でも良いが、本実施の形態では基板全面に樹脂膜を形成した後これをパターニングして形成する方法を採用した。このようなスペーサの材料を、スピナーで塗布した後、露光と現像処理によって所定のパターンに形成する。さらにクリーンオープンなどで 1 5 0 ~ 2 0 0 で加

10

20

30

40

20

30

40

50

熱して硬化させる。このようにして作製されるスペーサは露光と現像処理の条件によって形状を異ならせることができるが、好ましくは、スペーサの形状は柱状で頂部が平坦な形状となるようにすると、対向側の基板を合わせたときに液晶表示パネルとしての機械的な強度を確保することができる。形状は円錐状、角錐状などを用いることができ、特別な限定はない。シール材にはフィラーが混入されていても良く、さらに対向基板348には、遮蔽膜(ブラックマトリクス)などが形成されていても良い。また、液晶表示装置内部と外部を電気的に接続するための端子電極層352に、異方性導電膜353によってFPC354が接着され、端子電極層352と電気的に接続する。

## [0167]

本実施の形態で示す図22の液晶表示装置は、ゲート電極層301、ゲート電極層302、ゲート電極層303a、ゲート電極層303b、画素電極層304を単層構造で示しているが、前述したように、ゲート電極層を2層以上の複数層積層してもよい。ゲート電極層及び容量配線層を積層構造にした例を図47に示す。

### [0168]

積層構造としては、Ta、Ti、W、Mo、Cr、前記元素の窒化膜などの積層を用いることはでき、具体的にはTaN\W、TaN\Mo、TaN\Cr、TiN\W、TiN\M、TiN\Crなどを用いることができる。本実施の形態では第1のゲート電極層301a、第1のゲート電極層302a、第1のゲート電極層303a1、第1のゲート電極層303b1、第1のゲート電極層303c1としてTaNを用い、第2のゲート電極層301b、第2のゲート電極層303c2としてWを用いる。同工程でのゲート電極層303b2、第2のゲート電極層303c2としてWを用いる。同工程で形成される画素電極層においても、第1の画素電極層304aとしてTaN膜を、第2の画素電極層304bとしてW膜を形成する。このようにゲート電極層及び画素電極層を積置を積置としてもよく、反対に、画素電極層を単層構造としゲート電極層を単層構造としてもよく、反対に、画素電極層を積層構造としゲート電極層を単層構造としてもよく、反対に、画素電極層を積層構造としゲート電極層を単層構造としてもよく、反対に、画素電極層を単層構造としゲート電極層を単層構造としてもよい。液晶表示装置に要求される機能に応じて適宜設定すればよい。

### [0169]

以上の工程により、結晶性半導体膜を有する逆スタガ型薄膜トランジスタを形成することができる。本実施の形態で形成される薄膜トランジスタは、結晶性半導体膜で形成されるため非晶質半導体膜で形成される薄膜トランジスタと比較して移動度が高い。また、ソース領域及びドレイン領域には、一導電型を付与する不純物元素に加え、金属元素をも含む。このため、抵抗率の低いソース領域及びドレイン領域が形成できる。この結果、高速動作が必要な液晶表示装置を作製することが可能である。よってOCBモードのような応答速度が速く且つ高視野角な表示が可能な液晶表示装置を製造することが可能である。

# [0170]

また、非晶質半導体膜で形成される薄膜トランジスタと比較して、しきい値のずれが 生じにくく、薄膜トランジスタ特性のバラツキを低減することが可能である。

### [0171]

更には、ゲッタリング工程により、成膜段階で半導体膜中に混入する金属元素をもゲッタリングするため、オフ電流を低減することが可能である。このため、このような薄膜トランジスタを液晶表示装置のスイッチング素子に設けることにより、コントラストを向上させることが可能である。

## [0172]

# (実施の形態10)

実施の形態 1 では、ゲート電極層と、ソース電極層又はドレイン電極層(ソース配線層も含む)及び容量配線層とがゲート絶縁層を介して積層し、ソース電極層又はドレイン電極層(ソース配線層も含む)とゲート配線層とが層間絶縁層を介して積層している多層構造を用いている。本実施の形態では、これらの積層構造が異なる例を図 2 8 乃至図 3 9、及び図 4 4 を用いて説明する。図 3 4 (A) 乃至図 3 9 (A) は、液晶表示装置の上面図であり、図 3 4 (B) 乃至図 3 6 (B) は、図 3 4 (A) 乃至図 3 6 (A) において線

X 1 - V 1 による断面図である。図 3 4 (A) 乃至図 3 6 (A) は、液晶表示装置の上面図であり、図 3 4 (B) 乃至図 3 9 (B) は、図 3 4 (A) 乃至図 3 9 (A) において線X 1 - V 1 による断面図である。

## [0173]

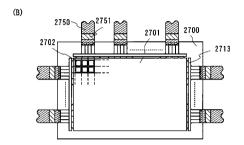

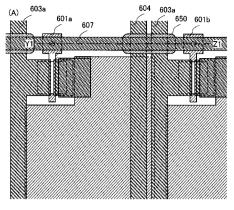

図34(A)は、液晶表示装置の上面図であり、図34(B)は、図34(A)における線X1-V1による断面図、図34(C)は、図34(A)における線M-Nによる断面図である。図34に示す液晶表示装置は、実施の形態1で示すようにソース電極層又はドレイン電極層と画素電極層が、ゲート配線層によって電気的に接続されている構造ではなく、ソース電極層又はドレイン電極層610が直接、画素電極層611と接するように形成され、電気的に接続している構造である。このように直接ソース電極層又はドレイン電極層610が画素電極層611に接続する構造でもよく、反射型液晶表示装置ならば、反射性を有する材料をソース電極層又はドレイン電極層610に用い、画素電極層611と積層するような構造であってもよい。

# [0174]

図34において、液晶表示装置の画素領域内には、基板600上にゲート電極層601a、ゲート電極層601b、画素電極層611、ゲート絶縁層602、容量配線層604、ソース電極層又はドレイン電極層603a、ソース電極層又はドレイン電極層603b、ゲート配線層607、半導体層608、n型を有する半導体層609a、n型を有する半導体層609b、パッシベーション膜である絶縁膜605、絶縁層606が形成されている。ゲート絶縁層602は実施の形態1と同様に3層構造とする。

### [ 0 1 7 5 ]

絶縁膜605は必ずしも必要ではないが、絶縁膜605を形成すると、パッシベーション膜として機能するので、より液晶表示装置の信頼性が向上する。また、絶縁膜605を形成し、熱処理を行うと、絶縁膜605中に含まれる水素によって半導体層の水素化を行うことができる。

# [0176]

図34(B)で示すようにソース電極層又はドレイン電極層603bは、層間絶縁層である絶縁層606を介して、ゲート配線層607と積層しており、ゲート配線層607は、ゲート電極層601a、ゲート電極層601bと絶縁層606、絶縁膜605、ゲート絶縁層602に形成されたコンタクトホールで接続されている。よってゲート配線層607と、ソース電極層又はドレイン電極層603b及び容量配線層604とはショートしない構造となっている。

### [0177]

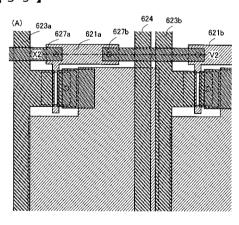

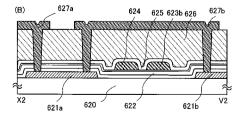

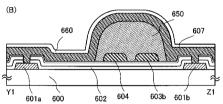

図35(A)は、液晶表示装置の上面図であり、図35(B)は、図35(A)における線X2・V2による断面図である。図35において、液晶表示装置の画素領域内には、基板620上にゲート電極層621a、ゲート電極層621b、ゲート絶縁層622、容量配線層624、ソース電極層又はドレイン電極層623a、ソース電極層又はドレイン電極層623b、ゲート配線層627a、ゲート配線層627b、パッシベーション膜である絶縁膜625、絶縁層626が形成されている。ゲート絶縁層622は実施の形態1と同様に3層構造とする。

# [0178]

図35(B)で示すようにソース電極層又はドレイン電極層623bは、層間絶縁層である絶縁層626を介して、ゲート配線層627bと積層しており、ゲート配線層627bは、ゲート電極層621a、ゲート電極層621bと絶縁層626、絶縁膜625、ゲート絶縁層622に形成されたコンタクトホールで接続されている。よってゲート配線層627bと、ソース電極層又はドレイン電極層623b及び容量配線層624とはショートしない構造となっている。また、図35で示す液晶表示装置は、ゲート配線層とゲート電極層は連続的ではなく断続的に形成され、お互いにコンタクトホールを介して電気的な接続を取りながら形成されている構造となっている。よって、ソース電極層又はドレイン電極層623b、容量配線層624が形成されている領域では、ゲート電極層621a

10

20

30

40

とゲート電極層621bとは、絶縁膜660上に形成するゲート配線層627bとコンタクトホールにおいて接続することで電気的に接続されている。

### [0179]

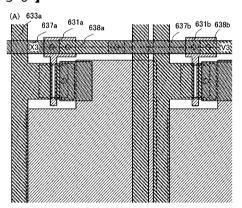

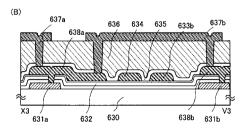

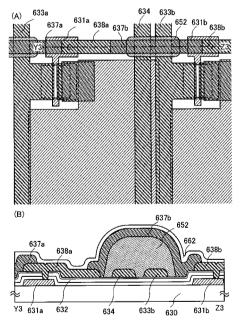

図36(A)は、液晶表示装置の上面図であり、図36(B)は、図36(A)における線X3-V3による断面図である。図36において、液晶表示装置の画素領域内には、基板630上にゲート電極層631a、ゲート電極層631b、ゲート絶縁層632、容量配線層634、ソース電極層又はドレイン電極層633a、ソース電極層又はドレイン電極層633b、ゲート配線層637b、配線層638a、配線層638b、パッシベーション膜である絶縁膜635、絶縁層636が形成されている。ゲート絶縁層632は実施の形態1と同様に3層構造とする。

[0180]

図36(B)で示すようにソース電極層又はドレイン電極層633bは、層間絶縁層である絶縁層636を介して、ゲート配線層637bと積層している。図35で示す液晶表示装置において、ゲート電極層621aとゲート配線層627a及びゲート配線層627bとは直接接続している。しかし図36で示す液晶表示装置では、ゲート電極層631aと、ゲート配線層637bとは、ソース電極層と同材料、同工程で形成される配線層638aとコンタクトホールで接続31aはゲート絶縁層638aとコンタクトホールで接続31aはゲート絶縁層632上に形成される配線層638aとコンタクトホールで接続10元線層638aは、ゲート配線層637a及びゲート配線層637bとコンタクトホールを介して接続する。よって、ゲート電極層637aとコンタクトホールで接続して記線層637bとコンタクトホールを介して接続する。よって、ゲート電極層637bとコンタクトホートの記線層637bと電気的に接続する。ソース電極層又はドレイン電極層637bと積層2元を配線層637bと積層2元を配線層637bと積層2元を配線層637bとはショートしない構造となっている。

[0181]

図34、図35及び図36は層間絶縁層として絶縁層を、広範囲にわたって覆うように形成した場合を示した。図37、図36及び図39は配線層間を隔てる層間絶縁層を、液滴吐出法を用いて必要な個所のみに選択的に形成する例を示す。

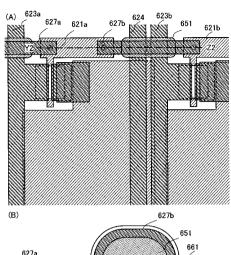

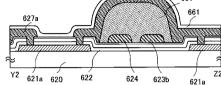

[0182]

図37は図34に、図38は図35に、図39は図36の液晶表示装置にそれぞれ対応しており、層間絶縁層の構造が異なる構造となっている。図37(A)は、液晶表示装置の上面図であり、図37(B)は、図37(A)における線Y1-Z1による断面図である。図37において、ソース電極層又はドレイン電極層603b及び容量配線層604を覆うように絶縁層650が液滴吐出法により形成されている。その絶縁層650上を跨ぐようにゲート配線層607が形成されている。ゲート配線層607上には、パッシベーション膜として絶縁膜660が形成されている。絶縁膜660は必ずしも必要ではないが、形成することで信頼性を向上させることができる。また本実施の形態では、絶縁層650単層で形成するが、絶縁層650の上、または下に絶縁膜を形成して積層構造としてもよい。

[0183]

図38(A)は、液晶表示装置の上面図であり、図38(B)は、図38(A)における線Y2-Z2による断面図である。図38においても図37と同様に、ソース電極層又はドレイン電極層623b及び容量配線層624を覆うように絶縁層651が、液滴吐出法により選択的に形成されている。その絶縁層651上を跨ぐようにゲート配線層627bが形成され、ゲート電極層621aとコンタクトホールにより接続されている。ゲート配線層627a上には、パッシベーション膜として絶縁膜661が形成されている。

[0184]

図39(A)は、液晶表示装置の上面図であり、図39(B)は、図39(A)における線Y3-Z3による断面図である。図36においても図34と同様に、ソース電極層又はドレイン電極層633b及び容量配線層634を覆うように絶縁層652が、液滴吐出

10

20

30

40

法により選択的に形成されている。その絶縁層652上を跨ぐようにゲート配線層637 bが形成され、配線層638aを介してゲート配線層637a及びゲート電極層631a と電気的に接続している。

### [0185]

絶縁層650、絶縁層651、絶縁層652のように配線層間のショートを防くための絶縁層を、液滴吐出法を用いて選択的に形成すると、材料のロスが軽減する。また、直接配線間が接するように形成することができるので、絶縁層にコンタクトホールを形成する工程が減る。よって、工程が簡略化し低いコスト、高い生産性を得ることができる。

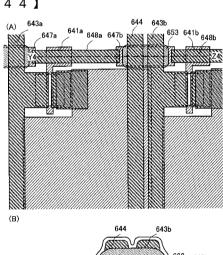

## [0186]

図43の液晶表示装置もソース電極層又はドレイン電極層643b及び容量配線層644と配線層647bを物理的に隔てるために設ける絶縁層653を液滴吐出法を用いて選択的に形成する例である。図37乃至図39における液晶表示装置では、絶縁層上にゲート配線層を跨ぐように形成することで、ソース電極層又はドレイン電極層とゲート配線層とのショートを防いでいた。図44の液晶表示装置では、ゲート電極層641a、ゲート電極層641bを形成する工程で、配線層647a、配線層647bを形成する。配線層647a、配線層647bを形成する。配線層647a、配線層647bを形成する。配線層647a、配線層647bた覆うゲート絶縁層の一部をエッチングによって除去する。配線層647b上の一部に絶縁層653を液滴吐出法によって選択的に形成し、絶縁層653上にソース電極層又はドレイン電極層643a、容量配線層644を形成する。ソース電極層又はドレイン電極層643a、容量配線層644を形成する。のと同工程で、配線層648a、配線層648bとは、絶縁層653の下で記線層647bによって電気的に接続されている。このように、絶縁層653の下層でゲート電極層を電気的に接続することができる。

#### [0187]

以上の工程で示すように、信頼性の高い液晶表示装置を低コストで生産性よく作製することができる。

#### [0188]

## (実施の形態11)

次に、実施の形態1乃至10によって作製される液晶表示パネルに駆動用のドライバ回路を実装する態様について説明する。

## [0189]

まず、COG方式を採用した液晶表示装置について、図33(A)を用いて説明する。基板2700上には、文字や画像などの情報を表示する画素部2701が設けられる。複数の駆動回路が設けられた基板を、矩形状に分断し、分断後の駆動回路(以下ドライバICと表記)2751は、基板2700上に実装される。図33(A)は複数のドライバIC2751、該ドライバIC2751の先にFPC2750を実装する形態を示す。また、分割する大きさを画素部の信号線側の辺の長さとほぼ同じにし、単数のドライバICに、該ドライバICの先にテープを実装してもよい。

## [0190]

また、TAB方式を採用してもよく、その場合は、図33(B)で示すように複数のテープを貼り付けて、該テープにドライバICを実装すればよい。COG方式の場合と同様に、単数のテープに単数のドライバICを実装してもよく、この場合には、強度の問題から、ドライバICを固定する金属片等を一緒に貼り付けるとよい。

#### [0191]

これらの表示パネルに実装されるドライバICは、生産性を向上させる観点から、一辺が300mmから1000mm以上の矩形状の基板上に複数個作り込むとよい。

#### [0192]

つまり、基板上に駆動回路部と入出力端子を一つのユニットとする回路パターンを複数 個形成し、最後に分割して取り出せばよい。ドライバICの長辺の長さは、画素部の一辺 10

20

30

40

20

30

40

50

の長さや画素ピッチを考慮して、長辺が15~80mm、短辺が1~6mmの矩形状に形成してもよいし、画素領域の一辺、又は画素部の一辺と各駆動回路の一辺とを足した長さに形成してもよい。

## [0193]

ドライバICのICチップに対する外形寸法の優位性は長辺の長さにあり、長辺が15~80mmで形成されたドライバICを用いると、画素部に対応して実装するのに必要な数がICチップを用いる場合よりも少なくて済み、製造上の歩留まりを向上させることができる。また、ガラス基板上にドライバICを形成すると、母体として用いる基板の形状に限定されないので生産性を損なうことがない。これは、円形のシリコンウエハからICチップを取り出す場合と比較すると、大きな優位点である。

[0194]

また、図32(B)のように走査線側の駆動回路3704は基板上に一体形成される場合、画素領域3701の外側の領域には、信号線側の駆動回路駆動回路が形成されたドライバICが実装される。これらのドライバICは、信号線側の駆動回路である。RGBフルカラーに対応した画素領域を形成するためには、XGAクラスで信号線の本数が3072本必要であり、UXGAクラスでは4800本が必要となる。このような本数で形成された信号線は、画素領域3701の端部で数ブロック毎に区分して引出線を形成し、ドライバICの出力端子のピッチに合わせて集められる。

[0195]

ドライバICは、基板上に形成された結晶質半導体により形成されることが好適であり、本発明を用いた薄膜トランジスタを用いることができる。また移動度や応答速度が良好なために高速駆動が可能で、従来よりも素子の動作周波数を向上させることができ、特性バラツキが少ないために高い信頼性を得ることができる。

[0196]

画素領域は、信号線と走査線が交差してマトリクスを形成し、各交差部に対応してトランジスタが配置される。画素領域に配置されるトランジスタとしても、本発明を用いた薄膜トランジスタを適用することができる。本発明を適用して作製される薄膜トランジスタは、簡略化した工程で比較的高移動度が得られるため、大画面の液晶表示装置を作製する上で有効である。従って、この薄膜トランジスタを画素のスイッチング用素子や、走査線側の駆動回路を構成する素子として用いることができる。従って、システムオンパネル化を実現した表示パネルを作製することができる。

[0197]

図33(A)、(B)のように走査線駆動回路及び信号線駆動回路の両方として、ドライバICを実装してもよい。その場合には、走査線側と信号線側で用いるドライバICの仕様を異なるものにするとよい。

[0198]

その場合には、走査線側と信号線側で用いるドライバICの仕様を異なるものにすることが好適である。例えば、走査線側のドライバICを構成するトランジスタには30V程度の耐圧が要求されるものの、駆動周波数は100kHz以下であり、比較的高速動作は要求されない。従って、走査線側のドライバを構成するトランジスタのチャネル長(L)は十分大きく設定することが好適である。一方、信号線側のドライバICのトランジスタには、12V程度の耐圧があれば十分であるが、駆動周波数は3Vにて65MHz程度であり、高速動作が要求される。そのため、ドライバを構成するトランジスタのチャネル長などはミクロンルールで設定することが好適である。なおチャネル長方向とは、チャネル形成領域において、電流が流れる方向、換言すると電荷が移動する方向と一致する。

[0199]

ドライバICの実装方法は、特に限定されるものではなく、公知のCOG方法やワイヤボンディング方法、或いはTAB方法を用いることができる。

[0200]

ドライバICの厚さは、対向基板と同じ厚さとすることで、両者の間の高さはほぼ同じ

ものとなり、液晶表示装置全体としての薄型化に寄与する。また、それぞれの基板を同じ材質のもので作製することにより、この液晶表示装置に温度変化が生じても熱応力が発生することなく、TFTで作製された回路の特性を損なうことはない。その他にも、本実施の形態で示すようにICチップよりも長尺のドライバICで駆動回路を実装することにより、1つの画素領域に対して、実装されるドライバICの個数を減らすことができる。

#### [0201]

以上のようにして、液晶表示パネルに駆動回路を組み入れることができる。

## [0202]

#### (実施の形態12)

本実施の形態では、上記実施の形態において、ゲート電極層とソース電極層及びドレイン電極層との端部の位置関係、即ちゲート電極層の幅とチャネル長の大きさの関係について、図28を用いて説明する。

#### [0203]

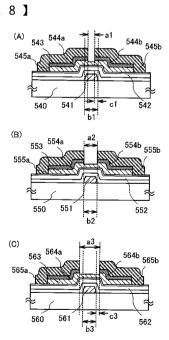

図28(A)は基板540上に形成された、ゲート電極層541、ゲート絶縁層542、半導体層543、一導電性を有する半導体層544a、一導電性を有する半導体層544b、ソース電極層又はドレイン電極層545a、ソース電極層又はドレイン電極層545bからなる薄膜トランジスタである。本実施の形態ではゲート絶縁層542は、窒化珪素膜、酸化珪素膜、窒化珪素膜の3層構造とするが、酸化珪素(SiOx)、窒化珪素(SiNxOy)、変化珪素(SiOxNy)、マ>y)、窒化酸化珪素(SiNxOy)(x>y)などの単層、又はこれらの積層構造を用いてもよい。

### [0204]

図28(A)は、ゲート電極層541上をソース電極層及びドレイン電極層545a、ソース電極層及びドレイン電極層545bの端部がc1だけ重なっている。ここでは、ソース電極層及びドレイン電極層545bとが重なっている領域をオーバーラップ領域と呼ぶ。即ち、ゲート電極層の幅b1がチャネル長a1よりも大きい。オーバーラップ領域の幅c1は、(b1-a1)/2で表される。このようなオーバーラップ領域を有するnチャネルTFTは、ソース電極層及びドレイン電極層と、半導体領域との間に、n+領域とn-領域とを有することが好ましい。この構造により、電界の緩和効果が大きくなり、ホットキャリア耐性を高めることが可能となる

## [0205]

図28(B)は基板550上に形成された、ゲート電極層551、ゲート絶縁層552、半導体層553、一導電性を有する半導体層554a、一導電性を有する半導体層554b、一導電性を有する半導体層554b、ソース電極層又はドレイン電極層555bからなる薄膜トランジスタである。本実施の形態ではゲート絶縁層552は、窒化珪素膜、酸化珪素膜、窒化珪素膜の3層構造とするが、酸化珪素(SiOx)、窒化珪素(SiNxOy)、窒化珪素(SiNxOy)、変化珪素(SiOxNy)、文はこれらの積層構造を用いてもよい。

## [0206]

図28(B)は、ゲート電極層551の端部と、ソース電極層及びドレイン電極層555a、ソース電極層及びドレイン電極層555bの端部が一致している。即ち、ゲート電極層の幅b2とチャネル長a2とが等しい。

## [0207]

図28(C)は基板560上に形成された、ゲート電極層561、ゲート絶縁層562、半導体層563、一導電性を有する半導体層564a、一導電性を有する半導体層564b、ソース電極層又はドレイン電極層565a、ソース電極層又はドレイン電極層565bからなる薄膜トランジスタである。本実施の形態ではゲート絶縁層562は、窒化珪素膜、酸化珪素膜、窒化珪素膜の3層構造とするが、酸化珪素(SiOx)、窒化珪素(SiNxOy)(x>y)などの単層、又はこれらの積層構造を用いてもよい。

20

10

30

50

#### [0208]

図28(C)は、ゲート電極層561とソース電極層及びドレイン電極層565a、ソース電極層及びドレイン電極層565aの端部とがc3だけ離れている。ここでは、ここでは、ゲート電極層561と、ソース電極層及びドレイン電極層565a、ソース電極層及びドレイン電極層565a、ソース電極層及びドレイン電極層565a、ソース電極層及びドレイン電極層565a、ソース電極層及びドレイン電極層565a、ソース電極層及びドレイン電極層565a、ソース電極層及びドレイン電極層565a、ソース電極層及びドレイン電極層565a、ソース電極層及びドレイン電極層565a、ソース電極層及びドレイン電極層565a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、ソース電極層365a、アース電極層365a、アース電極層365a、アース電極層365a、アース電極層365a、アース電極層365a、アース電極層365a、アース電極層365a、アース電極層365a、アース電極層365a、アース電極層365a、アース電極層365a、アース電極層365a、アース電極層365a、アース電極層365a、アース電極層365a、アース電極層365a、アース電極層365a、アース電極層365a、アース電極層365a、アース電極層365a、アース電極層365a、アース電極層365a、アース電極層365a、アース電極層365a、アース電極層365a、アース電極層365a、アース電極層365a、アース電磁角365a、アース電磁角365a、アース電磁角365a、アース電磁角365a、アース電磁角365a、アース電磁角365a、アース電磁角365a、アース電磁角365a、アース電磁角365a、アース電磁角365a、アース電磁角365a、アース電磁角365a、アース電磁角365a、アース電磁角365a、アース電磁角365a、アース電磁角365a、アース電磁角365a、アース電磁角365a、アース電磁角365a、アース電磁角365a、アース電磁角365a、アース電磁角365a、アース電磁角365a、アース電磁角365a、アース電磁角365a、アース電磁角365a、アース電磁角365a、アース電磁角365a、アース電磁角365a、アース電磁角365a、アース電磁角365a、アース電磁角365a、アース電磁角365a、アース電磁角365a、アース電磁角365a、アー

## [0209]

さらには、半導体領域が複数のゲート電極を覆ういわゆるマルチゲート構造のTFTと しても良い。この様な構造のTFTも、オフ電流を低減することができる。

#### [0210]

## (実施の形態13)

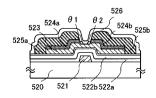

上記実施の形態において、チャネル形成領域表面に対して垂直な端部を有するソース電極層及びドレイン電極層を示したが、この構造に限定されない。図27に示すように、チャネル形成領域表面に対して90度より大きく、180度未満、好ましくは95~140度、さらに好ましくは135度~140度を有する端部であってもよい。また、ソース電極層とチャネル形成領域表面との角度を 1、ドレイン電極層とチャネル形成領域表面との角度を 2とすると、 1と 2が等しくてもよい。また、異なっていてもよい。このような形状のソース電極及びドレイン電極は、ドライエッチング法により形成することが可能である。

## [0211]

#### (実施の形態14)

本実施の形態では、上記実施の形態に適応可能な半導体膜の結晶化工程を図26を用いて説明する。

### [0212]

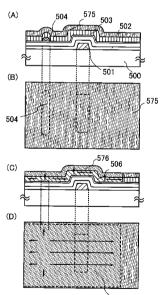

図26において、基板500上に、ゲート電極層501、ゲート絶縁層502が形成されている。ゲート絶縁層502上に、液滴吐出法などにより選択的に金属層507を形成し、半導体膜503を形成し、n型を有する半導体膜575を形成する。半導体膜を加熱すると、図26(B)の矢印で示すように、金属層507と半導体膜との接触部分から、基板の表面に平行な方向へ結晶成長が発生し、結晶性半導体膜506が形成するとともに、結晶化を助長する金属元素はn型を有する半導体膜576に捕獲される。なお、金属層507から、かなり離れた部分では結晶化は行われず、非晶質部分が残存する。本実施の形態ではゲート絶縁層502は、窒化珪素膜、酸化珪素膜、窒化珪素膜の3層構造とするが、酸化珪素(SiOxNy)(x>y)、窒化酸化珪素(SiNxOy)(x>y)などの単層、又はこれらの積層構造を用いてもよい。

## [0213]

このように、基板に平行な方向への結晶成長を横成長またはラテラル成長と称する。 横成長により大粒径の結晶粒を形成することができるため、より高い移動度を有する薄膜 トランジスタを形成することができる。

#### [0214]

## (実施の形態15)

本発明の表示装置に具備される保護回路の一例について説明する。

#### [0215]

図33で示すように、外部回路と内部回路の間に保護回路2713を形成することができる。保護回路は、TFT、ダイオード、抵抗素子及び容量素子等から選択された1つ又は複数の素子によって構成されるものであり、以下にはいくつかの保護回路の構成とその動作について説明する。まず、外部回路と内部回路の間に配置される保護回路であって、1つの入力端子に対応した保護回路の等価回路図の構成について、図45を用いて説明す

10

20

30

40

20

30

40

50

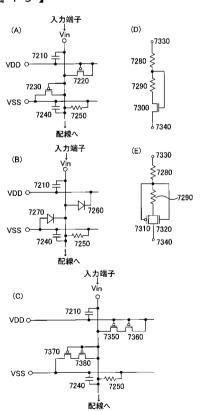

る。図45(A)に示す保護回路は、pチャネル型薄膜トランジスタ7220、7230、容量素子7210、7240、抵抗素子7250を有する。抵抗素子7250は2端子の抵抗であり、一端には入力電圧Vin(以下、Vinと表記)が、他端には低電位電圧VSS(以下、VSSと表記)が与えられる。

## [0216]

## [0217]

#### (実施の形態16)

上記実施の形態により作製される液晶表示パネルによって、液晶テレビジョン装置を完成させることができる。液晶表示パネルには、図32(A)で示すような構成として画素部のみが形成されて走査線側駆動回路と信号線側駆動回路とが、図33(B)のようなTAB方式により実装される場合と、図33(A)のようなCOG方式により実装される場合と、図32(B)に示すようにSASでTFTを形成し、画素部と走査線側駆動回路を基板上に一体形成し信号線側駆動回路を別途ドライバICとして実装する場合、また図32(C)のように画素部と信号線側駆動回路と走査線側駆動回路を基板上に一体形成する場合などがあるが、どのような形態としても良い。

### [0218]

その他の外部回路の構成として、映像信号の入力側では、チューナで受信した信号のうち、映像信号を増幅する映像信号増幅回路と、そこから出力される信号を赤、緑、青の各色に対応した色信号に変換する映像信号処理回路と、その映像信号をドライバICの入力仕様に変換するためのコントロール回路などからなっている。コントロール回路は、走査線側と信号線側にそれぞれ信号が出力する。デジタル駆動する場合には、信号線側に信号分割回路を設け、入力デジタル信号をm個に分割して供給する構成としても良い。

## [0219]

チューナで受信した信号のうち、音声信号は、音声信号増幅回路に送られ、その出力は 音声信号処理回路を経てスピーカに供給される。制御回路は受信局(受信周波数)や音量 の制御情報を入力部から受け、チューナや音声信号処理回路に信号を送出する。

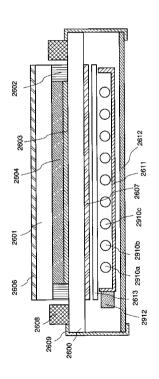

## [0220]

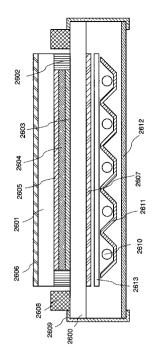

図25は液晶表示モジュールの一例であり、TFT基板2600と対向基板2601がシール材2602により固着され、その間に画素部2603と液晶層2604が設けられ表示領域を形成している。着色層2605はカラー表示を行う場合に必要であり、RGB方式の場合は、赤、緑、青の各色に対応した着色層が各画素に対応して設けられている。TFT基板2600と対向基板2601の外側には偏光板2606、2607、レンズフィルム2613が配設されている。光源は冷陰極管2610と反射板2611により構成され、回路基板2612は、フレキシブル配線基板2609によりTFT基板2600と接続され、コントロール回路や電源回路などの外部回路が組みこまれている。液晶表示モジュールには、TN(Twisted Nematic)モード、IPS(In-Plane-Switching)モード、MVA(Multi-domain Vertica1 Alignment)モード、ASM(Axially Symmetric allgned Micro-cell)モード、OCBモードなどを用いることができる

## [0221]

また、本発明で作製する液晶表示装置は高速応答が可能なOCBモードを用いることでより高性能化することができる。図48は図25の液晶表示モジュールにOCBモードを適用した一例であり、FS-LCD(Field seauential-LCD)となっている。FS-LCDは、1フレーム期間に赤色発光と緑発光と青発光をそれぞれ行うものであり、各発光を発光ダイオード等で行うので、カラーフィルターが不要である。よって、3原色のカラーフィルターを並べる必要がないため同じ面積で9倍の画素を表示できる。一方、1フレーム期間に3色の発光を行うため、液晶の高速な応答が求められる。

[0222]

本発明の液晶表示装置の有する薄膜トランジスタは高速作動することができるため、OCBモードを用いることができる。OCBモードの液晶層は、いわゆる セル構造を有している。 セル構造とは、液晶分子のプレチルト角がアクティブマトリクス基板と対向基板との基板間の中心面に対して面対称の関係で配向された構造である。 セル構造の配向状態は、基板間に電圧が印加されていない時はスプレイ配向となり、電圧を印加するとベンド配向に移行する。さらに電圧を印加するとベンド配向の液晶分子が両基板と垂直に配向し、光が透過する状態となる。なお、OCBモードにすると、従来のTNモードより約10倍速い高速応答性を実現できる。

[0223]

よって、本発明の液晶表示装置に、FS方式、及びOCBモードを適用することができる。 一層高性能で高画質な液晶表示装置、また液晶テレビジョンを完成させることができる。 また、FS方式に対応するモードとして、強誘電性液晶(FLC:Ferroelect ric Liquid Crystal)を用いたHV-FLC、SS-FLCなども用 いることができる。代表的にはOCBモードは粘度の比較的低いネマチック液晶が用いられるが、液晶材料とし れ、HV-FLC、SS-FLCには、スメクチック液晶が用いられるが、液晶材料とし ては、FLC、ネマチック液晶、スメクチック液晶などの材料を用いることができる。図 48の液晶表示モジュールは透過型の液晶表示モジュールを示しており、光源として赤色 光源2910a、緑色光源2910b、青色光源2910cが設けられている。光源は赤 色光源2910a、緑色光源2910b、青色光源2910cをそれぞれオンオフを制御 するために、制御部2912が設置されている。制御部2912によって、各色の発光は 制御され、液晶に光は入射し、時間分割を用いて画像を合成し、カラー表示が行われる。

[0224]

また、液晶表示モジュールの高速光学応答速度は、液晶表示モジュールのセルギャップを狭くすることで高速化する。また液晶材料の粘度を下げることでも高速化できる。上記高速化は、TNモードの液晶表示モジュールの画素領域の画素、またはドットピッチが30μm以下の場合に、より効果的である。

[0225]

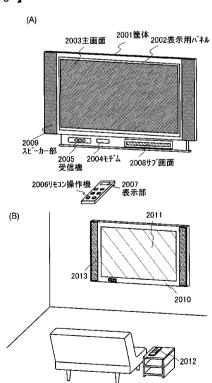

これらの液晶表示モジュールを、図40(A)に示すように、筐体2001に組みこんで、液晶テレビジョン装置を完成させることができる。液晶表示モジュールにより主画面2003が形成され、その他付属設備としてスピーカ部2009、操作スイッチなどが備えられている。このように、本発明により液晶テレビジョン装置を完成させることができる。

[0226]

筐体2001に液晶素子を利用した表示用パネル2002が組みこまれ、受信機2005により一般のテレビ放送の受信をはじめ、モデム2004を介して有線又は無線による通信ネットワークに接続することにより一方向(送信者から受信者)又は双方向(送信者と受信者間、又は受信者間同士)の情報通信をすることもできる。液晶テレビジョン装置の操作は、筐体に組みこまれたスイッチ又は別体のリモコン装置2006により行うことが可能であり、このリモコン装置にも出力する情報を表示する表示部2007が設けられていても良い。

10

20

30

40

#### [0227]

また、液晶テレビジョン装置にも、主画面2003の他にサブ画面2008を第2の表示用パネルで形成し、チャネルや音量などを表示する構成が付加されていても良い。主画面2003及びサブ画面2008を主画面2003とサブ画面を低消費電力で表示可能な液晶表示用パネルで形成しても良い。本発明を用いると、このような大型基板を用いて、多くのTFTや電子部品を用いても、信頼性の高い液晶表示装置とすることができる。

### [0228]

図40(B)は例えば20~80インチの大型の表示部を有するテレビジョン装置であり、筐体2010、表示部2011、操作部であるリモコン装置2012、スピーカー部2013等を含む。本発明は、表示部2011の作製に適用される。図40(B)のテレビジョン装置は、壁かけ型となっており、設置するスペースを広く必要としない。

#### [0229]

勿論、本発明はテレビジョン装置に限定されず、パーソナルコンピュータのモニタをは じめ、鉄道の駅や空港などにおける情報表示盤や、街頭における広告表示盤など特に大面 積の表示媒体として様々な用途に適用することができる。

#### [0230]

## (実施の形態17)

本発明を適用して、様々な液晶表示装置を作製することができる。即ち、それら液晶表示装置を表示部に組み込んだ様々な電子機器に本発明を適用できる。

## [0231]