# (19) 대한민국특허청(KR)(12) 공개특허공보(A)

(11) 공개번호 10-2019-0024568(43) 공개일자 2019년03월08일

리-신 로드 6, 넘버 8

리-신 로드 6, 넘버 8

(51) 국제특허분류(Int. Cl.)

H01L 27/088 (2006.01) H01L 21/8234 (2006.01) H01L 29/66 (2006.01) H01L 29/78 (2006.01) H01L 29/788 (2006.01)

(52) CPC특허분류

H01L 27/0886 (2013.01) H01L 21/823431 (2013.01)

(21) 출원번호 10-2018-0012998

(22) 출원일자 **2018년02월01일** 심사청구일자 **2018년02월01일**

(30) 우선권주장

62/551,624 2017년08월29일 미국(US) 15/799,611 2017년10월31일 미국(US)

리앙 치아 밍

모르 이-시엔 주하미구 타

중화민국, 타이완, 신추, 신추 사이언스 파크, 리-신 로드 6, 넘버 8

중화민국, 타이완, 신추, 신추 사이언스 파크,

타이완 세미콘덕터 매뉴팩쳐링 컴퍼니 리미티드

중화민국, 타이완, 신추, 신추 사이언스 파크,

(뒷면에 계속)

(74) 대리인

(71) 출원인

(72) 발명자

김태홍, 김진희

전체 청구항 수 : 총 10 항

### (54) 발명의 명칭 핀 임계 치수 로딩 최적화

### (57) 요 약

최적화 핀 임계 치수 로딩을 가지는 집적 회로 디바이스가 본원에 개시된다. 예시적인 집적 회로 디바이스는 제 1 멀티-핀 구조체를 포함하는 코어 영역 및 제2 멀티-핀 구조체를 포함하는 입력/출력 영역을 포함한다. 제1 멀티-핀 구조체는 제1 폭을 가지고 제2 멀티-핀 구조체는 제2 폭을 가진다. 제1 폭은 제2 폭보다 더 크다. 일부구현에서, 제1 멀티-핀 구조체는 제1 핀 간격을 가지고 제2 멀티-핀 구조체는 제2 핀 간격을 가진다. 제1 핀 간격은 제2 핀 간격보다 더 작다. 일부 구현에서, 제1 멀티-핀 구조체의 제1 인접 핀 피치는 최소 핀 피치의 3배보다 크거나 같고 제2 멀티-핀 구조체의 제2 인접 핀 피치는 최소 핀 피치의 2배보다 작거나 같다.

#### 대 표 도 - 도6a

(52) CPC특허분류

HO1L 29/66795 (2013.01) HO1L 29/7831 (2013.01) HO1L 29/7885 (2013.01)

(72) 발명자

### 치우 후아이-시엔

중화민국, 타이완, 신추, 신추 사이언스 파크, 리 -신 로드 6, 넘버 8

### 창 치-신

중화민국, 타이완, 신추, 신추 사이언스 파크, 리 -신 로드 6, 넘버 8

### 엔지 진-안

중화민국, 타이완, 신추, 신추 사이언스 파크, 리 -신 로드 6, 넘버 8

### 리 이-주에이

중화민국, 타이완, 신추, 신추 사이언스 파크, 리 -신 로드 6, 넘버 8

### 명세서

### 청구범위

#### 청구항 1

집적 회로 디바이스에 있어서,

제1 멀티-핀 구조체를 포함하는 코어 영역; 및

제2 멀티-핀 구조체를 포함하는 입력/출력 영역

을 포함하고,

상기 제1 멀티-핀 구조체는 제1 폭을 가지고 상기 제2 멀티-핀 구조체는 제2 폭을 가지고, 상기 제1 폭은 상기 제2 폭보다 더 큰 것인, 집적 회로 디바이스.

### 청구항 2

제1항에 있어서,

상기 제1 멀티-핀 구조체는 제1 핀 간격을 가지고 상기 제2 멀티-핀 구조체는 제2 핀 간격을 가지고, 상기 제1 핀 간격은 상기 제2 핀 간격보다 더 작은 것인, 집적 회로 디바이스.

#### 청구항 3

제1항에 있어서,

상기 제1 멀티-핀 구조체는 2개 이하의 핀을 가지고, 상기 제1 멀티-핀 구조체의 제1 인접 핀 피치(adjacent fin pitch)는 최소 핀 피치의 3배보다 크거나 같고,

상기 제2 멀티-핀 구조체는 3개 이상의 핀을 가지고, 상기 제2 멀티-핀 구조체의 제2 인접 핀 피치는 상기 최소 핀 피치의 2배보다 작거나 같은 것인, 집적 회로 디바이스.

#### 청구항 4

제1항에 있어서,

상기 제2 멀티-핀 구조체는 인터-핀 폭(inter-fin width)을 가지는 인터-핀 및 인트라-핀 폭(intra-fin width)을 가지는 인트라-핀을 포함하고, 상기 인터-핀 폭은 상기 인트라-핀 폭보다 더 큰 것인, 집적 회로디바이스.

### 청구항 5

제4항에 있어서,

상기 인터-핀은 최소 핀 피치의 3배보다 크거나 같은 인터-핀 인접 핀 피치(inter-fin adjacent fin pitch)를 가지고.

상기 인트라-핀은 상기 최소 핀 피치의 2배보다 작거나 같은 인트라-핀 인접 핀 피치(intra-fin adjacent fin pitch)를 가지는 것인, 집적 회로 디바이스.

### 청구항 6

제1항에 있어서,

상기 제1 멀티-핀 구조체 및 상기 제2 멀티-핀 구조체는 테이퍼링된 폭(tapered width)들을 가지는 핀들을 포함하는 것인, 집적 회로 디바이스.

### 청구항 7

제1항에 있어서,

상기 제1 멀티-핀 구조체 위에 배치된 제1 게이트 구조체 및 상기 제2 멀티-핀 구조체 위에 배치된 제2 게이트 구조체를 더 포함하는, 집적 회로 디바이스.

#### 청구항 8

제1항에 있어서,

상기 코어 영역은 상기 제2 폭보다 더 큰 제3 폭을 가지는 제3 멀티-핀 구조체를 더 포함하고, 상기 제1 멀티-핀 구조체와 상기 제3 멀티-핀 구조체 사이의 간격은 최소 핀 피치의 2배보다 크거나 같은 것인, 집적 회로 디바이스.

### 청구항 9

집적 회로 디바이스에 있어서,

기판 위에 배치된 멀티-핀 구조체 — 상기 멀티-핀 구조체는 인터-핀(inter-fin)들 사이에 배치된 인트라-핀(intra-fin)들을 포함함 — 를 포함하고,

상기 인터-핀들은 인터-핀 폭을 가지고 상기 인트라-핀들은 인트라-핀 폭을 가지고, 상기 인터-핀 폭은 상기 인트라-핀 폭보다 더 크고;

상기 인터-핀들은 최소 핀 피치의 3배보다 크거나 같은 인터-핀 인접 핀 피치(inter-fin adjacent fin pitch)를 가지고;

상기 인트라-핀들은 상기 최소 핀 피치의 2배보다 작거나 같은 인트라-핀 인접 핀 피치(intra-fin adjacent fin pitch)를 가지는 것인, 집적 회로 디바이스.

#### 청구항 10

방법에 있어서,

코어 영역에 제1 멀티-핀 구조체 - 상기 제1 멀티-핀 구조체는 제1 폭을 가짐 - 를 형성하는 단계;

주변 영역에 제2 멀티-핀 구조체 — 상기 제2 멀티-핀 구조체는 제2 폭을 가지고, 또한 상기 제1 폭은 상기 제2 폭보다 더 큼 — 를 형성하는 단계; 및

상기 제1 멀티-핀 구조체 위의 제1 게이트 구조체 및 상기 제2 멀티-핀 구조체 위의 제2 게이트 구조체를 형성 하는 단계

를 포함하는, 방법.

#### 발명의 설명

### 기술분야

[0001] 본 출원은 2017년 8월 29일에 출원된 미국 가 출원번호 제 62/551,624 호에 대한 우선권을 주장하며, 본원에서 그 전체가 인용에 의해 포함된다.

### 배경기술

- [0002] 집적 회로(integrated circuit: IC) 산업은 급격한 성장(exponential growth)을 경험하였다. IC 재료 및 설계에서의 기술적 진보는 IC의 세대를 생산하였고, 여기서 각 세대는 이전의 세대보다 더 소형이고 더 복잡한 회로를 가진다. IC 진화의 과정에서, 기능적 밀도(즉, 칩 면적(chip area) 당 상호연결 디바이스의 수)는 일반적으로 증가한 한편 기하학적 크기(즉, 제조 프로세스를 사용하여 생성될 수 있는 최소 컴포넌트(또는 라인))가 감소하였다. 이러한 축소 프로세스(scaling down process)는 일반적으로 생산 효율성을 증가시키고 관련 비용을 낮춤으로써 이점을 제공한다.

- [0003] 그와 같은 축소는 또한 IC를 프로세싱하고 제조하는 복잡도를 증가시켰고, 이런 진보가 실현되도록, IC 프로세싱 및 제조에서의 유사한 발전이 필요하다. 예를 들어, 핀-형 전계 효과 트랜지스터(fin-like field effect

transistor: FinFET) 기술은 더 소형의 피처 크기로 진행함에 따라, 프로세스 마진(margin)을 감소시킴으로써 FinFET 제조 프로세스가 상당히 제약된다. 특히, 다수의 핀 밀도가 존재하는 경우에, 핀 피치(fin pitch)를 감소시키고 핀 높이를 증가시킴으로써 종래의 에칭 프로세스가 핀 사이의 재료를 완전히 또는 상당부분 제거하는 것을 막는다. 결과적으로, FinFET 디바이스의 모든 장점이 실현될 수 있는 것은 아니다.

### 발명의 내용

### 도면의 간단한 설명

[0005] 본 개시물은 첨부한 도면과 함께 숙독할 때 다음의 상세한 설명으로부터 최적으로 이해된다. 산업분야의 표준 실시예에 따르면, 다양한 피처가 실척으로 그려지지 않고 예시 목적을 위해서만 사용됨이 강조된다. 사실, 다양한 피처의 치수는 논의의 명확성을 위해 임의선택적으로 증가하거나 감소할 수 있다.

도 1a-1c, 도 2a-2c, 도 3a-3c, 도 4a-4e, 도 5a-5e 및 도 6a-6e는 본 개시물의 다양한 양상에 따른 다양한 제조 스테이지에서, 부분적 또는 전체적인 집적 회로 디바이스의 단편적 개략도이다.

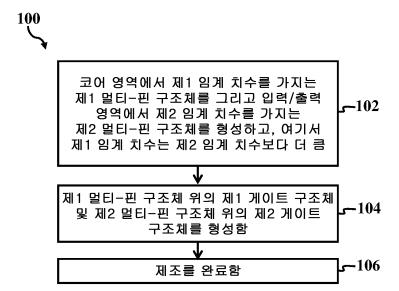

도 7은 본 개시물의 다양한 양상에 따른 집적 회로 디바이스를 제조하기 위한 방법의 흐름도이다.

도 8은 본 개시물의 다양한 양상에 따른 부분적 또는 전체적인 집적 회로 디바이스의 단편적 단면도이다.

#### 발명을 실시하기 위한 구체적인 내용

- [0006] 본 개시물은 일반적으로 집적 회로 디바이스에 관한 것으로, 더 구체적으로 핀-형 전계 효과 트랜지스터 (FinFET) 디바이스에 관한 것이다.

- [0007] 다음의 개시물은 본 발명의 서로 다른 피처를 구현하기 위한 많은 서로 다른 실시예, 또는 예를 제공한다. 컴 포넌트 및 장치(arrangement)의 특정 예는 본 개시물을 간략화하기 위해 이하에 설명된다. 이들은 물론, 단지 예이고 제한하려는 것이 아니다. 예를 들어, 후속하는 설명에서 제2 피처 위에 또는제2 피처 상의 제1 피처의 형성은 제1 및 제2 피처가 직접 접촉하여 형성되는 실시예를 포함할 수 있고, 또한 제1 및 제2 피처가 직접 접 촉하지 않을 수 있도록 제1 및 제2 피처 사이에 추가적인 피처가 형성될 수 있는 실시예를 포함할 수 있다.

- [0008] 추가로, 본 개시물은 다양한 예에서 참조 부호 및/또는 문자를 반복할 수 있다. 이러한 반복은 간략화 및 명확성의 목적을 위한 것이고, 스스로 논의된 다양한 실시예 및/또는 구성 사이의 관계를 서술하는 것이 아니다. 또한, 후속하는 본 개시물에서 다른 피처 상에, 연결된, 및/또는 커플링된 일 피처의 형성은 피처가 직접 접촉하여 형성되는 실시예를 포함할 수 있고, 또한 피처가 직접 접촉하지 않을 수 있도록 추가적인 피처가 피처에 삽입하여 형성될 수 있는 실시예를 포함할 수 있다. 추가로, "하부(lower)", "상부(upper)", "수평의 (horizontal)", "수직의(vertical)", "위에(above)", "위에(over)", "아래에(below)", "밑에(beneath)", "위에(up)", "아래에(down)", "최상부(top)", "바닥부(bottom)" 등과 같은 공간적으로 관련한 용어뿐 아니라 그 파생물(예를 들어, "수평으로(horizontally)", "하방으로(downwardly)", "상방으로(upwardly)" 등)은 본 개시물의 편의를 위해 일 피처의 다른 피처에 대한 관계를 위해 사용된다. 공간적으로 관련된 용어는 피처를 포함하는 디바이스의 서로 다른 배향(orientation) 포괄하려는 것이다.

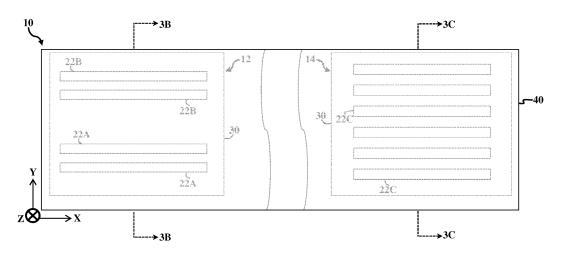

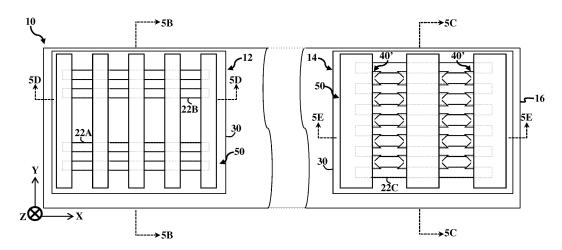

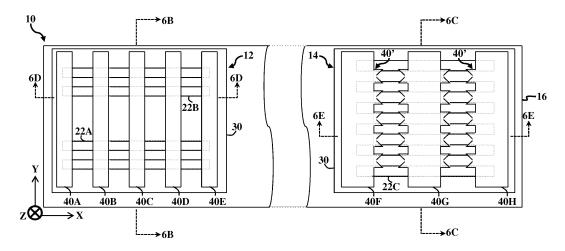

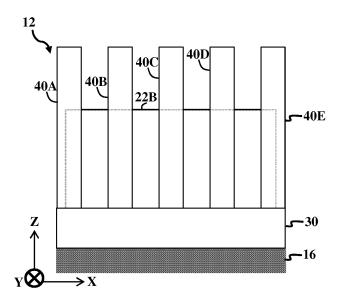

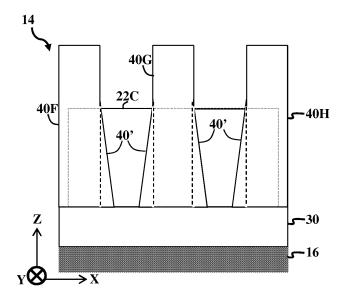

- [0009] 도 1a-1c, 도 2a-2c, 도 3a-3c, 도 4a-4e, 도 5a-5e 및 도 6a-6e는 본 개시물의 다양한 양상에 따른 다양한 제조 스테이지에서, 부분적 또는 전체적인 집적 회로 디바이스(10)의 단편적 개략도이다. 집적 회로 디바이스(10)는 코어 영역(종종 논리 영역으로 지칭됨), (정적 랜덤 액세스 메모리(SRAM) 영역과 같은) 메모리 영역, 아날로그 영역(analog region), 주변 영역(종종 입력/출력(I/O) 영역으로 지칭됨), 더미 영역(dummy region), 다른 적합한 영역 또는 그 조합과 같은 다양한 디바이스 영역을 포함한다. 도시된 실시예에서, 집적 회로 디바이스(10)는 코어 영역(12) 및 I/O 영역(14)을 포함하고, 그 각각은 저항기(resistor), 커패시터(capacitor), 인덕터(inductor), 다이오드(diode), 금속-산화물 반도체 전계 효과 트랜지스터(metal-oxide semiconductor field effect transistor: MOSFET), 상보성 금속-산화물 반도체(complementary metal-oxide semiconductor: CMOS) 트랜지스터, 바이폴라 접합 트랜지스터(bipolar junction transistor: BJT), 측면 확산 MOS(laterally diffused MOS: LDMOS) 트랜지스터, 고전압 트랜지스터, 고주파수 트랜지스터, 다른 적합한 컴포넌트 또는 그 조합과 같은 다양한 수동 및 능동 마이크로전자 디바이스(microelectronic device)를 포함할 수 있다. 본원에 설명된 바와 같이, 코어 영역(12) 및 I/O 영역(14)은 각각 하나 또는 그 이상의 핀-형 전계 효과 트랜지스터 (FinFET)를 포함한다. 집적 회로 디바이스(10)는 마이크로프로세서, 메모리 및/또는 다른 집적 회로 디바이스

에 포함될 수 있다. 일부 구현에서, 집적 회로 디바이스(10)는 IC 칩의 일부분, 시스템 온 칩(system on chip: SoC) 또는 그 일부분일 수 있다. 도 1a-1c, 도 2a-2c, 도 3a-3c, 도 4a-4e, 도 5a-5e 및 도 6a-6e는 명확성을 위해 본 개시물의 발명 개념을 더 잘 이해하기 위해 간략화되었다. 추가적인 피처가 집적 회로 디바이스(10)에 추가될 수 있고, 이하에 설명된 피처의 일부는 집적 회로 디바이스(10)의 다른 실시예에서 교체될 수 있고, 수정될 수 있거나 제거될 수 있다.

[0010]

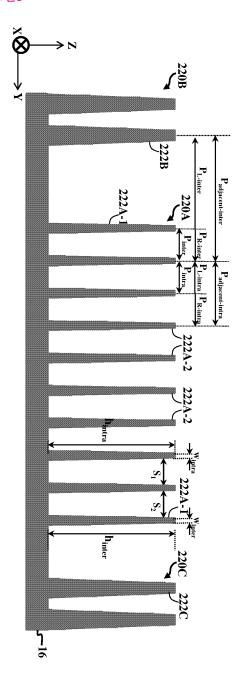

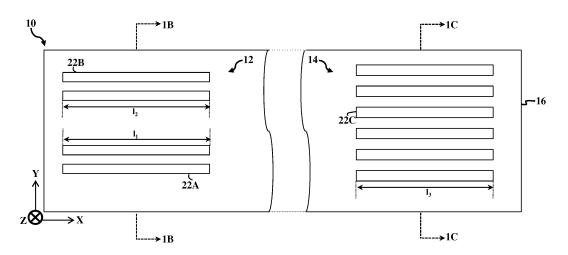

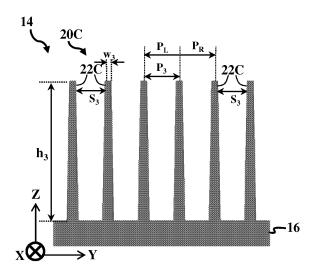

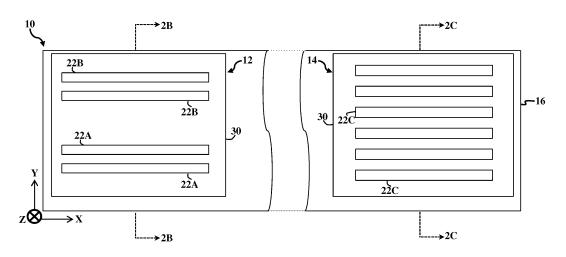

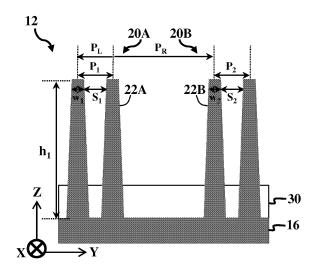

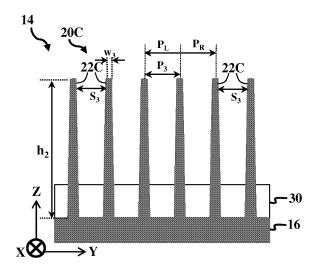

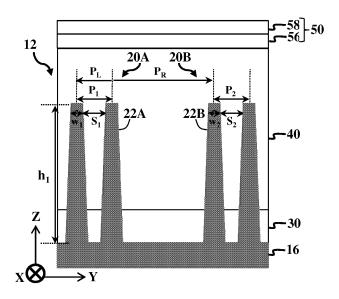

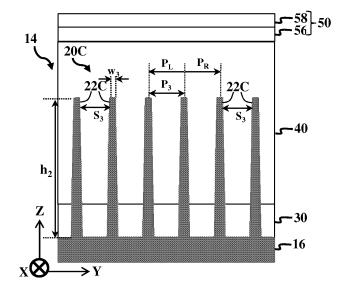

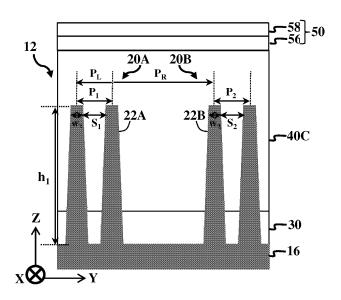

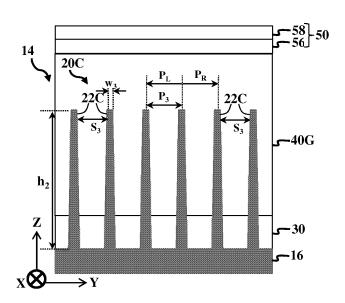

도 la-lc를 참조하면, 도 la는 집적 회로 디바이스(10)의 최상면도이다. 도 lb는 도 la의 라인 lB-lB를 따른 집적 회로 디바이스(10)의 부분적 단면도이고, 도 1c는 도 1a의 라인 1C-1C를 따른 집적 회로 디바이스(10)의 부분적 단면도이다. 코어 영역(12) 및 I/O 영역(14) 각각은 기판(웨이퍼)(16) 위에 배치된 적어도 하나의 핀 구조체를 포함한다. 도시된 실시예에서, 기판(16)은 실리콘을 포함한다. 대안적으로 또는 추가적으로, 기판 (16)은 게르마늄(germanium)과 같은 다른 기본 반도체; 실리콘 탄화물(silicon carbide), 실리콘 인화물 (silicon phosphide), 갈륨 비화물(gallium arsenide), 갈륨 인화물(gallium phosphide), 인듐 인화물(indium phosphide), 인듐 비화물 및/또는 인듐 안티몬화물(indium antimonide)과 같은 화합물 반도체; 실리콘 게르마늄 (SiGe), SiPC, GaAsP, AlInAs, AlGaAs, GaInAs, GaInP 및/또는 GaInAsP와 같은 합금 반도체; 또는 그 조합을 포함한다. 대안적으로, 기판(16)은 실리콘-온-절연체(silicon-on-insulator: SOI) 기판, 실리콘 게르마늄-온-절연체(silicon germanium-on-insulator: SGOI) 기판, 또는 게르마늄-온-절연체(germanium-on-insulator: GOI) 기판과 같은 반도체-온-절연체 기판이다. 반도체-온-절연체 기판은 산소의 주입에 의한 분리(separation by implantation of oxygen: SIMOX), 웨이퍼 본딩(wafer bonding) 및/또는 다른 적합한 방법을 사용하여 제조될 수 있다. 일부 구현에서, 기판(16)은 하나 또는 그 이상의 III-V 족(group) 재료를 포함한다. 일부 구현에서, 기판(16)은 하나 또는 그 이상의 II-IV 족 재료를 포함한다. 기판(16)은 코어 영역(12) 및 I/O 영역(14)의 설 계 요건에 따라 다양한 도핑 영역(도시되지 않음)을 포함한다. 예를 들어, 코어 영역(12)은 n-타입 디바이스 영역, p-타입 디바이스 영역, 또는 그 조합이고, I/O 영역(14)은 n-타입 디바이스 영역, p-타입 디바이스 영역 또는 그 조합이다. 일부 구현에서, 기판(16)은 붕소(boron), 인듐과 같은 p-타입 도펀트(dopant), 다른 p-타입 도펀트 또는 그 조합으로 도핑되는 p-타입 도핑 영역(예를 들어, p-타입 웰(well))을 포함한다. 구현에서, 기판(16)은 인(phosphorus), 비소(arsenic)와 같은 n-타입 도펀트, 다른 n-타입 도펀트 또는 그 조합 으로 도핑되는 n-타입 도핑 영역(예를 들어, n-타입 웰)을 포함한다. 일부 구현에서, 기판(16)은 p-타입 도편 트 및 n-타입 도펀트의 조합으로 형성된 도핑 영역을 포함한다. 다양한 도핑 영역이 예를 들어, p-웰 구조체, n-웰 구조체, 듀얼-웰(dual-well) 구조체, 상승 구조체 또는 그 조합을 제공하면서 기판(16) 상에 직접 및/또는 기판(16)에 형성될 수 있다.

[0011]

코어 영역(12)은 2개 이하의 핀을 가지는 적어도 하나의 핀 구조체를 포함하고, I/O 영역(14)은 3개 이상의 핀 을 가지는 적어도 하나의 핀 구조체를 포함한다. 예를 들어, 코어 영역(12)은 (2개의 핀(22A)을 가지는) 핀 구 조체(20A) 및 (2개의 핀(22B)을 가지는) 핀 구조체(20B)를 포함하고, I/O 영역(14)은 (6개의 핀(22C)을 가지는) 핀 구조체(20C)를 포함한다. 핀 구조체(20A-20C)는 도시된 실시예에서 멀티-핀 구조체이더라도, 본 개 시물은 핀 구조체(20A) 및/또는 핀 구조체(20B)가 단지 하나의 핀을 포함하는 실시예를 고려한다. 도시된 실시 예에서, 핀 구조체(20A-20C)는 각각 집적 회로 디바이스(10)의 제1 FinFET 디바이스, 제2 FinFET 디바이스 및 제3 FinFET 디바이스에 속한다. 대안적으로, 일부 구현에서, 핀 구조체(20A) 및 핀 구조체(20B)는 제1 FinFET 디바이스에 속하고, 핀 구조체(20C)는 제2 FinFET 디바이스에 속한다. 일부 구현에서, 핀(22A-22C)은 (기판 (16)의 재료 층의 일부분과 같은) 기판(16)의 일부분이다. 예를 들어, 기판(16)이 실리콘을 포함하는 경우에, 핀(22A-22C)은 실리콘을 포함한다. 대안적으로, 일부 구현에서, 핀(22A-22C)은 기판(16)을 오버라잉하는 하나 또는 그 이상의 반도체 재료 층과 같은 재료 층에 정의된다. 예를 들어, 핀(22A-22C)은 기판(16) 위에 배치된 (헤테로구조(heterostructure)와 같은) 다양한 반도체 층을 가지는 반도체 층 스택을 포함할 수 있다. 반도체 층은 실리콘, 게르마늄, 실리콘 게르마늄, 다른 적합한 반도체 재료 또는 그 조합과 같은 임의의 적합한 반도체 재료를 포함할 수 있다. 반도체 층은 집적 회로 디바이스(10)의 설계 요건에 따른 동일한 또는 서로 다른 재료, 에칭 속도(etching rate), 성분 원자 퍼센티지(constituent atomic percentage), 성분 중량 퍼센티지 (constituent weight percentage), 두께, 및/또는 구성을 포함할 수 있다. 일부 구현에서, 반도체 층 스택은 제1 재료로 구성되는 반도체 층 및 제2 재료로 구성되는 반도체 층과 같은 교번하는 반도체 층을 포함한다. 예 를 들어, 반도체 층 스택은 실리콘 층 및 실리콘 게르마늄 층(예를 들어, 바닥부로부터 최상부까지 SiGe/Si/SiGe/Si/SiGe/Si)을 교대한다. 일부 구현에서, 반도체 층 스택은 동일한 재료지만 제1 원자 퍼센트의 성분을 가지는 반도체 층 및 제2 원자 퍼센트의 성분을 가지는 반도체 층과 같은 교번하는 성분 원자 퍼센티지 를 가지는 반도체 층을 포함한다. 예를 들어, 반도체 층 스택은 교번하는 실리콘 및/또는 게르마늄 원자 퍼센 티지(예를 들어, 바닥부로부터 최상부까지 SiaGeb/SiaGed/SiaGeb/SiaGeb/SiaGeb/SiaGeb,/SiaGeb,/SiaGeb, a 및 c는 서로 다른 실리

콘 원자 퍼센티지이고 b 및 d는 서로 다른 게르마늄 원자 퍼센티지)를 가지는 실리콘 게르마늄 층을 포함한다. 일부 구현에서, 핀(22A), 핀(22B) 및/또는 핀(22C)은 각각의 FinFET 디바이스의 설계 요건에 따라 동일한 재료 및/또는 동일한 반도체 층 스택을 포함한다. 일부 구현에서, 핀(22A), 핀(22B) 및/또는 핀(22C)은 각각의 FinFET 디바이스의 설계 요건에 따라 서로 다른 재료 및/또는 서로 다른 반도체 층 스택을 포함한다.

[0012]

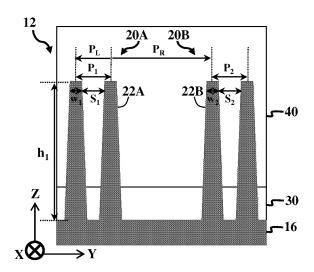

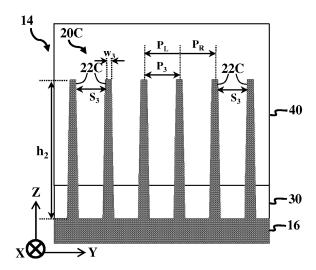

- 서로 다른 임계 치수를 가지는 코어 영역(12) 및 I/O 영역(14)의 핀 구조체를 구성함으로써 후속적인 프로세싱 을 위한 핀 임계 치수(CD) 로딩 최적화가 코어 영역(12)과 I/O 영역(14) 사이에 달성된다. 일부 구현에서, 임 계 치수는 일반적으로 집적 회로 디바이스(10)의 원하는 성능을 달성하기 위해 설계 요건에 의해 정의되는, 핀 폭 및/또는 핀 피치와 같은 치수를 지칭한다. 도 1a-1c에서, 핀(22A) 각각은 폭(w1)을 가지고, 핀(22B) 각각은 폭(w2)을 가지고, 핀(22C) 각각은 폭(w3)을 가지고, 여기서 핀 폭은 임계 치수이고, 폭(w1), 폭(w2) 및 폭(w3)은 핀 CD 로딩 최적화를 제공하도록 구성된다. 일부 구현에서, 핀 CD 로딩은 코어 영역(12)의 코어 핀 CD(또는 코 어 핀 폭)와 I/O 영역(14)의 I/O 핀 CD(또는 I/O 핀 폭) 사이의 차이로서 정의된다. 핀 CD 로딩은 핀 CD 로딩 이 0보다 큰 때(다시 말해, 핀 CD 로딩 = 코어 핀 CD - I/O 핀 CD > 0)의 게이트 형성 동안 사용되는 에칭 프로 세스를 위한 핀-투-핀 간격을 최적화한다. 예를 들어, 코어 핀 CD가 I/O 핀 CD보다 큰 경우에(다시 말해, 핀 (22A) 및 핀(22B) 각각은 핀(22C)의 폭보다 더 큰 폭(예를 들어, w<sub>1</sub> > w<sub>3</sub> 및 w<sub>2</sub> > w<sub>3</sub>)을 가질 때), 인접 핀(22A) 사이의 간격(S<sub>1</sub>)(거리) 및/또는 인접 핀(22B) 사이의 간격(S<sub>2</sub>)은 인접 핀(22C) 사이의 간격(S<sub>3</sub>)보다 작다(다시 말해,  $S_1 < S_3$  및  $S_2 < S_3$ ). 일부 구현에서, 폭( $w_1$ )은 약 1 nm 내지 약 30 nm 사이에 있고, 폭( $w_2$ )은 약 1 nm 내지 약 30 nm 사이에 있고, 폭(w3)은 약 1 nm 내지 약 30 nm 사이에 있다. 일부 구현에서, 간격(S1)은 약 10 nm 내지 약 30 nm이고, 간격(S<sub>2</sub>)은 약 10 nm 내지 약 30 nm이고, 간격(S<sub>3</sub>)은 약 10 nm 내지 약 30 nm이다. 도 시된 실시예에 더하여, 핀(22A) 및 핀(22B)은 실질적으로 같은 폭(다시 말해, w<sub>1</sub> ≒ w<sub>2</sub>)을 가지고, 핀(22A) 및 핀(22B)은 실질적으로 같은 간격(다시 말해,  $S_1 ≒ S_2$ )을 가진다. 일부 구현에서, 핀(22A)의 폭(w1) 및/또는 간 격(S<sub>1</sub>)은 코어 영역(12)의 설계 요건에 따른 핀(22B)의 폭(w<sub>2</sub>) 및/또는 간격(S<sub>2</sub>)과 서로 다르다. 도 1a-1c에서,  $\mathbb{P}(22A)$ 는 각각 높이 $(h_1)$  및 길이 $(1_1)$ 를 가지고;  $\mathbb{P}(22B)$ 은 각각 높이 $(h_2)$  및 길이 $(1_2)$ 를 가지고; 및  $\mathbb{P}(22C)$ 은 각각 높이(h<sub>3</sub>) 및 길이(l<sub>3</sub>)를 가진다. 일부 구현에서, 높이(h<sub>1</sub>)는 약 30 nm 내지 약 150 nm이고, 높이(h<sub>2</sub>)는 약 30 nm 내지 약 150 nm이고, 높이(h3)는 약 30 nm 내지 약 150 nm이다. 일부 구현에서, 길이(l1)는 약 30 nm 내 지 약 60 nm이고, 길이(l2)는 약 30 nm 내지 약 60 nm이고, 길이(l3)는 약 30 nm 내지 약 60 nm이다.

- [0013] 핀 구조체(20A)의 피치(P<sub>1</sub>)는 일반적으로 핀(22A)의 폭(w<sub>1</sub>) 및 (S<sub>1</sub>과 같은) 인접 핀(22A) 사이의 간격의 합계(다시 말해, P<sub>1</sub> = w<sub>1</sub> + S<sub>1</sub>)를 지칭한다. 핀 구조체(20B)의 피치(P<sub>2</sub>)는 일반적으로 핀(22B)의 폭(w<sub>2</sub>) 및 (S<sub>2</sub>와 같은) 인접 핀(22B) 사이의 간격의 합계(다시 말해, P<sub>2</sub> = w<sub>2</sub> + S<sub>2</sub>)를 지칭한다. 핀 구조체(20C)의 피치(P<sub>3</sub>)는 일반적으로 핀(22C)의 폭(w<sub>3</sub>) 및 (S<sub>3</sub>와 같은) 인접 핀(22C) 사이의 간격의 합계(다시 말해, P<sub>3</sub> = w<sub>3</sub> + S<sub>3</sub>)를 지칭한다. 도시된 실시예에서, 피치(P<sub>1</sub>), 피치(P<sub>2</sub>) 및 피치(P<sub>3</sub>)는 핀 사이의 센터-투-센터(center-to-center) 거리를 정의한다. 일부 구현에서, 피치(P<sub>1</sub>), 피치(P<sub>2</sub>) 및 피치(P<sub>3</sub>)는 약 10 nm 내지 약 80 nm이다. 일부 구현에서, 피치(P<sub>1</sub>), 피치(P<sub>2</sub>)는 약 10 nm 내지 약 600 nm이고, 피치(P<sub>3</sub>)는 약 10 nm 내지 약 80 nm이다. 일부 구현에서, 핀 구조체(20A-20C)는 거의 같은 피치를 가진다. 일부 구현에서, 핀 구조체(20A-20C)는 서로 다른 피치를 가진다. 일부 구현에서, 피치(P<sub>1</sub>), 피치(P<sub>2</sub>) 및/또는 피치(P<sub>3</sub>)는 최소 핀 피치(P<sub>m</sub>)와 동등하다. 일부 구현에서, 최소 핀 피치는 일반적으로 리소그래피 프로세스 및/또는 정해진 IC 기술 노드의 (증착, 리소그래피 및/또는 에칭 프로세스를 포함하는) 핀 제조 프로세스에 의해 달성가능한 최소 핀 피치를 지칭한다. 일부 구현에서, 최소 핀 피치는 일반적으로 집적 회로 디바이스(10)를 위한 설계 요건에 의해 특정된 최소 핀 피치를 지칭한다.

- [0014] 핀(22A-22C)의 각각은 코어 영역(12) 및 I/O 영역(14)에서의 게이트 형성 동안 사용되는 에칭 프로세스를 위한 핀-투-핀 간격(fin-to-fin spacing)을 더 최적화하도록 구성될 수 있는 인접 핀 피치를 가진다. 인접 핀 피치 (P<sub>adjacent</sub>)는 핀의 우측 핀 피치(P<sub>R</sub>) 및 핀의 좌측 핀 피치(P<sub>L</sub>)의 합계이다. 우측 핀 피치(P<sub>R</sub>)는 핀의 센터와 핀 의 우측에 포지셔닝된(positioned) 인접한(이웃하는) 핀의 센터 사이의 거리를 정의하고, 좌측 핀 피치(P<sub>L</sub>)는 핀의 센터와 핀의 센터와 핀의 좌측에 포지셔닝된 인접한(이웃하는) 핀의 센터 사이의 거리를 정의한다. 일부 구현에서, 핀

및 인접 핀은 동일한 핀 구조체 및/또는 동일한 FinFET 디바이스에 속한다. 일부 구현에서, 핀 및 인접 핀은 서로 다른 핀 구조체 및/또는 서로 다른 FinFET 디바이스에 속한다. 코어 영역(12)은 최소 핀 피치의 3배보다 크거나 같은(다시 말해, P<sub>adjacent-core</sub> ≥ 3P<sub>m</sub>) 코어 인접 핀 피치(P<sub>adjacent-core</sub>)를 가지는 핀 구조체를 포함하고, I/O 영역(14)은 최소 핀 피치의 2배보다 작거나 같은(다시 말해, P<sub>adjacent-IO</sub> ≤ 2P<sub>m</sub>) I/O 코어 인접 핀 피치 (P<sub>adjacent-I0</sub>)를 가지는 핀 구조체를 포함한다. 예를 들어, 코어 영역(12)에서, 핀 구조체(20A)의 최우측 핀(22 A)은 그 인접 핀 피치가 최소 핀 피치의 3배와 같도록(다시 말해, P<sub>adjacent-20A</sub> = P<sub>m</sub> + 2P<sub>m</sub> = 3P<sub>m</sub>), 최소 핀 피치  $(P_L = P_m)$ 와 같은 좌측 핀 피치 및 2배의 최소 핀 피치 $(P_R = 2P_m)$ 와 같은 우측 핀 피치를 가진다. 일부 구현에 서, 최우측 핀(22C)의 우측 핀 피치는 최소 핀 피치의 2배보다 더 크고 및/또는 최우측 핀(22C)의 좌측 핀 피치 는 최소 핀 피치보다 더 작다. 반대로, I/O 영역(14)에서, 핀 구조체(20C)의 센터 핀(22C) 중 하나는 그 인접 핀 피치가 2배의 최소 핀 피치(다시 말해, P<sub>adjacent-200</sub> = P<sub>m</sub> + P<sub>m</sub> = 2P<sub>m</sub>)와 같도록, 최소 핀 피치(P<sub>L</sub> = P<sub>m</sub>)와 같은 좌측 핀 피치 및 최소 핀 피치( $P_R = P_m$ )와 같은 우측 핀 피치를 가진다. 일부 구현에서, 센터 핀(22C)의 좌측 핀 피치 및/또는 우측 핀 피치는 최소 핀 피치보다 작다. 도시된 실시예에서, 핀 구조체(20A) 및 핀 구조체 (20B)가 2개 이하의 핀을 가지기 때문에, 핀(22A) 및 핀(22B) 각각은 제1 FinFET 디바이스의 핀과 제2 FinFET 디바이스의 핀 사이의 좌측 핀 피치 및/또는 우측 핀 피치를 정의하는 인접 핀 피치를 가진다. 도시된 실시예 에 더하여, 핀 구조체(20C)는 3개 이상의 핀을 가지기 때문에, 센터 핀(22C) 각각은 같은 FinFET 디바이스의 핀 사이의 좌측 핀 피치 및 우측 핀 피치를 정의하는 인접 핀 피치를 가진다.

[0015] 본 개시물은 집적 회로 디바이스(10)의 프로세싱 및 제조에서 발생할 수 있는 핀(22A-22C)의 높이, 폭 및/또는 길이에서의 변화를 고려한다. 도시된 실시예에서, 핀(22A-22C)은 그 각각의 높이를 따른 테이퍼링 폭을 가지고, 여기서 폭(w1), 폭(w2) 및 폭(w3)은 각각 변화하는 폭의 평균을 나타낸다. 예를 들어, 핀(22A-22C)의 폭은 상부 부분의 평균 폭이 핀(22A-22C)의 하부 부분의 평균 폭보다 작도록, 핀(22A-22C)의 하부 부분으로부터 핀(22A-22C)의 상부 부분으로 감소한다. 일부 구현에서, 폭이 핀(22A-22C)의 높이를 따라 측정된 위치에 따라 폭은 핀(22A-22C)을 따라 약 5 nm 내지 약 15 nm로 변화할 수 있다. 일부 구현에서, 핀 폭은 집적 회로 디바이스(10)의 다른 핀에 대한 및/또는 다른 피처에 대한 핀의 포지션(position)에 따라 변화한다. 예를 들어, 핀 구조체(20C)에 대해, 센터 핀의 폭(w3)(도시된 실시예에서, 핀 구조체(20C)는 3개의 센터 핀(22C)을 포함함)은 에지 핀(22C)(여기서, 3개의 센터 핀(22C)을 인클로징하는 최좌측 핀(22C) 및 최우측 핀(22C))의 폭(w3)보다 더 크다. 다른 예에서, 대안적으로, 센터 핀의 폭(w3)은 에지 핀의 폭(w3)보다 작다. 그와 같은 양쪽 구현에서, 폭(w3)은 폭(w1) 및 폭(w2)보다 작다. 그와 같은 구현에 더하여, 에지 핀의 폭(w3)은 에지 핀의 평균 폭을 나타낼 수 있고, 센터 핀의 폭(w3)은 센터 핀의 평균 폭을 나타낼 수 있다. 핀(22A-22C)이 테이퍼링 폭을 가지는 것으로 도시되더라도, 일부 구현에서, 핀(22A-22C)은 실질적으로 그 각각의 높이를 따라 동일한 폭을 가진다.

[0016]

도 22a-22c는 임의의 적합한 프로세스를 사용하여 기판(16) 위에 형성된다. 일부 구현에서, 증착, 리소그래피 및/또는 에칭 프로세스의 조합이 도 1a-1c에 도시된 바와 같이 기판(16)으로부터 연장하는 핀(22A-22C)을 정의 하도록 수행된다. 예를 들어, 핀(22A-22C)을 형성하는 단계는 기판(16) 위에 패터닝된 레지스트 층(또는 기판 (16) 위에 배치된, 헤테로구조와 같은 재료 층)을 형성하기 위해 리소그래피 프로세스를 수행하는 단계 및 기판 (16)에 패터닝된 레지스트 층(또는 기판(16) 위에 배치된, 헤테로구조와 같은 재료 층)에 정의된 패턴을 전달하 기 위해 에칭 프로세스를 수행하는 단계를 포함한다. 리소그래피 프로세스는 기판(16) 상에 (예를 들어, 스핀 코팅(spin coating)에 의해) 레지스트 층을 형성하는 단계, 사전-노출 베이킹 프로세스(pre-exposure baking process)를 수행하는 단계, 마스크를 사용하여 노출 프로세스를 수행하는 단계, 사후-노출 베이킹 프로세스를 수행하는 단계, 및 현상 프로세스(developing process)를 수행하는 단계를 포함할 수 있다. 노출 프로세스 동 안, 레지스트 층은 (자외선(ultraviolet: UV) 광, 딥(deep) UV(DUV) 광, 또는 극한(extreme) UV(EUV) 광과 같 은) 방사선 에너지(radiation energy)에 노출되고, 여기서 마스크는 이미지가 마스크 패턴에 대응하는 레지스트 층 상에 투영되도록(projected), 마스크 및/또는 마스크 타입(예를 들어, 이진 마스크, 위상 시프트 마스크, 또 는 EUV 마스크)의 마스크 패턴에 따라 레지스트 층에 대해 방사선을 차단, 투과 및/또는 반사시킨다. 레지스트 층은 방사선 에너지에 민감하기 때문에, 레지스트 층의 노출 부분은 화학적으로 변화하고, 레지스트 층의 노출 (또는 비-노출) 부분은 레지스트 층의 특성 및 현상 프로세스에 사용되는 현상액(developing solution)의 특성 에 따라 현상 프로세스 동안 용해된다. 현상 후에, 패터닝된 레지스트 층은 마스크에 대응하는 레지스트 패턴 을 포함한다. 에칭 프로세스는 기판(16)의 일부분(또는 기판(16) 위에 배치된 재료 층)을 제거하기 위해 에칭

마스크로서 패터닝된 레지스트 층을 사용한다. 에칭 프로세스는 건식 에칭 프로세스(예를 들어, 반응성 이온 에칭(reactive ion etching: RIE) 프로세스), 습식 에칭 프로세스, 다른 적합한 에칭 프로세스 또는 그 조합을 포함할 수 있다. 에칭 프로세스 후에, 패터닝된 레지스트 층은 예를 들어, 레지스트 박리 프로세스(resist stripping process)에 의해 기판(16)으로부터 제거된다. 대안적으로, 핀(22A-22C)은 더블 패터닝 리소그래피(double patterning lithography: DPL) 프로세스(예를 들어, 리소그래피-에칭-리소그래피-에칭(lithography-etch-lithography-etch: LELE) 프로세스, 자기-정렬된 더블 패터닝(self-aligned double patterning: SADP) 프로세스, 스페이서-이즈-유전체(spacer-is-dielectric: SID) SADP 프로세스, 다른 더블 패터닝 프로세스, 또는 그 조합), 트리플 패터닝 프로세스(triple patterning process)(예를 들어, 리소그래피-에칭-리소그래피-에칭-리소그래피-에칭-리소그래피-에칭-리소그래피-에칭(LELELE) 프로세스, 자기-정렬된 트리플 패터닝(self-aligned triple patterning: SATP) 프로세스, 다른 트리플 패터닝 프로세스 또는 그 조합), 다른 다수의 패터닝 프로세스(예를 들어, 자기-정렬된 쿼드 러플 패터닝(self-aligned quadruple patterning: SAQP) 프로세스) 또는 그 조합과 같은 다수의 패터닝 프로세스에 의해 형성된다. 일부 구현에서, 방향성 셀프-어셈블리(directed self-assembly: DSA) 기술은 핀(22A-22C)을 형성하는 동안 구현된다. 또한, 일부 구현에서, 노출 프로세스는 레지스트 층을 패터닝하기 위한 마스크리스(maskless) 리소그래피, 전자-빔(e-beam) 기록, 이온-빔 기록 및/또는 나노프린트 기술을 구현할 수 있다.

[0017]

일부 구현에서, 패터닝된 레지스트 층(또는 패터닝된 마스크 층)에 정의된 패턴은 핀 구조체(20A) 및 핀 구조체 (20B)를 정의하기 위한 제1 폭을 가지는 제1 개구 및 핀 구조체(20C)를 정의하기 위한 제2 폭을 가지는 제2 개 구를 포함하고, 여기서 제1 폭은 제2 폭보다 크다. 그와 같은 구현에서, 에칭 프로세스는 그 후에 핀(22A-22C)이 본원에 설명된 바와 같이 코어 영역(12)과 I/O 영역(14) 사이의 핀 CD 로딩을 가지고 제조되도록, 기판 (16)의 일부분(또는 기판(16) 위에 배치된 재료 층)을 제거하기 위해 에칭 마스크로서 패터닝된 레지스트 층을 사용한다. 일부 구현에서, 패터닝된 레지스트 층(또는 패터닝된 마스크 층)에 정의된 패턴은 핀 구조체(20A), 핀 구조체(20B) 및 핀 구조체(20C)를 정의하기 위한 제1 개구, 제2 개구 및 제3 개구를 포함하고, 여기서 제1 개구, 제2 개구 및 제3 개구는 동일한 폭을 가진다. 그와 같은 구현에서, 에칭 프로세스는 그 후에 핀(22A-22C)이 동일한 폭을 가지도록 기판(16)의 일부분(또는 기판(16)위에 배치된 재료 층)을 제거하기 위해 에칭 마 스크로서 패터닝된 레지스트 층을 사용한다. 그와 같은 구현에 더하여, 핀 구조체(20C)를 트리밍하기 위해 트 리밍 프로세스가 수행되고, 그에 의해 편(22C)의 폭을 감소시켜서, 본원에 설명된 바와 같이 코어 영역(12)과 I/O 영역(14) 사이의 핀 CD 로딩을 가지는 핀(22A-22C)이 제조된다. 트리밍 프로세스는 핀(22C)의 치수를 감소 시키기 위한 임의의 적합한 프로세스를 구현한다. 예를 들어, 일부 구현에서, 트리밍 프로세스는 집적 회로 디 바이스(10)의 다른 피처에 대해 핀(22C)을 선택적으로 에칭할 수 있는 에칭 프로세스를 포함한다. 에칭 프로세 스는 건식 에칭 프로세스, 습식 에칭 프로세스 또는 그 조합이다. 일부 구현에서, 습식 에칭 프로세스는 암모 늄 수산화물(ammonium hydroxide: NH4OH), 과산화수소(hydrogen peroxide: H2O2), 황산(sulfuric acid: H2SO4), 테트라메틸암모늄 수산화물(tetramethylammonium hydroxide: TMAH), 다른 적합한 습식 에칭 용액 또는 그 조합 을 포함하는 에칭 용액을 구현한다. 예를 들어, 습식 에칭 용액은  $\mathrm{NH_4OH:H_2O_2}$  용액, (암모니아-과산화물 혼합물 (ammonia-peroxide mixture: APM)로서 알려진) NH40H:H202:H20 용액, 또는 (유황 과산화물 혼합물(sulfuric peroxide mixture: SPM)로 알려진) H<sub>2</sub>SO<sub>4</sub>:H<sub>2</sub>O<sub>2</sub> 용액을 활용할 수 있다. 일부 구현에서, 건식 에칭 프로세스는 불소-함유 에천트 가스(fluorine-containing etchant gas)(예를 들어, CF4, SF6, CH2F2, CHF3 및/또는 C2F6), 산 소-함유 가스(oxygen-containing gas), 염소-함유 가스(예를 들어, Cl<sub>2</sub>, CHCl<sub>3</sub>, CCl<sub>4</sub> 및/또는 BCl<sub>3</sub>), 브롬-함유 가스(bromine-containing gas)(예를 들어, HBr 및/또는 CHBR<sub>3</sub>), 요오드-함유 가스(iodine-containing gas), 다 른 적합한 가스 및/또는 플라즈마 또는 그 조합을 포함하는 에천트 가스를 구현한다. 일부 구현에서, 트리밍 프로세스는 산화 프로세스를 구현한다. 예를 들어, 트리밍 프로세스는 핀(22C)을 오존 환경(ozone environment)에 노출시킴으로써, 핀(22C)의 일부분을 산화시키고, 후속적으로 세정 프로세스 및/또는 에칭 프로 세스에 의해 제거된다.

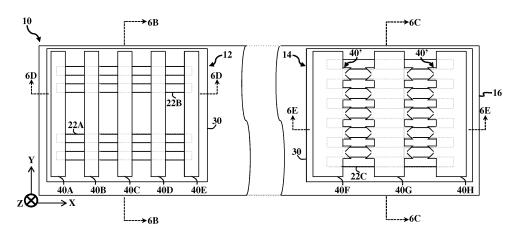

[0018] 도 2a-2c를 참조하면, 도 2a는 집적 회로 디바이스(10)의 최상면도이고, 도 2b는 도 2a의 라인 2B-2B를 따른 집적 회로 디바이스(10)의 부분적 단면도이고, 도 2c는 도 2a의 라인 2C-2C를 따른 집적 회로 디바이스(10)의 부분적 단면도이다. 집적 회로 디바이스(10)의 다양한 디바이스 영역과 같은 다양한 영역을 격리시키기 위해 격리 피처(30)가 기판(16) 위에 및/또는 기판(16)에 형성된다. 예를 들어, 격리 피처(30)는 I/O 영역(14)으로부터 코어 영역(12)을 분리하고 격리시킨다. 격리 피처(30)는 서로로부터 핀(22A-22C)을 더 분리하고 격리시킨다. 도시된 실시예에서, 격리 피처(30)는 핀(22A-22C)의 바닥 부분을 둘러싼다. 격리 피처(30)는 실

리콘 산화물, 실리콘 질화물, 실리콘 산화질화물, (예를 들어, 실리콘, 산소, 질소, 탄소 또는 다른 적합한 격 리 구성 성분을 포함하는) 다른 적합한 격리 재료 또는 그 조합을 포함한다. 격리 피처(30)는 얕은 트렌치 격 리(shallow trench isolation: STI) 구조체, 딥 트렌치 격리(deep trench isolation: DTI) 구조체, 및/또는 실 리콘의 로컬 산화(LOCOS) 구조체와 같은 서로 다른 구조체를 포함할 수 있다. 일부 구현에서, STI 피처는 (일 부 구현에서, 절연체 재료 층이 핀(22A-22C) 사이의 갭(트렌치)을 충전하도록) 핀(22A-22C)을 형성하고 격리 피 처(30)를 형성하기 위해 절연체 재료 층을 에칭 백(etching back)한 후에 기판(16) 위에 절연체 재료를 증착함 으로써 형성될 수 있다. 일부 구현에서, STI 피처는 (예를 들어, 건식 에칭 프로세스 및/또는 습식 에칭 프로 세스를 사용함으로써) 기판(16)에 트렌치를 에칭하고 (예를 들어, 화학 기상 증착 프로세스 또는 스핀-온 글래 스(spin-on glass) 프로세스를 사용함으로써) 트렌치를 절연체 재료로 충전함으로써 형성될 수 있다. 화학 기 계적 연마(chemical mechanical polishing: CMP) 프로세스는 과잉 절연체 재료를 제거하고 및/또는 격리 피처 (30)의 최상면을 평탄화하기 위해 수행될 수 있다. 일부 구현에서, 격리 피처(30)는 라이너 유전체 층(liner dielectric layer) 위에 배치된 벌크 유전체 층(bulk dielectric layer)과 같은 트렌치를 충전하는 다층 구조 (multi-layer structure)를 포함하고, 여기서 벌크 유전체 층 및 라이너 유전체 층은 설계 요건에 따른 재료(예 를 들어, 열적 산화물을 포함하는 라이너 유전체 층 위에 배치된 실리콘 질화물을 포함하는 벌크 유전체 층)를 포함한다. 일부 구현에서, 격리 피처(30)는 (예를 들어, 붕소 실리케이트 유리(boron silicate glass: BSG) 또는 인산 실리케이트 유리(phosphosilicate glass: PSG)를 포함하는) 도핑 라이너 층(doped liner layer) 위 에 배치된 유전체 층을 포함한다.

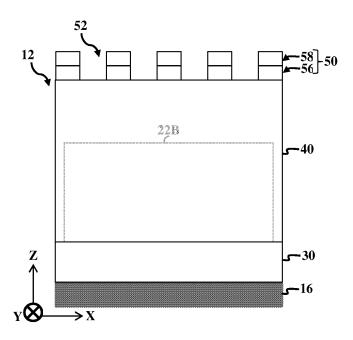

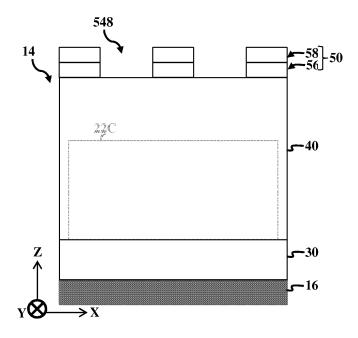

[0019] 도 3a-3c를 참조하면, 도 3a는 집적 회로 디바이스(10)의 최상면도이고, 도 3b는 도 3a의 라인 3B-3B를 따른 집 적 회로 디바이스(10)의 부분적 단면도이고, 도 3c는 도 3a의 라인 3C-3C를 따른 집적 회로 디바이스(10)의 부 분적 단면도이다. 게이트 층(40)은 코어 영역(12) 및 I/O 영역(14)에 각각 배치된 핀 구조체(20A-20C) 위에 형 성된다. 예를 들어, 기판(16) 위에, 특히 핀 구조체(20A-20C) 및 격리 피처(30) 위에 게이트 층(40)을 형성하 기 위해 적어도 하나의 증착 프로세스가 수행된다. 게이트 층(40)은 핀 구조체(20A-20C) 사이의 공간을 충전하 고 핀(22A-22C) 사이의 공간을 충전한다. 중착 프로세스는 화학 기상 증착(CVD), 물리적 기상 증착(PVD), 원자 층 증착(atomic layer deposition: ALD), 고밀도 플라즈마 CVD(high density plasma CVD: HDPCVD), 금속 유기 CVD(metal organic CVD: MOCVD), 원격 플라즈마 CVD(remote plasma CVD: RPCVD), 플라즈마 강화 CVD(plasma enhanced CVD: PECVD), 저압 CVD(low-pressure CVD: LPCVD), 원자 층 CVD(ALCVD), 상압 CVD(atmospheric pressure CVD: APCVD), 도금(plating), 다른 적합한 방법 또는 그 조합을 포함한다. 그 후에, CMP 프로세스는 게이트 층(40)의 최상면을 평탄화하기 위해 수행될 수 있다. 도시된 실시예에서, 게이트 층(40)은 폴리실리콘 층을 포함한다. 일부 구현에서, 게이트 층(40)은 핀 구조체(20A-20C)와 폴리실리콘 층 사이에 배치된 (실리콘 산화물과 같은 유전체 재료를 포함하는) 계면 층(interfacial layer)을 더 포함한다. 일부 구현에서, 게이트 층(40)은 더미 게이트 전극 및 더미 게이트 유전체 층을 포함하는 더미 게이트 스택이다. 그와 같은 구현에서, 기판(16) 위에 더미 게이트 유전체 층을 형성하기 위해 증착 프로세스가 수행되고, 게이트 유전체 층 위에 더미 게이트 전극 층을 형성하기 위해 증착 프로세스가 수행된다. 그와 같은 구현에 더하여, 더미 게이트 전극은 폴 리실리콘 또는 다른 적합한 더미 게이트 재료를 포함하고, 더미 게이트 유전체는 유전체 재료(예를 들어, 실리 콘 산화물), 하이-k 유전체 재료, 다른 적합한 유전체 재료 또는 그 조합을 포함한다. 하이-k 유전체 재료의 예는 HfO<sub>2</sub>, HfSiO, HfSiON, HfTaO, HfTiO, HfZrO, 지르코늄 산화물, 알루미늄 산화물, 하프늄 이산화물-알루미 나( $\mathrm{HfO_2-Al_2O_3}$ ) 합금, 다른 적합한 하이 $\mathrm{-k}$  유전체 재료 또는 그 조합을 포함한다. 게이트 층(40)은 수많은 다른 층, 예를 들어, 캡핑 층(capping layer), 계면 층, 확산 층, 배리어 층(barrier layer), 하드 마스크 층(hard mask layer) 또는 그 조합을 포함할 수 있다. 일 예에서, 티타늄 질화물(TiN) 캡핑 층과 같은 캡핑 층은 더미 게이트 유전체(또는 더미 게이트 유전체가 생략된 기판(16))와 더미 게이트 전극 사이에 배치된다.

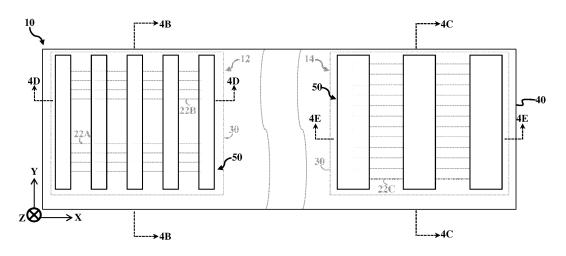

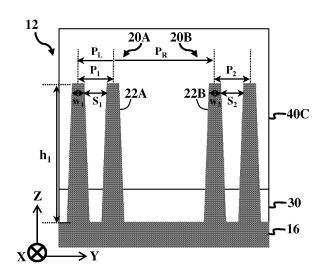

도 4a-4c를 참조하면, 도 4a는 집적 회로 디바이스(10)의 최상면도이고, 도 4b는 도 4a의 라인 4B-4B를 따른 집적 회로 디바이스(10)의 부분적 단면도이고, 도 4c는 도 4a의 라인 4C-4C를 따른 집적 회로 디바이스(10)의 부분적 단면도이고, 도 4d는 도 4a의 라인 4D-4D를 따른 집적 회로 디바이스(10)의 부분적 단면도이고, 도 4e는 도 4a의 라인 4E-4E를 따른 집적 회로 디바이스(10)의 부분적 단면도이다. 도 4a-4e에서, 패터닝 층(50)은 게이트 층(40) 위에 형성되고, 여기서 패터닝 층(50)은 코어 영역(12)에서의 게이트 층(40)의 일부분을 노출시키는 개구(52) 및 I/0 영역(14)에서의 게이트 층(40)의 일부분을 노출시키는 개구(54)를 포함한다. 도시된 실시예에서, 패터닝 층(50)은 게이트 층(40) 위에 배치된 마스크 층(56), 및 마스크 층(56) 위에 배치된 (또한, 포토레지스트 층, 감광성 층(photosensitive layer), 이미징 층(imaging layer), 패터닝 층 또는 방사선 민감성층(radiation sensitive layer)으로 지칭된) 레지스트 층(58)을 포함한다. 마스크 층(56)은 게이트 층(40)의

[0020]

재료와 다른 에칭 속도(etching rate)를 가지는 재료를 포함한다. 예를 들어, 마스크 층(56)은 실리콘 질화물, 실리콘 산화물, 실리콘 산화질화물, 실리콘 탄화물, 실리콘 탄화 질화물, 다른 적합한 재료 또는 그 조합을 포 일부 구현에서, 마스크 층(56)은 게이트 층(40)이 마스크 층(56)에 대해 선택적으로 에칭될 수 있도록, 게이트 층(40)의 재료에 대해 낮은 에칭 속도를 가지는 재료를 포함한다. 마스크 층(56)은 CVD 프로세 스와 같은 임의의 적합한 프로세스에 의해 임의의 적합한 두께로 형성된다. 일부 구현에서, 실리콘-함유 및 질 소-함유 마스크 층이 LPCVD를 사용하여 형성된다. 일부 구현에서, 실리콘-함유 및 질소-함유 마스크 층이 실리 콘-함유 층의 열적 질화를 포함하는 프로세스를 수행함으로써 형성된다. 레지스트 층(58)은 임의의 적합한 레 지스트 재료를 포함한다. 패터닝 층(50)은 레지스트 코팅(예를 들어, 스핀-온 코팅)을 포함하는 리소그래피 패 터닝 프로세스, 소프트 베이킹(soft baking), 마스크 정렬(mask aligning), 노출, 사후-노출 베이킹(postexposure baking), 현상, 린싱(rinsing), 건조(예를 들어, 하드 베이킹(hard baking)), 다른 적합한 프로세스 또는 그 조합에 의해 형성된다. 대안적으로, 리소그래피 노출 프로세스는 마스크리스 리소그래피(maskless lithography), 전자-빔 기록(electron-beam writing) 또는 이온-빔 기록(ion-beam writing)과 같은 다른 방법 에 의해 보조, 구현 또는 교체된다. 또 다른 대안에서, 리소그래피 패터닝 프로세스는 나노임프린트 기술 (nanoimprint technology)을 구현한다. 일부 구현에서, 리소그래피 프로세스는 건식 에칭, 습식 에칭, 다른 에 칭 방법 또는 그 조합과 같은 에칭 프로세스를 구현한다. 탈이온화(de-ionized: DI)수 린스와 같은 린싱 프로 세스는 패터닝 층(50)을 형성하기 전에 게이트 층(40) 상에 수행될 수 있다.

[0021]

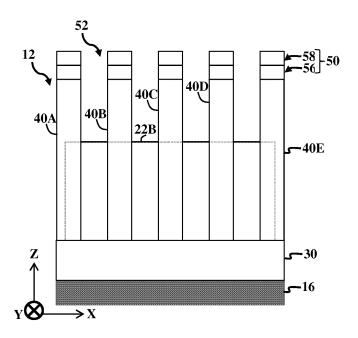

도 5a-5e를 참조하면, 도 5a는 집적 회로 디바이스(10)의 최상면도이고, 도 5b는 도 5a의 라인 5B-5B를 따른 집 적 회로 디바이스(10)의 부분적 단면도이고, 도 5c는 도 5a의 라인 5C-5C를 따른 집적 회로 디바이스(10)의 부 분적 단면도이고, 도 5d는 도 5a의 라인 5D-5D를 따른 집적 회로 디바이스(10)의 부분적 단면도이고, 도 5e는 도 5a의 라인 5E-5E를 따른 집적 회로 디바이스(10)의 부분적 단면도이다. 도 5a-5e에서, 게이트 충(40)의 노 출된 부분을 제거하기 위해 마스크로서 패터닝 층(50)을 사용하여 에칭 프로세스가 수행됨으로써, 게이트 구조 체(40A-40H)를 형성한다. 에칭 프로세스는 건식 에칭 프로세스(예를 들어, 반응성 이온 에칭(RIE) 프로세스), 습식 에칭 프로세스, 다른 적합한 에칭 프로세스 또는 그 조합을 포함할 수 있다. 에칭 프로세스는 핀(22C) 사 이에 배치된 나머지 게이트 층 부분(40')을 남기면서, I/O 영역(14)에서의 개구(54) 내의 게이트 층(40)의 노출 부분을 완전히 제거할 수 없다. 따라서 게이트 구조체(40F-40H)는 그 길이 및 높이를 따라 변화하는 폭을 가지 는 한편, 게이트 구조체(40A-40E)는 그 길이 및 높이를 따라 실질적으로 동일한 폭을 가진다. 도 5a에서, 그 길이를 따라, 핀(22C) 위에 배치된 게이트 구조체(40F-40H)의 폭은 핀(22C) 사이에 배치된 게이트 구조체(40F-40H)의 폭보다 작다. 그 높이를 따라, 게이트 구조체(40F-40H)는 테이퍼링된 폭을 가진다. 예를 들어, 도 5e 에서, 핀(22C) 사이에 배치된 게이트 구조체(40G)의 일부분은 격리 피처(30)(또는 기판(16))에 근접한 게이트 구조체(40G)의 일부분의 폭이 패터닝 층(50)에 근접한 게이트 구조체(40G)의 일부분의 폭보다 더 크도록, 그 높 이를 따라 감소하는 폭을 가진다. 일부 구현에서, 핀 구조체(22C)의 최상면 위의 게이트 구조체(40G)의 일부분 의 폭은 그 높이를 따라 실질적으로 동일한 한편, 핀 구조체(22C)의 최상면 아래의 게이트 구조체(40G)의 일부 분의 폭은 그 높이를 따라 감소한다. 종래의 집적 회로 디바이스에서, 코어 영역 및 I/O 영역은 실질적으로 동 일한 핀 임계 치수(폭)를 가지는 핀 구조체를 가지는 경우에, 그와 같은 나머지 게이트 층 부분은 게이트로 하 여금 소스/드레인 브레이크다운(breakdown), 디바이스 성능 저하를 야기시킨다. 반대로, 본원에 설명된 바와 같이 코어 영역(12)과 I/O 영역(14) 사이의 핀 CD 로딩을 구현함으로써(그리고 그에 따라 코어 영역(12)에서의 핀 간격에 대해 I/O 영역(14)에서의 핀 간격을 증가시킴으로써), 에칭 프로세스 동안 에칭 로딩 효과가 최소화 되어, 종래의 집적 회로 디바이스와 비교하여 나머지 게이트 층 부분(40')의 양(특히, 두께)을 상당히 감소시킨 다. 개시된 핀 CD 로딩은 (예를 들어, I/O 핀 CD 보다 더 큰 코어 핀 CD를 가짐으로써) 코어 영역(12)의 성능 을 부스팅하기 위해 원하는 더 작은 핀-투-핀 간격(fin-to-fin spacing)을 유지하면서 (예를 들어, I/O 영역 (14)에서의 핀-투-핀 간격을 증가시킴으로써) I/O 영역(14)을 위한 브레이크다운 전압(Vm) 윈도우를 확대한다. 따라서 I/O 영역(14)을 위한  $V_{BD}$  윈도우는 코어 영역(12)의 성능에 영향을 미치지 않고서 및/또는 게이트 제조 프로세스(특히, 폴리실리콘 에칭 프로세스)에 영향을 미치지 않고서 확대된다. 서로 다른 실시예는 서로 다른 장점을 가질 수 있고, 임의의 실시예에 특정 장점이 반드시 요구되는 것은 아니다.

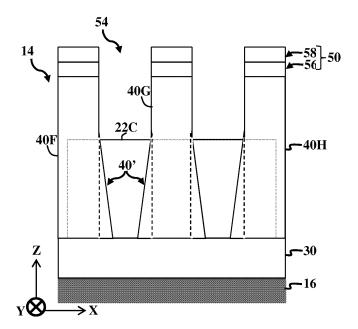

[0022] 도 6a-6e를 참조하면, 도 6a는 집적 회로 디바이스(10)의 최상면도이고, 도 6b는 도 6a의 라인 6B-6B를 따른 집적 회로 디바이스(10)의 부분적 단면도이고, 도 6c는 도 6a의 라인 6C-6C를 따른 집적 회로 디바이스(10)의 부분적 단면도이고, 도 6d는 도 6a의 라인 6D-6D를 따른 집적 회로 디바이스(10)의 부분적 단면도이고, 도 6e는 도 6a의 라인 6E-6E를 따른 집적 회로 디바이스(10)의 부분적 단면도이다. 도 6a-6c에서, 예를 들어, 레지스트 박리 프로세스에 의해 패터닝 층(50)이 게이트 층(40)으로부터 제거된 후에, 게이트 구조체(40A-40H)가 핀(22A-

22C) 위에 배치된다. 게이트 구조체(40A-40H)는 (예를 들어, 핀(22A-22C)에 실질적으로 수직인) y-방향을 따라 연장한다. 도시된 실시예에서, 게이트 구조체(40A-40E)가 핀(22A) 및 핀(22B)의 일부분을 랩핑하도록, 게이트 구조체(40A-40E)는 핀 구조체(20A) 및 핀 구조체(20B) 위에 배치되고; 및 게이트 구조체(40F-40H)가 핀(22C)의 일부분을 랩핑하도록 게이트 구조체(40F-40H)는 핀 구조체(20C) 위에 배치된다. 게이트 구조체(40A-40H)는 집 적 회로 디바이스(10)의 설계 요건에 따라 능동 게이트 구조체 또는 더미 게이트 구조체이다. "능동 게이트 구 조체"는 일반적으로 집적 회로 디바이스(10)의 전기적으로 기능적 게이트 구조체를 지칭하는 한편, "더미 게이 트 구조체"는 일반적으로 집적 회로 디바이스(10)의 전기적인 비-기능적 게이트 구조체를 지칭한다. 일부 구현 에서, 더미 게이트 구조체는 능동 게이트 구조체의 물리적 치수와 같은 능동 게이트 구조체의 물리적 특성을 모 방하지만, FinFET에서 동작불능이다(다시 말해, 전류를 흐르게 할 수 없다). 일부 구현에서, 게이트 구조체 (40A-40E) 중 적어도 하나는 핀(22A) 및 핀(22B)의 채널 영역을 랩핑함으로써, 핀(22A) 및 핀(22B)의 소스/드레 인 영역을 삽입하고; 및 게이트 구조체(40F-40H) 중 적어도 하나는 핀(22C) 의 채널 영역을 랩핑함으로써, 핀 (22C)의 소스/드레인 영역을 삽입한다. 그와 같은 구현에서, 게이트 구조체(4OA-4OH) 중 적어도 하나는 동작 동안 핀(22A-22C)의 소스/드레인 영역 사이에 전류가 흐를 수 있도록 핀(22A-22C)의 채널 영역과 맞물린다. 일 부 구현에서, 게이트 구조체(40A-40H)는 실질적으로 균일한 프로세싱 환경을 가능하게 하는데, 예를 들어, (예 를 들어, 에피택셜 소스/드레인 피처를 형성할 때) 핀(22A-22C)의 소스/드레인 영역에서의 균일한 에피택셜 재 료 성장, (예를 들어, 소스/드레인 리세스를 형성할 때) 핀(22A-22C)의 소스/드레인 영역에서의 균일한 에칭 속 도, 및/또는 (예를 들어, CMP-유발 디싱 효과(dishing effect)를 감소시킴으로써(또는 방지함으로써)) 균일한, 실질적으로 평탄한 표면을 가능하게 한다.

[0023] 집적 회로 디바이스(10)는 제조를 완료하기 위해 추가적인 프로세싱을 겪을 수 있다. 예를 들어, 일부 구현에 서, 게이트 구조체(40A-40H) 인접에 게이트 스페이서가 형성된다. 예를 들어, 게이트 충(40)(의 측벽을 따라) 인접에 게이트 스페이서가 배치된다. 게이트 스페이서는 임의의 적합한 프로세스에 의해 형성되고 유전체 재료 를 포함한다. 유전체 재료는 실리콘, 산소, 탄소, 질소, 다른 적합한 재료, 또는 그 조합(예를 들어, 실리콘 산화물, 실리콘 질화물, 실리콘 산화질화물 또는 실리콘 탄화물)을 포함할 수 있다. 예를 들어, 도시된 실시예 에서, 실리콘 질화물 층과 같은 실리콘 및 질소를 포함하는 유전체 층은 기판(16) 위에 증착될 수 있고 게이트 스페이서를 형성하기 위해 후속적으로 이방성으로 에칭될 수 있다. 일부 구현에서, 게이트 스페이서는 실리콘 질화물을 포함하는 제1 유전체 층 및 실리콘 산화물을 포함하는 제2 유전체 층과 같은 다층 구조를 포함한다. 일부 구현에서, 시일 스페이서(seal spacer), 오프셋 스페이서(offset spacer), 희생 스페이서(sacrificial spacer), 더미 스페이서 및/또는 메인 스페이서와 같은 하나 이상의 스페이서 세트가 게이트 구조체(40A-40H) 인접에 형성된다. 그와 같은 구현에서, 스페이서의 다양한 세트는 서로 다른 에칭 속도를 가지는 재료를 포함 할 수 있다. 예를 들어, 실리콘 및 산소(예를 들어, 실리콘 산화물)를 포함하는 제1 유전체 층은 게이트 구조 체(40A-40H) 인접에 제1 스페이서 세트를 형성하기 위해 기판(16) 위에 증착되고 후속적으로 이방성 에칭될 수 있고, 실리콘 및 산소(예를 들어, 실리콘 산화물)를 포함하는 제2 유전체 층은 제1 스페이서 세트 인접에 제2 스페이서 세트를 형성하기 위해 기판(16) 위에 증착되고 후속적으로 이방성 에칭될 수 있다.

[0024]

일부 구현에서, 고농도 도핑(heavily doped) 소스/드레인 영역 및/또는 저농도 도핑 소스/드레인(lightly doped source/drain: LDD) 피처와 같은 소스/드레인 피처가 핀(22A-22C)의 소스/드레인 영역에 형성된다. 일부 구현 에서, (에피택셜 소스/드레인 피처로 지칭되는) 에피택셜 소스 피처 및 에피택셜 드레인 피처가 핀(22A-22C)의 소스/드레인 영역에 형성된다. 예를 들어, 반도체 재료는 핀(22A-22C)의 노출 부분 상에 에피택셜 성장되어, 에피택셜 소스/드레인 피처를 형성한다. 에피택시 프로세스(epitaxy process)는 CVD 증착 기술(예를 들어, VPE 및/또는 UHV-CVD), 분자 빔 에피택시(molecular beam epitaxy), 다른 적합한 에피택셜 성장 프로세스 또는 그 조합을 사용할 수 있다. 에피택시 프로세스는 핀(22A-22C)의 조성과 상호작용하는 가스 및/또는 액체 전구체 (precursor)를 사용할 수 있다. 에피택셜 소스/드레인 피처는 n-타입 도펀트 및/또는 p-타입 도펀트로 도핑된 다. 일부 구현에서, 에피택셜 소스/드레인 피처는 실리콘 및/또는 탄소를 포함하는 에피택셜 층이고, 여기서 실리콘 함유 에피택셜 층 또는 실리콘 탄소 함유 에피택셜 층은 인, 다른 n-타입 도펀트 또는 그 조합으로 도핑 된다(예를 들어, Si:P 에피택셜 층 또는 Si:C:P 에피택셜 층을 형성함). 일부 구현에서, 에피택셜 소스/드레인 피처(260)는 실리콘 및 게르마늄을 포함하는 에피택셜 층이고, 여기서 실리콘 게르마늄 함유 에피택셜 층은 붕 소, 다른 p-타입 도펀트 또는 그 조합으로 도핑된다(예를 들어, Si:Ge:B 에피택셜 층을 형성함). 일부 구현에 서, 에피택셜 소스/드레인 피처는 핀(22A-22C)의 채널 영역에서 원하는 장력 및/또는 압축력을 달성하는 재료 및/또는 도펀트를 포함한다. 일부 구현에서, 에피택셜 소스/드레인 피처는 불순물을 에피택시 프로세스의 소스 재료에 첨가함으로써 증착 동안 도핑된다. 일부 구현에서, 에피택셜 소스/드레인 피처는 증착 프로세스에 후속 하여 이온 주입 프로세스에 의해 도핑된다. 일부 구현에서, 집적 회로 디바이스(10)의 에피택셜 소스/드레인

피처 및/또는 다른 소스/드레인 영역(예를 들어, 핀(22A-22C)의 소스/드레인 영역 및/또는 에피택셜 소스/드레인 미처에 형성되는 HDD 영역 및/또는 LDD 영역)에서의 도펀트를 활성화하기 위해 어닐링 프로세스(annealing process)가 수행된다.

- [0025] 그 후에, 게이트 구조체(40A-40H) 중 적어도 하나의 더미 게이트 스택을 금속 게이트 스택과 같은 게이트로 교 체하기 위해 게이트 교체 프로세스가 수행될 수 있다. 예를 들어, 레벨-간 유전체(inter-level dielectric: ILD) 층이 예를 들어, (CVD, PVD, ALD, HDPCVD, MOCVD, RPCVD, PECVD, LPCVD, ALCVD, APCVD, 도금, 다른 적합 한 방법 또는 그 조합과 같은) 증착 프로세스에 의해 기판(16) 위에 형성될 수 있다. ILD 층은 예를 들어, 실 리콘 산화물, 실리콘 질화물, 실리콘 산화질화물, TEOS 형성 산화물, PSG, BPSG, 로우-k 유전체 재료, 다른 적 합한 유전체 재료 또는 그 조합을 포함하는 유전체 재료를 포함한다. 예시적인 로우-k 유전체 재료는 FSG, 탄 소 도핑 실리콘 산화물, Black Diamond®(Applied Materials of Santa Clara, California), 크세로겔 (Xerogel), 에어로겔(Aerogel), 아모르퍼스 플루오르화 탄소(amorphous fluorinated carbon), (Parylene), BCB, SiLK(Dow Chemical, Midland, Michigan), 폴리이미드(polyimide), 다른 로우-k 유전체 재료, 또는 그 조합을 포함한다. ILD 층은 다수의 유전체 재료를 가지는 다층 구조를 포함할 수 있다. ILD 층의 증 착에 후속하여, 게이트 충(40)의 더미 게이트 전극(예를 들어, 폴리실리콘 층)과 같은 게이트 구조체(40A-40H)의 최상부 부분이 도달(노출)되도록, CMP 프로세스가 수행될 수 있다. 그 후에, (게이트 층(40)의 더미 게 이트 전극과 같은) 게이트 구조체(40A-40H) 중 적어도 하나의 일부분이 제거됨으로써, 계면 층 및/또는 게이트 유전체를 노출시킬 수 있는 트렌치(개구)를 형성한다. 일부 구현에서, 에칭 프로세스는 더미 게이트 전극(및, 일부 구현에서, 더미 게이트 유전체)을 선택적으로 제거한다. 에칭 프로세스는 건식 에칭 프로세스, 습식 에칭 프로세스, 또는 그 조합이다. 선택적 에칭 프로세스는 더미 게이트 전극 층이 계면 층, 스페이서 및/또는 ILD 층에 대해 적합한 에칭 속도를 가지도록 조정될 수 있다.

- [0026] 그 후에 게이트 구조체(40A-40H) 중 적어도 하나의 금속 게이트 스택이 개구(트렌치)에 형성된다. 게이트 구조 체(40A-40H) 중 적어도 하나의 금속 게이트 스택은 게이트 유전체(예를 들어, 게이트 유전체 층) 및 게이트 전 극(예를 들어, 일함수 층 및 벌크(또는 충전) 전도성 층)을 포함한다. 게이트 스택은 수많은 다른 층, 예를 들 어, 캡핑 층, 계면 층, 확산 층, 배리어 층, 하드 마스크 층 또는 그 조합을 포함할 수 있다. 게이트 유전체 층은 실리콘 산화물, 하이-k 유전체 재료, 다른 적합한 유전체 재료 또는 그 조합을 포함한다. 하이-k 유전체 재료의 예는 하프늄 이산화물(HfO<sub>2</sub>), HfSiO, HfSiON, HfTaO, HfTiO, HfZrO, 지르코늄 산화물, 알루미늄 산화물, 하프늄 이산화물-알루미나(HfO<sub>2</sub>-Al<sub>2</sub>O<sub>3</sub>) 합금, 다른 적합한 하이-k 유전체 재료 또는 그 조합을 포함한다. 일부 구현에서, 게이트 유전체 층은 하이-k 유전체 층이다. 게이트 전극은 폴리실리콘, 알루미늄(Al), 구리(Cu), 티 타늄(Ti), 탄탈륨(Ta), 텅스텐(W), 몰리브데늄(molybdenum: Mo), 코발트(Co), TaN, NiSi, CoSi, TiN, WN, TiAl, TiAlN, TaCN, TaC, TaSiN, 다른 전도성 재료 또는 그 조합과 같은 전도성 재료를 포함한다. 일부 구현에 서, 일함수 층은 (n-타입 일함수 또는 p-타입 일함수와 같은) 원하는 일함수를 가지도록 조정되는 전도성 층이 고, 전도성 벌크 층은 일함수 층 위에 형성된 전도성 층이다. 일부 구현에서, 일함수 층은 Ti, 은(Ag), TaAl, TaAlC, TiAlN, TaC, TaCN, TaSiN, 망간(Mn), 지르코늄(Zr), 다른 적합한 n-타입 일함수 재료, 또는 그 조합을 포함한다. 일부 구현에서, 일함수 층은 TiN, TaN, 루테늄(ruthenium: Ru), Mo, Al, WN, ZrSi<sub>2</sub>, MoSi<sub>2</sub>, TaSi<sub>2</sub>, NiSi<sub>2</sub>, WN, 다른 적합한 p-타입 일함수 재료 또는 그 조합과 같은 p-타입 일함수 재료를 포함한다. 벌크 전도 성 층은 Al, W 및/또는 Cu와 같은 적합한 전도성 재료를 포함한다. 일부 구현에서, 벌크 전도성 층은 폴리실리 콘, Ti, Ta, 금속 합금, 다른 적합한 재료 또는 그 조합을 추가로 또는 집합적으로 포함한다. 게이트 유전체 층, 일함수 층 및 벌크 전도성 층은 ALD, CVD, PVD 및/또는 다른 적합한 프로세스와 같은 다양한 증착 프로세스 에 의해 형성된다. CMP 프로세스는 (임의의 과잉 일함수 층 및/또는 임의의 과잉 금속 충진 층과 같은) 과잉 재료를 제거하여, 게이트 구조체(40A-40H)를 평탄화하기 위해 수행될 수 있다. 게이트 구조체(40A-40H)가 동일 하거나 서로 다른 층 및/또는 재료를 포함하도록, 게이트 구조체(40A-40H)가 집적 회로 디바이스(10)의 설계 요 건에 따라 원하는 기능을 달성하도록 구성되는 게이트 스택을 포함하는 것이 이해된다.

- [0027] 일부 구현에서, 집적 회로 디바이스(10)의 동작을 용이하게 하기 위해 다양한 컨택트(contact)가 형성된다. 예를 들어, 추가적인 ILD 층이 기판(16) 위에(도시된 실시예에서, ILD 층 및 게이트 구조체(40A-40H) 위에) 형성될 수 있다. 게이트 구조체(40A-40H)와 전기적으로 커플링되는 컨택트 및 핀 구조체(20A-20C)의 소스/드레인 영역과 전기적으로 커플링되는 컨택트와 같은 컨택트가 ILD 층에 형성될 수 있다. 컨택트는 금속과 같은 전도성 재료를 포함한다. 금속은 알루미늄, (알루미늄/실리콘/구리 합금과 같은) 알루미늄 합금, 구리, 구리 합금, 티타늄, 티타늄 질화물, 탄탈륨, 탄탈륨 질화물, 텅스텐, 폴리실리콘, 금속 규화물, 다른 적합한 금속 또는 그

조합을 포함한다. 금속 규화물은 니켈 규화물, 코발트 규화물, 텅스텐 규화물, 탄탈륨 규화물, 티타늄 규화물, 백금 규화물, 에르븀 규화물(erbium silicide), 팔라듐 규화물(palladium silicide) 또는 그 조합을 포함할 수 있다. 일부 구현에서, ILD 층 및 컨택트는 기판(16) 위에 배치된 다층 상호연결(multilayer interconnect: MLI) 피처의 일부분이다. MLI 피처는 다양한 컴포넌트가 설계 요건에 의해 특정된 바와 같이 기능하게 동작가능하도록 집적 회로 디바이스(10)의 다양한 컴포넌트를 전기적으로 커플링한다. MLI 피처는 컨택트 및/또는 비아(via)와 같은 수직 상호연결 피처, 및/또는 라인과 같은 수평 상호연결 피처를 형성하도록 구성되는 금속 층 및 ILD 층의 조합을 포함할 수 있다. 다양한 전도성 피처는 컨택트와 유사한 재료를 포함한다. 일부구현에서, 다마신 프로세스(damascene process) 및/또는 듀얼 다마신 프로세스(dual damascene process)는 구리-기반 다층 상호연결 구조체를 형성하기 위해 사용된다. 집적 회로 디바이스(10)는 설계 요건에 따라 제조를 완료하기 위해 후속적인 프로세싱을 겪을 수 있다.

- [0028] 도 7은 본 개시물의 다양한 양상에 따른 집적 회로 디바이스(10)와 같은 집적 회로 디바이스를 제조하기 위한 방법(100)의 흐름도이다. 블록(102)에서, 방법(100)은 코어 영역에서의 제1 임계 치수 및 입력/출력 영역에서의 제2 임계 치수를 가지는 제2 멀티-핀 구조체를 형성하는 단계를 포함한다. 제1 임계 치수는 제2 임계 치수보다 더 크다. 일부 구현에서, 제1 멀티-핀 구조체 및 제2 멀티-핀 구조체는 도 1a-1c를 참조하여 개시된 바와같이 형성된다. 블록(104)에서, 방법(100)은 제1 멀티-핀 구조체 위의 제1 게이트 구조체 및 제2 멀티-핀 구조체 위의 제2 게이트 구조체를 형성하는 단계를 포함한다. 일부 구현에서, 제1 게이트 구조체 및 제2 게이트 구조체는 도 2a-2c, 도 3a-3c, 도 4a-4e, 도 5a-5e 및 도 6a-6e를 참조하여 개시된 바와 같이 형성된다. 블록(106)에서, 방법(100)은 계속해서 FinfEt 디바이스의 제조를 완료할 수 있다. 예를 들어, 제1 게이트 구조체 및/또는 제2 게이트 구조체가 더미 게이트를 포함하는 구현에서, 더미 게이트를 금속 게이트로 교체하기 위해게이트 교체 프로세스가 수행된다. 방법(100) 전에, 방법(100) 동안 및 방법(100) 후에 추가적인 단계가 제공될 수 있고, 설명된 단계 중 일부는 방법(100)의 추가적인 실시예에 대해 이동, 교체 또는 제거될 수 있다.

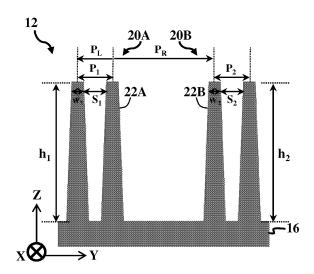

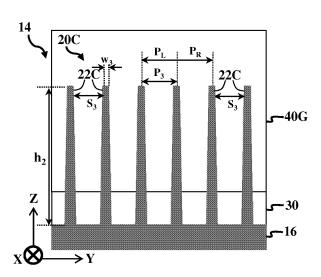

- [0029] 도 8은 본 개시물의 다양한 양상에 따른 부분적인 또는 전체적인 집적 회로 디바이스(200)의 부분적 단면도이다. 집적 회로 디바이스(200)는 마이크로프로세서, 메모리 및/또는 다른 집적 회로 디바이스에 포함될수 있다. 일부 구현에서, 집적 회로 디바이스(200)는 저항기(resistor), 커패시터(capacitor), 인덕터 (inductor), 다이오드, PFET, NFET, MOSFET, CMOS 트랜지스터, BJT, LDMOS 트랜지스터, 고전압 트랜지스터, 고주파수 트랜지스터, 다른 적합한 컴포넌트 또는 그 조합과 같은 다양한 수동 및 능동 마이크로전자 디바이스를 포함하는 IC 칩의 일부분, SoC, 또는 그 일부분이다. 도 8은 본 개시물의 발명 개념을 더 잘 이해하도록 명확성을 위해 간략화되었다. 추가적인 피처가 집적 회로 디바이스(200)에 추가될 수 있고, 이하에 설명된 피처의 일부는 집적 회로 디바이스(200)의 다른 실시예에서 교체, 수정 또는 제거될 수 있다.

- [0030] 도 8에서, 집적 회로 디바이스(200)는 도 1a-1c를 참조하여 상기에 상세하게 설명된 집적 회로 디바이스(10)의 기판과 유사한 기판(116)을 포함한다. 집적 회로 디바이스(200)는 핀 구조체(220A), (핀(222B)을 포함하는) 핀 구조체(220B) 및 (핀(222C)을 포함하는) 핀 구조체(220C)를 더 포함한다. 핀 구조체(220A)는 핀 구조체(220B)와 핀 구조체(220C) 사이에 배치된다. 도시된 실시예에서, 핀 구조체(220A)는 (예를 들어, 3개보다 많거나 같은 핀을 가지는) 조밀한(dense) 핀 구조체이고, 핀 구조체(220B) 및 핀 구조체(220C)는 (예를 들어, 2개 이하의 핀을 가지는) 격리된 핀 구조체이다. 도시된 실시예에서 핀 구조체(220A-220C)가 멀티-핀 구조체라도, 본 개시물은 핀 구조체(220B) 및/또는 핀 구조체(220C)가 단 하나의 핀을 포함하는 실시예를 고려한다. 본 개시물은 핀 구조체(220A)가 도 8에 도시된 것보다 더 많거나 더 적은 핀을 포함하는 실시예를 더 고려한다. 일부 구현에서, 핀 구조체(220A-220C)는 집적 회로 디바이스(200)의 서로 다른 FinFET 디바이스에 속한다. 일부 구현에서, 핀 구조체(220A-220C)는 집적 회로 디바이스(200)의 동일한 FinFET 디바이스에 속한다. 일부 구현에서, 핀 구조체(220A-220C)는 집적 회로 디바이스(200)의 서로 다른 영역에 속한다. 예를 들어, 일부 구현에서, 핀 구조체(220A)는 집적 회로 디바이스(200)의 I/O 영역에 배치되고 핀 구조체(220B) 및/또는 핀 구조체(220C)는 집적 회로 디바이스(200)의 I/O 영역에 배치되고 핀 구조체(220B) 및/또는 핀 구조체(220C)는 집적 회로 디바이스(200)의 되어 영역에 배치되고 핀 구조체(220B) 및/또는 핀 구조체(220C)는 집적 회로 디바이스(200)의 되어 영역에 배치되고 핀 구조체(220B) 및/또는 핀 구조체(220C)는 집적 회로 디바이스(200)의 되어 영역에 배치되고 핀 구조체(220B) 및/또는 핀 구조체(220C)는 집적 회로 디바이스(200)의 되어 영역에 배치되고 핀 구조체(220B) 및/또는 핀 구조체(220C)는 집적 회로 디바이스(200)의 되어 영역에 배치되고 핀 구조체(220B) 및/또는 핀 구조체(220C)는

- [0031] 핀 구조체(220A)는 인터-핀(222A-1) 및 인트라-핀(222A-2)을 가지고, 여기서 인트라-핀(222A-2)은 인터-핀(222A-1) 사이에 배치된다. 도시된 실시예에서, 인터-핀(222A-1)은 핀 구조체(220A)의 최외측 핀이고, 인트라-핀(222A-2)은 핀 구조체(220A)의 내부 핀이다. 일부 구현에서, 인트라-핀은 일반적으로 동일한 핀 구조체(여기서, 핀 구조체(220A))의 핀 사이에 배치된 핀을 지칭하는 한편, 인터-핀은 일반적으로 동일한 핀 구조체(또는 FinFET 디바이스)의 핀과 다른 핀 구조체(또는 FinFET 디바이스)(여기서, 핀 구조체(220B) 또는 핀 구조체(220C))의 핀 사이에 배치된 핀을 지칭한다. 일부 구현에서, 인트라-핀은 일반적으로 게이트 구조체 및/또는 소스/드레인 피처를 공유하는 핀 사이에 배치된 핀을 지칭하는 한편, 인터-핀은 일반적으로 게이트 구조체 및/

또는 소스/드레인 피처를 공유하지 않는 핀 사이에 배치된 핀을 지칭한다.

[0032]

핀 구조체(220A)를 서로 다른 임계 치수로 구성함으로써 인터-핀(222A-1)과 인트라-핀(222A-2) 사이의 핀 CD 로 딩 최적화(loading optimization)가 달성된다. 도시된 실시예에서, 인터-핀(222A-1)은 인터-핀 CD를 가지고 인트라-핀(222A-2)은 인트라-핀 CD인 한편, 인터-핀 CD는 인트라-핀 CD보다 더 크다. 일부 구현에서, 조밀한 핀 구조체를 위한 핀 CD 로딩은 인터-핀 CD와 인트라-핀 CD 사이의 차이로서 정의되고, 핀 CD 로딩이 0보다 클 때(다시 말해, 조밀한 핀 CD 로딩 = 인터-핀 CD - 인트라-핀 CD > 0) 핀 CD 로딩은 게이트 형성동안 사용되는 에칭 프로세스를 위한 핀-투-핀 간격을 최적화한다. 예를 들어, 인터-핀(222A-1)은 각각 폭(w<sub>inter</sub>)을 가지고, 인트라-핀(222A-2)은 각각 폭(wintra)을 가진다. 도시된 실시예에서, 인터-핀(222A-1)이 인트라-핀(222A-2)의 폭보다 큰 폭을 가질 때(다시 말해, Winter > Wintra), 인트라-핀(222A-2) 사이의 간격(S1)(거리)은 인터-핀(222A-1)과 인트라-핀(222A-2) 사이의 간격(S<sub>2</sub>)보다 작다(다시 말해, S<sub>1</sub> < S<sub>2</sub>). 일부 구현에서, 폭(w<sub>inter</sub>)은 약 1 nm 내지 약 30 nm이고, 폭(Wintra)은 약 1 nm 내지 약 30 nm이다. 일부 구현에서, 간격(S1)은 약 10 nm 내지 약 30 nm이고, 간격(S<sub>2</sub>)은 약 10 nm 내지 약 30 nm이다. 인터-핀(222A-1)은 각각 높이(h<sub>inter</sub>)를 가지고, 인트라-핀 (222A-2)은 각각 높이(h<sub>intra</sub>)를 가진다. 일부 구현에서, 높이(h<sub>inter</sub>)는 약 30 nm 내지 약 150 nm이고, 높이 (h<sub>intra</sub>)는 약 30 nm 내지 약 150 nm이다. 핀 구조체(220A)의 피치(P)는 일반적으로 (인터-핀(222A-1) 및 인트 라-핀(222A-2)을 집합적으로 포함하는) 핀의 폭(w) 및 인접 핀 사이의 간격(S)의 합계(다시 말해, P = w + S)를 지칭한다. 도시된 실시예에서, 핀 구조체(220A)의 피치(P<sub>intra</sub>)는 일반적으로 인트라-핀(222A-2) 사이의 센터-투 -센터 거리를 지칭하고, 핀 구조체(220A)의 피치(P<sub>inter</sub>)는 일반적으로 인터-핀(222A-1) 중 하나와 인접 인트라-핀(222A-2) 사이의 센터-투-센터 거리의 합계를 지칭한다. 일부 구현에서, 피치(P<sub>intra</sub>)는 약 10 nm 내지 약 50 nm이고, 피치(P<sub>inter</sub>)는 약 30 nm 내지 약 600 nm이다. 일부 구현에서, 피치(P<sub>intra</sub>) 및 피치(P<sub>inter</sub>)는 같다(예를 들어,  $P_{intra} = P_{inter}$ ). 일부 구현에서, 피치 $(P_{intra})$  및 피치 $(P_{inter})$ 는 서로 다르다. 예를 들어, 일부 구현에서, 피치(P<sub>intra</sub>)는 피치(P<sub>inter</sub>)보다 더 크다. 일부 구현에서, 피치(P<sub>intra</sub>) 및/또는 피치(P<sub>inter</sub>)는 최소 핀 피치(P<sub>m</sub>)와 등가이다. 일부 구현에서, 최소 핀 피치는 일반적으로 정해진 IC 기술 노드의 (증착, 리소그래피, 및/또는 에 칭 프로세스를 포함하는) 리소그래피 프로세스 및/또는 핀 제조 프로세스에 의해 달성가능한 가장 작은 핀 피치 를 지칭한다. 일부 구현에서, 최소 핀 피치는 일반적으로 집적 회로 디바이스(200)를 위한 설계 요건에 의해 특정된 가장 작은 핀 피치를 지칭한다.

[0033] 도시된 실시예에 더하여, 인터-핀(222A-1)은 인터-핀 인접 피치(P<sub>adjacent-inter</sub>)를 가지고 인트라-핀(222A-2)은 인 트라-핀 인접 피치(Padjacent-intra)를 가지고, 이는 상술한 바와 같은 게이트 형성 동안 사용되는 에칭 프로세스를 위한 핀-투-핀 간격을 더 최적화하도록 구성될 수 있다. 인터-핀 인접 피치는 인터-핀의 우측 핀 피치 및 인터 -핀의 좌측 핀 피치의 합계이다. 인터-핀의 우측 핀 피치(P<sub>R-inter</sub>)는 인터-핀의 센터와 핀의 우측에 포지셔닝된 (positioned) 인접한(이웃하는) 핀의 센터 사이의 거리를 정의하고, 인터-핀의 좌측 핀 피치(P<sub>L-inter</sub>)는 인터-핀 의 센터와 핀의 좌측에 포지셔닝된 인접한(이웃하는) 핀의 센터 사이의 거리를 정의한다. 인터-핀 좌측 핀 피 치 또는 인터-핀 우측 핀 피치 중 하나는 동일한 핀 구조체의 인터-핀과 인트라-핀 사이에 정의되는 한편, 인터 -핀 좌측 핀 피치 또는 인터-핀 우측 핀 피치 중 다른 하나는 인터-핀과 다른 핀 구조체의 핀 사이에 정의된다. 인트라-핀 인접 피치는 인트라-핀의 우측 핀 피치 및 인트라-핀의 좌측 핀 피치의 합계이다. 인트라-핀의 우측 핀 피치(P<sub>R-intra</sub>)는 인트라-핀의 센터와 인트라-핀의 우측에 포지셔닝된 인접한(이웃하는) 인트라-핀의 센터 사이 의 거리를 정의하고, 인트라-핀의 좌측 핀 피치(P<sub>L-intra</sub>)는 인트라-핀의 센터와 핀의 좌측에 포지셔닝된 인접한 (이웃하는) 인트라-핀의 센터 사이의 거리를 정의한다. 인트라-핀 좌측 핀 피치 및 인트라-핀 우측 핀 피치는 동일한 핀 구조체의 핀 사이에 정의된다. 도시된 실시예에서, 인터-핀(222A-1)은 최소 핀 피치보다 3배보다 크 거나 같은 인터-핀 인접 피치를 가지고(다시 말해, P<sub>adjacent-inter</sub> ≥ 3P<sub>m</sub>), 인트라-핀(222A-2)은 최소 핀 피치의 2 배보다 작거나 같은 인트라-핀 인접 피치를 가진다(다시 말해,  $P_{adjacent-inter} \leq 2P_m$ ). 예를 들어, 인터-핀 인접 핀 피치가 최소 핀 피치의 3배와 같도록(다시 말해, Padjacent-inter = 2Pm + Pm = 3Pm), 핀 구조체(220A)의 최좌측 인터-핀(222A-1)은 2개의 최소 핀 피치(P<sub>L-inter</sub> = 2P<sub>m</sub>)와 같은 좌측 핀 피치 및 최소 핀 피치(P<sub>R-inter</sub> = P<sub>m</sub>)와 같 은 우측 핀 피치를 가진다. 일부 구현에서, 최좌측 인터-핀(222A-1)의 좌측 핀 피치는 최소 핀 피치의 2배보다 더 크고 및/또는 최좌측 인터-핀(222A-1)의 좌측 핀 피치는 최소 핀 피치보다 더 작다. 반대로, 인트라-핀 인접 핀 피치가 최소 핀 피치의 2배와 같도록(다시 말해,  $P_{adjacent-intra} = P_m + P_m = 2P_m$ ), 인트라-핀(222A-2) 중 하나는 최소 핀 피치와 같은 좌측 핀 피치( $P_{L-intra} = P_m$ ) 및 최소 핀 피치와 같은 우측 핀 피치( $P_{R-intra} = P_m$ )를 가진다. 일부 구현에서, 인트라-핀(222A-2)의 좌측 핀 피치 및/또는 우측 핀 피치는 최소 핀 피치보다 더 작다.

- [0034] 본 개시물은 집적 회로 디바이스(200)의 프로세싱 및 제조로부터 발생할 수 있는 인터-핀(222A-1) 및 인트라-핀 (222A-2)의 높이, 폭 및/또는 길이에서의 변화를 고려한다. 도시된 실시예에서, 인터-핀(222A-1) 및 인트라-핀 (222A-2)은 각각의 높이를 따른 테이퍼링 폭을 가지고, 여기서 폭(w<sub>inter</sub>) 및 폭(w<sub>intra</sub>) 각각은 변화하는 폭의 평균을 나타낸다. 예를 들어, 상부 부분의 평균 폭은 하부 부분의 평균 폭보다 더 작도록, 인터-핀(222A-1) 및/또는 인트라-핀(222A-2)의 폭은 인터-핀(222A-1) 및/또는 인트라-핀(222A-2)의 하부 부분으로부터 인터-핀(222A-1) 및/또는 인트라-핀(222A-2)의 상부 부분으로 감소한다. 일부 구현에서, 폭은 폭이 인터-핀(222A-1) 및 인트라-핀(222A-2)을 따라 약 5 nm 내지 약 15 nm로 변화할 수 있다. 인터-핀(222A-1) 및 인트라-핀(222A-2)이 테이퍼링된 폭을 가지는 것으로 도시되더라도, 일부 구현에서, 인터-핀(222A-1) 및/또는 인트라-핀(222A-2)은 그 각각의 높이를 따라 실질적으로 동일한 폭을 가진다.

- [0035] 본 개시물은 많은 서로 다른 실시예를 제공한다. 예시적인 집적 회로 디바이스는 제1 멀티-핀 구조체를 포함하는 고어 영역 및 제2 멀티-핀 구조체를 포함하는 입력/출력 영역을 포함한다. 제1 멀티-핀 구조체는 제1 폭을 가지고 제2 멀티-핀 구조체는 제2 폭을 가지고, 여기서 제1 폭은 제2 폭보다 더 크다. 일부 구현에서, 제1 멀티-핀 구조체는 제1 핀 간격을 가지고 제2 멀티-핀 구조체는 제2 핀 간격을 가지고, 여기서 제1 핀 간격은 제2 핀 간격보다 더 작다. 일부 구현에서, 제1 멀티-핀 구조체는 2개 이하의 핀을 가지고, 제2 멀티-핀 구조체는 3 개 이상의 핀을 가진다. 일부 구현에서, 제1 멀티-핀 구조체의 제1 인접 핀 피치는 최소 핀 피치의 3배보다 크 거나 같고 제2 멀티-핀 구조체의 제2 인접 핀 피치는 최소 핀 피치의 2배보다 작거나 같다. 일부 구현에서, 제1 멀티-핀 구조체는 1 멀티-핀 구조체 및 제2 멀티-핀 구조체는 테이퍼링된 폭을 가지는 핀을 포함한다.

- [0036] 일부 구현에서, 제2 멀티-핀 구조체는 인터-핀 폭을 가지는 인터-핀 및 인트라-핀 폭을 가지는 인트라-핀을 포함하고, 여기서 인터-핀 폭은 인트라-핀 폭보다 더 크다. 일부 구현에서, 인터-핀은 최소 핀 피치의 3배보다 크거나 같은 인터-핀 인접 핀 피치를 가진다. 일부 구현에서, 인트라-핀은 최소 핀 피치의 2배보다 작거나 같은 인트라-핀 인접 핀 피치를 가진다. 일부 구현에서, 집적 회로 디바이스는 제1 멀티-핀 구조체 위에 배치된 제1 게이트 구조체 및 제2 멀티-핀 구조체 위에 배치된 제2 게이트 구조체를 더 포함한다. 일부 구현에서, 코어 영역은 제2 폭보다 더 큰 제3 폭을 가지는 제3 멀티-핀 구조체를 더 포함하고, 여기서 제1 멀티-핀 구조체와 제3 멀티-핀 구조체 사이의 간격은 최소 핀 피치의 2배보다 크거나 같다.

- [0037] 다른 예시적인 집적 회로 디바이스는 기판 위에 배치된 멀티-핀 구조체를 포함하고, 여기서 멀티-핀 구조체는 인터-핀 사이에 배치된 인트라-핀을 포함한다. 인터-핀은 인터-핀 폭을 가지고 인트라-핀은 인트라-핀 폭을 가지고, 여기서 인터-핀 폭은 인트라-핀 폭보다 더 크다. 인터-핀은 최소 핀 피치의 3배보다 크거나 같은 인터-핀 인접 핀 피치를 가진다. 인트라-핀은 최소 핀 피치의 2배보다 작거나 같은 인트라-핀 인접 핀 피치를 가진다. 일부 구현에서, 멀티-핀 구조체는 입력/출력 영역에 배치된다. 일부 구현에서, 인트라-핀 인접 피치는 인트라-핀 중 제1 인트라-핀과 이트라-핀 중 제2 인트라-핀 사이의 제1 피치 및 인트라-핀 중 제1 인트라-핀과 제3 인트라-핀 사이의 제2 피치를 포함한다. 그와 같은 구현에서, 제1 피치 및 제2 피치는 최소 핀 피치와 같다. 일부 구현에서, 집적 회로 디바이스는 멀티-핀 구조체 위에 배치된 게이트 구조체를 포함하고, 여기서 게이트 구조체는 멀티-핀 구조체를 횡단한다. 일부 구현에서, 인터-핀 및 인트라-핀은 테이퍼링된 폭을 가진다. 일부 구현에서, 집적 회로 디바이스는 제1 영역에 배치된 멀티-핀 구조체를 더 포함한다. 그와 같은 구현에서, 인터-핀 인접 피치는 인터-핀 중 인터-핀과 인트라-핀 중 인접 인트라-핀 사이의 제1 피치 및 인터-핀과 제1 영역에 인접한 제2 영역에 배치된 핀 사이의 제2 피치를 포함한다. 제1 피치는 최소 핀 피치와 같다. 제2 피치는 최소 핀 피치의 2배보다 크거나 같다. 일부 구현에서, 제1 영역은 입력/출력 영역이고 제2 영역은 논리 영역이다.

- [0038] 예시적인 방법은 코어 영역에 제1 멀티-핀 구조체를 형성하는 단계, 주변 영역에 제2 멀티-핀 구조체를 형성하는 단계, 및 제1 멀티-핀 구조체 위의 제1 게이트 구조체 및 제2 멀티-핀 구조체 위의 제2 게이트 구조체를 형성하는 단계를 포함한다. 제1 멀티-핀 구조체는 제1 폭을 가진다. 제2 멀티-핀 구조체는 제2 폭을 가진다. 제1 폭은 제2 폭보다 더 크다. 일부 구현에서, 제1 멀티-핀 구조체는 2개 이하의 핀을 가지고 제2 멀티-핀 구조체는 3개 이상의 핀을 가진다. 일부 구현에서, 제1 멀티 핀 구조체의 제1 인접 핀 피치는 최소 핀 피치의 적

어도 3배이고 제2 멀티-핀 구조체의 제2 인접 핀 피치는 최소 핀 피치의 2배보다 작거나 같다. 일부 구현에서, 제1 멀티-핀 구조체 및 제2 멀티-핀 구조체는 동시에 형성된다. 일부 구현에서, 제1 멀티-핀 구조체를 형성하는 단계 및 제2 멀티-핀 구조체를 형성하는 단계는 기판 위에 패터닝된 마스크 층을 형성하는 단계를 포함하고, 여기서 패터닝된 마스크 층은 제1 멀티-핀 구조체를 정의하기 위한 제1 개구 및 제2 멀티-핀 구조체를 정의하기 위한 제2 개구를 포함하고, 패터닝된 마스크 층에 제1 개구 및 제2 개구에 의해 노출되는 기판을 에칭하는 단계를 포함한다. 일부 구현에서, 제1 게이트 구조체 및 제2 게이트 구조체는 더미 게이트를 포함하고, 방법은 더미 게이트를 금속 게이트로 교체하는 단계를 더 포함한다.

- [0039] 본 개시의 실시형태에 따른 집적 회로 디바이스는, 제1 멀티-핀 구조체를 포함하는 코어 영역; 및 제2 멀티-핀 구조체를 포함하는 입력/출력 영역을 포함하고, 상기 제1 멀티-핀 구조체는 제1 폭을 가지고 상기 제2 멀티-핀 구조체는 제2 폭을 가지고, 상기 제1 폭은 상기 제2 폭보다 더 크다.

- [0040] 본 개시의 실시형태에 따른 집적 회로 디바이스에 있어서, 상기 제1 멀티-핀 구조체는 제1 핀 간격을 가지고 상기 제2 멀티-핀 구조체는 제2 핀 간격을 가지고, 상기 제1 핀 간격은 상기 제2 핀 간격보다 더 작다.

- [0041] 본 개시의 실시형태에 따른 집적 회로 디바이스에 있어서, 상기 제1 멀티-핀 구조체는 2개 이하의 핀을 가지고, 상기 제1 멀티-핀 구조체의 제1 인접 핀 피치(adjacent fin pitch)는 최소 핀 피치의 3배보다 크거나 같고, 상기 제2 멀티-핀 구조체는 3개 이상의 핀을 가지고, 상기 제2 멀티-핀 구조체의 제2 인접 핀 피치는 상기 최소 핀 피치의 2배보다 작거나 같다.

- [0042] 본 개시의 실시형태에 따른 집적 회로 디바이스에 있어서, 상기 제2 멀티-핀 구조체는 인터-핀 폭(inter-fin width)을 가지는 인터-핀 및 인트라-핀 폭(intra-fin width)을 가지는 인트라-핀을 포함하고, 상기 인터-핀 폭은 상기 인트라-핀 폭보다 더 크다.

- [0043] 본 개시의 실시형태에 따른 집적 회로 디바이스에 있어서, 상기 인터-핀은 최소 핀 피치의 3배보다 크거나 같은 인터-핀 인접 핀 피치(inter-fin adjacent fin pitch)를 가지고, 상기 인트라-핀은 상기 최소 핀 피치의 2배보다 작거나 같은 인트라-핀 인접 핀 피치(intra-fin adjacent fin pitch)를 가진다.

- [0044] 본 개시의 실시형태에 따른 집적 회로 디바이스에 있어서, 상기 제1 멀티-핀 구조체 및 상기 제2 멀티-핀 구조체는 테이퍼링된 폭(tapered width)들을 가지는 핀들을 포함한다.

- [0045] 본 개시의 실시형태에 따른 집적 회로 디바이스에 있어서, 상기 제1 멀티-핀 구조체 위에 배치된 제1 게이트 구조체 및 상기 제2 멀티-핀 구조체 위에 배치된 제2 게이트 구조체를 더 포함한다.

- [0046] 본 개시의 실시형태에 따른 집적 회로 디바이스에 있어서, 상기 코어 영역은 상기 제2 폭보다 더 큰 제3 폭을 가지는 제3 멀티-핀 구조체를 더 포함하고, 상기 제1 멀티-핀 구조체와 상기 제3 멀티-핀 구조체 사이의 간격은 최소 핀 피치의 2배보다 크거나 같다.

- [0047] 본 개시의 다른 실시형태에 따른 접적 회로 디바이스는, 기판 위에 배치된 멀티-핀 구조체 상기 멀티-핀 구조체는 인터-핀(inter-fin)들 사이에 배치된 인트라-핀(intra-fin)들을 포함함 를 포함하고, 상기 인터-핀들은 인터-핀 폭을 가지고 상기 인트라-핀들은 인트라-핀 폭을 가지고, 상기 인터-핀 폭은 상기 인트라-핀 폭보다 더 크고, 상기 인터-핀들은 최소 핀 피치의 3배보다 크거나 같은 인터-핀 인접 핀 피치(inter-fin adjacent fin pitch)를 가지고, 상기 인트라-핀들은 상기 최소 핀 피치의 2배보다 작거나 같은 인트라-핀 인접 핀 피치 (intra-fin adjacent fin pitch)를 가진다.

- [0048] 본 개시의 다른 실시형태에 따른 집적 회로 디바이스에 있어서, 상기 멀티-핀 구조체는 제1 영역에 배치되고, 상기 인터-핀 인접 피치는 상기 인터-핀들 중 하나의 인터-핀과 상기 인트라-핀들 중 하나의 인접 인트라-핀 사이의 제1 피치 및 상기 인터-핀과 상기 제1 영역 인접인 제2 영역에 배치된 핀 사이의 제2 피치를 포함하고, 상기 제1 피치는 상기 최소 핀 피치와 같고, 상기 제2 피치는 상기 최소 핀 피치의 2배보다 크거나 같다.

- [0049] 본 개시의 다른 실시형태에 따른 집적 회로 디바이스에 있어서, 상기 제1 영역은 입력/출력 영역이고 상기 제2 영역은 논리 영역이다.

- [0050] 본 개시의 다른 실시형태에 따른 집적 회로 디바이스에 있어서, 상기 인트라-핀 인접 피치는 상기 인트라-핀들 중 제1 인트라-핀과 상기 인트라-핀들 중 제2 인트라-핀 사이의 제1 피치 및 상기 제1 인트라-핀과 상기 인트라-핀과 상기 인트라-핀들 중 제3 인트라-핀 사이의 제2 피치를 포함하고, 상기 제1 피치 및 상기 제2 피치는 상기 최소 핀 피치와 같다.

- [0051] 본 개시의 다른 실시형태에 따른 집적 회로 디바이스에 있어서, 상기 멀티-핀 구조체는 입력/출력 영역에 배치되다.

- [0052] 본 개시의 다른 실시형태에 따른 집적 회로 디바이스에 있어서, 상기 인터-핀들 및 상기 인트라-핀들은 테이퍼 링된 폭(tapered width)을 가진다.

- [0053] 본 개시의 다른 실시형태에 따른 집적 회로 디바이스에 있어서, 상기 멀티-핀 구조체 위에 배치된 게이트 구조 체를 더 포함하고, 상기 게이트 구조체는 상기 멀티-핀 구조체를 횡단한다.

- [0054] 본 개시의 또 다른 실시형태에 따른 방법은, 코어 영역에 제1 멀티-핀 구조체 상기 제1 멀티-핀 구조체는 제 1 폭을 가짐 를 형성하는 단계; 주변 영역에 제2 멀티-핀 구조체 상기 제2 멀티-핀 구조체는 제2 폭을 가지고, 또한 상기 제1 폭은 상기 제2 폭보다 더 큼 를 형성하는 단계; 및 상기 제1 멀티-핀 구조체 위의 제1 게이트 구조체 및 상기 제2 멀티-핀 구조체 위의 제2 게이트 구조체를 형성하는 단계를 포함한다.

- [0055] 본 개시의 또 다른 실시형태에 따른 방법에 있어서, 상기 제1 멀티-핀 구조체는 2개 이하의 핀을 가지고, 상기 제1 멀티-핀 구조체의 제1 인접 핀 피치는 적어도 최소 핀 피치의 3배이고, 상기 제2 멀티-핀 구조체는 3개 이상의 핀을 가지고, 상기 제2 멀티-핀 구조체의 제2 인접 핀 피치는 상기 최소 핀 피치의 2배보다 작거나 같다.

- [0056] 본 개시의 또 다른 실시형태에 따른 방법에 있어서, 상기 제1 멀티-핀 구조체 및 상기 제2 멀티-핀 구조체는 동 시에 형성된다.

- [0057] 본 개시의 또 다른 실시형태에 따른 방법에 있어서, 상기 제1 멀티-핀 구조체를 형성하는 단계 및 상기 제2 멀티-핀 구조체를 형성하는 단계는, 기판 위에 패터닝된 마스크 층 상기 패터닝된 마스크 층은 상기 제1 멀티-핀 구조체를 정의하기 위한 제1 개구 및 상기 제2 멀티-핀 구조체를 정의하기 위한 제2 개구를 포함함 을 형성하는 단계; 및 상기 패터닝된 마스크 층에서의 상기 제1 개구 및 상기 제2 개구에 의해 노출된 상기 기판을 에칭하는 단계를 포함한다.

- [0058] 본 개시의 또 다른 실시형태에 따른 방법에 있어서, 상기 제1 게이트 구조체 및 상기 제2 게이트 구조체는 더미 게이트를 포함하고, 상기 방법은 상기 더미 게이트를 금속 게이트로 교체하는 단계를 더 포함한다.

- [0059] 전술한 바는 여러 실시예의 피처를 개략하여 당업자가 본 개시물의 양상을 더 잘 이해할 수 있다. 당업자는 본원에 도입된 실시예의 동일한 목적을 실행하고 및/또는 동일한 장점을 달성하기 위한 다른 프로세스 및 구조체를 설계하거나 수정하기 위한 기반으로서 본 개시물을 용이하게 사용할 수 있음을 인식할 것이다. 당업자는 또한 그와 같은 등가물 구성이 본 개시물의 정신 및 범위로부터 이탈하지 않고, 본 개시물의 정신 및 범위로부터 이탈하지 않고서 본원의 다양한 변경, 치환 및 변형을 행할 수 있음을 인식할 것이다.

### 도면

### 도면1a

## *도면1b*

## *도면1c*

## 도면2a

## 도면2b

## *도면2c*

## 도면3a

## 도면3b

## 도면3c

## 도면4a

## *도면4b*

### 도면4c

## *도면4d*

## *도면4e*

### 도면5a

## 도면5b

### *도면5c*

## *도면5d*

### *도면5e*

### 도면6a

### 도면6b

### 도면6c

## 도면6d

## *도면6e*

### 도면7

## 도면8