# (19) 대한민국특허청(KR)

## (12) 등록특허공보(B1)

(51) Int. Cl.

**H05K 1/02** (2006.01)

(21) 출원번호 10-2009-0087645

(22) 출원일자 **2009년09월16일** 심사청구일자 **2009년09월16일**

(65) 공개번호 **10-2011-0029814**

(43) 공개일자 **2011년03월23일**

(56) 선행기술조사문헌

KR1020090014950 A\*

US20050224912 A1\* KR100867150 B1

JP2008147763 A

\*는 심사관에 의하여 인용된 문헌

(45) 공고일자 2011년06월01일

(11) 등록번호 10-1038236

(24) 등록일자 2011년05월25일

(73) 특허권자

#### 삼성전기주식회사

경기도 수원시 영통구 매탄동 314

(72) 발명자

#### 김한

경기 용인시 수지구 신봉동 LG신봉자이1차아파트 115동 1101호

#### 한미자

전라북도 전주시 완산구 남노송동 41-1 기린봉아 파트 103동 206호

#### 박대현

울산 중구 복산동 장미a 204호

(74) 대리인

특허법인이지

전체 청구항 수 : 총 2 항

심사관 : 김종희

#### (54) 전자기 밴드갭 구조를 구비하는 인쇄회로기판

## (57) 요 약

전자기 밴드갭 구조를 구비하는 인쇄회로기판이 개시된다. 상기 인쇄회로기판은, 노이즈를 차폐하는 전자기 밴드 갭 구조물이 내부에 삽입되는 인쇄회로기판으로서, 상기 밴드갭 구조물은, 제1 도전판; 상기 제1 도전판과 상이한 평면 상에 배치되는 제2 도전판; 상기 제2 도전판과 상이한 평면 상에 배치되는 제3 도전판; 상기 제2 도전판 이 배치되는 평면을 경유하여 상기 제1 도전판과 상기 제3 도전판을 연결하며, 인덕터 소자를 포함하는 스티칭비아부를 포함한다.

#### 대 표 도 - 도4

## 특허청구의 범위

#### 청구항 1

노이즈를 차폐하는 전자기 밴드갭 구조물이 내부에 삽입되는 인쇄회로기판으로서,

상기 밴드갭 구조물은,

제1 도전판;

상기 제1 도전판과 상이한 평면 상에 배치되는 제2 도전판;

상기 제2 도전판과 상이한 평면 상에 배치되는 제3 도전판;

상기 제2 도전판이 배치되는 평면을 경유하여 상기 제1 도전판과 상기 제3 도전판을 연결하는 제1 스티칭 비아부를 포함하고,

상기 제1 스티칭 비아부는.

상기 제2 도전판과 동일 평면 상에 배치되되, 상기 제2 도전판과 전기적으로 분리되는 배선라인부;

상기 배선라인부에 실장된 제1 인덕터 소자;

상기 배선라인부의 일단과 상기 제1 도전판을 전기적으로 연결하는 제1 비아; 및

상기 배선라인부의 타단과 상기 제2 도전판을 전기적으로 연결하는 제2 비아를 포함하는 것을 특징으로 하는 인 쇄회로기판.

### 청구항 2

삭제

## 청구항 3

제1항에 있어서.

상기 제1 도전판을 중심으로 상기 제2 도전판의 반대측 평면 상에 배치되는 제4 도전판;

상기 제3 도전판과 동일한 평면 상에 배치되는 제5 도전판; 및

상기 제4 도전판이 배치되는 평면을 경유하여 상기 제3 도전판과 상기 제5 도전판을 연결하며, 제2 인덕터 소자를 포함하는 제2 스티칭 비아부를 더 포함하는 것을 특징으로 하는 인쇄회로기판.

#### 명 세 서

[0002]

## 발명의 상세한 설명

## 기 술 분 야

[0001] 본 발명은 기판에 관한 것으로서, 보다 구체적으로는 전자기 밴드갭 구조(EBG structure)를 이용하여 전자기 간섭 노이즈(EMI noise)를 저감시킬 수 있는 노이즈 저감 기판에 관한 것이다.

## 배경기술

EMI(Electromagnetic interference) 문제는 전자제품의 동작주파수가 고속화되면서 고질적인 노이즈 문제로 인식되어 왔다. 특히, 최근 들어 전자제품의 동작주파수가 수십 MHz ~ 수 GHz 대로 되면서 이러한 EMI 문제는 더더욱 심각해져서 해결책이 절실히 필요한 상황이다. 특히, 기판에서의 EMI 문제 중에서 기판 에지(edge)에서 발생하는 노이즈의 해결책에 대한 연구가 이루어지지 않아, 기판에서의 노이즈를 전면적으로 차단하는데 한계를 가지고 있다.

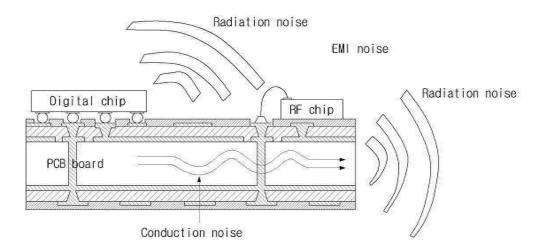

- [0003] EMI 노이즈는 어느 하나의 전자회로, 소자, 부품 등에서 발생한 전자기파(EM wave)가 다른 회로, 소자, 부품 등으로 전달됨으로써 간섭에 의한 노이즈 문제를 발생시키는 원인이 되는 노이즈를 말한다. 이와 같은 EMI 노이즈를 크게 분류하면, 방사 노이즈(radiation noise)와 전도 노이즈(conduction noise)로 나눌 수 있다.

- [0004] 이 중, 기판의 상부(즉, 전자부품의 탑재면)로 방사되는 방사 노이즈의 경우에는 메탈 캡 등의 전자기 차폐용 캡으로 기판 상부 영역을 쉴드(shield)함으로써 해결하는 방식이 일반적이지만, 전도 노이즈의 저감을 위한 방법을 찾는 것은 매우 어려운 일이다. 또한, 이러한 문제는 디지털 전자기기의 동작주파수가 증가하면서, 점점 복잡해져 해결이 더욱 더 어려워 지고 있다.

#### 발명의 내용

#### 해결 하고자하는 과제

[0005] 본 발명은 인덕터 소자를 활용하여 보다 다양한 주파수 대역의 노이즈를 용이하게 저감시켜 공간 활용도, 제조비용, 소비 전력 등의 측면에서도 유리한 이점을 갖는 EMI 노이즈 저감 인쇄회로기판을 제공한다.

#### 과제 해결수단

- [0006] 본 발명의 일 측면에 따르면, 노이즈를 차폐하는 전자기 밴드갭 구조물이 내부에 삽입되는 인쇄회로기판으로서, 상기 밴드갭 구조물은, 제1 도전판; 상기 제1 도전판과 상이한 평면 상에 배치되는 제2 도전판; 상기 제2 도전 판과 상이한 평면 상에 배치되는 제3 도전판; 및 상기 제2 도전판이 배치되는 평면을 경유하여 상기 제1 도전판 과 상기 제3 도전판을 연결하며, 제1 인덕터 소자를 포함하는 제1 스티칭 비아부를 포함하는 것을 특징으로 하 는 인쇄회로기판이 제공된다.

- [0007] 상기 제1 도전판과 상기 제3 도전판은 동일 평면 상에 배치될 수 있으며, 상기 스티칭 비아부는, 상기 제2 도전 판과 동일 평면 상에 배치되되, 상기 제2 도전판과 전기적으로 분리되며, 상기 인덕터 소자를 포함하는 배선라인부; 상기 배선라인부의 일단과 상기 제1 도전판을 전기적으로 연결하는 제1 비아; 및 상기 배선라인부의 타단과 상기 제2 도전판을 전기적으로 연결하는 제2 비아를 포함할 수 있다.

- [0008] 또한, 상기 제1 도전판을 중심으로 상기 제2 도전판의 반대측 평면 상에 배치되는 제4 도전판; 상기 제3 도전판과 자동일한 평면 상에 배치되는 제5 도전판; 및 상기 제4 도전판이 배치되는 평면을 경유하여 상기 제3 도전판과 상기 제5 도전판을 연결하며, 제2 인덕터 소자를 포함하는 제2 스티칭 비아부를 더 포함할 수도 있다.

#### 直 과

[0009] 본 발명의 바람직한 실시예에 따르면, 인덕터 소자를 활용하여 보다 다양한 주파수 대역의 노이즈를 용이하게 저감시켜 공간 활용도, 제조 비용, 소비 전력 등의 측면에서도 유리한 이점이 있다.

## 발명의 실시를 위한 구체적인 내용

- [0010] 본 발명은 다양한 변환을 가할 수 있고 여러 가지 실시예를 가질 수 있는 바, 특정 실시예들을 도면에 예시하고 상세한 설명에 상세하게 설명하고자 한다. 그러나, 이는 본 발명을 특정한 실시 형태에 대해 한정하려는 것이 아니며, 본 발명의 사상 및 기술 범위에 포함되는 모든 변환, 균등물 내지 대체물을 포함하는 것으로 이해되어야 한다.

- [0011] 본 발명을 설명함에 있어서, 관련된 공지 기술에 대한 구체적인 설명이 본 발명의 요지를 불필요하게 흐릴 수 있다고 판단되는 경우 그 상세한 설명을 생략한다. 또한, 본 명세서의 설명 과정에서 이용되는 숫자(예를 들어, 제1, 제2 등)는 하나의 구성요소를 다른 구성요소와 구분하기 위한 식별기호에 불과하다.

- [0012] 본 실시예에 따른 인쇄회로기판은, 도 1에 도시된 바와 같이 어느 하나의 전자회로, 소자 등(예를 들면 디지털

칩)에서 발생한 전자기파가 다른 회로, 소자 등(예를 들면 RF 칩)으로 전달되는 현상을 방지하기 위해, 그 내부에 전자기 밴드갭 구조물이 구비된다. 즉, 인쇄회로기판 내부에 삽입된 전자기 밴드갭 구조물이 노이즈를 차폐하는 것이다.

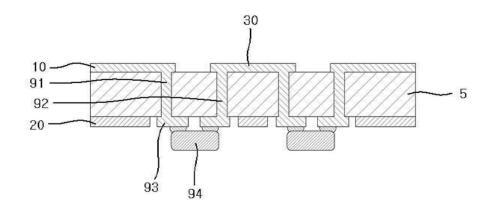

- [0013] 전자기 밴드갭 구조물은, 제1 도전판(10)과, 상기 제1 도전판(10)과 상이한 평면 상에 배치되는 제2 도전판(20); 상기 제2 도전판(20)과 상이한 평면 상에 배치되는 제3 도전판(30); 및 상기 제2 도전판(20)이 배치되는 평면을 경유하여 상기 제1 도전판(10)과 상기 제3 도전판(30)을 연결하는 제1 스티칭 비아부(90)를 포함한다. 여기서 제1 스티칭 비아부(90)에는 제1 인덕터 소자(94)가 구비되며, 제1 스티칭 비아부(90)는 제2 도전판(20)에 형성된 클리어런스 홀(22)에 의해 제2 도전판(20)과는 전기적으로 분리된다.

- [0014] 이러한 전자기 밴드갭 구조물은, 제1 스티칭 비아부(90) 내에 제1 인덕터 소자(94)가 포함됨으로써, 필터회로로 서의 특성을 쉽고도 다양하게 변경할 수 있는 장점이 있다. 이러한 특성에 대한 보다 구체적인 내용은 추후에 다시 설명하도록 한다.

- [0015] 전자기 밴드갭 구조물은, 전도되는 노이즈를 차폐할 필요가 있는 곳에 적절히 배치될 수 있으며, 필요에 따라 1 열 또는 2열 이상으로 배치될 수도 있다.

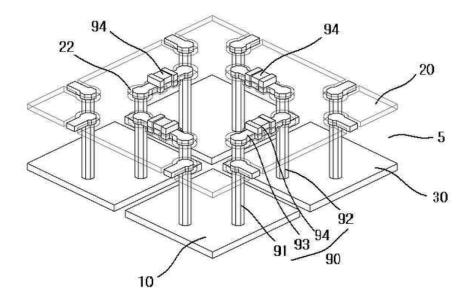

- [0016] 한편, 도 2 및 도 4에 도시된 바와 같이, 상기 제1 스티칭 비아부(90)는 제2 도전판(20)과 동일 평면 상에 배치되며 인덕터 소자(94)를 포함하는 배선라인부(93)와, 상기 배선라인부(93)의 일단과 상기 제1 도전판(10)을 전기적으로 연결하는 제1 비아(91), 및 상기 배선라인부(93)의 타단과 상기 제2 도전판(20)을 전기적으로 연결하는 제2 비아(92)를 포함할 수 있다. 이러한 구조의 경우, 인덕터 소자(94)를 단순히 배선라인부(93)의 표면에 실장함으로써, 인덕터 소자(94)가 스티칭 비아부(90)에 포함되도록 할 수 있는 장점이 있다.

- [0017] 도 2 및 도 4를 통해 도시된 구조물이 특정 주파수 대역의 신호를 차폐하는 전자기 밴드갭 구조물로서 기능할 수 있는 원리는 다음과 같다.

- [0018] 제2 도전판(20)과 제1 및 제3 도전판(10, 30) 사이에는 유전층(5)이 개재되며, 이에 의해 제2 도전판(20)과 제1 및 제3 도전판(10, 30) 간 그리고 이웃하는 제1 도전판(10)와 제3 도전판(30) 간에 형성되는 캐패시턴스 (capacitance) 성분이 존재한다. 또한, 제1 스티칭 비아부(90)에 의하여 이웃하는 2개의 도전판(10, 30) 간에는 제1 비아(91) -> 배선라인부(93) 및 인덕터 소자(94) -> 제2 비아(92)를 경유하는 인덕턴스(inductance) 성분도 존재하게 된다.

- [0019] 이때, 캐패시턴스 성분은 제2 도전판(20)과 제1 및 제3 도전판(10, 30) 간, 및 이웃하는 2개의 도전판(10, 30) 간의 이격 간격, 유전층(5)을 구성하는 유전 물질의 유전율, 도전판의 크기, 형상, 면적 등과 같은 팩터에 의해 그 값이 변화된다.

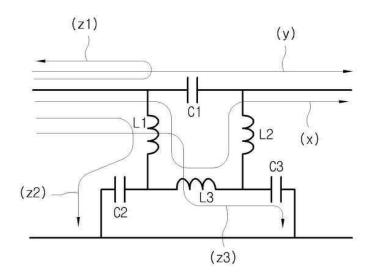

- [0020] 인덕턴스 성분 또한 제1 비아(91), 제2 비아(92) 그리고 연결 패턴(243a)의 형상, 길이, 두께, 폭, 단면적 등과 같은 팩터에 의해 그 값이 변화된다. 따라서, 상술한 다양한 팩터들을 적절히 조정, 설계하게 되면, 도 2에 도시된 구조물을 목적 주파수 대역의 특정 신호 또는 특정 노이즈의 제거 또는 차폐를 위한 전자기 밴드갭 구조 (electro bandgap structure)로서 활용할 수 있다. 이는 도 3의 등가회로도를 통해 쉽게 이해할 수 있을 것이다.

- [0021] 도 3의 등가회로도를 도 2의 전자기 밴드갭 구조물과 비교하여 설명하면, 인덕턴스 성분인 L1은 제1 비아(91)에 해당되고, 인덕턴스 성분인 L2는 제2 비아(92)에 해당되며, 인덕턴스 성분인 L3는 배선라인부(93) 및 인덕터 소자(94)에 해당된다. C1은 제1 및 제3 도전판(10, 30)과 그 상부에 위치할 다른 임의의 유전층 및 제2 도전판(20)에 의한 캐패시턴스 성분이고, C2 및 C3는 배선라인부(93)을 기준으로 그와 동일 평면에 위치한 제2 도전판(20)과 그 하부에 위치할 다른 임의의 유전층 및 제2 도전판(20)에 의한 캐패시턴스 성분이다. 위와 같은 등가회로도에 도시된 바와 같이, 도 2의 전자기 밴드갭 구조물은 특정 주파수 대역의 신호를 차폐하는 필터회로로서의 기능을 수행하게 된다.

- [0022] 한편, 본 실시예에 따르면 스티칭 비아부(90) 중간에 인덕터 소자(94)가 연결됨으로써, 인덕턴스(L3) 값을 자유롭게 변경할 수 있어, 같은 크기로도 낮은 주파수대에서 저지대역(Stopband) 특성을 구현할 수 있다. 또한, 다양한 인덕턴스 값을 가지는 소자를 실장함으로 인해, 여러 개의 저지대역 주파수를 만들 수도 있고, 차폐할 수있는 주파수의 대역폭(bandwidth)을 넓힐 수도 있다.

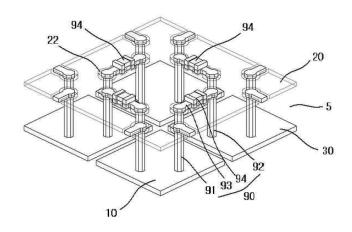

- [0023] 도 4에는 전자기 밴드갭 구조물이 반복적으로 배치되어 있는 모습이 도시되어 있다. 이 때 제2 도전판(20)에는 클리어런스 홀(22)이 형성되어 스티칭 비아부(90), 보다 구체적으로는 배선라인부(93)와 제2 도전판(20)은 서로

전기적으로 분리될 수 있게 된다.

- [0024] 한편, 도 2 및 도 4에는 2층 구조를 갖는 인쇄회로기판에 형성된 전자기 밴드갭 구조물이 도시되어 있으나, 도 5에 도시된 바와 같이 3층 이상의 다층 구조의 인쇄회로기판에 전자기 밴드갭 구조물이 마련될 수도 있음은 물론이다. 도 5의 참조번호 6은 유전층을 나타내고, 참조번호 7은 별도의 층을 구성하는 금속층을 나타낸다.

- [0025] 뿐만 아니라, 도 6에 도시된 바와 같이, 제1 금속판(10)과 제2 금속판(20) 사이에 별도의 금속층(8)이 마련되고, 각각의 비아(91, 92)들이 금속층(8)을 관통하는 구조를 가질 수도 있다.

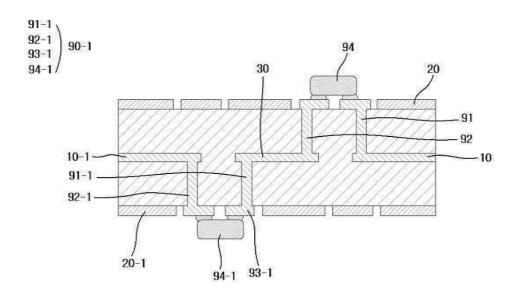

- [0026] 또 다른 한편, 도 7에 도시된 바와 같이 제1 도전판(10)을 중심으로 제2 도전판(20)의 반대측 평면 상에 배치되는 제4 도전판(20-1); 제3 도전판(30)과 동일한 평면 상에 배치되는 제5 도전판(10-1); 및 상기 제4 도전판(20-1)이 배치되는 평면을 경유하여 상기 제3 도전판(30)과 상기 제5 도전판(10-1)을 연결하며, 제2 인덕터 소자 (94-1)를 포함하는 제2 스티칭 비아부(90-1)를 더 포함할 수도 있다. 이 경우, 제2 인덕터 소자(94-1)는 제2 배선라인부(93-1)의 표면에 실장될 수 있다.

- [0027] 즉, 인쇄회로기판이 3층 이상의 다층 구조를 갖는 경우, 복수 개의 인덕터 중 일부(94)는 인쇄회로기판의 상면 방향에 실장되고, 또 다른 일부(94-1)는 인쇄회로기판의 하면 방향에 실장될 수도 있는 것이다. 이러한 구조의 경우, 인쇄회로기판의 양면을 모두 활용함으로써, 전자기 밴드갭 구조물의 설계 자유도를 향상시켜 보다 다양한 주파수 특성을 갖는 필터를 구현할 수 있게 된다.

- [0028] 한편, 전술한 도전판들이 모두 일정한 크기 및 형상으로 이루어질 수도 있을 것이나, 설계 상의 필요 등에 따라 각각 다른 크기, 다른 형상으로 이루어질 수도 있음은 물론이다.

- [0029] 상기에서는 본 발명의 바람직한 실시예를 참조하여 설명하였지만, 해당 기술 분야에서 통상의 지식을 가진 자라면 하기의 특허 청구의 범위에 기재된 본 발명의 사상 및 영역으로부터 벗어나지 않는 범위 내에서 본 발명을 다양하게 수정 및 변경시킬 수 있음을 이해할 수 있을 것이다.

- [0030] 전술한 실시에 외의 많은 실시예들이 본 발명의 특허청구범위 내에 존재한다.

#### 도면의 간단한 설명

- [0031] 도 1은 인쇄회로기판 내에서 노이즈가 발생하는 모습을 나타내는 도면.

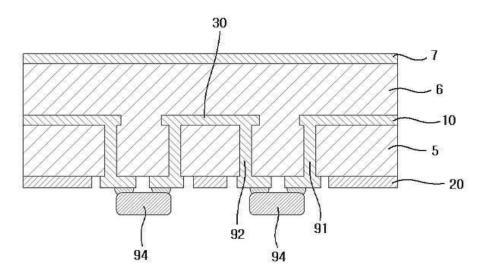

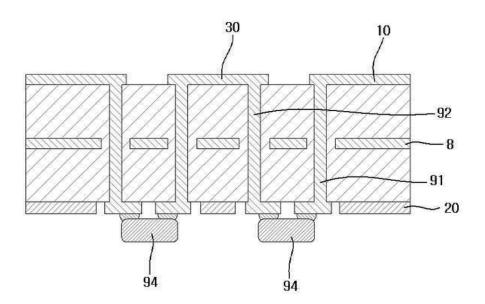

- [0032] 도 2는 본 발명의 일 실시예에 따른 전자기 밴드갭 구조를 구비하는 인쇄회로기판을 나타내는 단면도.

- [0033] 도 3은 도 2의 전자기 밴드갭 구조의 등가회로도.

- [0034] 도 4는 본 발명의 일 실시예에 따른 전자기 밴드갭 구조를 구비하는 인쇄회로기판을 나타내는 사시도.

- [0035] 도 5 내지 도 7은 본 발명의 다른 실시예들에 따른 전자기 밴드갭 구조를 구비하는 인쇄회로기판을 나타내는 단면도.

- [0036] <도면의 주요부분에 대한 부호의 설명>

- [0037] 10: 제1 도전판

- [0038] 20: 제2 도전판

- [0039] 30: 제3 도전판

- [0040] 90, 90-1: 스티칭 비아부

- [0041] 94, 94-1: 인덕터 소자

## 도면1