# (19) **日本国特許庁(JP)**

# (12) 公 表 特 許 公 報(A)

(11)特許出願公表番号

特表2004-519009 (P2004-519009A)

(43) 公表日 平成16年6月24日(2004.6.24)

(51) Int.C1.7

$\mathbf{F} \mathbf{I}$

テーマコード (参考) 2HO92

GO2F 1/1343

GO2F 1/1343

\_\_\_\_

## 審査請求 未請求 予備審査請求 未請求 (全 50 頁)

(21) 出願番号 特願2002-563071 (P2002-563071) (86) (22) 出願日 平成14年1月25日 (2002.1.25) (85) 翻訳文提出日 平成15年5月27日 (2003.5.27) (86) 国際出願番号 PCT/1B2002/000216 (87) 国際公開番号 W02002/063386

(87) 国際公開日 平成14年8月15日 (2002. 8. 15)

(31) 優先権主張番号 0102756.4

(32) 優先日 平成13年2月3日(2001.2.3)

(33) 優先権主張国 英国 (GB)

(81) 指定国 EP (AT, BE, CH, CY, DE, DK, ES, FI, FR,

GB, GR, IE, IT, LU, MC, NL, PT, SE, TR), JP, KR

(71) 出願人 590000248

コーニンクレッカ フィリップス エレク トロニクス エヌ ヴィ Koninkliike Philips

Koninklijke Philips Electronics N. V. オランダ国 5621 ベーアー アイン ドーフェン フルーネヴァウツウェッハ

Groenewoudseweg 1, 5 621 BA Eindhoven, T he Netherlands

(74)代理人 100087789

弁理士 津軽 進

(74) 代理人 100114753

弁理士 宮崎 昭彦

最終頁に続く

## (54) 【発明の名称】透明導体ラインの導電率を改善する方法

# (57)【要約】

基板(46)上に担持される透明導電ライン(32)( 特には、小マスク数工程を用いて製造されるアクティブ マトリクス液晶表示器等のピクセル化された装置用のア クティブプレート上のアドレスライン)の導電率を改善 する方法が、透明導電材料(例えば、ITO)の被着層 (53)から上記基板上に上記ラインを形成すると共に 、これらラインの上面上に少なくとも一つの端部(75 )から延び且つ該上面を部分的に覆うような被覆層(7 2')を設けるステップと、次いで上記端部にメッキ電 位が印加された状態で上記ラインをメッキ(80)する 電気メッキ処理を実行するステップとを含む。上記被覆 層(72')は、上記ラインの長さに沿って一層均一な メッキ層(80)を達成するよう補助する。該被覆層は 、好ましくは、透明層(53)をパターニングするため に使用される被着フォトレジスト層(54)の選択的パ ターニング及び部分的エッチングにより規定されたフォ トレジストを有する。ピクセル化された装置においては 、ピクセル電極(38)も上記透明層から規定される。

#### 【特許請求の範囲】

## 【請求項1】

基板上に担持された透明導電材料を有するラインの導電率を改善する方法において、

前記透明導電材料のラインを前記基板上に形成すると共に、これらラインの各々の上面に上記ラインの端部から延び且つ該ラインの前記上面を部分的に覆うような被覆層を設けるステップと、

前記ラインに金属電気メッキ処理を施すステップであって、該処理においてはメッキ電位が前記各ラインに前記端部で印加され、これにより金属層が前記ラインの露出された表面の領域にメッキされ、該メッキの間において前記被覆層が該層の下に位置する前記ラインの表面を遮蔽するように作用するステップと、

を有することを特徴とする方法。

#### 【請求項2】

請求項1に記載の方法において、前記被覆層は前記ラインの前記露出された表面が前記端部から離れるにつれて漸進的に増加するように成形されていることを特徴とする方法。

#### 【請求項3】

請求項2に記載の方法において、前記被覆層は前記端部から離れるにつれて幅が先細りに成形されていることを特徴とする方法。

#### 【請求項4】

請求項2に記載の方法において、前記被覆層は前記ラインに沿って幅が階段状に成形されていることを特徴とする方法。

#### 【請求項5】

請求項1ないし4の何れか一項に記載の方法において、前記被覆層は前記ラインの両端から同様の態様で延在し、前記メッキ電位は前記メッキ処理の間において前記ラインの前記両端において印加されることを特徴とする方法。

#### 【請求項6】

請求項1ないし5の何れか一項に記載の方法において、前記被覆層がフォトレジストを有することを特徴とする方法。

#### 【請求項7】

請求項1ないし6の何れか一項に記載の方法において、前記ラインを形成するステップが

前記基板上に透明導電材料の層を被着するステップと、

前記透明導電材料の層上にフォトレジストの層を被着すると共に、該フォトレジストを前 記所望のラインに対応する形状にパターニングするステップと、

前記透明導電層を前記フォトレジストを用いてパターニングし、前記透明導電材料のラインを残存させるステップと、

を有していることを特徴とする方法。

#### 【請求項8】

請求項7に記載の方法において、前記フォトレジスト層は前記所望のラインに対応する部分にパターニングされ、これら部分の各々は第1の厚さを有すると共に前記所要の被覆層の形状に従うような選択された領域を含み、前記部分の残部は減少された厚さのものであり、前記透明導電層をパターニングした後に前記フォトレジスト層は部分的にエッチングされて前記減少された厚さの領域を除去する一方、前記選択された領域においてはフォトレジストを残存させ、該フォトレジストが前記被覆層を構成するようにすることを特徴とする方法。

#### 【請求項9】

請求項7又は請求項8に記載の方法であって、前記導電ラインと共に前記基板上に担持された透明導電材料のピクセル電極を有するようなピクセル化された装置の製造に使用する方法において、前記フォトレジスト層は前記所望のピクセル電極にも対応する形状にパターニングされ、前記透明導電層は前記フォトレジストを用いてパターニングされ、ピクセル電極領域を残存させることを特徴とする方法。

10

20

30

40

#### 【請求項10】

請求項9に記載の方法において、前記電気メッキ処理の間において前記ピクセル電極領域 上にフォトレジストが残存されることを特徴とする方法。

## 【請求項11】

ピクセル化された装置用のアクティブプレートを形成する方法において、

絶縁基板上にゲート導体層を被着及びパターニングするステップと、

前記パターニングされたゲート導体層上にゲート絶縁層を被着するステップと、

前記ゲート絶縁層上にシリコン層を被着するステップと、

前記シリコン層上に透明導体層を被着するステップと、

前記透明導体層上に、ソース及びドレイン領域、ピクセル電極領域並びに前記ソース又はドレイン領域に関連する導体ライン領域を規定するような形状を有するようにフォトレジスト層を被着及びパターニングするステップと、

前記透明導体層を前記フォトレジストを用いてパターニングし、ソース及びドレイン、ピクセル電極並びに導体ラインを形成するステップと、

前記フォトレジストを、前記各導体ライン上に該ラインの一端部から延び且つ該ラインの 表面を部分的に覆うフォトレジスト領域を残存させるように規定するステップと、

前記透明導体ラインの露出された領域を、前記各ラインの前記端部にメッキ電位が印加されるようにして金属層で選択的に電気メッキするステップと、

を有していることを特徴とする方法。

## 【請求項12】

請求項11に記載の方法において、前記フォトレジスト層は前記導体ラインにおいて異なる厚さの領域にパターニングされ、前記フォトレジストを規定するステップは該フォトレジストを部分的にエッチングして薄い領域を除去するステップを有していることを特徴とする方法。

## 【請求項13】

請求項11又は請求項12に記載の方法において、前記フォトレジストは前記各ライン上に他端部から延びる同様のフォトレジスト領域を残存させるように規定され、前記メッキ電位が前記他端部においても印加されることを特徴とする方法。

# 【請求項14】

請求項11ないし13の何れか一項に記載の方法により作製されたアクティブプレートと、該アクティブプレートから離隔された電極構造を担持する他の基板と、前記アクティブプレートと前記他の基板との間に配設された液晶とを有することを特徴とするアクティブマトリクス液晶表示装置。

## 【発明の詳細な説明】

# [0001]

## 【発明の属する技術分野】

本発明は、基板上に担持された透明導電ラインの導電率を改善する方法に関する。特に、本発明はアクティブマトリクス液晶表示器等のピクセル化された装置における透明導電材料を有するアドレスラインの導電率を増加させることに関するものである。また、本発明は、斯様な表示器の製造に使用される、アクティブプレートとして知られているトランジスタ基板にも関する。

## [0002]

## 【従来の技術】

アクティブマトリクス液晶表示器(AMLCD)は、典型的には、アクティブプレートとパッシブプレートとを有し、これらプレートの間に液晶材料が挟持される。アクティブプレートはトランジスタスイッチング装置のアレイを有し、典型的には1つのトランジスタが当該表示器の1つのピクセルに関連される。また、各ピクセルはアクティブプレート上にピクセル電極を有し、該電極には個々のピクセルの表示出力を制御するために信号が印加される。液晶表示器は、透過型又は反射型の装置として構成することができる。

# [0003]

50

20

30

40

20

30

40

50

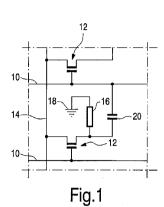

図1は、AMLCDの或る既知の例のアクティブプレートのピクセルを形成する電気構成要素を示している。ピクセルは行及び列に配列されている。或るピクセルの行アドレス導体10はTFT12のゲートに接続され、列アドレス導体14はソースに結合されている。該ピクセルのピクセル電極上に設けられた液晶材料は実効的に液晶セル16を規定し、該セルはトランジスタ12のドレインと共通接地面18との間に接続される。任意選択的なピクセル蓄積コンデンサ20が、トランジスタ12のドレインと、隣接する行のピクセルに関連する行導体10との間に接続される。

[0004]

透過型表示器に関しては、上記アクティブプレートの大きな面積が少なくとも部分的に透明であり、これは、該表示器が典型的にはバックライトにより照明されるために必要である。従来の表示装置においては、ピクセル電極は透明でなければならない一方、行及び列導体は金属製の不透明ラインとして形成される。高導電率故に、クロム、モリブデン、アルミニウム、合金又は多層構造等の金属層が行及び列導体のために使用され、上記高導電率が装置性能を改善する。ピクセル駆動信号が供給されるライン(通常は、列ライン)の導電率は、大型の表示器では特に重要である。何故なら、ラインの長さにわたってかなりの電圧降下が生じ、該ライン(列)に沿う全てのピクセルを一様に駆動することを不可能にするからである。

[0005]

金属製列導体の使用に伴う問題点は、列導体及びピクセル電極を形成するために別個の被着及びリソグラフィック手順が必要とされる点にある。ピクセル電極は透明でなければならず、典型的には透明導電性酸化膜から形成される。製造工程におけるリソグラフィック手順は、当該製造工程の経費に対する主要な寄与要因であることが良く知られている。各リソグラフィックステップが、当該工程の歩留まりを減少させると共に経費を増加させると考えられる。

[0006]

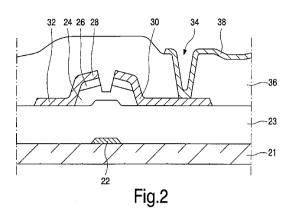

LCDのアクティブプレートに関する従来の製造工程は 5 マスク工程である。図 2 に示されたボトムゲートTFT LCDアクティブプレートに関しては、各々が別個のマスク規定を必要とする処理ステップは:

(i)基板21上にゲート22(これは、行導体の一部である)を規定するステップ;

(ii)下側の真性層 2 4 及び上側のドーピングされた接触層 2 6 を有するような、アモルファスシリコン島部(これは、全体の構造を被覆するゲート誘電体 2 3 に重なる)を規定するステップ;

( i i i ) 金属製のソース 2 8 、ドレイン 3 0 及び列電極 3 2 を規定するステップ;

( i v ) 全体の基板を被覆するパシベーション層 3 6 に接触孔 3 4 を規定するステップ; 及び

( v ) 上記孔 3 4 を介してドレイン 3 0 と接触する透明なピクセル電極 3 8 を規定するステップ;

である。

[0007]

図 1 に示したコンデンサは、 1 つのピクセル電極の隣接する行の行 / ゲート導体の一部との重なり領域を設けることにより上記ゲート誘電体から簡単に形成することができる。

[0008]

経費を低減し且つ歩留まりを向上させるために、リソグラフィックステップの数(従って、マスクのカウント)を低減する種々の提案がなされている。

[0009]

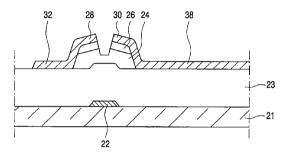

例えば、列導体をピクセル電極と同一の透明導電性酸化膜から形成し、ピクセル構造のこれら要素が一緒に被着及びパターン化することができるようにすることが提案されている。追加の対策の結果、2マスク工程が得られ、これを、図3に示されたボトムゲートTFT LCDアクティブプレートを参照して説明する。各々が別個のマスク規定を要するような処理ステップは:

( i ) ゲート 2 2 ( 及び行導体 ) を規定するステップ; 及び

( i i ) 透明な列導体 3 2 (これは、TFTのソース 2 8 も形成する)及びピクセル電極 3 8 (これは、TFTのドレイン 3 0 も形成する)を規定するステップ;である。

#### [ 0 0 1 0 ]

半導体島部24、26の規定は、例えば基板を介しての露光を使用することにより、ゲート22を用いた自己整合処理により達成することができる。勿論、該半導体は第3のマスクステップ(上記ステップ(i)及び(ii)の間の)によっても等しく形成することができる。当該アレイの周辺部において、ゲート誘電体23は低精度工程を用いてエッチング除去され、当該表示器の周辺部における上記ゲートへの接触を可能にする。

#### [0011]

この構成において、上記列ラインに使用される透明導電性酸化物薄膜の高抵抗率は、該構造の大型(TVサイズの)表示器への又は例えばVGAを超える高解像度表示器への使用を妨げる。

# [0012]

このような理由により、上記層の列導体領域を導電率を増加させるように処理する。一方、でけたい電極の透明性に影響を与えないますることであろうが、この技術により電気メッキすることであろうが、この技術に大きな変動が生じる斯かるラインの抵抗性の性質のため、ラインの長さにわたりメッキ厚で変動が生じる順向があるといい。当日の変動は極めて好ましくない。「DD93」がよっている。斯様ない。「DD93」がよっている。「DD93」がよっては、近くなが、「側壁の銅の電気メッキによる透明電極の導電率の向上では、銅のバスを金属酸化物の列ラインの側部に電気メッキによる透明電極の導電率を向上させる方法を開示している。該工程は金属酸化物の電気メッキによることにより導電率を向上させる方法を開示している。前のが国難であると共に、制御するのが困難である。加えて、上記・のがいるがいるである。この処理は複雑であると共に、制御するのが困難である。加えて、上記・のがの、この処理は複雑であると共に、制御するのが困難である。加えて、上記・ののがは、この処理は複雑であると共に、制御するのが困難である。から、この処理は複雑であると共に、制御するのが困難である。から、この処理は複雑であると共に、制御するのが困難である。また、ソースとドレインとの間の短絡の危険性がある。また、ソースは、カースを形成する際の速いが、カースを形成する際のである。また、ソースは、カースを形成する際のでは、カースをである。また、カースをである。

# [0013]

国際特許出願公開第WO99/59024号は、透明電極の導電率を、該透明電極に隣接 してパターン化された金属層を設けることにより向上させる方法を開示している。

#### [0014]

# 【発明が解決しようとする課題】

依然として、ITO等の透明金属酸化物層の薄膜ラインの導電率を工程の複雑さを著しく増加させることなしに向上させるような簡単且つ信頼性のある工程に対する要求が存在する。斯様な工程は、アクティブマトリクスLCDの製造に用途を見出すものであるが、透明導電層を少なくとも或る領域において他の領域における透明性を失うことなく一層導電的にすることができるなら、マスクのカウントの低減を達成することができるような他の技術においても有効であろう。これは、高分子LED及び大面積画像センサにとっても有益であり得る。

#### [0015]

## 【課題を解決するための手段】

本発明の第 1 態様によれば、基板上に担持された透明導電材料を有するラインの導電率を 改善する方法であって、

# [0016]

上記基板上に上記透明導電材料のラインを形成し、これらラインの各々の上面に、当該ラインの一端部から延びると共に該ラインの上記上面を部分的に被覆する被覆層を設けるステップと、

# [0017]

50

10

20

30

40

上記ラインに金属電気メッキ処理を施すと共に、該処理においてはメッキ電位が各ラインに対し上記端部において印加されるようにし、これにより金属層が当該ラインの露出表面領域上にメッキされ、上記被覆層がメッキの間において該層の下に位置する当該ラインの表面を遮蔽するように作用するステップと、

を有するような方法が提供される。

#### [0018]

この方法によれば、上記透明導電材料のメッキの結果、上記ラインの大幅に改善された導 電率が得られる。重要なことに、そして上記被覆層を使用する結果として、得られた金属 メッキは、上面が完全に露出されたラインを電気メッキする場合に得られる金属メッキ層 と比 較 し て 、 一 層 滑 ら か で 且 つ 当 該 ラ イ ン の 長 さ に 沿 っ て 厚 さ が 一 層 均 一 に な る 傾 向 が あ る。この改善は、メッキ処理における上記被覆層の効果によりもたらされるもので、メッ キ の 間 に お い て 発 生 す る 電 流 の 性 質 及 び 斯 か る 性 質 の メ ッ キ 層 特 性 に 対 す る 帰 結 の 理 解 の 結果である。上記透明導電ラインは、基本的に抵抗的であり、浴の陽極電位に対して一端 が陰極メッキ電位に維持された状態でメッキ浴内に配置された場合、一連の分散された抵 抗と等価であると見なすことができ、この結果、上記一端に最も近い部分を介して流れる 電流が最も大きくなる傾向にある。金属被着速度は電流に比例するので、メッキはこの部 分において一層速くなる。この結果、上記部分は一層導電的にされ、これがメッキを加速 させ、従ってメッキの不均一さを悪化させる。結果として、当該ラインに沿って得られる メッキ層の厚さは上記端部から離れる領域においてよりも該端部に向かって著しく大きく な る で あ ろ う 。 上 記 被 覆 層 の 配 設 は 、 上 記 端 部 領 域 に お い て 導 電 は 依 然 と し て 当 該 ラ イ ン の全幅を介してのものとなるが、当該表面の部分的面積のみにしかメッキが施されず、大 部分の面積は上記端部から離れた部分で関わることになることを意味する。このことは、 上記端部から離れる領域の抵抗が減少する傾向となり、向上されたメッキに繋がることを 意味する。当該ラインに沿って依然としてメッキの不均一さは存在するであろうが、その 程度は著しく減少する。

## [0019]

上記被覆層は、単に、当該ラインの長さに沿って一部延在する略一定幅の細条を有することができる。しかしながら、好ましくは一層良好な結果のために、上記層は該ラインの透明導電材料の表面の被覆されていない領域が前記端部から当該ラインに沿って離れるにつれて漸進的に増加するように成形される。例えば、該被覆層は先細りとすることができる。他の例として、上記層の形状は、該層の幅が当該ラインに沿って階段状に減少するようなものとすることができる。

#### [0020]

好ましくは、上記メッキ電位は当該ラインの反対側の端部にも印加されるようにすると共に、上記被覆層は該端部からもラインに沿って同様の態様で延在するように構成し、かくして例えば対称な被覆層パターンを形成するようにする。

#### [ 0 0 2 1 ]

上記被覆層は、好ましくは、フォトレジスト材料を有するものとする。

## [0022]

上記電気メッキ処理に続いて、上記被覆絶縁層は当該ラインから除去することができ、そ 40の後に、所望ならば更なる電気メッキ処理を実行することができる。

#### [0023]

透明導電材料の上記ラインは、

基板上に透明導電材料の層を被着し、

上記透明導電材料の層上にフォトレジストの層を被着すると共に、該フォトレジストを所望のラインに対応する形状にパターニングし、

上記透明導電層を上記フォトレジストを用いてパターニングし、透明導電材料のラインを 残存させる、

ことにより都合良く形成することができる。

## [0024]

50

20

30

30

40

50

この場合、上記被覆絶縁層は適切な層を被着することにより別個に設けることもできるが、これは、この層を所要の形状に規定するために更なるパターニングを必要とするであろう。

#### [0025]

特に好ましい実施例においては、上記透明導電材料のラインを規定するために使用される フォトレジスト層は、これらライン上に上記被覆層を設けるためにも使用される。この目 的のため、上記フォトレジストの層は所要のラインに対応する部分にパターニングするこ とができ、各部分が第1の厚さを有すると共に上記被覆層に必要とされるものに形状が対 応するような選択された領域を含むようにし、該部分の残部が減少された厚さのものとす ることができる。上記のフォトレジスト層の規定された部分は、エッチング処理により下 に位置する透明導電材料の層をパターニングし、所要のラインを残存させるために使用さ れる。その後、これらライン上に残存するフォトレジストの部分は部分的にエッチングさ れて、上記の減少された厚さ領域のものに対応する厚さが除去される。この結果、フォト レジストは前記被覆層を構成する上記選択領域に残存され、当該ラインの表面の残部は露 出されて、電気メッキ処理が実行される準備が整う。所望の異なる厚さのパターンを得る ための上記フォトレジスト層のパターニングは、SID 00ダイジェストの第1006 ~ 1 0 0 9 頁に公開された" TFT-LCD用の新規な 4 マスク数工程のアーキテクチャ "なる題名の文献にC.W. Kim他により記載された種類のフォトリソグラフィック パターニング工程を用いて達成することができる。上記の記載された技術(TFTチャン ネルを規定する方法に関するものである)は、所謂、スリット又はグレイトーンフォトリ ソグラフィを使用し、これは、(陽型)フォトレジストを中実(不透明)領域、透明領域 及び格子又はスリットパターンを持つ領域からなるフォトリソグラフィックマスクを介し て露光する過程を伴う。上記中実及び透明領域は、(完全な厚さで)残存されるべき及び 除去されるべき領域を各々規定するよう作用する一方、上記スリットパターンを有する領 域 は 結 果 と し て 部 分 的 露 光 と な り 、 該 露 光 は 当 該 フ ォ ト レ ジ ス ト の 現 像 の 際 に 当 該 領 域 が 残存されるが、減少された厚さで残存されることに繋がる。

## [0026]

上記被覆絶縁層を形成するために斯様な方法でフォトレジスト材料を使用することにより 、所要のマスクステップの数は少ないままとなる。

#### [0027]

前記金属メッキ層は、好ましくは、銅又は銀を有するものとし、上記透明導電層は、好ましくは、ITO(インジウム錫酸化物)のような導電性酸化物を有するものとする。

#### [0028]

透明導電ラインの導電率を向上させる本方法は、上記ラインがアドレス指定の目的で使用されるような液晶表示器(アクティブマトリクス及びパッシブマスクの両方)、LED表示器、PDP(プラズマ表示パネル)表示器及び画像センサ等のピクセル化された装置の製造に特に有効である。斯様な装置においては、上記ラインに関連する透明ピクセル電域、好都合にも、これらラインに使用されるのと同一の透明導電層から形成することができると共に、フォトレジスト層の適切なパターニングにより同一のフォトレジスト層にあいて規定することができる。好ましくは、上記ピクセル電極を遮蔽するために、電気メッキ処理の間においてフォトレジスト材料は斯かるピクセル電極上に残存するようには、完全な厚さのフォトレジストを上記ピクセル電極上に規定することができるいて、前記部分的エッチングステップに引き続いてフォトレジストは上記電極上に依然として残存する。

# [0029]

本発明の第2の態様によれば、ピクセル化された装置用のアクティブプレートを形成する方法であって、

絶 縁 基 板 上 に ゲ ー ト 導 体 層 を 被 着 及 び パ タ ー ニ ン グ す る ス テ ッ プ と 、

前記パターニングされたゲート導体層上にゲート絶縁層を被着するステップと、

前記ゲート絶縁層上にシリコン層を被着するステップと、

前記シリコン層上に透明導体層を被着するステップと、

前記透明導体層上に、ソース及びドレイン領域、ピクセル電極領域並びに前記ソース又はドレイン領域に関連する導体ライン領域を規定するような形状を有するようにフォトレジスト層を被着及びパターニングするステップと、

前記透明導体層を前記フォトレジストを用いてパターニングし、ソース及びドレイン、ピクセル電極並びに導体ラインを形成するステップと、

前記フォトレジストを、前記各導体ライン上に該ラインの一端部から延び且つ該ラインの 表面を部分的に覆うフォトレジスト領域を残存させるように規定するステップと、

前記透明導体ラインの露出された領域を、前記各ラインの端部にメッキ電位が印加されるようにして金属層で選択的に電気メッキするステップと、

を有するような方法が提供される。

#### [0030]

上記フォトレジスト層は好ましくは上記導体ラインにおいて異なる厚さの領域にパターニングされ、上記フォトレジストを規定するステップは該フォトレジストを部分的にエッチングして薄い領域を除去するステップを有する。この方法は、ゲート導体が第1リソグラフィック工程を用いて被着及びパターニングされ、フォトレジスト層が第2リソグラフィック工程を用いて被着及びパターニングされるような2マスク工程が使用されるのを可能にし、上記シリコン層は上記ゲート導体に自己整合される。

## [0031]

## 【発明の実施の形態】

以下、本発明の実施例を、添付図面を参照して例示として詳細に説明する。尚、各図は概念的なものであって、実寸通りには描かれていないことに注意すべきである。また、これら図の各部の寸法及び比率は、明瞭化のために及び図面の便宜上誇張され又は縮尺されている。また、全図を通して同一の符号は同一の又は類似の部分を示すように使用されている。

## [0032]

アクティブマトリクス液晶表示器のアクティブプレートを製造する小マスク数工程への本発明の適用を図 5 A ないし 5 H を参照して説明するが、これら図は該製造工程を種々の段階で示している。該工程の最初のステップは、既知の 2 マスクエ程と共通している。

### [0033]

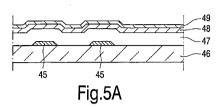

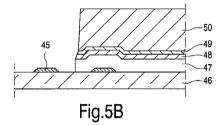

図 5 A は、小マスク数工程の最初のステップの概略図である。例えばCr、Al、Mo又はこれらの組合せを有するゲート金属 4 5 が絶縁基板 4 6 上に被着されると共に湿式又は乾式エッチング技術を用いて規定されており、標準のバックチャンネルエッチTFT積層被着(Back Channel Etch TFT stack

deposition)が実施されている。これは、窒化シリコンゲート絶縁層47、アモルファスシリコン層48、及び接触面として作用するドーピング(n+)されたシリコン層49を形成し、これら層は全体の基板面上に設けられる。図5Aの右側の領域は表示ピクセルに関連するスイッチングトランジスタ(図1の12)を形成するために使用され、該図5Aの左側部分は、行導体に駆動信号を供給することが可能な行リードイン領域を形成する。典型的には、SiNゲート絶縁体47は400nm厚であり、真性アモルファスシリコン48は160nm厚であり、上記のドーピングされたアモルファスシリコン48は160nm厚であり、上記のドーピングされたアモルファスシリコンは40nm厚である。もっとも、他の厚さの層も使用することができる。ドーピングされたシリコン層49は、良好な品質のITO対シリコン接触を提供するために微小結晶性シリコンとすることもできる。

# [0034]

上記TFT積層部は、行リードイン領域からエッチング分離されねばならない。これは粗い位置合わせしか必要とせず、精細な形状をエッチングする必要はない。このマスキングステップは、印刷により、エッチング前にプラスチックシートを当該アレイ領域上に積層することにより、又は図5Bに示されたように粗く位置合わせされた印刷フォトレジスト

20

10

30

40

50

20

30

40

50

50を用いて実施することができる。図5Cにおいては、上記TFT積層部は行リードイン領域からエッチング分離されており、陽型フォトレジスト51が全体のプレートに塗布される。

[0035]

次いで、図5Dに示されるように、上記陽型フォトレジストがゲートライン構造と同一のパターンを有するようにパターニングするために背面照射が使用される。残存する上記フォトレジスト層は、上記2つのシリコン層をパターニングし、図5Eにおけるトランジスタチャンネル領域52及びそれ以外の場所ではゲートライン(行導体)構造上に重なる領域を残存させるために使用される。次いで、図5Fに示されるように、例えばスパッタリング形成されたITO等の透明導電層53が全体のプレート上に形成される。

[0036]

透明導電層 5 3 は、後述するように、TFT用のソース及びドレイン、透明ピクセル電極、並びに薄膜列アドレスラインを形成するために使用される。かくして、再び図 3 を参照すると、この層は、関連する列導体ラインに結合されたTFTソースコンタクト 2 8、及び各ピクセル電極 3 8 に接続されたTFTドレインコンタクト 3 0 を形成する。もし要するならば、上記ピクセル電極とゲート導体(行)ライン 4 5 との重なりが、介在するゲート誘電体と共に、蓄積コンデンサ(図 1 )を形成することができる。

[0037]

図5Aないし5Fに示されたステップは、概ね、既知の方法に従っている。

[0038]

薄膜列ラインの導電率を改善するために、これら部分は以下に述べるような方法で金属により選択的に電気メッキされる。

[0039]

図5 Gを参照すると、陽型フォトレジスト層5 4 が基板4 6 上の構造上全体に被着される。この層5 4 は層5 3 から形成されるべき構成部分を規定するような形状、即ち図5 Hに示されたソース及びドレインコンタクト領域に対応する領域5 5 及び5 6、ピクセル電極に対応する領域5 7 並びに行リードインパターンに対応する領域5 8、更に図5 Hでは見えないが上記ソースコンタクト5 5 に一体的に結合された列ラインを有するような形状、にパターニングされる。次いで、上記層のうちの上記パターニングされたフォトレジストにより覆われていない領域は、湿式又は乾式エッチング工程を用いてエッチング除去される。

[0040]

上記フォトレジスト層54は、フォトレジストを選択された領域に異なる厚さで残存させ るように、既知ではあるが通常ではない方法でパターニングされる。好適なフォトリソグ ラフィックパターニング技術の例が、 C . W . Kim他による前記文献、 及び第 1 8 回 国際表示器研究会議(アジア表示器 ′98)のSID会報の第1109ないし1112頁 に公開されたC.W./ Han他による"新しいフォトリソグラフィを用いて4マスク 工程により製造されたTFT"なる題名の文献に記載されているので、これら文献を参照 されたいと共に、これら文献の内容は本明細書に参考文献として組み込まれるものである 。 上 記 パ タ ー ニ ン グ 処 理 は 、 光 阻 止 領 域 、 透 明 領 域 及 び 所 定 の 格 子 又 は ス リ ッ ト パ タ ー ン を持つ領域からなるマスクを介しての上記フォトレジスト層54(ここでは、陽型フォト レジスト)の露光を伴う。上記光阻止及び透明領域は、通常のマスクにおけるように、当 該フォトレジストにおける残存すべき及び除去されるべき領域を各々規定するように作用 する。上記スリットのパターンを有する領域は、部分的に露光される領域を規定するため に使用され、この目的のために要するパターンのパラメータは上記文献に記載されている 。この部分的露光(上記スリットにより生成される回折効果に依存する)の結果、上記フ ォトレジストの当該領域は該フォトレジストの現像の後に、上記マスクの光阻止領域によ り規定された完全な厚さの領域と較べて減少された厚さで残存するようになる。従って、 本 質 的 に 、 該 技 術 は フ ォ ト レ ジ ス ト 層 が 異 な り 及 び 制 御 さ れ た 厚 さ を 持 つ よ う な 領 域 に 選 択的にパターニングされ、且つ、当該フォトレジストが完全に除去されるような領域を形

30

40

50

成するのを可能にする。図 5 Hにおける領域 5 5 、 5 6 、 5 7 及び 5 8 は全て上記マスクの光阻止領域により規定されており、結果として完全な厚さのフォトレジスト領域を有する。一方、列ラインは更に上記マスクにおけるスリットパターンを用いて規定され、結果として異なる厚さのフォトレジストの特別な構造となる。

#### [ 0 0 4 1 ]

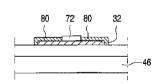

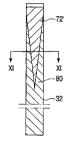

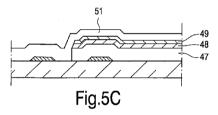

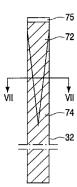

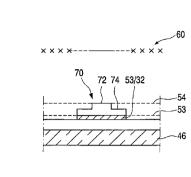

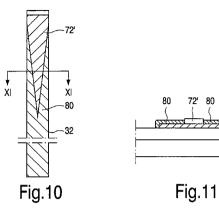

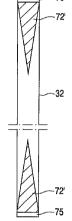

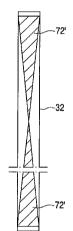

図6は上記製造工程でのこの段階における列ライン32の典型的な1つの一部を概略平面図として示し、図7は図6のVII・VII線に沿う断面図である。列ライン32は、全長に沿って略一定な幅及び厚さを有する透明導電層53の長尺細条を有し、パターニング後にフォトレジスト層54の領域70により規定される。図6において斜線により示す該フォトレジスト層の領域70は、層54をパターニングするのに使用されたマスクの光阻止領域により形成された第1領域72と、該マスクのスリット領域により形成された厚さが減少されたフォトレジストの第2領域74とからなっている。このようにして上記フォトレジスト層をパターニングにするのに使用されたマスクの部分は図7では60に概念的に図示され、光阻止領域、透明領域及びスリットパターン領域は実線、×印及び点線により各々表されている。

#### [0042]

2 レベルレジストパターン 7 0 における第 1 領域 7 2 の形状は、以下で明らかとなるであろう理由により注意深く制御される。図 6 に見られるように、領域 7 2 はライン 3 2 の一方の端部 7 5 から反対側の端部に向かって延び、当該ラインの表面を部分的に覆っている。領域 7 2 は、該領域 7 2 により被覆されるライン 3 2 の表面の面積の程度が上記端部 7 5 から離れるにつれて減少するように(この場合は、領域 7 2 が漸進的に先細りとされると共にライン 3 2 の中心線に対して対称である)、逆に、薄いフォトレジスト領域 7 4 により被覆される当該ラインの表面の面積が漸進的に増加するように成形されている。

### [ 0 0 4 3 ]

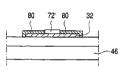

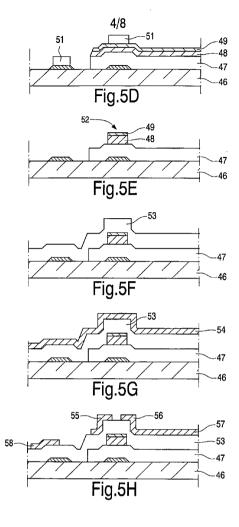

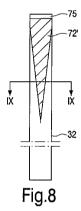

次いで、上記フォトレジストパターンには部分的エッチング処理が施され、該処理において薄い領域74の厚みに対応する該レジストパターンの厚さは完全に除去され、結果として図8及び9の平面及び断面図に示すような構造が得られる。ここでは減少された厚さを持つことになるレジストの第1領域72は、72′に示すように依然として当該ライン上に存在する一方、該ライン32の表面の残部は、ここでは、露出されることになる。前述したように、ソース及びドレインコンタクト、ピクセル電極並びに行リードインパターンに各々対応する当該フォトレジスト層の領域55及び56、57並びに58は完全な厚さのレジストのものであり、従って、この部分的エッチングの後でも厚さは減少されるものの依然として残存する。

# [ 0 0 4 4 ]

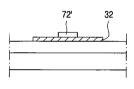

次いで、透明導電列ライン32には選択的電気メッキ処理が施され、該処理において該ラインの露出面上に金属の層がメッキされる。この目的のために、好ましくは銅が使用されるが、代わりに銀等の他の金属も使用することができる。この選択的メッキの前に、上記透明導電ラインの露出領域は、例えば酸又は中性電解液内での還元処理を用いて前処理することができる。当該電気メッキのために、所要の陰極メッキ電位が各ライン32の端部75に印加されるが、この目的のために該ラインの端部はフォトレジストが無いままとされる。該電気メッキ処理の結果、当該ラインの露出面上に金属層が形成され、レジスト領域72,は直下表面領域のメッキを防止する遮蔽として作用する。これが図10及び11に示され、これら図において上記金属メッキは80に示されている。

# [0045]

この処理の間における上記ライン32上の保護レジスト領域72°の存在は、それ以外の場合よりも一層滑らか及び一様なメッキが得られることを保証する。ライン32に使用される材料(例えば、ITO)の抵抗率及び結果としての電流の不均一な分布により、当該メッキ層において不均一さが生じようとし、メッキ速度、従ってメッキ厚は上記メッキ電圧が印加される当該ラインの端部に向かって一層大きくなる。典型的には、電気メッキされる場合、被覆されていないラインに対しては、当該点の近く及び遠くでのメッキ厚に1

30

40

50

0以上の係数の差が存在し得る。

## [0046]

金属被着の速度は、電流の流れに比例する。ライン32は、一端において陰極電位に接続され、当該ラインの長さに沿う多数の離隔された位置において電解液の抵抗により構成される抵抗を介してメッキ陽極に接続された一連の分散された抵抗と等価であると見なすことができる。この場合、ライン32の上記陰極に近い領域における抵抗が上記電解液の抵抗より大幅に小さくない限り、この領域における当該ラインの電流は上記陰極から更に離れるよりも大幅に大きくなるであろう。従って、被覆されていないラインが電気メッキをおよりも大幅に大きなる。メッキ金属はライン32より一層導電的であるから、これが一個域の抵抗は急激に減少し、これが被着の更に一層の増加に繋がり、かくして、当該問題を増大させ、ライン32の長さに沿うメッキ層の厚さの更に一層の不均一さを生じさせる。

# [0047]

上記の被覆層72,の存在は、この種の影響を、或る程度電流の分布に影響を与えるこにより制御するよう作用し、結果としたのと同様の一種の分散された抵抗パターン大幅にない、導電は層72,により部分的に被覆される領域においてはライン32の全幅を介したである。しかしながら、ここで、当該ラインの開始点では対応したのまりに対応してライン32の領域の部分的生じる一方、改造部のよりに対応してラインの領域の部分的より、当該ラインの端部から一層離れるでは対の実効抵抗は上記端部領域と較べて減少する傾向となる。この結果、当該ラインにあるが、当該ラインの結果によりがのよりとなる。この非均しとなる。な然として、幾らかの厚さの非均しも大幅に少ないメッキ厚特性は改善される。依然として、幾らかの厚さの非均しも大幅に少ないる方が、できる。できる。

## [0048]

当該ライン上における保護レジスト領域72~の、従って該ラインの露出された領域の形状は、このことを考慮して選定される。

### [0049]

メッキ電圧が当該ラインの一端のみに印加され、図8及び10に示すように該レジスト領域72′が該一端から面積が単純に徐々に減少する代わりに、メッキ電圧はライン32の両端に印加することもできる。この場合、レジスト領域72′の形状は、それに応じて、図12Aに概念的に示すように該ライン32の中点を通る線に対して略対称となるように変更される。該レジスト被覆層の可能性のある他の形状は、ライン32の長さに沿う被覆層の延在が増加されるような図12Bに、及び該被覆層の幅が滑らかに先細りされるというよりも階段状にされるような図12Cにも示されている。

## [0050]

以上、被覆層に関して特定の形状を図示したが、該層の形状及び寸法は変更することができ、例えばライン32の特性及びメッキ処理パラメータに依存すると共にこれらにより或る程度決定されるであろうと理解される。これらの要因は、所望の結果を達成するために要する該被覆層の形状を選択する場合に考慮されるであろう。一般的に言って、該被覆層は最良の結果を得るためには当該ラインの長さのかなりの割合にわたり延在しそうである

# [0051]

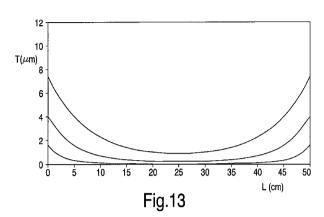

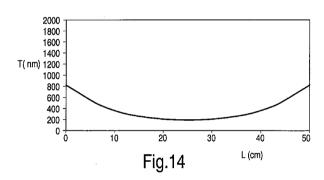

図 1 3 は、銅メッキ層のマイクロメータでの厚さTと、当該ラインの長さに沿う位置Lとの間の関係であって、メッキ処理の間においてメッキ電圧が該ラインの両端に印加される場合に如何なる被覆レジストも無い平らなITOラインの表面上に電気メッキすることにより形成される場合に予測され得る関係を示すグラフである。該グラフに示された異なる

20

30

40

50

曲線は、最も薄い場合の約50秒から最も厚い場合の約200秒までにわたる異なるメッキ時間に関する結果である。該ITO ラインは50cm長で、20 $\mu$ mの一定幅を有している。本例で使用された重要なメッキパラメータに関しては、浴導電率は約40 m  $^{-1}$  となるように選定され、電流密度(J)は約1A/dm $^{-2}$ (=100A/m $^{-2}$ )となるように選定され、陽極-陰極(ライン32)距離は約50cmである。明らかなように、得られた銅メッキの厚さは、ITO ラインの中間(25cm)におけるよりも端部に向かって10倍以上も厚くなり得る。

[0052]

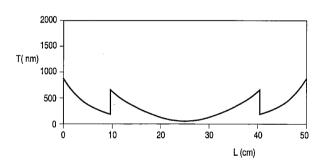

比較のために、図14に図示されたグラフは、銅メッキ層のナノメータでの厚さTと、同様の寸法のITOラインに沿う位置Lとの関係であって、該ラインが表面上に図12Aに図示した形態の保護レジスト領域72~を有している場合に期待することができる関係を示している。メッキパラメータは上記と同様のままである。このグラフに示される曲線は、約800秒のメッキ時間に相当する。ここでは、ライン32の両端部は、さもなければ末端で発生するであろう著しく増加したメッキ厚を防止するために、メッキ処理の間において慎重に機械的に遮蔽された。明らかなように、当該ラインに沿うメッキ厚の変動は大幅に目立たないようになっている。

[0053]

図 1 3 及び 1 4 に示された結果から、比肩し得る平均厚において、図 1 4 の場合のライン 3 2 の長さに沿う厚さの変動は約 3 倍程度に過ぎないのに対し、図 1 3 の場合、この変動は 1 0 倍程度までにもなることが分かる。

[0054]

得られるメッキ層の厚さは、望ましくは、最も薄い部分(即ち、当該ラインの中間周辺)において約100nmであり、好ましくは100nmと500nmとの間である。

[0055]

もっと簡単な形状のレジスト領域72′を使用する場合にさえも、メッキ層特性の改善された結果が可能である。図15は、ここでも50cm長及び20μm幅のITOライン32を示し、該ラインは両端に(前述したのと同様の処理を用いて)設けられた長方形のレジスト領域72′を単に有している。これら2つの領域の各々は18μmの幅(w)と10cmの長さ(1)とを有し、露出されたITOの1μm幅の細条が両側に存在するように該ITOラインの中央に配置されている。図16のグラフは、斯様なラインを先のものと同様の電気メッキパラメータを用いてメッキした場合に得られることが期待されるようなメッキ厚特性を示している。

[0056]

ここで、図10を再び参照すると、メッキ層80が形成された後、前記フォトレジストパターンの残部、即ち領域72<sup>~</sup>は除去される。

[0057]

当該製造工程の最後において、上記ITO列ラインは表面上に銅の層を有し、該層は大型の高解像度表示器をアドレスするのに要する一層高い導電率を提供する。

[0058]

該向上された導電率の列が、上記実施例に示されるような小マスク数技術と共に使用される場合、斯かる行ライン上に位置するアモルファスシリコンは寄生TFTを生じ、これらが当該表示器の駆動に影響を与え得る。これらの影響は駆動方法において調節することができ、慎重な設計により最小化することができる。

[0059]

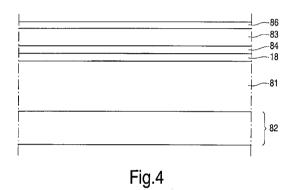

図4は完全な液晶表示器の構造を示している。液晶材料の層81がアクティブプレート82上に設けられ、該プレートは上述したような構造を有している。他の基板83が上記液晶材料層に重なっている。この他の基板83には、一方の面上にカラーフィルタ84及び共通電極層18(図1に図示)を規定するプレートの配列が設けられている。また、該基板の反対側には偏光膜86も設けられている。

[0060]

20

30

40

50

本発明の該実施例は主にトランジスタ基板と該基板の製造に関するものであるから、該液晶表示器の動作及び構造は、これ以上詳細には説明しない。斯様な点は当業者には明らかであろう。

[0061]

上述した特定の例はITOの透明列ライン上に銅メッキを設ける。他の導電性酸化物透明材料も使用することができ、他の金属をメッキすることもできる。これらの可能性は本発明の範囲内に入るものである。

[0062]

レジストの一部を上述した方法により好都合に形成すると共にライン上の保護領域72<sup>・</sup>として利用することができるが、斯様な領域は、例えば他の好適な材料を被着及びパターニングすることにより、代わりに他の方法で形成することができると思われる。もっとも、これは当該製造工程に更なるマスキング段階を追加することになるであろう。

[0063]

上述したものに対して付加的な層を設けることもでき、当業者にとり自明な種々の代替案も存在する。本発明は既知の個々の処理ステップ及び材料に依存するものであるので、本出願においては特定の処理パラメータ及び材料は詳細には説明されていない。可能性のある代替案のステップ及び範囲は当業者にとり明らかであろう。

[0064]

上記特定の実施例はLCDのアクティブプレートにアモルファスシリコンTFTを使用しているが、多結晶及び微小結晶等の他の半導体構成も可能である。

[0065]

上述した特定の実施例においては、ボトムゲートトランジスタが使用されたが、トップゲートトランジスタも使用することができる。事実、本発明は、透明ピクセル電極が必要とされ、ピクセル電極を規定する層の被着とライン(行又は列)導体とを組み合わせることに利益が存在するような如何なるピクセル化された装置にも適用することが可能である。

[0066]

本発明は、アクティブマトリクスLCDに適用された場合について詳細に説明された。本発明は、更に、例えばパッシブ型LCD、アクティブマトリクスLED表示器及び画像センサにも適用することができる。また、本発明は、当該装置のピクセル電極用と同一の層を用いて行又は列アドレスラインを規定することが有益であるような、透明ピクセル電極を必要とする如何なるピクセル化された装置にも適用することが可能である。また、本発明は透過型及び反射型のアクティブマトリクスLCD表示器にも適用可能である。反射型表示器の場合にも、ITOはソース及びドレインコンタクトの形成に関し周知の利点を有しているので、透明層を使用することが依然として望ましい。

[0067]

上述した実施例においては、透過型表示器が示され、ピクセル電極はメッキ処理から遮蔽されている。反射型表示器の場合は、ピクセル電極は列導体と共にメッキされてもよい。この場合、ライン32及びピクセル電極は、フォトレジスト領域72′が除去された後の第2電気メッキ工程において金属により再び電気メッキすることができ、これは以前に形成されたメッキを強化すると共に、ライン32の新たに露出された表面領域も被覆する。

[0068]

本開示を熟読することにより、当業者にとっては他の変形例も明らかとなるであろう。斯様な変形例は、アクティブマトリクス液晶表示器等の分野で既知であると共に、ここで既述した特徴の代わりに又は斯かる特徴に付加して使用することができるような他の特徴を含むことができる。

【図面の簡単な説明】

【図1】図1は、アクティブプレートのピクセル要素を示す。

【図2】図2は、5マスク工程を使用して製造された、ボトムゲートTFTを使用する従来のアクティブプレートを示す。

【図3】図3は、2マスク工程を使用して製造された、ボトムゲートTFTを用いる提案

されたアクティブプレートを示す。

- 【図4】図4は、全体の液晶表示器の構造を示す。

- 【図 5 A 】図 5 A は、本発明を用いてLCD表示器のアクティブプレートを製造する製造工程における或る段階を示す。

- 【図5B】図5Bは、本発明を用いてLCD表示器のアクティブプレートを製造する製造工程における次の段階を示す。

- 【図5C】図5Cは、本発明を用いてLCD表示器のアクティブプレートを製造する製造工程における次の段階を示す。

- 【図5D】図5Dは、本発明を用いてLCD表示器のアクティブプレートを製造する製造工程における次の段階を示す。

- 【図5E】図5Eは、本発明を用いてLCD表示器のアクティブプレートを製造する製造工程における次の段階を示す。

- 【図5F】図5Fは、本発明を用いてLCD表示器のアクティブプレートを製造する製造工程における次の段階を示す。

- 【図5G】図5Gは、本発明を用いてLCD表示器のアクティブプレートを製造する製造工程における次の段階を示す。

- 【図5H】図5Hは、本発明を用いてLCD表示器のアクティブプレートを製造する製造工程における次の段階を示す。

- 【図6】図6は、上記アクティブプレートの典型的な導体ラインの或る製造段階における 平面図である。

- 【図7】図7は、図6のVII-VII線に沿う断面図である。

- 【図8】図8は、前記アクティブプレートの典型的な導体ラインの別の製造段階における 平面図である。

- 【図9】図9は、図8のIX-IX線に沿う断面図である。

- 【図 1 0 】図 1 0 は、前記アクティブプレートの典型的な導体ラインの別の製造段階における平面図である。

- 【図11】図11は、図10のXI-XI線に沿う断面図である。

- 【図12A】図12Aは、導体ラインの形成の他の形態を概念的に平面図として示す。

- 【図12B】図12Bは、導体ラインの形成の他の形態を概念的に平面図として示す。

- 【図12C】図12Cは、導体ラインの形成の他の形態を概念的に平面図として示す。

- 【図13】図13は、既知の電気メッキ処理を用いた導体ラインに沿う電気メッキ層の厚さと位置との間の関係を示すグラフである。

- 【図14】図14は、本発明による方法を用いた導体ラインに沿う電気メッキ層の厚さと位置との間の関係を示すグラフである。

- 【図15】図15は、導体ラインの形成の更に他の形態の概略平面図である。

- 【図16】図16は、図15の導体ライン形成法を用いた導体ラインに沿う電気メッキ層の厚さと位置との間の関係を示すグラフである。

10

20

30

## 【国際公開パンフレット】

#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization International Bureau

#

# (43) International Publication Date 15 August 2002 (15.08,2002)

PCT

# WO 02/063386 A2

(51) International Patent Classification7: G02F 1/1345, 1/1362, H01L 31/18, 51/20

J.; Prof. Holstlaan 6, NL-5656 AA Eindhoven (NL). DE KUBBER, Daan, L.; Prof. Holstlaan 6, NL-5656 AA Eindhoven (NL).

(21) International Application Number: PCT/IB02/00216

(22) International Filing Date: 25 January 2002 (25.01.2002)

(74) Agent: WILLIAMSON, Paul, L.; Internationaal Octoobbrean B.V., Prof. Holstlaan 6, NL-5656 AA Bindhoven (NL).

(25) Filing Language:

Linglish (81) Designated States (national): JP. KR.

(26) Publication Language:

English

(30) Priority Data: 0102756.4 3 February 2001 (03.02.2001) GB

(84) Designated States (regional): European patent (AT, BE, CH, CY, DB, DK, ES, FI, FR, GB, GR, IE, FI, LU, MC, NL, PT, SE, TR).

(71) Applicant: KONINKLIJKE PHILIPS ELECTRON-ICS N.V. [NL/NL]; Groenewoudseweg 1, NL-5621 BA Eindhoven (NL).

#### Published:

without international search report and to be republished upon receipt of that report

(72) Inventors: FRENCH, Ian, D.; Prof. Holstlaan 6, NL-5656 ΛΛ Eindhoven (NL). VAN DER ZAAG, Pieter,

For two-letter codes and other abbreviations, refer to the "Guid-ance Notes on Codes and Abbreviations" appearing at the begin-ning of each regular issue of the PCT Gazette.

(54) Title: METHOD OF IMPROVING THE CONDUCTIVITY OF TRANSPARENT CONDUCTOR LINES

(57) Abstract: A method of improving the electrical conductivity of transparent conducting lines (32) carried on a substrate (46), particularly address lines on the active plate for a pixellated device such as an active matrix liquid crystal display or the like fabricated to sing a low mask count process, involves forming the lines on the substrate from a deposited player of transparent conducting material (33), e.g., ITO, and provided on their upper surface with a covering layer (72') extending from at least one end (75) and partially covering the surface, and then performing an electroplating operation to plate the lines (80) with a plating tential being applied at that end. The covering layer (72') assists in achieving a more uniform plated layer (80) along the length of the line. The covering layer preferably comprises photoresist defined by selective patterning and partial etching of a deposited photoresist layer (54) used for patterning the transparent layer (55). In a pixellated device, pixel electrodes (38) are also defined from the transparent layer.

PCT/1B02/00216

# METHOD OF IMPROVING THE CONDUCTIVITY OF TRANSPARENT CONDUCTOR LINES

This invention relates to a method of improving the electrical conductivity of transparent conducting lines carried on a substrate. In particular the invention is concerned with increasing the conductivity of addressing lines comprising transparent conducting material in pixellated devices such as active matrix liquid crystal displays. The invention also relates to the transistor substrate, known as the active plate, used in the manufacture of such displays.

An active matrix liquid crystal display (AMLCD) typically comprises an active plate and a passive plate between which liquid crystal material is sandwiched. The active plate comprises an array of transistor switching devices, typically with one transistor associated with each pixel of the display. Each pixel also has a pixel electrode on the active plate to which a signal is applied for controlling the display output of the individual pixel. Liquid crystal displays may be arranged as transmissive or reflective devices.

Figure 1 shows the electrical components which make up the pixels of one known example of active plate of an AMLCD. The pixels are arranged in rows and columns. The row address conductor 10 of a pixel is connected to the gate of the TFT 12, and the column address conductor 14 is coupled to the source. The liquid crystal material provided over a pixel electrode of the pixel effectively defines a liquid crystal cell 16 which is connected between the drain of the transistor 12 and a common ground plane 18. An optional pixel storage capacitor 20 is connected between the drain of the transistor 12 and the row conductor 10 associated with an adjacent row of pixels.

For transmissive displays, a large area of the active plate is at least partially transparent, and this is required because the display is typically illuminated by a back light. In conventional display devices, the pixel electrode

PCT/IB02/00216

2

must be transparent, whereas row and column conductors are formed as metallic opaque lines. Metallic layers, such as chromium, molybdenum, aluminium, alloys or multilayer structures, are used for the row and column conductors because of the high conductivity, which improves the device performance. The conductivity of the lines (usually the column lines) to which the pixel drive signals are applied is particularly important in large displays, because a sizeable voltage drop occurs over the length of the line, making it impossible to drive uniformly all pixels along the line (column).

A problem with the use of metallic column conductors is that separate deposition and lithographic procedures are required to form the column conductors and the pixel electrodes. The pixel electrodes must be transparent, and are typically formed from a transparent conductive oxide film. It is well known that the lithography steps in the manufacturing process are a major contributing factor to the expense of the manufacturing process. Each lithographic step can be considered to reduce the yield of the process, as well as increasing the cost.

A conventional manufacturing process for the active plate of an LCD is a five mask process. With reference to the bottom gate TFT LCD active plate shown in Figure 2, the process steps, each requiring a separate mask definition, are:

- (i) defining the gate 22 (which is part of the row conductor) over the substrate 21:

- (ii) defining the amorphous silicon island (which overlies a gate dielectric 23 that covers the entire structure), comprising a lower intrinsic layer 24 and an upper doped contact layer 26;

- (iii) defining the metallic source 28, drain 30 and column electrode 32:

- (iv) defining a contact hole 34 in a passivation layer 36 which covers the entire substrate; and

- (v) defining the transparent pixel electrode 38 which contacts the drain 30 through the hole 34.

PCT/IB02/00216

3

The capacitor shown in Figure 1 may simply be formed from the gate dielectric by providing an area of overlap of one pixel electrode with a portion of the row/gate conductor of the adjacent row.

There have been various proposals to reduce the number of lithography steps, and thereby the mask count, of the manufacture process in order to reduce cost and increase yield.

For example, it has been proposed to form the column conductors from the same transparent conductive oxide film as the pixel electrode, so that these components of the pixel structure can be deposited and patterned together. Additional measures can result in a two mask process, and this is explained with reference to the bottom gate TFT LCD active plate shown in Figure 3. The process steps, each requiring a separate mask definition, are:

- (i) defining the gate 22 (and row conductors); and

- (ii) defining the transparent column conductor 32 (which also forms the TFT source 28) and the pixel electrode 38 (which also forms the TFT drain 30).

The definition of the semiconductor island 24, 26 can be achieved by a self-aligned process using the gate 22, for example by using light exposure through the substrate. Of course, the semiconductor could equally be formed with a third mask step (between steps (i) and (ii) above). In the periphery of the array, the gate dielectric 23 is etched away using a low-precision stage, to allow contact to the gate lines at the periphery of the display.

In this structure, the high resistivity of the transparent conductive oxide thin film used for the column lines prevents the use of the structure in large (TV-sized) displays or in higher resolution displays, for example above VGA.

For this reason, there are further proposals to treat the column conductor area of the layer to increase the conductivity, whilst not affecting the transparency of the pixel electrode. One possibility would be to electroplate the top of the conducting lines with a metal but this technique has been found to have problems as, due to the resistive nature of the lines being plated, wide variations in the plating thickness over the length of the line tend to occur. Such thickness variations translate to variations in the LC cell gap which is

PCT/IB02/00216

4

highly undesirable. The article "Conductivity Enhancement of Transparent Electrode by Side-Wall Copper Electroplating", J. Liu et al, SID 93 Digest, page 554 discloses a method of enhancing the conductivity by electroplating a copper bus to the side of the metal oxide column line. The process involves an incomplete etching process to leave metal oxide residues, which act as seeds for the copper growth. The process is, though, both complicated and difficult to control. In addition, the copper bus will surround the source and drain electrodes, and there is a risk of shorts between the source and drain resulting from fast lateral copper growth when forming the bus. The copper bus around the source and drain electrodes also influences the channel length of the TFT and therefore makes the TFT characteristics unpredictable.

WO 99/59024 discloses a method for enhancing the conductivity of a transparent electrode by providing patterned metallic layers adjacent to the transparent electrodes.

There is still a need for a simple and reliable process for increasing the conductivity of thin film lines of transparent metal oxide layer, such as ITO, without increasing dramatically the complexity of the process. Such a process will find application in active matrix LCD manufacture, but will also be useful for other technologies where mask count reduction could be achieved if a transparent conductive layer could be made to be more conductive at least in certain regions without losing the transparency in others. This may be of benefit for polymer LEDs and large area image sensors.

According to a first aspect of the invention, there is provided a method

of improving the electrical conductivity of lines comprising transparent

conducting material carried on a substrate, comprising the step of forming the

lines of transparent conducting material on the substrate and providing on the

upper surface of each of the lines a covering layer extending from an end part

of the line and partially covering the upper surface of the line,

and the step of subjecting the lines to a metal electroplating process in which a plating potential is applied to each line at the end part whereby a

PCT/IB02/00216

F

metal layer is plated on the exposed surface area of the line, the covering layer serving to shield the underlying surface of the line during the plating.

With this method, the plating of the transparent conducting material 5 results in much improved electroconductivity of the lines. Importantly, and as a consequence of using the covering layer, the metal plating obtained tends to be smoother and more uniform in thickness along the length of the line compared with the kind of metal plating layer obtained when electroplating lines whose upper surface is completely exposed. This improvement is brought about by the effect of the covering layer in the plating process and results from an understanding of the nature of the electrical currents occurring during the plating and the consequences of such to the plating layer characteristics. The transparent conducting line is basically resistive and when disposed in a plating bath with the one end held at the cathode plating potential with respect to an anode potential of the bath can be considered equivalent to a series of distributed resistances by virtue of which the current flowing through the portion closest to that end tends to be greatest. As the metal deposition rate is proportional to the current flow then plating will be faster at this portion. This in turn results in the portion being made more conductive which accelerates plating, and hence exacerbates the nonuniformity of plating. Consequently, the thickness of the plated layer obtained along the line will be significantly greater towards that end than at regions away from that end. The provision of the covering layer means that, although conduction is still through the whole width of the line at the end region, now 25 only a partial area of the surface is subjected to plating while larger areas are involved away from that end. This means that the resistance of regions away from the end will tend to reduce, leading to enhanced plating. Although there will still be non-uniformity of the plating along the length of the line, the extent of this is considerably diminished.

The covering layer could comprise simply a strip of substantially constant width extending part way along the length of the line. Preferably, however, for better results the layer is shaped such that the uncovered area of

PCT/IB02/00216

6

the surface of the transparent conducting material of the line increases progressively away from the said end part along the line. The covering layer may be, for example, tapered. Alternatively, the shape of the layer may be such that its width decreases in steps along the line.

Preferably, the plating potential is applied also at an opposite end part of the line and the covering layer is arranged to extend along the line from this opposite end as well in similar manner, thus forming for example a symmetrical covering layer pattern.

The covering layer preferably comprises photoresist material.

Following the electroplating process, the covering insulating layer may be removed from the lines, and thereafter a further electroplating process may be carried out if desired.

The lines of transparent conducting material can conveniently be formed by depositing a layer of transparent conducting material over the substrate,

depositing a photoresist layer over the layer of transparent conducting material and patterning the photoresist into a configuration corresponding to the desired lines,

and patterning the transparent conducting layer using the photoresist to leave lines of transparent conducting material.

The covering insulating layers could then be provided separately by depositing a suitable layer but this would require a further patterning step to define this layer to the required shape.

In a particularly preferred embodiment, the photoresist layer used for defining the lines of transparent conducting material is used also to provide the covering layer over the lines. To this end, the layer of photoresist may be patterned into portions corresponding to the required lines with each portion including a selected region having a first thickness and corresponding in shape to that required for the covering layer, with the remainder of the portion being of reduced thickness. The defined portions of the photoresist layer are used to pattern the underlying layer of transparent conducting material, through an etching process, to leave the required lines. Thereafter, the portions of

PCT/IB02/00216

7

photoresist remaining on the lines are partially etched so as to remove a thickness corresponding to that of the reduced thickness areas. This results in photoresist being left at the aforementioned selected regions to constitute the covering layers and the rest of the surface of the line being exposed and ready for the electroplating operation to be performed. The patterning of the photoresist layer to achieve the desired different thickness pattern can be accomplished using a photolithographic patterning process of the kind described by C.W. Kim et al in the paper entitled "A Novel Four Mask - Count Process Architecture for TFT - LCDs", published in SID 00 Digest, pages 1006-1009. The technique described, which is directed to defining TFT channels, uses so-called slit, or grey-tone, photolithography which entails exposing the (positive) photoresist through a photolithographic mask that consists of solid (opaque) areas, transparent areas, and areas with grid or slit patterns. The solid and transparent areas serve to define regions intended to be left (at full thickness) and removed respectively while the areas comprising slit patterns result in partial exposure which upon development of the photoresist leads to the areas concerned being left but with a reduced thickness.

By utilising the photoresist material to form the covering insulating layer in this manner, the number of mask steps required is kept low.

The metallic, plated, layer preferably comprises copper or silver and the transparent conducting layer preferably comprises a conductive oxide, such as ITO (Indium Tin Oxide).

The method of increasing the conductivity of transparent conducting lines is particularly useful in the manufacture of pixellated devices such as liquid crystal displays (both active matrix and passive type), LED displays, PDP (Plasma Display Panel) displays and image sensors, in which the lines are used for addressing purposes. In such devices, transparent pixel electrodes associated with the lines can conveniently be formed from the same transparent conducting layer used for the lines and defined using the same photoresist layer by suitable patterning of that photoresist layer. Preferably, photoresist material remains on the pixel electrodes during the electroplating

10

PCT/IB02/00216

я

operation in order to shield the pixel electrodes. In the preferred embodiment described above in which the photoresist is patterned to different thicknesses, then full thickness photoresist may be defined over the pixel electrodes so that photoresist still remains over the electrodes following the partial etch step.

According to a second aspect of the invention, there is provided a method of forming an active plate for a pixellated device, comprising:

depositing and patterning a gate conductor layer over an insulating substrate;

depositing a gate insulator layer over the patterned gate conductor layer;

depositing a silicon layer over the gate insulator layer;

depositing a transparent conductor layer over the silicon layer;

depositing and patterning a photoresist layer over the transparent conductor layer having a configuration defining source and drain areas, pixel electrode areas and conductor line areas associated with the source or drain conductors:

patterning the transparent conductor layer using the photoresist to form source and drains, pixel electrodes and conductor lines;

defining the photoresist to leave a photoresist region on each conductor line extending from one end part of the line partially covering the surface of the line:

and selectively electroplating the exposed areas of the transparent conductor lines with a metallic layer with a plating potential being applied at the end part of each line.

The photoresist layer is preferably patterned into areas of different thickness at the conductor lines and the step of defining the photoresist comprises partially etching the photoresist to remove the thinner areas. This method can enable a two mask process to be used, wherein the gate conductor is deposited and patterned with a first lithographic process and the photoresist layer is deposited and patterned with a second lithographic process, the silicon layer being self aligned to the gate conductor.

15

PCT/IB02/00216

Ç

Embodiments of the invention will now be described in detail, by way of example, with reference to the accompanying drawings, in which:

Figure 1 shows the pixel components of an active plate;

Figure 2 shows a conventional active plate using bottom gate TFTs and manufactured using a five mask process;

Figure 3 shows a proposed active plate using bottom gate TFTs and manufactured using a two mask process;

Figure 4 shows the structure of a complete liquid crystal display;

Figures 5A to 5H show various stages in the manufacturing process for manufacturing the active plate of an LCD display using the invention;

Figures 6, 8 and 10 are plan views of a typical conductor line of the active plate at different fabrication stages;

Figures 7, 9 and 11 are sectional views along the lines VII - VII,  $\,$  IX and XI - XI in Figures 6, 8 and 10 respectively;

Figures 12A, B and C illustrate schematically in plan view alternative forms of conductor line formation:

Figure 13 is graph illustrating a relationship between an electroplated layer thickness and position along a conductor line using a known electroplating process;

Figure 14 is a graph illustrating a relationship between an electroplated layer thickness and position along a conductor line when using a method according to the invention;

Figure 15 is a plan schematic view of a further alternative form of conductor line formation; and

Figure 16 is a graph illustrating a relationship between an electroplated layer thickness and position along a conductor line using the conductor line formation of Figure 15

It should be noted that the figures are diagrammatic and not drawn to scale. Relative dimensions and proportions of parts of these figures have been shown exaggerated or reduced in size, for the sake of clarity and convenience in the drawings. The same reference numbers are used throughout the Figures to denote the same or similar parts.

PCT/IB02/00216

10

The application of the invention to a low mask count process for manufacturing the active plate of an active matrix liquid crystal display will now be described with reference to Figures 5A to 5H which illustrate the manufacturing process at various stages. The first steps of the process are common with known 2-mask processes.

Fig. 5A is a schematic diagram of the first stages of a low mask count process. The gate metal 45, for example comprising Cr, Al, Mo or combinations of such, has been deposited and defined over the insulating substrate 46 using a wet or dry etching technique, and a standard Back Channel Etch TFT stack deposition carried out. This provides a silicon nitride gate insulator layer 47, an amorphous silicon layer 48 and a doped (n+) silicon layer 49, which acts as a contact face, which are provided over the entire substrate surface. The area to the right of Figure 5A will be used to form the switching transistors (12 of Figure 1) associated with the display pixels whereas the left part of Figure 5A will form the row lead-in areas, where driving signals can be applied to the row conductors. Typically, the SiN gate insulator 47 is 400 nm thick, the intrinsic amorphous silicon 48 is 160 nm thick and the doped amorphous silicon is 40 nm thick, although other thickness layers can be used. The doped silicon layer 49 may be microcrystalline silicon to give good quality ITO to silicon contacts.

The TFT stack must be etched away from the row lead-in area. This only requires coarse alignment and no fine features to be etched. This masking step could be carried out by printing, laminating a plastic sheet on the array area before etching, or using coarsely aligned printed photoresist 50, as shown in Figure 5B. In Figure 5C, the TFT stack has been etched away from the row lead-in area, and a positive photoresist 51 is applied to the whole plate.

Rear illumination is then used to pattern the positive photoresist to have the same pattern as the gate line structure, as shown in Figure 5D. The remaining photoresist layer is used to pattern the two silicon layers to leave the transistor channel area 52 in Fig 5E and regions overlying the gate line (row conductor) structure elsewhere. A transparent conducting layer 53, for

PCT/IB02/00216

1.

example sputtered ITO, is then applied over the whole plate, as shown in Figure 5F.

The transparent conducting layer 53 is used, as will be described subsequently, to provide source and drain contacts for the TFTs, transparent pixel electrodes, and thin film column address lines. Referring again to Figure 3, this layer will thus form a TFT source contact 28 coupled to an associated column conductor line and a TFT drain contact 30 connected to a respective pixel electrode 38. An overlap between the pixel electrode and a gate conductor (row) line 45 can provide, together with the intervening gate dielectric, a storage capacitor (Figure 1) if required.

The steps illustrated in Figures 5A to 5F generally follow a known method.

In order to improve the electrical conductivity of the thin film column lines, these parts are selectively electroplated with a metal in a manner which will now be described.

Referring to Figure 5G, a positive photoresist layer 54 is deposited completely over the structure on the substrate 46. This layer 54 is patterned into a configuration to define the components to be formed from the layer 53, namely a configuration comprising areas 55 and 56 corresponding to the source and drain contact areas, areas 57 corresponding to the pixel electrodes, and areas 58 corresponding to a row lead-in pattern, as shown in Figure 5H, and also the column lines, not visable in Figure 5H, integrally coupled with the source contacts 55. Regions of the layer which are not covered by the patterned photoresist are then etched away, using a wet or dry etch process.

The photoresist layer 54 is patterned in a known, but unconventional, manner so as to leave photoresist in selected areas with different thicknesses. Examples of a suitable photolithographic patterning technique are described in the aforementioned paper by C.W. Kim et al and in the paper by C.W. Han et al entitled "A TFT manufactured by 4 masks process with new photolithography", published in SID Proceedings of the 18th International Display Research Conference, (Asia Display '98), pages 1109-1112, to which

PCT/IB02/00216

12

reference is invited and whose contents are incorporated herein as reference material. The patterning process entails exposing the photoresist layer 54, here a positive type photoresist, through a mask consisting of light-blocking areas, transparent areas and areas with predetermined grid or slit patterns. The light-blocking and transparent areas, as in conventional masks, serve to define respectively regions of the photoresist which are to remain and which are to be removed. The areas comprising a pattern of slits are used to define partially exposed regions, the parameters of the patterns required for this objective being described in the paper. This partial exposure, which relies upon diffraction effects produced by the slits, results in the regions of the photoresist concerned remaining after development of the photoresist but at a reduced thickness compared with the full thickness regions defined by the light - blocking areas of the mask. Essentially, therefore, the technique enables a photoresist layer to be selectively patterned into regions having different; and controlled, thickness as well as providing areas where the resist to totally removed. The areas 55, 56, 57 and 58 in Figure 5H are all defined by light blocking areas of the mask, and consequently comprise full-thickness photoresist regions. The column lines, on the other hand, are defined using in addition slit pattern areas in the mask so as to result in a particular structure of different thicknesses of photoresist.

Figure 6 shows schematically in plan view part of a typical one of the column lines 32 at this stage in the fabrication process and Figure 7 is a cross-sectional view along the line VII -VII of Figure 6. The column line 32, comprises an elongate strip of the transparent conducting layer 53, having substantially constant width and thickness along its entire length, and is defined by an area 70 of the photoresist layer 54 after patterning. This area 70 of the photoresist layer, indicated in Figure 6 by hatching, consists of a first region 72 formed by a light-blocking area of the mask used to pattern the layer 54 and a second region 74 of reduced thickness photoresist formed by a slit pattern area of the mask. The portion of the mask used to pattern the photoresist layer in this way is depicted schematically at 60 in Figure 7 with the

PCT/IB02/00216

13

light blocking, transparent and slit pattern areas represented by a solid line, crosses, and dashed lines respectively.

The shape of the first region 72 of the two-level resist pattern 70 is carefully controlled for reasons which will become apparent. As seen in Figure 6, the region 72 extends from one end part 75 of the line 32 towards the opposite end and partially covers the surface of the line. The region 32 is shaped such that the extent of the area of the surface of the line 32 covered by the region 72 decreases away from the end part 75, in this case with the region 72 being progressively tapered and symmetrical around a centre line of the line 32, and, conversely, such that the area of the surface of the line covered by the thinner photoresist region 74 progressively increases.

The photoresist pattern is then subjected to a partial etching operation in which a thickness of the resist pattern corresponding to the thickness of the thinner region 74 is completely removed, resulting in the structure shown in the plan and sectional views of Figures 8 and 9. The first region 72 of resist, now with reduced thickness, is still present on the line as shown at 72', while the rest of the surface of the line 32 is now exposed. As mentioned earlier, the regions 55, 56, 57 and 58 of the photoresist layer corresponding to the source and drain contacts, pixel electrodes and row lead-in pattern respectively (Figure 5H) are of full - thickness resist and consequently remain after this partial etching, although with reduced thickness.

The transparent conducting column lines 32 are then subjected to a selective electroplating process in which a layer of metal is plated on their exposed surfaces. Copper is preferably used for this purpose although other metals, such as silver, can be used instead. Before this selective plating, the exposed areas of the transparent conducting lines may be pre-treated, for example using a reductive process in acid or neutral electrolyte. For the electroplating, a required cathode plating potential is applied to the end part 75 of each line 32, the end of the line being kept free of photoresist for this purpose. The electroplating process results in a metal layer being formed on the exposed surface of the line, with the resist region 72' serving as a shield

PCT/IB02/00216

14

preventing plating of the immediately underlying surface area. This shown in Figures 10 and 11 where the metal plating is referenced at 80.

The presence of the protective resist region 72' on the lines 32 during this process ensures that a smoother and more even plating is obtained than would be the case otherwise. Due to the resistivity of the material (e.g. ITO) used for the lines 32 and the resulting inhomogeneous distribution of current, then non-uniformities tend to occur in the plating layer with the rate of plating, and hence the plating thickness, being much greater towards the end of the line where the plating voltage is applied. Typically, there may be a factor of ten or more difference in the plating thickness close to and remote from that point for an uncovered line when electroplated.

The rate of metal deposition is proportional to the electrical current flow. The line 32 can be considered equivalent to a series of distributed resistances connected at one end to the cathode potential and at a number of spaced locations along the length of the line to the plating anode via a resistance constituted by the resistance of the electrolyte. Then, unless the resistance of the line 32 at a region close to the cathode is much less than the resistance of the electrolyte the current flow in the line at this region will be much greater than that further away from the cathode. In the case, therefore, of an uncovered line being electroplated, this larger current in the line at the region towards the cathode will result in a thicker plating deposition. As the plating metal is more conductive than the line 32 then the resistance of this end region rapidly decreases which leads to a still further increase in deposition, thus aggravating the problem and causing even greater non-uniformity in the thickness of the plating layer along the length of the line 32.

The presence of the covering layer 72' serves to control this kind of effect by, to an extent, affecting the distribution of currents with the result that the extent of non-uniformity in the plating layer thickness is considerably reduced. Initially, the structure presents a kind of distributed resistance pattern similar to that described, with electrical conduction being through the whole width of the line 32 at the region partially covered by the layer 72'. Now, however, only partial plating of the area of line 32 at the beginning of the line.

10

PCT/IB02/00216

15

occurs, corresponding to the reduced area which is exposed, while the larger surface areas begin to plate further along the line. Through this, the effective resistance of the areas of the line further away from the end tend to reduce compared with the end region. This leads to an improved plating thickness characteristic along the line. There will still be some non-uniformity in thickness, but much less than that obtained when plating an uncovered line. The end region of the line will tend to have the largest degree of non-uniformity but this can be avoided by the use of an appropriate mechanical masking shield positioned to overlie the end part during the plating process.

The shape of the protective resist region 72' on the line, and thus the exposed area of the line, is selected with this in mind.

Rather than the plating voltage being applied to just one end of the line, and the resist region 72' as shown in Figures 8 and 10 simply decreasing in area gradually from that one end, it can instead be applied to both ends of the line 32. In this case, the shape of the resist region 72' is changed accordingly so as to be substantially symmetrical around a line through the middle of the line 32, as shown schematically in Figure 12A. Possible alternative forms for the resist covering layer are illustrated also in Figure 12B, in which the extent of the covering layer along the length of the line 32 is increased, and in Figure 12C in which the width of the covering layer is stepped rather than being smoothly tapered.

Although particular forms for the covering layer have been depicted, it will be understood that the shape and dimensions of the layer can be varied and will be dependent on, and to an extent determined by, for example the properties of the line 32 and the plating process parameters. These factors will be taken into account in selecting the form of the covering layer required to achieve the desired results. Generally, speaking, the covering layer is likely to extend over a significant proportion of the length of the line in order to obtain the best results.

Figure 13 is a graph showing the relationship between the thickness, T, in micrometres of a copper plating layer and the position, L, along the length of the line which can be expected when formed by electroplating on the surface

PCT/IB02/00216

16

of a plain ITO line without any covering resist in the case where the plating voltage is applied to both ends of the line during the plating process. The different curves shown in the graph are the results for different plating times, ranging from around 50 seconds for the thinnest to around 200 seconds for the thickest. The ITO line is 50 cms long and has a constant width of 20μm. As regards the key plating parameters used in this example, the bath conductivity is selected to be approximately 40 Ω° m<sup>-1</sup>, the currently density (J) is selected to be approximately 1 A/dm² ( = 100 A/m²), and the anode - cathode (line 32) distance is approximately 50cm. As is apparent, the thickness of the copper plating obtained can be as much as ten times greater or more towards the ends than at the middle (25cm) of the ITO line.

For comparison, the graph shown in Figure 14 illustrates similarly the relationship between the thickness T, in nanometres, of the Cu plating layer and position, L, along a similarly dimensioned ITO line which can be expected when the line has a protective resist region 72' on its surface of the form depicted in Figure 12A. The plating parameters remain the same as before. The curve shown in this graph corresponds to a plating time of approximately 800 seconds. The opposite end parts of the line 32 have here been deliberately mechanically shielded during the plating process to avoid the significantly increased plating thickness which would otherwise occur at the very ends. As is evident, the variation in plating thickness along the length of the line is considerably less pronounced.

From the results illustrated in Figures 13 and 14, it will be appreciated that at comparable average thicknesses, the variation in thickness along the length of the line 32 in the Figure 14 case is only around a factor of three or so while in the Figure 13 case this variation is up to around a factor of ten.

The thickness of the plating layer obtained desirably is at about 100nm at the thinnest part, i.e. around the middle of the line, and preferably between 100nm and 500nm.

Improved results in the plating layer characteristics are possible even when using a much simplified shape of resist region 72'. Figure 15 shows an ITO line 32, again of 50cms length and 20µm width, having simply rectangular

10

PCT/IB02/00216

17

resist regions 72' provided at its opposing ends (using the same process as previously described). Each of the two regions has a width (w) of 18 $\mu$ m and a length, I, of 10 cm and is arranged centrally of the ITO line such that 1 $\mu$ m width strips, x, of exposed ITO are present at either side. The graph of Figure 16 illustrates the kind of plating thickness characteristic which can be expected to be obtained when plating such a line using the same electroplating parameters as before.

Referring now again to Figure 10, then after the plating layer 80 has been formed, the remainder of the photoresist pattern, i.e the region 72', is removed.

At the end of the fabrication process, the ITO column lines have a layer of copper on their surface which provides the higher conductivity required for addressing large, high resolution displays.

When the enhanced conductivity columns are used with a low mask count technology, as shown in the embodiment above, then the amorphous silicon lying above the rows lines may introduce parasitic TFTs that could affect the driving of the display. The effect of these can be accommodated in the driving scheme, and they can be minimised by careful design.

Figure 4 shows the structure of a complete liquid crystal display. A layer of liquid crystal material 81 is provided over the active plate 82, which comprises the structure described above. A further substrate 83 overlies the layer of liquid crystal material. This further substrate 83 may be provided on one face with an arrangement of colour filters 84 and a plate defining the common electrode 18 layer (shown in Figure 1). Polarizing films 86 are also provided on the opposite sides of the substrates.

As this embodiment of the invention is concerned principally with the transistor substrate and its fabrication, the operation and construction of the liquid crystal display will not be described in any further detail. Such aspects will be apparent to those skilled in the art.

The specific examples described provide Cu plating on ITO transparent column lines. Other conductive oxide transparent materials may be used, and

PCT/IB02/00216

18

other metals may be plated. These possibilities fall within the scope of the invention.

While portions of resist are conveniently formed in the above described manner and utilised for the protective regions 72' on the lines, it is envisaged that such regions could instead be formed otherwise, for example by depositing and patterning another suitable material, although this would add a further masking stage to the fabrication process.

Additional layers to those described may be provided, and there are various alternatives which will be apparent to those skilled in the art. The specific processing parameters and materials have not been described in detail in this application, as this invention relies upon known individual processing steps and materials. The steps, and the range of possible alternatives, will be apparent to those skilled in the art.

The specific example above uses amorphous silicon TFTs in the active plate of the LCD, but other semiconductor arrangements are possible, such as polycrystalline or microcrystalline.

In the specific example described, bottom gate transistors are used, but top gate transistors may also be used. In fact, the invention can be applied to any pixellated device in which a transparent pixel electrode is required and where there may be benefit in combining the deposition of the layer defining the pixel electrode with line (row or column) conductors.

The invention has been described in detail when applied to an active matrix LCD. The invention can also be applied for example to passive type LCDs, active matrix LED displays and to image sensors. The invention may be applied to any pixellated device requiring transparent pixel electrodes, where they may be benefit in defining row or column address lines using the same layer as for the pixel electrodes of the device. The invention can also be applied to transmissive and reflective active matrix LCD displays. In the case of reflective displays, it may still be desirable to use a transparent layer as ITO has well known benefits for forming the source and drain contacts.

In the examples described above, a transmissive display is shown, and the pixel electrode is shielded from the plating operation. For a reflective

PCT/IB02/00216

19

display, the pixel electrode may be plated together with the column conductors. In this case, the lines 32 and pixel electrodes may again be electroplated with metal in a second electroplating process after the photoresist regions 72' have been removed which builds upon the previously formed plating and also covers the newly-exposed surface areas of the line 32.

From reading the present disclosure, other modifications will be apparent to persons skilled in the art. Such modifications may involve other features which are already known in the field of active matrix liquid crystal displays and the like and which may be used instead of or in addition to features already described herein.

PCT/IB02/00216

20

## CLAIMS

- A method of improving electrical conductivity of lines comprising transparent conducting material carried on a substrate, comprising the step of forming the lines of transparent conducting material on the substrate and providing on the upper surface of each of the lines a covering layer extending from an end part of the line and partially covering the upper surface of the line, and the step of subjecting the lines to a metal electroplating process in which a plating potential is applied to each line at the end part whereby a metal layer is plated on the exposed surface area of the line, the covering layer serving to shield the underlying surface of the line during the plating.

- A method according to Claim 1, wherein the covering layer is shaped such that the exposed surface of the line increases progressively away

from the end part.

- 3. A method according to Claim 2, wherein the covering layer tapers in width away from the end part.

- A method according to Claim 2, wherein the covering layer is stepped in width along the line.

- A method according to any one of Claims 1 to 4, wherein the covering layer extends from both ends of the line in similar manner and the

plating potential is applied at both ends of the line during the plating process.

- 6. A method according to any one of Claims 1 to 5, wherein the covering layer comprises photoresist.

- 7. A method according to any one of Claims 1 to 6, wherein the step of forming the lines comprises:

depositing a layer of transparent conducting material over the substrate,

25

PCT/IB02/00216

21

depositing a photoresist layer over the layer of transparent conducting material and patterning the photoresist into a configuration corresponding to the desired lines,

patterning the transparent conducting layer using the photoresist to leave the lines of transparent conducting material.

- A method according to Claim 7, wherein the photoresist layer is patterned into portions corresponding to the desired lines with each portion including a selected region having a first thickness and conforming with the form of the required covering layer with the remainder of the portion being of reduced thickness, and after patterning the transparent conducting layer the photoresist is partially etched to remove the areas of reduced thickness while leaving photoresist at the selected region which photoresist constitutes the covering layer.

- A method according to Claim 7 or Claim 8, and for use in the manufacture of a pixellated device comprising pixel electrodes of transparent conducting material carried together with the conductive lines on the substrate, wherein the photoresist layer is patterned into a configuration corresponding also to the desired pixel electrodes, and wherein the transparent conducting layer is patterned using the photoresist to leave pixel electrode regions.

- 10. A method according to Claim 9, wherein photoresist is left over the pixel electrode regions during the electroplating process.

- 11. A method of forming an active plate for a pixellated device, comprising:

depositing and patterning a gate conductor layer over an insulating substrate;

depositing a gate insulator layer over the patterned gate conductor layer;

depositing a silicon layer over the gate insulator layer;

10

PCT/IB02/00216

22

depositing a transparent conductor layer over the silicon layer;

depositing and patterning a photoresist layer over the transparent conductor layer having a configuration defining source and drain areas, pixel electrode areas and conductor line areas associated with the source or drain conductors;

patterning the transparent conductor layer using the photoresist to form source and drains, pixel electrodes and conductor lines;

defining the photoresist to leave a photoresist region on each conductor line extending from one end part of the line partially covering the surface of the line:

and selectively electroplating the exposed areas of the transparent conductor lines with a metallic layer with a plating potential being applied at the end part of each line.

- 12. A method according to Claim 11, wherein the photoresist layer is patterned into areas of different thicknesses at the conductor lines and wherein the step of defining the photoresist comprises partially etching the photoresist to remove the thinner areas.

- 13. A method according to Claim 11 or Claim 12, wherein the photoresist is defined to leave on each line a similar photoresist region extending from the other end part and wherein the plating potential is applied also at that other end part.

- 14. An active matrix liquid crystal display device comprising an active plate made according to any one of Claims 11 to 14, a further substrate carrying an electrode structure spaced from the active plate, and liquid crystal disposed between the active plate and the further substrate.

PCT/IB02/00216

PCT/IB02/00216

Fig.3

PCT/IB02/00216

PCT/IB02/00216

PCT/IB02/00216

Fig.6

Fig.7

Fig.9

PCT/IB02/00216

Fig.12B

Fig.12C

PCT/IB02/00216

PCT/IB02/00216

Fig.15

Fig.16

#### 【国際公開パンフレット(コレクトバージョン)】

#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

## (19) World Intellectual Property Organization International Bureau

##

## (43) International Publication Date 15 August 2002 (15.08.2002)

PCT

# WO 02/063386 A3

- (51) International Patent Classification<sup>7</sup>: G02F 1/1345, 1/1362, IJO1L 31/18, 51/20

- (21) International Application Number: PCT/IB02/00216

- (22) International Filing Date: 25 January 2002 (25.01.2002)

- (25) Filing Language:

- (26) Publication Language: English

- (30) Priority Data: 0102756.4 3 February 2001 (03.02.2001) GB

- (71) Applicant: KONINKLIJKE PHILIPS ELECTRON-ICS N.V. [NL/NL]; Groenewoudseweg 1, NL-5621 BA Ländhoven (NL). ewoudseweg 1, NL-5621 BA

- (72) Inventors: FRENCH, Ian, D.; Prof. Holstlaan 6, NL-5656 AA Eindhoven (NL). VAN DER ZAAG, Pieter, J.; Prof. Holstlaan 6, NL-5656 AA Hindhoven (NL). DE KUBBER, Daan, L.; Prof. Holstlaan 6, NL-5656 AA Eindhoven (NL).

- (74) Agent: WILLIAMSON, Paul, L.; Internationaal Octrooibureau B.V., Prof. Holstlaan 6, NL-5656 AA trooibureau B.V., Prof. Eindhoven (NL).

- (81) Designated States (national): JP, KR.

- (84) Designated States (regional): European patent (AI, BE, CII, CY, DE, DK, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PI, SE, TR).

#### Published:

- with international search report before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments

- (88) Date of publication of the international search report: 10 October 2002

For two-letter codes and other abbreviations, refer to the "Guid-ance Notes on Codes and Abbreviations" appearing at the begin-ning of each regular issue of the PCT Gazette.

(54) Title: METIIOD OF IMPROVING THE CONDUCTIVITY OF TRANSPARENT CONDUCTOR LINES

98 (57) Abstract: A method of improving the electrical conductivity of transparent conducting lines (32) carried on a substrate (46), particularly address lines on the active plate for a pixellated device such as an active matrix liquid crystal display or the like fabricated using a low mask count process, involves forming the lines on the substrate from a deposited layer of transparent conducting material (53), e.g., ITO, and provided on their upper surface with a covering layer (72') extending from at least one end (75) and partially covering the surface, and then performing on electroplating operation to plate the lines (80) with a plating tentinal being applied or that end. The covering layer (72') assists in achieving a more uniform plated layer (80) along the length of the line. The covering layer preferably comprises photoresist defined by selective patterning and partial etching of a deposited photoresist layer (54) used for patterning the transparent layer (53). In a pixellated device, pixel electrodes (38) are also defined from the transparent layer.

A3

## 【国際調査報告】

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | INTERNATIONAL SEARCH RE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | nal Application No<br>B 02/00216 |  |  |