# (19) 国家知识产权局

# (12) 发明专利

(10) 授权公告号 CN 112084730 B (45) 授权公告日 2024. 04. 05

(21)申请号 202010950156.1

(22)申请日 2020.09.11

(65) 同一申请的已公布的文献号 申请公布号 CN 112084730 A

(43) 申请公布日 2020.12.15

(73) 专利权人 昇显微电子(苏州)股份有限公司 地址 215000 江苏省苏州市苏州市高新区 竹园路209号4号楼1905室

(72) 发明人 洪郁文 秦良

(74) 专利代理机构 苏州久元知识产权代理事务 所(普通合伙) 32446

专利代理师 袁欣琪

(51) Int.CI.

*G06F 30/327* (2020.01) *G06F 30/3312* (2020.01)

#### (56) 对比文件

CN 101373424 A, 2009.02.25

CN 101681249 A, 2010.03.24

CN 110888622 A,2020.03.17

CN 205375448 U.2016.07.06

JP 2006005954 A,2006.01.05

US 4672307 A,1987.06.09

US 7518535 B1,2009.04.14

刘海涛;王志功;孟桥;唐凯.高速模数转换器中格雷码与二进制编码对比.东南大学学报(自然科学版).2010,(第03期),全文.

审查员 王轩

权利要求书1页 说明书4页 附图3页

#### (54) 发明名称

一种改善Asynchronous FIF0支持非2的幂次深度方法

#### (57) 摘要

本发明公开了一种改善Asynchronous FIFO 支持非2的幂次深度算法,包括计算位移数据,新增写满二进制及格雷码逻辑电路和读空二进制及格雷码逻辑电路,写满判断和 读空判断都使用新增的逻辑电路,写满判断和 读空判断都使用新增的逻辑电路,其优点在于在写满的二进制逻辑要先在转换成格雷码逻辑前加上位移数据,因此要先了解当前电路所需求的资料最大笔数是多少,推导出数值后,加到写满的二进制逻辑再转换成格雷码逻辑,来满足格雷码条件以及写满的逻辑判断,使用资料笔数存取弹性和节省面积资源都大幅改善。

- 1. 一种改善Asynchronous FIF0支持非2的幂次深度方法,包括以下步骤:

- S1. 先计算出位移数据;

- S2. 新增写满和读空的二进制逻辑电路和格雷码逻辑电路;

- S3. 写满判断,使用新增写满的二进制逻辑电路产生的写满格雷码判断以及新增读空的二进制逻辑电路产生的读空格雷码判断,再经由两次非同步时钟的寄存器同步来判断出写满条件;

- S4. 读空判断,利用新增的写满二进制逻辑电路以及新增读空的二进制逻辑电路进行读空判断;

所述步骤S1中的位移数据是指利用设置参数ADDR\_WIDTH以及DEPTH来推导出非2的幂次深度资料笔数比2的幂次深度资料笔数少多少深度的值,其中ADDR\_WIDTH为地址位宽n,DEPTH为非2的幂次深度, $2^{n-1}$ <DEPTH< $2^n$ ,该推导过程为, $2^{ADDR_WIDTH}$ -DEPTH,算出的值即为所述位移数据;

所述步骤S2中原始的逻辑电路循环条件是计数到最大资料笔数深度就循环,只用来判断写指针与读指针;

所述步骤S2中新增的写满和读空的二进制逻辑电路的循环条件是计数到最大资料笔数深度的2倍再循环:

所述步骤S3还包括,在新增写满条件的二进制逻辑电路在转格雷码逻辑电路之前,加上所述位移数据;

将加上所述位移数据后转换成的格雷码数值和新增读空条件二进制转换成的格雷码数值同步到写的时钟域,然后比较最大位元及次大位元比特数值不同,其余比特数相同,则写满条件成立;

在所述循环条件下,将新增的写条件二进制逻辑转成格雷码再经由两次的非同步时钟的寄存器同步,再与新增读条件二进制逻辑转成格雷码来比较判断是否是相同位址,如果相同,则读空判断成立。

# 一种改善Asynchronous FIF0支持非2的幂次深度方法

## 技术领域

[0001] 本发明提出了Asynchronous FIFO(不同时钟域的资料寄存器)除了2的幂次深度外,在任意深度并且符合格雷码特性下,可以支持FULL(写满)和EMPTY(读空)的方法,该技术属于数字电路设计领域。

## 背景技术

[0002] 目前,常用的Asynchronous FIF0(不同时钟域的资料寄存器)技术基本上都是以2的幂次深度为基础,也就是资料量只能限制存2笔数据、4笔数据、8笔数据、16笔数等。

[0003] 传统的技术缺点是只支持2的幂次深度的资料寄存器,资料量被限制只能存2笔数据、4笔数据、8笔数据、16笔数等,当深度不是2的幂次笔数,FULL(写满)和EMPTY(读空)判断受限于格雷码特性将无法判断,也就是不同时钟域的资料寄存器因技术限制无法存5-7笔数据或是9-15笔数,各家公司电路模块皆有使用此不同时钟域的资料寄存器,如果存取资料笔数不到2的幂次资料笔数,还是会使用2的幂次最大深度的资料寄存器来存取,这样就会浪费多余的深度寄存器面积。

# 发明内容

[0004] 本发明的目的在于提供一种可以使用不是2的幂次深度的资料笔数来存取资料的方法,并且还要保留格雷码特性,只要改动设置参数,任何的要存取资料笔数都可以支援,使FULL(写满)和EMPTY(读空)逻辑判断依然可实行,以解决上述背景技术中提出的问题。

[0005] 为实现上述目的,本发明提供如下技术方案:

[0006] 一种改善Asynchronous FIF0支持非2的幂次深度方法,包括以下步骤:

[0007] S1. 先计算出位移数据;

[0008] S2. 新增写满和读空的二进制逻辑电路和格雷码逻辑电路;

[0009] S3. 写满判断,使用新增写满的二进制逻辑电路产生的写满格雷码判断以及新增读空的二进制逻辑电路产生的读空格雷码判断,再经由两次非同步时钟的寄存器同步来判断出写满条件;

[0010] S4. 读空判断,利用新增的写满二进制逻辑电路以及新增读空的二进制逻辑电路 进行读空判断。

[0011] 进一步地,所述步骤S1中的位移数据是指利用设置参数ADDR\_WIDTH以及DEPTH来推导出非2的幂次深度资料笔数比2的幂次深度资料笔数少多少深度的值,其中ADDR\_WIDTH为地址位宽n,DEPTH为非2的幂次深度, $2^{n-1}$ DEPTH  $2^n$ ,该推导过程为, $2^{ADDR_wIDTH}$ -DEPTH,算出的值即为所述位移数据。

[0012] 进一步地,所述步骤S2中原始的逻辑电路循环条件是计数到最大资料笔数深度就循环,只用来判断写指针与读指针。

[0013] 进一步地,所述步骤S2中新增的写满和读空的二进制逻辑电路的循环条件是计数到最大资料笔数深度的2倍再循环。

[0014] 进一步地,所述步骤S3还包括,在新增写满条件的二进制逻辑电路在转格雷码逻辑电路之前,加上所述位移数据。

[0015] 进一步地,将加上所述位移数据后转换成的格雷码数值和新增读空条件二进制转换成的格雷码数值同步到写的时钟域,然后比较最大位元及次大位元比特数值不同,其余比特数相同,则写满条件成立。

[0016] 进一步地,在所述循环条件下,将新增的写条件二进制逻辑转成格雷码再经由两次的非同步时钟的寄存器同步,再与新增读条件二进制逻辑转成格雷码来比较判断是否是相同位址,如果相同,则读空判断成立。

[0017] 还提供了一种基于权利要求1-6所述的任一改善Asynchronous FIF0支持非2的幂次深度方法的逻辑电路,其特征在于,包括:

[0018] 新增的写满和读空的逻辑电路模块;

[0019] 在新增的写条件逻辑电路从二进制转换成格雷码并且做两次同步到读的时钟域;

[0020] 在新增的读条件逻辑电路从二进制转换成格雷码并且做两次同步到写的时钟域。

[0021] 与现有技术相比,本发明的有益效果是:

[0022] 本发明可以使得Asynchronous FIF0 (不同时钟域的资料寄存器) 可以支持2的幂次深度以及非2的幂次深度 (意指任意资料笔数都支持),资料数据不用被限制一定只能存2 笔数据、4笔数据、8笔数据、16笔数等,而可以存5笔数据,9笔数据,10笔数据之类的任意笔数,使得电路设计需求更有弹性。

[0023] 其次,将写指针/读指针和这次新增判断FULL(写满)/EMPTY(读空)的二进制和格雷码逻辑电路分开独立处理,写指针或读指针的计数条件是使用最大资料深度做循环,不相同的地方是本发明计数满循环的限制条件不同,因此才可以让写满的判断继续符合格雷码的特性。本发明最重要的一点就是在写满的二进制逻辑要先在转换成格雷码逻辑前加上位移数据,因此要先了解当前电路所需求的资料最大笔数是多少,利用本发明推导算出数值后,加到写满的二进制逻辑再转换成格雷码逻辑,来满足格雷码条件以及写满的逻辑判断。

[0024] 另外,改良后的设计在相同地址位宽和深度状况下,与原本的电路设计相比,只多了一点点电路改良面积,但是可以省下不少面积资源,经过综合的数据显示,此资料寄存器在少一个深度的状况可以省下将近10%面积,甚至在地址位宽为4和深度为16的情况下,可以支持深度10的资料笔数,少了这6个深度,面积少了将近35%,对于电路使用需求越多的资料寄存器,使用资料笔数存取弹性和节省面积资源都大幅改善。

### 附图说明

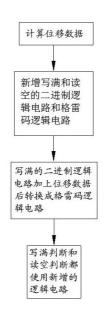

[0025] 图1为本发明方法示意图;

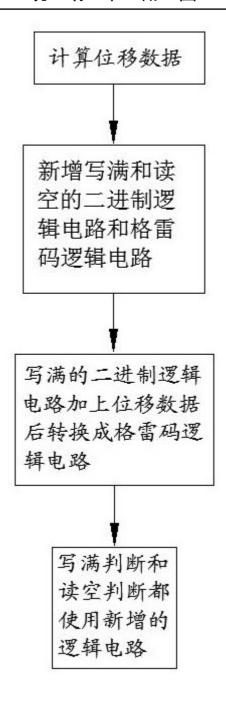

[0026] 图2为本发明实施例1的格雷码特性示意图;

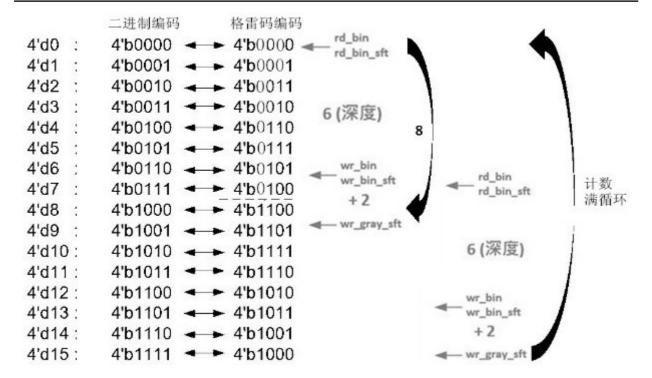

[0027] 图3为本发明实施例1的加入位移数据示意图。

#### 具体实施方式

[0028] 下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于

本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

[0029] 请参阅图1-3,参见图1本发明提供一种改善Asynchronous FIF0支持非2的幂次深度方法。

[0030] 如图2所示,新增写满和读空的二进制逻辑电路和格雷码逻辑电路,此两电路负责处理新的写满的二进制、写满的格雷码逻辑电路以及新的读空的二进制、读空的格雷码逻辑电路,这两个新增的写满和读空的逻辑电路也都会被使用来改善判断写满条件和读空条件,不再使用原始的逻辑电路判断。而原始这部份的逻辑电路计数到最大资料深度就循环,本发明只用来判断写指针与读指针,也就是指针的判断与写满读空的逻辑关系完全是独立分开,这样可以让写指针和读指针的可读性依然直觉简单,写满和读空判断条件也会正确不会被影响。

[0031] 假设最大资料笔数要存取8笔,写指针与读指针的计数是0-7再循环到0,循环最大值是最大的资料笔数深度8。新增的条件为了满足写满及读空判断,计数是0-15再循环到0,循环最大值是在最大资料笔数深度8乘2,由,1可看出格雷码特性(任两数值比特数,包含计数到最大值后循环归零都只会调动1比特数值)有上下镜射特性。

[0032] 如图3所示,在写满条件的二进制逻辑在转格雷码逻辑电路之前,一定要加上位移数据,因写满的判断式会使用新增写满的逻辑电路产生的写满格雷码判断以及新增读空的逻辑电路产生的读空格雷码判断再经由两次的非同步时钟的寄存器同步来判断,这个加上位移数据只在新增写满条件的步骤用意是使新增写满条件逻辑电路的格雷码与新增读空条件的格雷码这两个判断式要保持原来最大深度资料笔数的特性判断写满逻辑,保持这样的特性就可以继续满足格雷码镜射特性,然后比较最大位元及次大位元比特数值不同,其余比特数相同的逻辑判断就可以判断出写满条件,图2中假设地址位宽是3,资料深度是最大的8为例子,即使要存取的资料量最大限制只有6笔资料,而不是8笔资料,利用新增的逻辑电路可以看到将写条件二进制加上8-6=2的位移数据后再转换成格雷码数据,这样的目的就是与读条件的判断始终继据维持著最大资料深度8的镜射特性范围,即使计数满归零都还是符合格雷码的特性。

[0033] 为了判断读空条件正确,即使深度改变,循环条件依然要保持格雷码特性,读空条件是写条件的格雷码位址和读条件的格雷码位址位元数都要相同,代表着读到的资料存取位址与写到的资料存取位址相同,资料寄存器内部已经没有资料,读空判断成立,因此将新增的写条件二进制逻辑(在2的幂次乘2做计数满循环)不需要加上位移数据直接转成格雷码再经由两次的非同步时钟的寄存器同步,再与新增读条件二进制逻辑(在2的幂次乘2做计数满循环)不需要加上位移数据直接转成格雷码来比较判断是否是相同位址,这部份做的判断比较改善了新的读空条件。

[0034] 需要说明的是,在本文中,诸如第一和第二等之类的关系术语仅仅用来将一个实体或者操作与另一个实体或操作区分开来,而不一定要求或者暗示这些实体或操作之间存在任何这种实际的关系或者顺序。而且,术语"包括"、"包含"或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者设备所固有的要素。

[0035] 尽管已经示出和描述了本发明的实施例,对于本领域的普通技术人员而言,可以理解在不脱离本发明的原理和精神的情况下可以对这些实施例进行多种变化、修改、替换和变型,本发明的范围由所附权利要求及其等同物限定。

图1

|       |   | 二进制编码   |              | 格雷码编码    |

|-------|---|---------|--------------|----------|

| 4'd0  | : | 4'b0000 | <b></b>      | 4'b0000  |

| 4'd1  | : | 4'b0001 | <b>*</b>     | 4'b0001  |

| 4'd2  | : | 4'b0010 | <b>←</b> ►   | 4'b0011  |

| 4'd3  | : | 4'b0011 | $\leftarrow$ | 4'b0010  |

| 4'd4  | : | 4'b0100 | <b>←</b>     | 4'b0110  |

| 4'd5  | : | 4'b0101 | <b>←</b>     | 4'b0111  |

| 4'd6  | : | 4'b0110 | <b>←</b> ►   | 4'b0101  |

| 4'd7  | : | 4'b0111 | <b>←</b>     | 4'b 0100 |

| 4'd8  | : | 4'b1000 | <b>←</b>     | 4'b1100  |

| 4'd9  | : | 4'b1001 | <b>*</b>     | 4'b1101  |

| 4'd10 | : | 4'b1010 | <b>←</b>     | 4'b1111  |

| 4'd11 | : | 4'b1011 | <b>←</b>     | 4'b1110  |

| 4'd12 | : | 4'b1100 | <b>←</b>     | 4'b1010  |

| 4'd13 | : | 4'b1101 | <b>←</b>     | 4'b1011  |

| 4'd14 | : | 4'b1110 | <b>←→</b>    | 4'b1001  |

| 4'd15 | : | 4'b1111 | <b>*</b>     | 4'b1000  |

|       |   |         |              |          |

图2

图3