# (19) 中华人民共和国国家知识产权局

# (12) 发明专利

(10) 授权公告号 CN 107346770 B (45) 授权公告日 2020. 11. 24

(21)申请号 201610356955.X

(22)申请日 2016.05.26

(65) 同一申请的已公布的文献号 申请公布号 CN 107346770 A

(43) 申请公布日 2017.11.14

(30) 优先权数据 105113803 2016.05.04 TW

(73) **专利权人** 联华电子股份有限公司 **地址** 中国台湾新竹市新竹科学工业园区

(72) 发明人 叶书玮 吴宗训 苏智洺 郭有策

(74) **专利代理机构** 北京市柳沈律师事务所 11105

代理人 陈小雯

(51) Int.CI.

*H01L* 27/11 (2006.01)

(56) 对比文件

US 2011026308 A1,2011.02.03

CN 104022116 A,2014.09.03

CN 102298963 A, 2011.12.28

CN 103915112 A,2014.07.09

CN 101840921 A,2010.09.22

CN 104752353 A,2015.07.01

US 6445002 B1,2002.09.03

审查员 董蕴萱

权利要求书2页 说明书9页 附图7页

#### (54) 发明名称

静态随机存取存储器的布局图案

#### (57) 摘要

本发明公开一种静态随机存取存储器的布局图案,至少包含一第一上拉晶体管、一第二上拉晶体管、一第二下拉晶体管、一第一存取晶体管以及一第二存取晶体管位于一基底上,多个鳍状结构位于基底上,至少包含有一至少一第一鳍状结构与至少一第二鳍状结构,至少一J状栅极结构,该至少一J状栅极结构包含有一长边部分、一短边部分以及一连接该长边部分与该短边部分的桥接部分,以及至少一第一延伸接触结构,横跨于该至少一第一鳍状结构与该至少一第二鳍状结构与该至少一第二

1.一种静态随机存取存储器的布局图案,至少包含:

第一上拉晶体管 (PL1)、第二上拉晶体管 (PL2)、第一下拉晶体管 (PD1)、第二下拉晶体管 (PD2)、第一存取晶体管 (PG1)以及第二存取晶体管 (PG2)位于一基底上;

多个鳍状结构位于该基底上,该些鳍状结构至少包含有至少一第一鳍状结构、至少一 第二鳍状结构、至少一第三鳍状结构以及至少一第四鳍状结构;

J状栅极结构,该J状栅极结构包含有一长边部分、一短边部分,以及一连接该长边部分与该短边部分的桥接部分,其中该第一下拉晶体管 (PD1) 至少包含该J状栅极结构以及该至少一第一鳍状结构、该至少一第二鳍状结构和该至少一第四鳍状结构,其中该长边部分横跨于该至少一第一鳍状结构、该至少一第二鳍状结构、该至少一第三鳍状结构以及该至少一第四鳍状结构,而该短边部分则跨越该至少一第一鳍状结构;

第一存取栅极结构,位于该基底上,其中该第一存取栅极结构与该J状栅极结构的该短边部分排列方向相同,且该第一存取栅极结构与该J状栅极结构的该短边部分具有相同的一对称轴,该第一存取栅极结构横跨该至少一第四鳍状结构;以及

第一延伸接触结构(N1),横跨于该至少一第一鳍状结构、该至少一第二鳍状结构、该至少一第三鳍状结构以及该至少一第四鳍状结构,其中该第一延伸接触结构与该桥接部分不重叠。

- 2. 如权利要求1所述的布局图案,其中该J状栅极结构的该短边部分,位于该桥接部分以及该第一存取栅极结构之间。

- 3. 如权利要求1所述的布局图案,其中该J状栅极结构的该长边部分横跨于该至少一第三鳍状结构上,组成该第一上拉晶体管 (PL1) 的一栅极。

- 4.如权利要求3所述的布局图案,其中还包含一电压源Vcc,与该至少一第三鳍状结构 电连接。

- 5. 如权利要求1所述的布局图案,其中该第一延伸接触结构为连续结构。

- 6.如权利要求1所述的布局图案,其中还包含至少一字符线,与该第一存取栅极结构电 连接。

- 7.如权利要求1所述的布局图案,其中该第一存取栅极结构与该J状栅极结构不互相接触。

- 8.如权利要求1所述的布局图案,其中该J状栅极结构的该长边部分与该短边部分沿着一第一方向排列,该桥接部分沿着一第二方向排列。

- 9.如权利要求1所述的布局图案,其中还包含至少一位线,与该至少一第二鳍状结构电连接。

- 10.如权利要求1所述的布局图案,其中还包含一电压源Vss,与该至少一第一鳍状结构与该至少一第二鳍状结构电连接。

- 11.如权利要求1所述的布局图案,其中该静态随机存取存储器的布局图案位于一特定范围内,该特定范围具有一边界,其中该桥接部分相邻于该边界。

- 12. 如权利要求1所述的布局图案,其中该第一延伸接触结构位于该J状栅极结构的该长边部分与该短边部分之间。

- 13.如权利要求1所述的布局图案,还包含一第二存取栅极结构,位于该基底上,其中该 第二存取栅极结构与该J状栅极结构的该短边部分排列方向相同。

- 14. 如权利要求13所述的布局图案,其中该第二存取栅极结构与该J状栅极结构的该短边部分具有相同的一对称轴。

- 15. 如权利要求14所述的布局图案,其中还包含第三存取晶体管 (PG3) 以及第四存取晶体管 (PG4) 位于该基底上。

- 16. 如权利要求1所述的布局图案,其中该桥接部分为一单层的多晶硅层。

- 17.如权利要求1所述的布局图案,其中还包含接触结构,位于该桥接部分与该长边部分之间,以及另一接触结构位于该桥接部分与该短边部分之间,且该桥接部分为一金属层。

# 静态随机存取存储器的布局图案

#### 技术领域

[0001] 本发明涉及一种静态随机存取存储器(static random access memory, SRAM),尤其是涉及一种具有增加良率和提升读取速度的静态随机存取存储器(SRAM)的布局图案。

### 背景技术

[0002] 在一嵌入式静态随机存取存储器 (embedded static random access memory, embedded SRAM)中,包含有逻辑电路 (logic circuit)和与逻辑电路连接的静态随机存取存储器。静态随机存取存储器本身属于一种挥发性 (volatile)的存储单元 (memory cell),亦即当供给静态随机存取存储器的电力消失之后,所存储的数据会同时抹除。静态随机存取存储器存储器存储数据的方式是利用存储单元内晶体管的导电状态来达成,静态随机存取存储器的设计是采用互耦合晶体管为基础,没有电容器放电的问题,不需要不断充电以保持数据不流失,也就是不需作存储器更新的动作,这与同属挥发性存储器的动态随机存取存储器 (Dynamic Random Access Memory, DRAM)利用电容器带电状态存储数据的方式并不相同。静态随机存取存储器的存取速度相当快,因此有在电脑系统中当作快取存储器 (cache memory)等的应用。

[0003] 然而随着制作工艺线宽与曝光间距的缩减,现今SRAM元件的制作难以利用现有的架构曝出所要的图案。因此如何改良现有SRAM元件的架构来提升曝光的品质即为现今一重要课题。

#### 发明内容

[0004] 本发明提供一种静态随机存取存储器 (SRAM) 的布局图案,至少包含一第一上拉晶体管 (PL1)、一第二上拉晶体管 (PL2)、一第一下拉晶体管 (PD1)、一第二下拉晶体管 (PD2)、一第一存取晶体管 (PG1)以及一第二存取晶体管 (PG2)位于一基底上,多个鳍状结构位于该基底上,该些鳍状结构至少包含有一至少一第一鳍状结构与至少一第二鳍状结构,至少一J状栅极结构,该至少一J状栅极结构包含有一长边部分、一短边部分以及一连接该长边部分与该短边部分的桥接部分,以及至少一第一延伸接触结构 (N1),横跨于该至少一第一鳍状结构与该至少一第二鳍状结构,其中该至少一第一延伸接触结构与该桥接部分不重叠。

[0005] 此外,上述第一下拉晶体管 (PD1) 至少包含该J状栅极结构以及该些多个鳍状结构,其中该长边部分横跨于该至少一第一鳍状结构与该至少一第二鳍状结构,而该短边部分则跨越该至少一第一鳍状结构,以及还包含至少一第一存取栅极结构,位于该基底上,其中该至少一第一存取栅极结构与该至少一J状栅极结构的该短边部分排列方向相同,且该至少一第一存取栅极结构与该至少一J状栅极结构的该短边部分具有相同的一对称轴。

[0006] 本发明的特征在于,J状栅极结构的长边部分与短边部分都同时跨越了同一鳍状结构,因此在有限的空间内,增加了栅极结构跨越的鳍状结构数量,进一步提升下拉晶体管的读取速度。除此之外,本实施例的另外一特征在于,从上视图来看,接触结构与桥接结构并不互相重叠,两者之间保有一间距。根据申请人实验发现,当桥接结构不与接触结构重叠

时,可以降低寄生电容产生,进而达到增加制作工艺良率、提高SRAM稳定度与读取速度等功效。

#### 附图说明

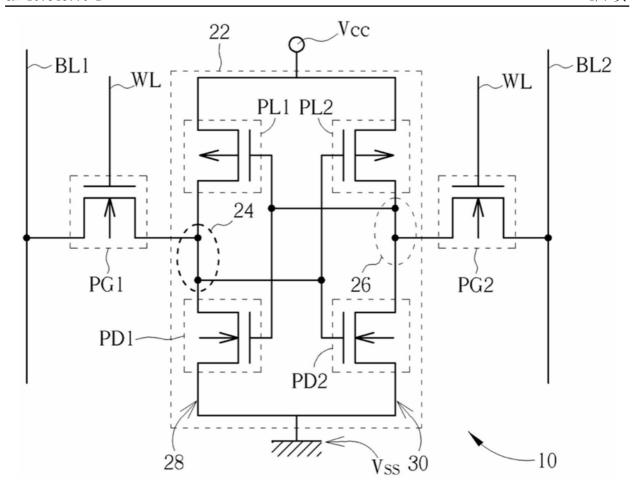

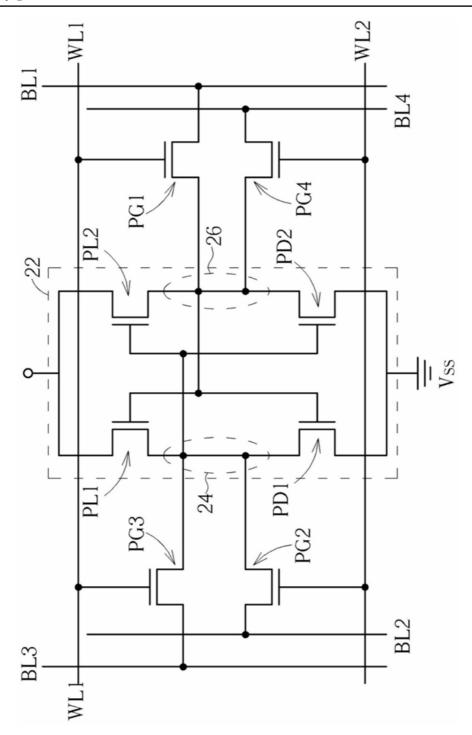

[0007] 图1为本发明静态随机存取存储器中一组六晶体管静态随机存取存储器(sixtransistor SRAM,6T-SRAM)存储单元的电路图;

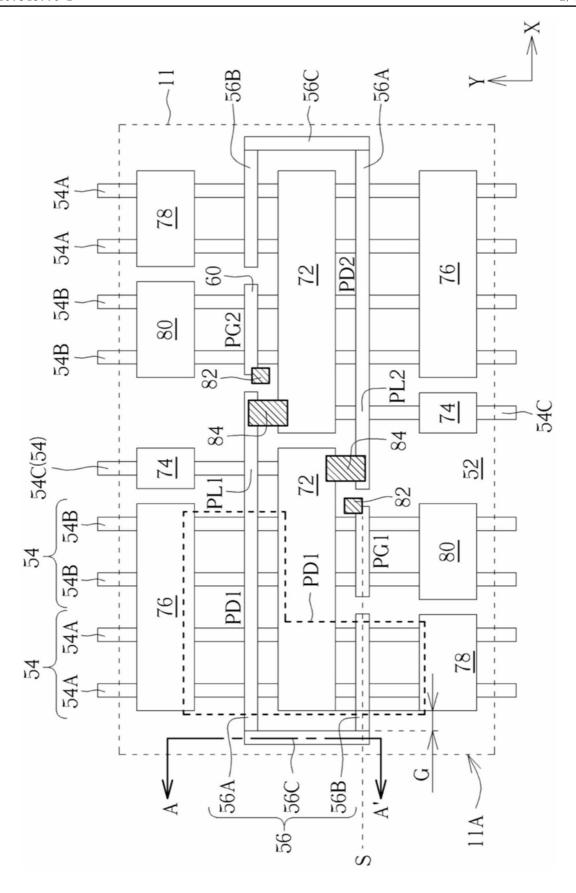

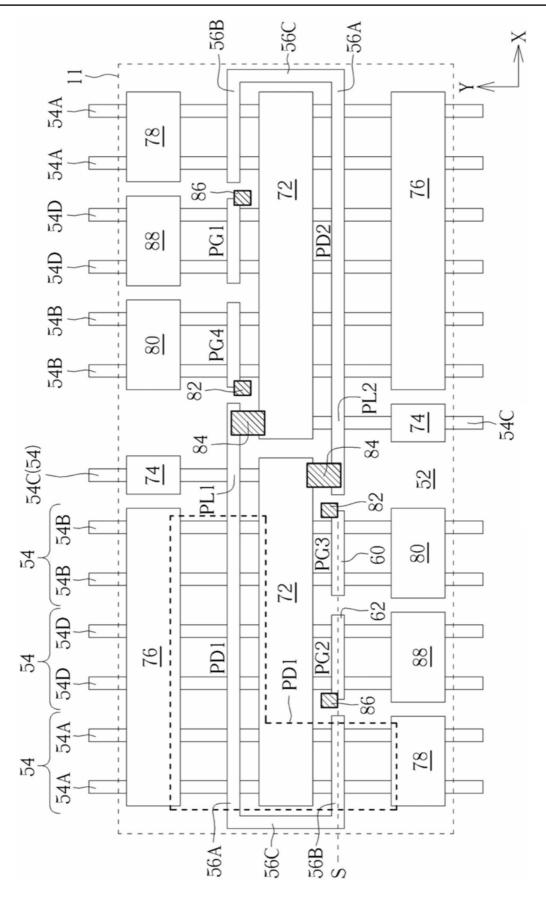

[0008] 图2为本发明较佳实施例的一静态随机存取存储器的布局图:

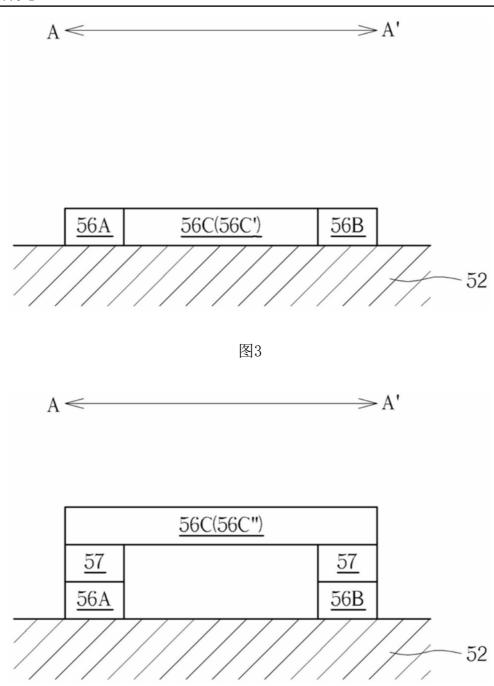

[0009] 图3为本发明的一实施例,得到沿着图2中剖面线A-A'的剖视图;

[0010] 图4为本发明的另一实施例,得到沿着图2中剖面线A-A'的剖视图;

[0011] 图5为本发明静态随机存取存储器中一组双端口八晶体管静态随机存取存储器 (eight-transistor dual port SRAM, 8TDP-SRAM) 存储单元的电路图;

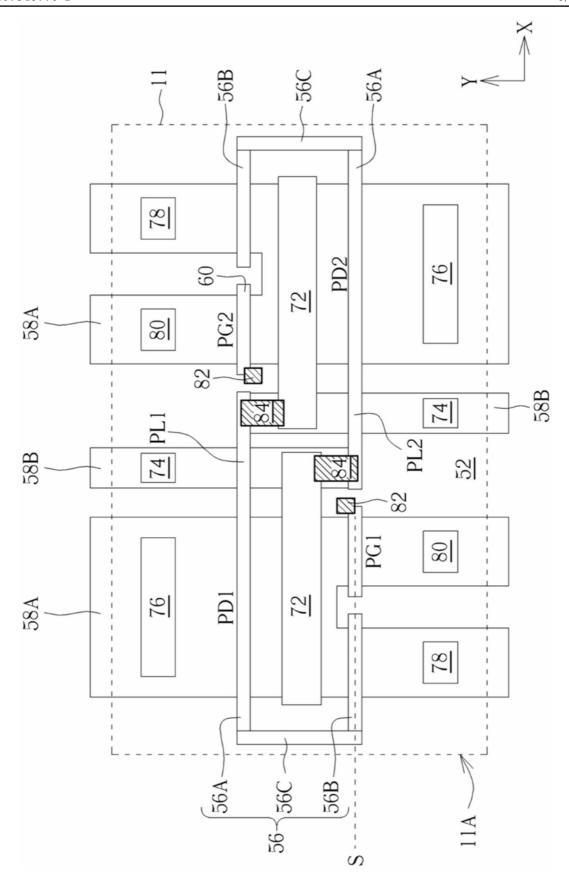

[0012] 图6为本发明第二较佳实施例的一静态随机存取存储器的布局图;

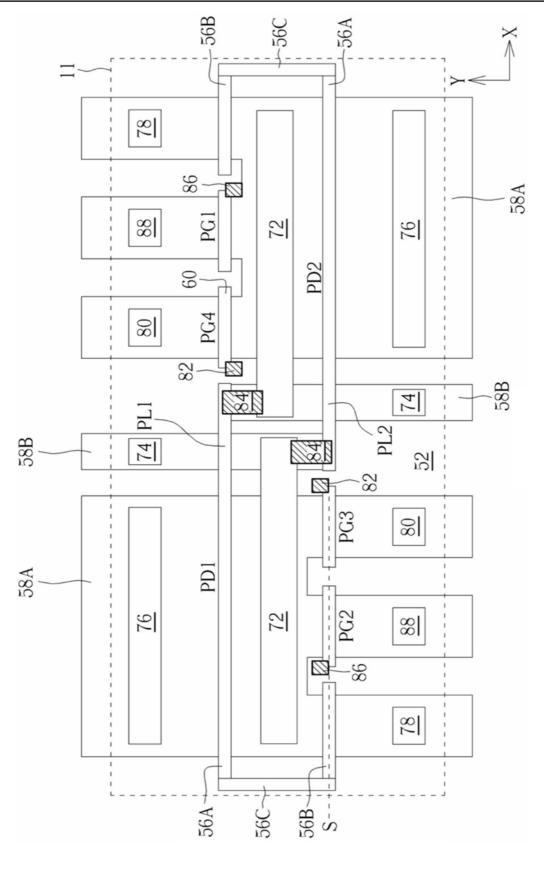

[0013] 图7为本发明另一较佳实施例的一六晶体管静态随机存取存储器的布局图:

[0014] 图8为本发明另一较佳实施例的一八晶体管静态随机存取存储器的布局图。

[0015] 符号说明

[0016] 10 6T-SRAM存储单元

[0017] 11 特定范围

[0018] 11A 边界

[0019] 12 8TDP-SRAM存储单元

[0020] 24 存储节点

[0021] 26 存储节点

[0022] 28 串接电路

[0023] 30 串接电路

[0024] 52 基底

[0025] 54 鳍状结构

[0026] 54A 第一鳍状结构

[0027] 54B 第二鳍状结构

[0028] 54C 第三鳍状结构

[0029] 54D 第四鳍状结构

[0030] 56.J 状栅极结构

[0031] 56A 长边部分

[0032] 56B 短边部=分

[0033] 56C 桥接部分

[0034] 56C'多晶硅层

[0035] 56C"金属层

[0036] 57 接触结构

[0037] 58A 第一扩散区

[0038] 58B 第二扩散区

[0039] 60 第一存取栅极结构

- [0040] 62 第二存取栅极结构

- [0041] 72 延伸接触结构

- [0042] 74、76、78、80、82、84、86、88 接触结构

- [0043] PL1 第一上拉晶体管

- [0044] PD1 第一下拉晶体管

- [0045] PL2 第二上拉晶体管

- [0046] PD2 第二下拉晶体管

- [0047] PG1 第一存取晶体管

- [0048] PG2 第二存取晶体管

- [0049] PG3 第三存取晶体管

- [0050] PG4 第四存取晶体管

- [0051] Vcc 电压源

- [0052] Vss 电压源

- [0053] BL1 位线

- [0054] BL2 位线

- [0055] BL3 位线

- [0056] BL4 位线

- [0057] WL 字符线

- [0058] WL1 字符线

- [0059] WL2 字符线

- [0060] G 间距

## 具体实施方式

[0061] 为使熟习本发明所属技术领域的一般技术者能更进一步了解本发明,下文特列举本发明的较佳实施例,并配合所附附图,详细说明本发明的构成内容及所欲达成的功效。

[0062] 为了方便说明,本发明的各附图仅为示意以更容易了解本发明,其详细的比例可依照设计的需求进行调整。在文中所描述对于图形中相对元件的上下关系,在本领域的人皆应能理解其是指物件的相对位置而言,因此皆可以翻转而呈现相同的构件,此皆应同属本说明书所公开的范围,在此容先叙明。

[0063] 请参照图1与图2,图1为本发明静态随机存取存储器中一组六晶体管静态随机存取存储器(six-transistor SRAM,6T-SRAM)存储单元的电路图,图2为本发明较佳实施例的一静态随机存取存储器的布局图。

[0064] 如图1与图2所示,本发明的静态随机存取存储器较佳包含至少一组静态随机存取存储器单元,其中每一静态随机存取存储器单元包含一六晶体管静态随机存取存储单元 (six-transistor SRAM,6T-SRAM)10。

[0065] 请参考图1,在本实施例中,各6T-SRAM存储单元10较佳由一第一上拉晶体管 (Pull-Up transistor) PL1、一第二上拉晶体管PL2、一第一下拉晶体管 (Pull-Down transistor) PD1、一第二下拉晶体管PD2、一第一存取晶体管 (Access transistor) PG1和一第二存取晶体管PG2构成正反器 (flip-flop),其中第一上拉晶体管PL1和第二上拉晶体管

PL2、第一下拉晶体管PD1和第二下拉晶体管PD2构成栓锁电路(latch),使数据可以栓锁在存储节点(Storage Node)24或26。另外,第一上拉晶体管PL1和第二上拉晶体管PL2是作为主动负载之用,其也可以一般的电阻来取代做为上拉元件,在此情况下即为四晶体管静态随机存取存储器(four-transistor SRAM,4T-SRAM)。另外在本实施例中,第一上拉晶体管PL1和第二上拉晶体管PL2各自的一源极区域电连接至一电压源Vcc,第一下拉晶体管PD1和第二下拉晶体管PD2各自的一源极区域电连接至一电压源Vss。

[0066] 在一实施例中,6T-SRAM存储单元10的第一上拉晶体管PL1、第二上拉晶体管PL2是由P型金属氧化物半导体(P-type metal oxide semiconductor,PMOS)晶体管所组成,而第一下拉晶体管PD1、第二下拉晶体管PD2和第一存取晶体管PG1、第二存取晶体管PG2则是由N型金属氧化物半导体(N-type metal oxide semiconductor,NMOS)晶体管所组成,但本发明不限于此。其中,第一上拉晶体管PL1和第一下拉晶体管PD1一同构成一反向器(inverter),且这两者所构成的串接电路28其两端点分别耦接于一电压源Vcc与一电压源Vss;同样地,第二上拉晶体管PL2与第二下拉晶体管PD2构成另一反向器,而这两者所构成的串接电路30其两端点也分别耦接于电压源Vcc与电压源Vss。

[0067] 此外,在存储节点24处,分别电连接有第二下拉晶体管PD2和第二上拉晶体管PL2的栅极(gate)、及第一下拉晶体管PD1、第一上拉晶体管PL1和第一存取晶体管PG1的漏极(Drain);同样地,在存储节点26上,也分别电连接有第一下拉晶体管PD1和第一上拉晶体管PL1的栅极、及第二下拉晶体管PD2、第二上拉晶体管PL2和第二存取晶体管PG2的漏极。至于第一存取晶体管PG1和第二存取晶体管PG2的栅极则分别耦接至字符线(Word Line)WL,而第一存取晶体管PG1和第二存取晶体管PG2的源极(Source)则分别耦接至相对应的位线(Bit Line)BL1与BL2。

[0068] 请参考图2,在本实施例中,6T-SRAM存储单元10设于一基底52上,例如一硅基底或硅覆绝缘(SOI)基板,基底52上设有多条相互平行排列的鳍状结构54,且各鳍状结构54周围设有浅沟隔离(图未示)。

[0069] 一般而言,一鳍状晶体管需要包含一栅极结构跨越于至少一鳍状结构上,然而根据实验发现,若同一栅极结构同时跨越多个互相平行的鳍状结构,在等效电路上,相当于多个晶体管相互并联,如此有助于提升该鳍状晶体管的栅极宽度,进而提高该鳍状晶体管的读取电流值(Iread),并可以加速整体SRAM的运算速度。

[0070] 因此,本发明的目的之一,是于一有限的固定空间之内,提高栅极结构跨越的鳍状结构数量,进而加速SRAM的运算速度。

[0071] 本发明的特征在于,还包含至少两个J状栅极结构56位于基底52上,两J状栅极结构56对称排列,为简化说明,本实施例中仅对其中一J状栅极结构56(例如图2中左边的J状栅极结构56)进行说明,而两个J状栅极结构56除了结构对称之外,其余特征完全相同。

[0072] J状栅极结构56包含有一长边部分56A、一短边部分56B以及一连接长边部分56A与短边部分56B的桥接部分56C。更详细说明,长边部分56A与短边部分56B两者皆沿着一第一方向排列(例如图2中的X方向),因此两者互相平行排列。此外,长边部分56A的长度较短边部分56B的长度更长,桥接部分56C位于长边部分56A与短边部分56B之间,并且电连接长边部分56A与短边部分56B。此外,桥接部分56C较佳沿着一第二方向排列(例如图2中的Y方向),第一方向与第二方向较佳互相垂直,但不限于此。

[0073] 值得注意的是,本实施例中的6T-SRAM存储单元10位于一特定范围11内,也就是说,特定范围11内仅包含有一组6T-SRAM存储单元10。而桥接部分56C则紧邻上述特定范围11的其中一边界(图2中标示为11A)。此外,图3与图4分别绘示根据本发明的两实施例,得到沿着图2中剖面线A-A'的剖视图。如图3所示,桥接部分56C可能为一单层的多晶硅层(标示为多晶硅层56C'),直接接触长边部分56A与短边部分56B,或是在其他实施例中(图未示),桥接部分56C与长边部分56A以及短边部分56B为一体成型结构。或是如图4所示,桥接部分56C可能为一金属层(标示为金属层56C"),通过两接触结构57分别与长边部分56A与短边部分56B电连接。为了简化图示,上述图3与图4中未绘出介电层,但可理解的是介电层应存在于基底52上,且上述各元件(长边部分56A、短边部分56B、桥接部分56C、接触结构57等)位于介电层中。

[0074] 上述的J状栅极结构56,跨越多个鳍状结构54,举例来说,在此将鳍状结构54分别标示为第一鳍状结构54A、第二鳍状结构54B与第三鳍状结构54C。值得注意的是,本实施例中,第一鳍状结构54A与第二鳍状结构54B的数量都大于1,包含有两根互相平行排列的第一鳍状结构54A,两根互相平行排列的第二鳍状结构54B以及一根第三鳍状结构54C,但上述第一鳍状结构54A、第二鳍状结构54B与第三鳍状结构54C的数量不限于此,可以是任何大于或等于1的整数,且可以依照实际需求而调整。

[0075] 本实施例中,J状栅极结构56的长边部分56A,跨越过第一鳍状结构54A、第二鳍状结构54B与第三鳍状结构54C;而短边部分56B则跨越过第一鳍状结构54A。其中长边部分56A跨越跨越过第三鳍状结构54C的部分,则形成第一上拉晶体管PL1的栅极;另外长边部分56A跨越过第一鳍状结构54A与第二鳍状结构54B的部分,以及短边部分56B跨越过第一鳍状结构54A的部分共同组成上述第一下拉晶体管PD1的栅极(其中图2中虚线范围内表示第一下拉晶体管PD1的范围),换句话说,第一下拉晶体管PD1的栅极跨越过两根第一鳍状结构54A两次,且跨越过两根第二鳍状结构54B一次。

[0076] 所以,在本实施例中,J状栅极结构56的长边部分56A与短边部分56B都同时跨越了第一鳍状结构54A,因此就第一下拉晶体管PD1而言,其包含了J状栅极结构56跨越了共6根鳍状结构(包含有长边部分56A跨越过的两根第一鳍状结构54A与两根第二鳍状结构54B,以及短边部分56B跨越过的两根第一鳍状结构54A),因此在有限的空间内,增加了栅极结构跨越的鳍状结构数量,因此可以提高第一下拉晶体管PD1的栅极宽度(channel width),进一步提高通过第一下拉晶体管PD1的电流量,并增快第一下拉晶体管PD1的读取速度。

[0077] 除了上述的J状栅极结构之外,本实施例中还包含至少两互相对称的第一存取栅极结构60位于基底52上。在此同样为了简化说明,仅针对其中一第一存取栅极结构60(例如图2中左边的第一存取栅极结构60)进行说明。两个第一存取栅极结构60除了结构对称之外,其余特征完全相同。

[0078] 较佳而言,第一存取栅极结构60沿着第一方向排列,且位于短边部分56B的延伸方向上。换句话说,短边部分56B与第一存取栅极结构60拥有相同的一对称轴S。第一存取栅极结构60跨越于第二鳍状结构54B上,组成上述第一存取晶体管PG1的栅极。同样地,另一个第一存取栅极结构60则跨越于另外的第二鳍状结构54B上而组成第二存取晶体管PG2的栅极。[0079] 除了上述鳍状结构以及栅极结构之外,本实施例中6T-SRAM存储单元10还包含有多个接触结构。其中包含有至少两对称排列的延伸接触结构72,位于J状栅极结构56的长边

部分56A与短边部分56B之间,并横跨于各第一鳍状结构54A、各第二鳍状结构54B与第三鳍状结构54C上,将各平行排列的鳍状结构相互连接,请配合图1来看,延伸接触结构72连接第一下拉晶体管PD1、第一上拉晶体管PL1和第一存取晶体管PG1的漏极。另外从上视图来看,延伸接触结构72的形状可能为长条状或是其他形状(例如L型等),本发明不限于此。

[0080] 除了上述延伸接触结构72之外,其他位于基底52上的接触结构包含:接触结构74,连接各第三鳍状结构54C,并且连接电压源Vcc(请配合图1,接触结构74连接第一上拉晶体管PL1及第二上拉晶体管PL2的源极至电压源Vcc);接触结构76,跨越于各第一鳍状结构54A与各第二鳍状结构54B,并且连接电压源Vss(请配合图1,接触结构76连接第一下拉晶体管PD1及第二下拉晶体管PD2的源极至电压源Vss);接触结构78,跨越于各第一鳍状结构54A,并且连接电压源Vss(请配合图1,接触结构78连接第一下拉晶体管PD1及第二下拉晶体管PD2的源极至电压源Vss);接触结构78连接第一下拉晶体管PD1及第二下拉晶体管PD2的源极至电压源Vss);接触结构80,跨越于各第二鳍状结构54B,并且连接位线BL1或BL2(请配合图1,接触结构80连接第一存取晶体管PG1及第二存取晶体管PG2的源极至分别至位线BL1与BL2);接触结构82,位于各第一存取栅极结构60上,并且连接字符线WL(请配合图1,接触结构82连接第一存取晶体管PG1及第二存取晶体管PG2的栅极至字符线WL);以及接触结构84,位于各第三鳍状结构54C上,并且连接J状栅极结构56以及延伸接触结构72(请配合图1,接触结构84连接第一上拉晶体管PL1的栅极至存储节点26,并连接第二上拉晶体管PL2的栅极至存储节点26,并连接第二上拉晶体管PL2的栅极至存储节点24)。此外,各接触结构也呈现对称排列,在此不多加赘述。

[0081] 除此之外,本发明的另外一特征在于,从上视图来看,延伸接触结构72与桥接结构56C并不互相重叠,两者之间保有一间距G。根据申请人实验发现,当桥接结构56C不与接触结构重叠时,可以降低寄生电容产生,进而达到增加制作工艺良率、提高SRAM稳定度与读取速度等功效。

[0082] 下文将针对本发明的静态随机存取存储器的不同实施样态进行说明,且为简化说明,以下说明主要针对各实施例不同之处进行详述,而不再对相同之处作重复赘述。此外,本发明的各实施例中相同的元件以相同的标号进行标示,以利于各实施例间互相对照。

[0083] 请参照图5与图6,图5为根据本发明第二较佳实施例的静态随机存取存储器中一组体静态随机存取存储器(static random access memory,SRAM)存储单元的电路图。图6为本发明第二较佳实施例的一静态随机存取存储器的布局图。

[0084] 如图5与图6所示,本实施例的静态随机存取存储器较佳包含至少一组静态随机存取存储器单元,其中每一静态随机存取存储器单元包含一双端口八晶体管静态随机存取存储器 (eight-transistor dual port SRAM,8TDP-SRAM) 存储单元12。

[0085] 在本实施例中,各8TDP-SRAM存储单元12较佳由一第一上拉晶体管(Pull-Up transistor)PL1、一第二上拉晶体管PL2、一第一下拉晶体管(Pull-Down transistor)PD1、一第二下拉晶体管PD2、一第一存取晶体管(Access transistor)PG1、一第二存取晶体管PG2、一第三存取晶体管PG3以及一第四存取晶体管PG4构成正反器(flip-flop),其中第一上拉晶体管PL1和第二上拉晶体管PL2、第一下拉晶体管PD1和第二下拉晶体管PD2构成一栓锁电路22(latch),使数据可以栓锁在存储节点(Storage Node)24或26。另外,第一上拉晶体管PL1和第二上拉晶体管PL2是作为主动负载之用,其也可以一般的电阻来取代做为上拉元件,在此情况下即为四晶体管静态随机存取存储器(four-transistor SRAM,4T-SRAM)。另外在本实施例中,第一上拉晶体管PL1和第二上拉晶体管PL2各自的一源极区域电连接至

一电压源Vcc,第一下拉晶体管PD1和第二下拉晶体管PD2各自的一源极区域电连接至一电压源Vss。

[0086] 此外,在存储节点24处,分别电连接有第二下拉晶体管PD2和第二上拉晶体管PL2的栅极(gate)、及第一下拉晶体管PD1、第一上拉晶体管PL1和第三存取晶体管PG3与第二存取晶体管PG2的漏极(Drain);同样地,在存储节点26上,也分别电连接有第一下拉晶体管PD1和第一上拉晶体管PL1的栅极、及第二下拉晶体管PD2、第二上拉晶体管PL2和第一存取晶体管PG1与第四存取晶体管PG4的漏极。至于第一存取晶体管PG1和第三存取晶体管PG3的栅极G则耦接至字符线(Word Line)WL1;第二存取晶体管PG2和第四存取晶体管PG4的栅极G则耦接至字符线WL2,而第一存取晶体管PG1的源极耦接至相对应的位线(Bit Line)BL1;第二存取晶体管PG2的源极耦接至相对应的位线BL2;第三存取晶体管PG3的源极耦接至相对应的位线BL3;第四存取晶体管PG4的源极耦接至相对应的位线BL4。

[0087] 请参考图6,本实施例的8TDP-SRAM存储单元12的布局图,与上述6T-SRAM所述的布局图大致相同(请参考图2),其中重复的元件在此不多加赘述。而主要的不同之处在于,由于更增设了第三存取晶体管PG3与第四存取晶体管PG4,因此本实施例中,除了原先的第一鳍状结构54A、第二鳍状结构54B与第三鳍状结构54C之外,还包含有至少两第四鳍状结构54D(同样地,呈对称排列)位于基底52上,各第四鳍状结构54D位于第一鳍状结构54A与第二鳍状结构54B之间。本实施例中,包含有两条相互平行排列的第四鳍状结构54D,但本发明不限于此。第四鳍状结构54D的数量可以是任何大于或等于1的整数,也可依照实际需求而调整。

[0088] 此外,还包含有至少两对称排列的第二存取栅极结构62位于基底52上,第二存取栅极结构62沿着第一方向排列,且位于短边部分56B的延伸方向上。换句话说,短边部分56B、第一存取栅极结构60与第二存取栅极结构62拥有相同的一对称轴S。第二存取栅极结构62跨越于第四鳍状结构54D上,组成第二存取晶体管PG2与第一存取晶体管PG1的栅极。

[0089] 另外,本实施例中,延伸接触结构72位于J状栅极结构56的长边部分56A与短边部分56B之间,并横跨于第一鳍状结构54A、第二鳍状结构54B、第三鳍状结构54C与第四鳍状结构54D上,将各平行排列的鳍状结构相互连接,请配合图5来看,延伸接触结构72连接第一下拉晶体管PD1、第一上拉晶体管PL1、第二存取晶体管PG2与第三存取晶体管PG3的漏极。另外上述延伸接触结构72的形状可能为条状或是其他形状(例如L型等),本发明不限于此。

[0090] 除了上述延伸接触结构72之外,其他位于基底52上的接触结构包含:接触结构74,连接各第三鳍状结构54C,并且连接电压源Vcc(请配合图5,接触结构74连接第一上拉晶体管PL1及第二上拉晶体管PL2的源极至电压源Vcc);接触结构76,跨越于第一鳍状结构54A与第二鳍状结构54B,并且连接电压源Vss(请配合图5,接触结构76连接第一下拉晶体管PD1及第二下拉晶体管PD2的源极至电压源Vss);接触结构78,跨越于各第一鳍状结构54A,并且连接电压源Vss(请配合图5,接触结构78连接第一下拉晶体管PD1及第二下拉晶体管PD2的源极至电压源Vss);接触结构78连接第一下拉晶体管PD1及第二下拉晶体管PD2的源极至电压源Vss);接触结构80,跨越于各第二鳍状结构54B,并且连接位线BL3或BL4(请配合图5,接触结构80连接第三存取晶体管PG3的源极至位线BL3,并连接第四存取晶体管PG4的源极至位线BL4);接触结构82,位于各第一存取栅极结构60上,并且连接字符线WL1或WL2(请配合图5,接触结构82连接第三存取晶体管PG3的栅极至字符线WL1,并连接第四存取晶体管PG4的栅极至字符线WL2);接触结构84,位于各第三鳍状结构54C上,并且连接J状栅极体管PG4的栅极至字符线WL2);接触结构84,位于各第三鳍状结构54C上,并且连接J状栅极

结构56以及延伸接触结构72 (请配合图5,接触结构84连接第一上拉晶体管PL1与第一下拉晶体管PD1的栅极至存储节点26,并连接第二上拉晶体管PL2与第二下拉晶体管PD2的栅极至存储节点24)。另外还包含:接触结构86,位于各第二存取栅极结构62上,并且连接字符线WL2或WL1 (请配合图5,接触结构86连接第二存取晶体管PG2的栅极至字符线WL2,并连接第一存取晶体管PG1的栅极至字符线WL1);以及接触结构88,跨越于各第四鳍状结构54D,并且连接位线BL1或BL2 (请配合图5,接触结构88连接第二存取晶体管PG3的源极至位线BL2,并连接第一存取晶体管PG1的源极至位线BL1)。可以理解的是,各接触结构也呈现对称排列,在此不多加赘述。

[0091] 本实施例的特征在于,J状栅极结构56的长边部分56A与短边部分56B都同时跨越了第一鳍状结构54A,因此就第一下拉晶体管PD1而言,其栅极结构共跨越了8根鳍状结构(包含有长边部分56A跨越过的两根第一鳍状结构54A、两根第二鳍状结构54B、两根第四鳍状结构54D,以及短边部分56B跨越过的两根第一鳍状结构54A),因此在有限的空间内,增加了栅极结构跨越的鳍状结构数量,进一步提升第一下拉晶体管PD1的读取速度。除此之外,本实施例的另外一特征在于,从上视图来看,延伸接触结构72与桥接结构56C并不互相重叠,两者之间保有一间距G。根据申请人实验发现,当桥接结构56C不与接触结构重叠时,可以降低寄生电容产生,进而达到增加制作工艺良率、提高SRAM稳定度与读取速度等功效。

[0092] 上述各实施例,都包含有鳍状结构54形成于基底52上,但在本发明的其他实施例中,可以不形成鳍状结构于基底上,而仅对基底进行离子掺杂步骤,在基底中形成多个扩散区(diffusion region),接着再继续形成上述的J状栅极结构、第一存取栅极结构以及接触结构等元件。也就是说,下述实施例中,以平面式的晶体管(planar transistor)代替上述实施例中的鳍状晶体管。请参考图7,图7为本发明另一较佳实施例之一六晶体管静态随机存取存储器的布局图。本实施例中,并未形成鳍状结构,而是在基底52中以离子布植等方式形成至少两对称的第一扩散区58A以及两对称的第二扩散区58B。接着形成如第一较佳实施例所述的J状栅极结构56、第一存取栅极结构60、延伸接触结构72以及多个接触结构(包含接触结构74、76、78、80、82、84)。J状栅极结构56位于第一扩散区58A以及第二扩散区58B上,而第一存取栅极结构60则位于第一扩散区58A上。本实施例中的第一下拉晶体管PD1的栅极也包含J状栅极结构56,并且J状栅极结构56的长边部分56A与短边部分56B都位于第一扩散区58A上,因此具有与其他实施例相同的优点,也就是可以提高第一下拉晶体管PD1的栅极宽度(channel width),进一步提高通过第一下拉晶体管PD1的电流量,并增快第一下拉晶体管PD1的读取速度。除了上述扩散区的特征之外,其余各部件的特征、材料特性以及制作方法与上述第一较佳实施例相似(可参考图2所述),故在此并不再赘述。

[0093] 同样地,第二较佳实施例中所述的静态随机存取存储器的布局图(请参考图6),也可以用平面式的晶体管代替该实施例中的鳍状晶体管。如图8所示,图8为本发明另一较佳实施例之一八晶体管静态随机存取存储器的布局图。本实施例中,并未形成鳍状结构,而是在基底52中以离子布植等方式形成至少两对称的第一扩散区58A以及两对称的第二扩散区58B。接着形成如第二较佳实施例所述的J状栅极结构56、第一存取栅极结构60、第二存取栅极结构62、延伸接触结构72以及多个接触结构(包含接触结构74、76、78、80、82、84、86、88)。J状栅极结构56位于第一扩散区58A以及第二扩散区58B上,而第一存取栅极结构60与第二存取栅极结构62则位于第一扩散区58A上。本实施例中的第一下拉晶体管PD1的栅极也包含

J状栅极结构56,并且J状栅极结构56的长边部分56A与短边部分56B都位于第一扩散区58A上,因此具有与其他实施例相同的优点,也就是可以提高第一下拉晶体管PD1的栅极宽度 (channel width),进一步提高通过第一下拉晶体管PD1的电流量,并增快第一下拉晶体管 PD1的读取速度。除了上述扩散区的特征之外,其余各部件的特征、材料特性以及制作方法与上述第二较佳实施例相似(可参考图6所述),故在此并不再赘述。

[0094] 以上所述仅为本发明的较佳实施例,凡依本发明权利要求所做的均等变化与修饰,皆应属本发明的涵盖范围。

图1

图2

图5

图6

图7

图8