### (19) World Intellectual Property Organization International Bureau

## (43) International Publication Date 27 February 2003 (27.02.2003)

#### **PCT**

# (10) International Publication Number WO 03/017413 A1

(51) International Patent Classification<sup>7</sup>: H01M 10/46

(21) International Application Number: PCT/US02/26333

(22) International Filing Date: 19 August 2002 (19.08.2002)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

60/313,260 17 August 2001 (17.08.2001) US 09/948,828 7 September 2001 (07.09.2001) US

(71) Applicant (for all designated States except US): O2 MI-CRO, INC. [US/US]; 3118 Patrick Henry Drive, Santa Clara, CA 95054 (US).

(72) Inventor; and

(75) Inventor/Applicant (for US only): BUCUR,, Constantin [RO/US]; 1674 Hollenbeck Avenue #5, Sunnyvale, CA 94087 (US).

- (74) Agents: PFLEGER, Edmund et al.; 55 South Commercial Street, Manchester, NH 03101 (US).

- (81) Designated States (national): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NO, NZ, OM, PH, PL, PT, RO, RU, SD, SE, SG, SI, SK, SL, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, YU, ZA, ZM, ZW.

- (84) Designated States (regional): ARIPO patent (GH, GM, KE, LS, MW, MZ, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European patent (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE, SK, TR), OAPI patent (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### **Published:**

with international search report

[Continued on next page]

(54) Title: VOLTAGE MODE, HIGH ACCURACY BATTERY CHARGER

(57) Abstract: A voltage mode battery charging system is provided that includes a battery current control section (28), a battery voltage control section (32), and a power control section (36). The battery current control section (28) and battery voltage control section (32) each generate signals indicative of the battery charging current and battery voltage, respectively. The power control section (36) generates a signal indicative of the power available from an adapter source. Each of these signals is combined at common node, and if any of these sections exceeds a threshold, battery charging current is decreased.

03/017413 A1

### WO 03/017413 A1

before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

#### **VOLTAGE MODE, HIGH ACCURACY BATTERY CHARGER**

2

3

The present application claims priority to Provisional Application Serial No. 60/313,260, filed August 17, 2001, and assigned to the same assignee.

#### Field of the Invention

The present invention relates to a battery charger circuit for charging one or more batteries. In particular, the present invention relates to a voltage mode battery charger that uses both current and voltage control to regulate the charging cycle and to provide accurate charging and charge termination.

#### **Summary of the Invention**

In one aspect, the present invention provides a circuit for adjusting the duty cycle of a PWM signal. The circuit includes a battery current control section that generates a current control signal proportional to an amount battery charging current exceeds a predetermined battery charging current threshold. The circuit also includes a battery voltage control section that generates a voltage control signal proportional to an amount a battery voltage exceeds a predetermined battery voltage threshold. A compensation capacitor and a current source charging the compensation capacitor are also provided. A comparator generates a PWM signal based on the amplitude of the voltage on the compensation capacitor. The current source and the current control signal and voltage control signal are summed together at a common node, so that the current control signal and/or said voltage control signal reduce the voltage on the compensation capacitor thereby reducing the duty cycle of the PWM signal.

In another aspect, the present invention provides a battery charging circuit that includes a current control circuit generating a current control signal proportional to the amount battery charging current exceeds a predetermined battery charging current threshold; a voltage control circuit generating a voltage control signal to the amount battery voltage exceeds a predetermined battery voltage threshold; a DC/DC converter circuit generating the battery charging current from a DC source; and a PWM signal generator circuit generating a PWM signal for controlling the duty cycle of the DC/DC converter circuit. The PWM circuit comprises a comparator, an oscillator, a compensation capacitor and a current source charging the compensation capacitor. The comparator generates the PWM signal based on the voltage on the compensation capacitor. The current source and the current control signal and voltage control signal are summed together at a common node so that the current control signal and/or the voltage control signal reduce the voltage on the compensation capacitor

thereby reducing the duty cycle of the PWM signal and thereby reducing the current delivered by the DC/DC converter circuit.

It will be appreciated by those skilled in the art that although the following Detailed Description will proceed with reference being made to preferred embodiments and methods of use, the present invention is not intended to be limited to these preferred embodiments and methods of use. Rather, the present invention is of broad scope and is intended to be limited as only set forth in the accompanying claims.

Other features and advantages of the present invention will become apparent as the following Detailed Description proceeds, and upon reference to the Drawings, wherein like numerals depict like parts, and wherein:

#### Brief Description of the Drawings

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16 17

18

19

20

21

22

23

24

25

2627

28

29

30

31

32

33

34

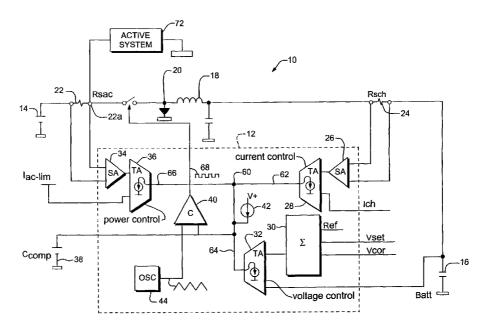

Figure 1 is a block diagram of an exemplary battery cell charging system according to the present invention;

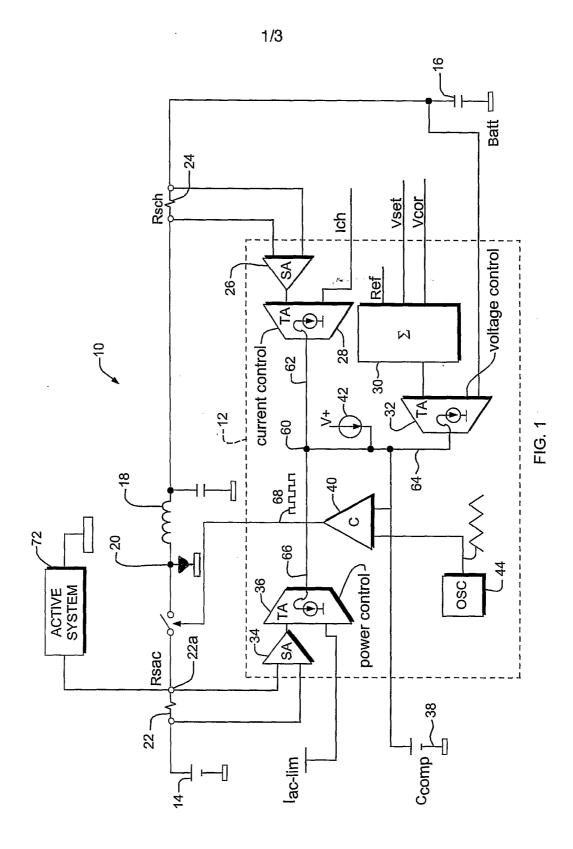

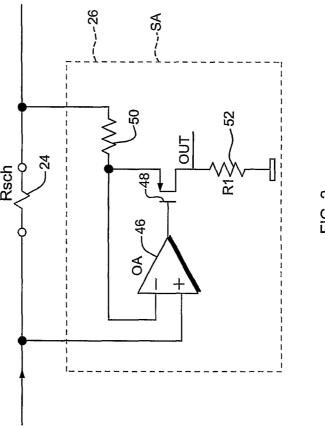

Figure 2 is an exemplary amplifier circuit of the present invention; and Figure 3 is a timing diagram representing an oscillator signal and DC signal to generate a PWM signal of the system of Figure 1.

#### **Detailed Description of Exemplary Embodiments**

Figure 1 depicts a voltage mode battery charger system 10 according to one exemplary embodiment. The system 10 includes a voltage mode battery charger circuit 12 for charging one or more batteries 16 using a DC source 14. The DC source may be an AC/DC adapter or other power supply. Circuit 12 operates to control the duty cycle of the Buck converter circuit 18 (comprising an inductor and capacitor, as is well understood in the art) via switches 20, to control the amount of charging power delivered to the battery 16. As an overview, circuit 12 controls the duty cycle of the Buck converter 18 by monitoring the source current, the battery charging current (current mode) and the battery voltage (voltage mode). Battery charging current is sensed across the sense resistor (or impedance) Rsch. Instead of sensing the current through the inductor (as in conventional current mode topologies), the present invention uses a voltage mode topology by sensing the current across Rsch. In this manner, and by utilizing both battery current control and voltage, the present invention achieves more accurate charging of the battery towards the end of the charging cycle, and provides more accurate charge termination than can be achieved with conventional current mode charging topologies. The details of the system 10 are described below. Essentially, the charger circuit 12 operates to control the duty cycle of the buck

converter 18 by controlling the power on the compensation capacitor Ccomp 38. The circuit

1 12 includes a battery current control section comprised of sense amplifier 26 and 2 transconductance amplifier 28, a battery voltage control section comprised of summing block 3 30 and transconductance amplifier 32, and a power control section comprised of sense 4 amplifier 34 and transconductance amplifier 36. The battery current control section and 5 battery voltage control section each generate signals indicative of the battery current and 6 voltage, respectively. The power control section generates a signal indicative of the power 7 available from the source 14. Each of these sections is combined (at node 60), and if any of 8 these sections exceeds a threshold, the power delivered to the charge capacitor decreases, 9 thereby reducing the duty cycle of the Buck converter. This operation is described in greater 10 detail below. 11 The duty cycle of the Buck converter 18 is controlled by the comparator 40, via 12 switches 20. The input of the comparator 40 is the voltage on the compensation capacitor 13 (Ccomp) 38 and a sawtooth signal generated by the oscillator 44. The output of the 14 comparator 40 is a PWM signal 68, whose pulse width (duty cycle) is reflected in the 15 intersection of the amplitude of the voltage on Ccomp 38 and the sawtooth signal. In this 16 sense, the duty cycle of the PWM signal thus generated is based on the voltage on the 17 compensation capacitor 38 and the sawtooth signal generated by the oscillator 44. "Based 18 on", as used herein, is to be interpreted broadly and generally means "as function of" or 19 "related to". The higher the amplitude of the voltage on Ccomp, the greater the duty cycle of 20 the PWM signal 68. In the exemplary embodiment, the sawtooth signal is a fixed frequency 21 signal, and the duty cycle of the PWM is therefore adjusted by adjusting the amplitude of the 22 voltage on Ccomp 38. Ccomp 38 is charged by the current source 42. When no signal is 23 generated by any of the current control section, the voltage control section or the power 24 control section, the current source charges Ccomp to maximum level, and thus the PWM is at 25 maximum duty cycle and the Buck converter is delivering maximum charging current and 26 voltage to the battery. Any signal generated by the current control section, the voltage 27 control section or the power control section acts as a sink to the compensation capacitor 38, 28 thereby reducing the voltage on the compensation capacitor and thereby reducing the duty 29 cycle of the PWM signal. In this manner, charging current is controllably delivered to the 30 battery 16. The particulars of the Buck converter 18 and switches 20 are well understood in 31 this art, and are not important to the present invention, and may be generalized as a 32 controllable DC/DC converter circuit.

3

33

**Current Control**

1 The current control section (circuit) includes a sense amplifier 26 and a 2 transconductance amplifier 28. The sense amplifier monitors the battery charging current 3 across the sense impedance Rsch 24, and generates a signal proportional to battery charge 4 current. The transconductance amplifier 28 receives the output of the sense amplifier 26 and 5 compares that signal with a programmed (desired) battery current signal Ich. As a general 6 matter, the inputs of the transconductance amplifier 28 are voltage signals, and the output is a 7 proportional current signal. The output of the transconductance amplifier is the current 8 control signal 62, which is proportional to the amount the battery charging current exceeds 9 the programmed Ich. Ich is zero until the battery charging current exceeds the programmed 10 current value Ich. The programmed value Ich is set to according to the particular battery type 11 and requirements, for example set to charge a conventional Lilon battery, as is well 12 understood in the art. 13 If the battery charging current exceeds the threshold Ich, the amplifier 28 generates a 14 proportional current control signal 62. Since the output of the amplifier is coupled to the 15 negative side of the current source 42 (at node 60), any signal generated by the amplifier 28 16 acts to sink current from the source 42. In turn, this operates to reduce the voltage on Ccomp 17 38, thereby reducing the duty cycle of the PWM signal 68 and reducing the charging current 18 delivered to the battery. Since the output current control signal 62 is proportional to the input 19 values, the duty cycle is dynamically adjusted as a function of battery charging current. 20 The current sense amplifier 26 may be a custom or off-the-shelf amplifier, as is readily available in the art. However, as is also understood in the art, amplifier 26 must 21 22 provide large common mode voltage rejection. Accordingly, and referring now to Figure 2, 23 another aspect of the present invention is an amplifier configuration to alleviate the 24 requirement for large common mode voltage rejection. The sense amplifier 26 depicted in 25 Figure 2 includes a switch 48 controlled by an operational amplifier 46, and gain resistors R1 26 50 and R2 52. The amplifier 26 of Figure 2 is not sensitive to common mode voltage. 27 Rather, the switch transfers the floating differential voltage that appears across Rsch by 28 referring it to ground and amplifying the voltage according to the gain given by R2/R1. 29 Voltage Control 30 The voltage control section (circuit) includes the summing block 30 and a 31 transconductance amplifier 32. In the exemplary embodiment, the summing block 30 32 includes three inputs: a high-precision reference or trim voltage Ref, a voltage set (Vset) and 33 a voltage correction (Vcor) signal. In the exemplary embodiment, the battery 16 is a LiIon 34 battery. Lilon batteries are very sensitive to overvoltage conditions, and indeed become

, 1 hazardous if overcharged. Thus, the reference or trim signal Ref is accurate to within the 2 tolerance required by the battery. For LiIon, the tolerance is on the order of +/- 0.005 Volts. 3 However, other battery types and reference voltage requirements are equally contemplated herein. Vset represents a voltage setting value, usually supplied by the manufacturer of the 4 5 battery. Vcor is a correction signal that is proportional to the charging current, and is 6 provided as a compensation signal for the particulars of the charging apparatus and for 7 parasitic resistance associated with the battery (since battery voltage cannot be measured 8 directly, and one must factor in parasitic resistance). Although not shown, Vcor can be 9 obtained by tapping a voltage divider placed in parallel with the output of sense amplifier 26. 10 These three signals are summed in a weighted fashion in summing block 30. For example, 11 the output of the summing block 30 can be set to the reference voltage + (Vset/x) + Vcor/y); 12 where x and y are chosen in accordance with the desired voltage setting value and correction 13 value, respectively. Vcor and Vset need not be as accurate as the reference voltage, since 14 their contribution is divided diminished by x and y. 15 The output weighted voltage signal from the summer block 30 may be generally 16 deemed as a predetermined battery voltage threshold signal. The transconductance amplifier 17 32 compares the output of the summer block to the battery voltage. The output of the 18 amplifier 32 is a voltage control signal 64, which is proportional to the amount the battery 19 voltage exceeds the threshold established by the summing block. As with the current control 20 section described above, signal 64 is nonzero if the battery voltage exceeds the threshold 21 determined by the summer block. Since the output of the amplifier 32 is coupled to the 22 negative side of the current source 42 (at node 60), any signal 64 generated by the amplifier 23 32 acts to sink current from the source. In turn, this operates to reduce the voltage on Ccomp 24 38, thereby reducing the duty cycle of the PWM signal 68 and reducing the charging current 25 delivered to the battery. Since the output 64 of the amplifier 32 is proportional to the input 26 values, the duty cycle is dynamically adjusted to achieve a desired battery voltage. 27 Power Control 28 The power control section (circuit) includes a sense amplifier 34 and a 29 transconductance amplifier 36. The power control section is provided to reduce the duty 30 cycle of the Buck converter, and thereby reduce the charging current delivered to the battery 31 if the DC source needs to deliver more power to an active system 72 (e.g., portable electronic 32 device) attached to the source. The active system is coupled in parallel to the charging 33 system 10 across the sense resistor Rsac. Since the total amount of power provided by the

source 14 is fixed, in a well-designed system the load requirements of the active system and

34

battery charging circuit are balanced. The power control section ensures that the active system always takes priority (in terms of power requirements) by reducing the charging current to meet the demands of the active system. Accordingly, the power control section generates a power control signal 66 proportional to the amount of power required by the battery charger and the active system exceeds the threshold Iac\_lim. Iac\_lim is typically the maximum that can be delivered by the adapter source 14. For example, the source 14 may be simultaneously supplying power to an active system (not shown) and charging current to the battery. If the portable system requires more power, charging current to the battery is accordingly reduced to meet the demands of the system. The source 14 is generally defined as a DC power source, as may be supplied from an AC/DC adapter.

33.

The sense amplifier 34 monitors the total adapter current delivered by the source 14 across the sense impedance Rsac 22. The total adapter (source) current includes the system current (i.e., current delivered to a portable system (not shown) connected to the source 14) and the battery charger circuit 12 (which is a measure of the charging current divided by duty cycle of the Buck converter 18). The signal across the sense resistor Rsac is a signal proportional to the total adapter current. The transconductance amplifier 36 receives the output of the sense amplifier 34 and compares that signal with a power threshold signal Iac\_lim. Thus, if the signal across the sense resistor is larger than Iac\_lim, this indicates that the system is requiring more power, and accordingly battery charging current is to be reduced. Of course, this limit signal may be fixed, or may be adjusted based on the dynamic power requirements of the system and/or changes in the source. The output of the transconductance amplifier is the power control signal 66, which is zero until the power required by the battery charger and the active system exceeds the threshold value Iac\_lim.

If the power required by the battery charger and the active system exceeds the threshold Iac\_lim, the amplifier 36 generates a proportional power control signal 66. Since the output of the amplifier is coupled to the negative side of the current source 42 (at node 60), any signal generated by the amplifier 36 acts to sink current from the source. In turn, this operates to reduce the voltage on Ccomp 38, thereby reducing the duty cycle of the PWM signal 68 and reducing the charging current delivered to the battery. Since the output 66 of the amplifier 36 is proportional to the input values, the duty cycle is dynamically adjusted as a function of balancing power demands between a system and the battery, and so as not to exceed a maximum power output of the DC source 14.

Figure 3 depicts a timing diagram 70 representing the PWM signal 68 (bottom figure) and the intersection between the voltage on the compensation capacitor, Vccomp, and the

sawtooth signal 44 (top figure). In the present exemplary embodiment, Vccomp is essentially

1 a DC signal whose amplitude is moved up by the current source 42, and down by either the 2 current control signal 62, the voltage control signal 64 or the power control signal 66. In 3 other words, the value (amplitude) of Vccomp is the sum of signals (42-(62, 64 and/or 66)). 4 By moving the value of Vccomp downward, the duty cycle of PWM signal is decreased. 5 6 7 Thus, with present invention, the duty cycle of the PWM signal can be adjusted using a differential the compensation capacitor. In the exemplary embodiments, adjusting the 8 9 PWM is accomplished dynamically as a function of battery charging current, battery voltage 10 and/or system power requirements. The topology depicted in Figure 1 is a voltage mode topology. Voltage mode topology means that the sense resistor Rsch is placed outside of the 11 12 Buck converter, and thus the current across this resistor is a DC value (without ripple). Those

skilled in the art will recognize numerous modifications to the present invention. These and

all other modifications as may be apparent to one skilled in the art are deemed within the

spirit and scope of the present invention, only as limited by the appended claims.

13

14

15

1 <u>CLAIMS</u>

- 2 1. A circuit for adjusting the duty cycle of a PWM signal, comprising:

- a battery current control section generating a current control signal proportional to an

- 4 amount a battery charging current exceeds a predetermined battery charging current

- 5 threshold; a battery voltage control section generating a voltage control signal proportional to

- an amount a battery voltage exceeds a predetermined battery voltage threshold; a

- 7 compensation capacitor and a current source charging said compensation capacitor; and a

- 8 comparator generating a PWM signal based on the amplitude of the voltage on said

- 9 compensation capacitor; said current source and said current control signal and voltage

- 10 control signal summed together at a common node, said current control signal and/or said

- voltage control signal reducing the voltage on said compensation capacitor thereby reducing

- the duty cycle of said PWM signal.

- 13 2. A circuit as claimed in claim 1, further comprising a power control section generating

- a power control signal proportional to an amount of total current that is required by an active

- system and a battery charger; said current source and said current control signal and voltage

- 16 control signal and said power control signal summed together at said common node, said

- 17 current control signal and/or said voltage control signal and/or said power control signal

- 18 reducing the voltage on said compensation capacitor thereby reducing the duty cycle of said

- 19 PWM signal.

- 20 3. A circuit as claimed in claim 2, wherein said power control section comprises a sense

- 21 amplifier for sensing the total current generated by said source and generating a signal

- 22 indicative of said total current generated by DC source, and a transconductance amplifier

- 23 comparing said signal indicative of said total current generated by said source with a

- 24 predetermined power threshold signal.

- 25 4. A circuit as claimed in claim 3, wherein said power control signal has a nonzero value

- 26 if said signal indicative of said total current generated by said source exceeds said power

- 27 threshold signal.

- 28 5. A circuit as claimed in claim 1, wherein said current control section comprises a sense

- 29 amplifier for sensing charging current supplied to said battery and generating a signal

- 30 indicative of charging current supplied to said battery, and a transconductance amplifier

- 31 comparing said signal indicative of charging current supplied with a predetermined charging

- 32 current signal and generating said current control signal.

1 6. A circuit as claimed in claim 5, wherein said current control signal has a nonzero

- 2 value if said signal indicative of charging current supplied to said battery exceeds said

- 3 predetermined charging current signal.

- 4 7. A circuit as claimed in claim 1, wherein said voltage control section comprises a

- 5 summing block generating a predetermined battery voltage signal, and a transconductance

- 6 amplifier comparing said signal indicative of battery voltage with said predetermined signal

- 7 and generating said voltage control signal.

- 8 8. A circuit as claimed in claim 7, wherein said summing block having a first input

- 9 signal comprising a reference voltage signal, said reference signal being selected in

- accordance with a threshold voltage for said battery, a second input signal comprising a

- battery voltage setting signal, said battery voltage setting signal being generated by said

- battery, and a third input signal comprising a voltage correction signal, said voltage

- 13 correction signal compensating for parasitic capacitance of said battery, wherein said

- summing block providing a weighted sum of said first, second and third input signals to

- 15 generate said battery voltage threshold signal.

- 16 9. A circuit as claimed in claim 1, further comprising an oscillator generating a fixed

- 17 frequency sawtooth signal, said comparator comparing said sawtooth signal and said

- amplitude of the charge on said charge capacitor and generating said PWM signal having a

- 19 duty cycle adjusted by said amplitude of the charge on said charge capacitor.

- 20 10. A circuit as claimed in claim 1, further comprising a Buck DC/DC converter circuit

- 21 coupled to a plurality of switches and a DC power source, said PWM signal controlling the

- 22 conduction states of said switches to control the duty cycle of said Buck converter to adjust

- 23 the amount of charging current delivered to said battery from said DC power source.

- 24 11. A circuit as claimed in claim 5, wherein said sense amplifier comprising an

- 25 operational amplifier coupled in parallel to a sense resistor, said operational amplifier sensing

- 26 the current through a sense resistor, said current through said sense resistor indicative of said

- 27 current supplied to said battery; a switch coupled between one input of said operational

- amplifier and ground, the conduction state of said switch being controlled by the output of

- 29 said operational amplifier; and first and second gain resistors placed between said sense

- 30 resistor and said one input of said operational amplifier, and between said switch and a

- 31 reference node, respectively; wherein said signal indicative said charging current supplied to

- 32 said battery being taken from a node between said second resistor and said switch.

33

1 12. A circuit as claimed in claim 2, wherein said active system comprising a portable

- 2 computer.

- 3 13. A circuit as claimed in claim 3, wherein said DC source comprises an AC/DC adapter.

- 4 14. A battery charging circuit, comprising:

- a current control circuit generating a current control signal proportional to the amount

- 6 battery charging current exceeds a predetermined battery charging current threshold;

- a voltage control circuit generating a voltage control signal to the amount battery

- 8 voltage exceeds a predetermined battery voltage threshold;

- 9 a DC/DC converter circuit generating said battery charging current from a DC source;

- a PWM signal generator circuit generating a PWM signal for controlling the duty

- 11 cycle of said DC/DC converter circuit, said PWM circuit comprising a comparator, an

- oscillator, a compensation capacitor and a current source charging said compensation

- 13 capacitor;

- said comparator generating said PWM signal based on the voltage on said

- 15 compensation capacitor; said current source and said current control signal and voltage

- 16 control signal summed together at a common node, said current control signal and/or said

- voltage control signal reducing the voltage on said compensation capacitor thereby reducing

- the duty cycle of said PWM signal and thereby reducing the current delivered by said DC/DC

- 19 converter circuit.

- 20 15. A circuit as claimed in claim 14, further comprising a power control section

- 21 generating a power control signal proportional to an amount of total current that is required

- by an active system and a battery charger; said current source and said current control signal

- 23 and voltage control signal and said power control signal summed together at said common

- 24 node, said current control signal and/or said voltage control signal and/or said power control

- 25 signal reducing the voltage on said compensation capacitor thereby reducing the duty cycle of

- 26 said PWM signal.

- 27 16. A circuit as claimed in claim 15, wherein said power control section comprises a

- 28 sense amplifier for sensing the total current generated by said source and generating a signal

- 29 indicative of said total current generated by DC source, and a transconductance amplifier

- 30 comparing said signal indicative of said total current generated by said source with a

- 31 predetermined power threshold signal.

- 32 17. A circuit as claimed in claim 16, wherein said power control signal has a nonzero

- 33 value if said signal indicative of said total current generated by said source exceeds said

- 34 power threshold signal.

1 18. A circuit as claimed in claim 14, wherein said current control section comprises a

- 2 sense amplifier for sensing charging current supplied to said battery and generating a signal

- 3 indicative of charging current supplied to said battery, and a transconductance amplifier

- 4 comparing said signal indicative of charging current supplied with a predetermined charging

- 5 current signal and generating said current control signal.

- 6 19. A circuit as claimed in claim 18, wherein said current control signal has a nonzero

- 7 value if said signal indicative of charging current supplied to said battery exceeds said

- 8 predetermined charging current signal.

- 9 20. A circuit as claimed in claim 14, wherein said voltage control section comprises a

- summing block generating a predetermined battery voltage signal, and a transconductance

- amplifier comparing said signal indicative of battery voltage with said predetermined signal

- and generating said voltage control signal.

- 13 21. A circuit as claimed in claim 20, wherein said summing block having a first input

- signal comprising a reference voltage signal, said reference signal being selected in

- accordance with a threshold voltage for said battery, a second input signal comprising a

- battery voltage setting signal, said battery voltage setting signal being generated by said

- battery, and a third input signal comprising a voltage correction signal, said voltage

- 18 correction signal compensating for parasitic capacitance of said battery, wherein said

- 19 summing block providing a weighted sum of said first, second and third input signals to

- 20 generate said battery voltage threshold signal.

- 21 22. A circuit as claimed in claim 14, further comprising an oscillator generating a fixed

- 22 frequency sawtooth signal, said comparator comparing said sawtooth signal and said

- 23 amplitude of the charge on said charge capacitor and generating said PWM signal having a

- 24 duty cycle adjusted by said amplitude of the charge on said charge capacitor.

- 25 23. A circuit as claimed in claim 14, wherein said DC/DC converter circuit comprises a

- 26 Buck DC/DC converter circuit coupled to a plurality of switches and a DC power source, said

- 27 PWM signal controlling the conduction states of said switches to control the duty cycle of

- 28 said Buck converter to adjust the amount of charging current delivered to said battery from

- 29 said DC power source.

- 30 24. A circuit as claimed in claim 18, wherein said sense amplifier comprising an

- 31 operational amplifier coupled in parallel to a sense resistor, said operational amplifier sensing

- 32 the current through a sense resistor, said current through said sense resistor indicative of said

- 33 current supplied to said battery; a switch coupled between one input of said operational

- 34 amplifier and ground, the conduction state of said switch being controlled by the output of

said operational amplifier; and first and second gain resistors placed between said sense

- 2 resistor and said one input of said operational amplifier, and between said switch and a

- 3 reference node, respectively; wherein said signal indicative said charging current supplied to

- 4 said battery being taken from a node between said second resistor and said switch.

- 5 25. A circuit as claimed in claim 18, wherein said circuit operates in voltage mode by

- 6 placing said sense resistor in parallel with said DC/DC converter for sensing said charging

- 7 current supplied to said battery.

- 8 26. A circuit as claimed in claim 14, wherein said DC/DC converter circuit comprises a

- 9 Buck converter comprising an inductor in parallel with a capacitor.

- 10 27. A circuit as claimed in claim 15, wherein said active system comprising a portable

- 11 computer.

- 12 28. A circuit as claimed in claim 14, wherein said DC source comprises an AC/DC

- 13 adapter.

FIG. 2

#### INTERNATIONAL SEARCH REPORT

International application No. PCT/US02/26333

| A. CLASSIFICATION OF SUBJECT MATTER  IPC(7) :H01M 10/46 US CL : 320/145 According to International Patent Classification (IPC) or to both national classification and IPC  B. FIELDS SEARCHED  Minimum documentation searched (classification system followed by classification symbols) U.S. : 320/128, 137, 139, 141, 145  Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched  Electronic data base consulted during the international search (name of data base and, where practicable, search terms used) |                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C. DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                 |

| Category* Citation of document, with indication, where a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | appropriate, of the relevant passages                                                                                                                                                                                                                                          | Relevant to claim No.                                                                                                                                                                                                           |

| A US 5,912,549 A (FARRINGTON (15.06.99)<br>SEE ABSTRACT AND FIGURE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ·                                                                                                                                                                                                                                                                              | 1-28                                                                                                                                                                                                                            |

| SEE ENTIRE DOCUMENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                 |

| Further documents are listed in the continuation of Box                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | C. See patent family annex.                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                 |

| * Special categories of cited documents:  "A" document defining the general state of the art which is not considered to be of particular relevance  "E" earlier document published on or after the international filing date  "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)  "O" document referring to an oral disclosure, use, exhibition or other means                                                                                                      | "X" document of particular relevance; the considered novel or cannot be considered when the document is taken alone "Y" document of particular relevance; the considered to involve an inventive combined with one or more other such being obvious to a person skilled in the | e claimed invention cannot be ered to involve an inventive step se claimed invention cannot be ered to involve an inventive step se claimed invention cannot be extep when the document is h documents, such combination he art |

| "P" document published prior to the international filing date but later than the priority date claimed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | de document member of the ballo parts.                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                 |

| Date of the actual completion of the international search  24 SEPTEMBER 2002                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Date of mailing of the international second                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                 |

| Name and mailing address of the ISA/US Commissioner of Patents and Trademarks Box PCT Washington, D.C. 20231 Facsimile No. (703) 305-3230  Form PCT/ISA/210 (second sheet) (July 1998)*                                                                                                                                                                                                                                                                                                                                                                                                  | Authorized officer  MICHAEL SHERRY  Telephone No. (703) 3                                                                                                                                                                                                                      | Deborah P. Vega<br>Paralegal Specialist<br>echnology Center 280                                                                                                                                                                 |