## (19)**日本国特許庁(JP)**

# (12)**公開特許公報(A)**

(11)公開番号 **特開2023-129959** (**P2023-129959A**)

(43)公開日 令和5年9月20日(2023.9.20)

| (51)国際特許分類            | FΙ                |       |   | テーマコード(参考) |

|-----------------------|-------------------|-------|---|------------|

| H 0 1 L 25/07 (2006.0 | <i>1)</i> H 0 1 L | 25/08 | E | 5 F 1 3 6  |

| H 0 1 L 25/04 (2023.0 | <i>1)</i> H 0 1 L | 25/04 | Z |            |

| H 0 1 L 23/36 (2006.0 | 1) H 0 1 L        | 23/36 | D |            |

#### 審査請求 未請求 請求項の数 10 OL (全11頁)

|                     | 番                                               | <b>省請</b> 水 木請氷 | 請氷頃の数 10 UL (全11貝)                        |

|---------------------|-------------------------------------------------|-----------------|-------------------------------------------|

| (21)出願番号<br>(22)出願日 | 特願2022-34338(P2022-34338)<br>令和4年3月7日(2022.3.7) | (71)出願人         | 318010018<br>キオクシア株式会社<br>東京都港区芝浦三丁目1番21号 |

|                     |                                                 | (74)代理人         | 110001092<br>弁理士法人サクラ国際特許事務所              |

|                     |                                                 | (72)発明者         | 板倉 悟<br>東京都港区芝浦三丁目1番21号 キオ<br>クシア株式会社内    |

|                     |                                                 | Fターム (参考        | 号) 5F136 BC03 FA16 FA82                   |

|                     |                                                 |                 |                                           |

|                     |                                                 |                 |                                           |

|                     |                                                 |                 |                                           |

## (54)【発明の名称】 半導体装置

### (57)【要約】

【課題】高い信頼性を有する半導体装置を提供する。

【解決手段】半導体装置は、表面を有する配線基板と、表面の上方に設けられ、第1の半導体チップを含むチップ積層体と、表面とチップ積層体との間に設けられた第2の半導体チップと、表面と第1の半導体チップとの間に設けられ、表面に沿って第2の半導体チップを連続的に囲み、シリコンの熱伝導率よりも高い熱伝導率を有する材料を含むスペーサと、チップ積層体を覆う絶縁封止層と、を具備する。

【選択図】図1

### 【特許請求の範囲】

#### 【請求項1】

表面を有する配線基板と、

前記表面の上方に設けられ、第1の半導体チップを含むチップ積層体と、

前記表面と前記チップ積層体との間に設けられた第2の半導体チップと、

前記表面と前記第1の半導体チップとの間に設けられ、前記表面に沿って前記第2の半導体チップを連続的に囲み、シリコンの熱伝導率よりも高い熱伝導率を有する材料を含むスペーサと、

前記チップ積層体を覆う絶縁封止層と、

を具備する、半導体装置。

【請求項2】

前記スペーサは、金属を含む、請求項1に記載の半導体装置。

【請求項3】

前記スペーサは、セラミックを含む、請求項1に記載の半導体装置。

【請求項4】

前記スペーサの表面は、導体である、請求項1ないし請求項3のいずれか一項に記載の半導体装置。

【請求項5】

前記スペーサは、前記配線基板に電気的に接続される、請求項4に記載の半導体装置。

【請求項6】

前記スペーサと前記配線基板とを電気的に接続するボンディングワイヤをさらに具備する、請求項5に記載の半導体装置。

【請求項7】

前記スペーサと前記配線基板とを電気的に接続するバンプをさらに具備する、請求項5に記載の半導体装置。

【請求項8】

前記スペーサは、接着層を介して前記表面に接合され、

前記スペーサは、前記接着層よりも薄い、請求項1ないし請求項7のいずれか一項に記載の半導体装置。

【請求項9】

前記スペーサは、前記表面上において前記スペーサの外側の第1の領域と前記スペーサの内側の第2の領域とを接続する通路を有し、

前記絶縁封止層は、前記通路内を延在するとともに前記第2の半導体チップを覆う、請求項1ないし請求項8のいずれか一項に記載の半導体装置。

【請求項10】

前記第1の半導体チップは、メモリチップであり、

前記第2の半導体チップは、メモリコントローラチップである、請求項1ないし請求項9のいずれか一項に記載の半導体装置。

【発明の詳細な説明】

【技術分野】

40

10

20

30

[0001]

本発明の実施形態は、半導体装置に関する。

【背景技術】

[0002]

NAND型フラッシュメモリ等の半導体装置は、配線基板上に積層された複数の半導体チップを具備する。

【先行技術文献】

【特許文献】

[0003]

【 特 許 文 献 1 】 米 国 特 許 出 願 公 開 第 2 0 1 9 / 0 2 8 7 9 4 5 号 明 細 書

【 特 許 文 献 2 】 米 国 特 許 出 願 公 開 第 2 0 1 9 / 0 1 9 8 4 5 2 号 明 細 書

【発明の概要】

【発明が解決しようとする課題】

[0004]

実施形態において解決しようとする課題の一つは、高い信頼性を有する半導体装置を提供することである。

【課題を解決するための手段】

[00005]

実施形態の半導体装置は、表面を有する配線基板と、表面の上方に設けられ、第1の半導体チップを含むチップ積層体と、表面とチップ積層体との間に設けられた第2の半導体チップと、表面と第1の半導体チップとの間に設けられ、表面に沿って第2の半導体チップを連続的に囲み、シリコンの熱伝導率よりも高い熱伝導率を有する材料を含むスペーサと、チップ積層体を覆う絶縁封止層と、を具備する。

【図面の簡単な説明】

[0006]

- 【図1】半導体装置の第1の構造例を示す平面模式図である。

- 【 図 2 】 半 導 体 装 置 の 第 1 の 構 造 例 を 説 明 す る た め の 断 面 模 式 図 で あ る 。

- 【図3】半導体装置の第1の構造例を説明するための断面模式図である。

- 【図4】半導体装置の第1の構造例を説明するための断面模式図である。

- 【図5】半導体装置の第1の構造例を説明するための断面模式図である。

- 【図6】半導体装置の第1の構造例を説明するための断面模式図である。

- 【図7】半導体装置の第1の構造例を説明するための断面模式図である。

- 【図8】半導体装置の第2の構造例を示す平面模式図である。

- 【図9】半導体装置の第2の構造例を説明するための断面模式図である。

- 【図10】半導体装置の第2の構造例を説明するための断面模式図である。

- 【図11】半導体装置の第2の構造例を説明するための断面模式図である。

- 【図12】半導体装置の第2の構造例を説明するための断面模式図である。

- 【図13】半導体装置の第3の構造例を示す平面模式図である。

- 【 図 1 4 】 半 導 体 装 置 の 第 3 の 構 造 例 を 説 明 す る た め の 断 面 模 式 図 で あ る 。

- 【図15】半導体装置の第3の構造例を説明するための断面模式図である。

【発明を実施するための形態】

[0007]

以下、実施形態について、図面を参照して説明する。図面に記載された各構成要素の厚さと平面寸法との関係、各構成要素の厚さの比率等は現物と異なる場合がある。また、実施形態において、実質的に同一の構成要素には同一の符号を付し適宜説明を省略する。

本明細書において「接続する」とは、特に指定する場合を除き、物理的に接続することだけでなく、電気的に接続することも含む。

[0009]

(半導体装置の第1の構造例)

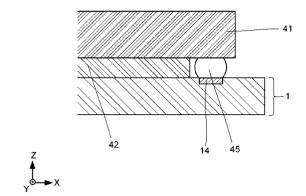

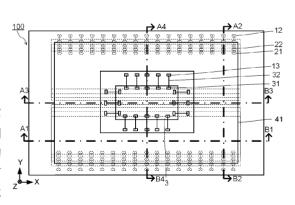

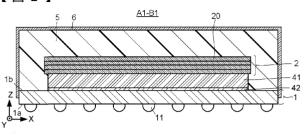

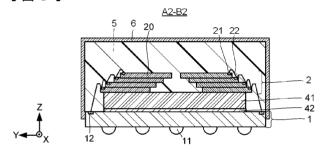

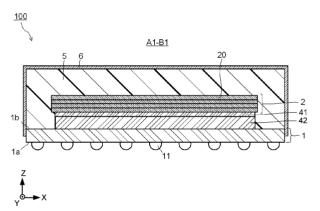

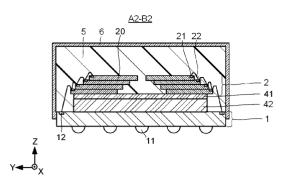

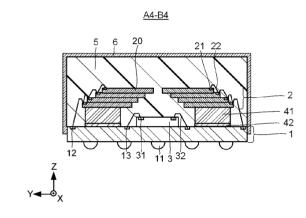

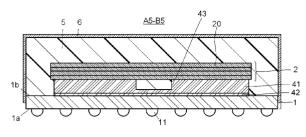

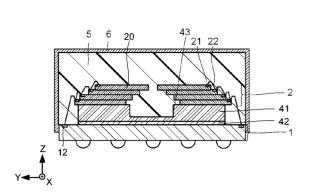

図1は、半導体装置の第1の構造例を示す平面模式図である。図2ないし図7は、半導体装置の第1の構造例を説明するための断面模式図である。図1ないし図7は、X軸と、X軸に垂直なY軸と、X軸およびY軸に垂直なZ軸と、を示す。なお、X軸は、例えば配線基板1の表面1bに平行な方向であり、Y軸は表面1bに平行であって且つX軸に垂直な方向であり、Z軸は、表面1bに垂直な方向である。図1は、X-Y平面の一例を示す。図1は、便宜のため、一部の構成要素を図示しないまたは点線で図示する。図2は、図1の線分A1-B1におけるX-Z断面の一例を示す。図3は、図1の線分A2-B2におけるY-Z断面の一例を示す。図5は、図1の線分A1-B1におけるX-Z断面の他の例を示す。図5は、図1の線分A3-B3におけるX-Z断面の一例を示す。図7は、図1の線分A4-B

30

10

20

40

4 における Y - Z 断面の一例を示す。

#### [0010]

半導体装置100は、配線基板1と、チップ積層体2と、半導体チップ3と、スペーサ41と、絶縁封止層5と、導電性シールド層6と、を具備する。

#### [0011]

配線基板1は、表面1 a に設けられた複数の外部接続端子1 1 と、表面1 a の反対側の表面1 b に設けられた複数のボンディングパッド1 2 と、複数のボンディングパッド1 3 と、を有する。配線基板1の例は、プリント配線板(PWB)を含む。

#### [0012]

外部接続端子11は、例えば金、銅、はんだ等を用いて形成される。外部接続端子11は、例えば、錫-銀系、錫-銀-銅系の鉛フリーはんだを用いて形成されてもよい。また、複数の金属材料の積層を用いて外部接続端子11を形成してもよい。なお、図1では、導電性ボールを用いて外部接続端子11を形成してもよい。

#### [0013]

ボンディングパッド12およびボンディングパッド13は、配線基板1の内部配線を介して複数の外部接続端子11に接続される。ボンディングパッド12およびボンディングパッド13は、例えば銅、銀、金、またはニッケル等の金属元素を含有する。例えば、電解めっき法または無電解めっき法等により上記材料を含むめっき膜を形成することによりボンディングパッド12およびボンディングパッド13を形成してもよい。また、導電性ペーストを用いてボンディングパッド12およびボンディングパッド13を形成してもよい。

### [0014]

チップ積層体2は、配線基板1の表面1bの上方に設けられる。チップ積層体2は、複数の半導体チップ20を含む。半導体チップ20の例は、メモリチップを含む。複数の半導体チップ20は、スペーサ41を介して配線基板1の表面1bの上方に順に積層される。チップ積層体2は、スペーサ41の上に互いに段々に積層された4つの半導体チップ20を含む第1のチップ積層体と、スペーサ41の上に互いに段々に積層された4つの半導体チップ20を含む第2のチップ積層体とを有する。互いに段々に積層された複数の半導体チップ20は、換言すると、互いに部分的に重畳する。なお、半導体チップ20の数および積層構造は、図1ないし図7に示す数および積層構造に限定されない。

#### [0015]

複数の半導体チップ20のそれぞれは、複数の接続パッド21を有する。各接続パッド21は、対応するボンディングワイヤ22を介して各ボンディングパッド12に接続される。ボンディングワイヤ22は、例えば金、銀、銅、アルミニウム等の金属元素を含有する。複数の半導体チップ20の一つと他の一つは、例えば接着層を介して接着される。最下段の半導体チップ20は、例えば接着層を介してスペーサ4に接着される。これらの接着層の例は、ダイアタッチフィルム(DAF)を含む。なお、図1は、便宜のため、ボンディングパッド12、半導体チップ20、接続パッド21、およびボンディングワイヤ22を点線で示す。

### [0016]

半導体チップ3は、図7に示すように、配線基板1とチップ積層体2との間に設けられる。半導体チップ3は、複数の接続パッド31を有する。図6および図7に示す半導体チップ3の接続パッド31は、ボンディングワイヤ32を介して配線基板1のボンディングパッド13に電気的に接続されているが、これに限定されず、配線基板1または半導体チップ3上に形成されたバンプを介して配線基板1と半導体チップ3とを接合するフリップチップボンディングを用いてもよい。

### [0017]

半導体チップ3の例は、メモリコントローラチップを含む。半導体チップ3は、配線基板1の表面1bに搭載され、配線基板1を介して半導体チップ20に電気的に接続される

20

10

30

10

20

30

40

50

。半導体チップ3は、接着層を介して表面1bに設けられていてもよい。半導体チップ20がメモリチップであり、半導体チップ3がメモリコントローラチップである場合、半導体チップ3は、例えば半導体チップ20に対するデータの書き込みおよびデータの読み出し等の動作を制御する。

#### [0018]

スペーサ41は、配線基板1とチップ積層体2との間に半導体チップ3を搭載するための空間を形成するために設けられる。これによりチップ積層体2の下方に半導体チップ3を搭載できるため、半導体装置のサイズを小さくできる。

#### [0019]

スペーサ41は、配線基板1と最下段の半導体チップ20との間に設けられる。スペーサ41は、図1に示すように、表面1bに沿って半導体チップ3を連続的に囲む。スペーサ41は、接着層42を介して配線基板1と接着される。接着層42の例は、ダイアタッチフィルムを含む。

#### [0020]

スペーサ41は、シリコンの熱伝導率よりも高い熱伝導率を有する材料を含有する。スペーサ41は、例えば銅等の金属を含有する。スペーサ41は、たとえば窒化アルミニウム等の熱伝導率が高いセラミックを含んでいてもよい。さらに、スペーサ41の熱伝導率がシリコンの熱伝導率よりも高ければスペーサ41がシリコンを含んでいてもよい。スペーサ41は、セラミック等の絶縁体からなる基体と、基体の表面にめっき処理により形成された金属等の導電膜と、を有していてもよい。スペーサ41の常温での熱伝導率は、例えば170W・m/K以上であることが好ましい。200W・m/K以上であればより好ましい。

#### [0021]

スペーサ41は、例えば予め所望の形状に加工された上記材料からなる部材を準備し、接着層42を介して当該部材を配線基板1に接着することにより形成できる。

### [0022]

図 2 および図 3 に示すスペーサ 4 1 は、接着層 4 2 よりも厚いが、これに限定されず、スペーサ 4 1 は、図 4 および図 5 に示すように、接着層 4 2 よりも薄くてもよい。スペーサ 4 1 を薄くすることにより、スペーサ 4 1 のコストを削減できる。

#### [ 0 0 2 3 ]

絶縁封止層 5 は、チップ積層体 2 および半導体チップ 3 を封止する。絶縁封止層 5 は、酸化シリコン(SiO2)等の無機充填材を含有し、例えば無機充填材を有機樹脂等と混合した封止樹脂を用いてトランスファモールド法、コンプレッションモールド法、インジェクションモールド法等のモールド法により形成される。なお、図 1 は、便宜のため、絶縁封止層 5 の図示を省略する。

### [0024]

導電性シールド層 6 は、例えば配線基板 1 の側面の少なくとも一部と絶縁封止層 5 とを覆う。導電性シールド層 6 は、絶縁封止層 5 内の半導体チップ 2 0 や配線基板 1 の配線層から放射される不要電磁波の漏洩を防止する上で、電気抵抗率が低い金属層で形成することが好ましく、例えば銅、銀、ニッケル等からなる金属層が適用される。導電性シールド層 6 の厚さは、その電気抵抗率に基づいて設定することが好ましい。なお、配線基板 1 内のビアの一部を露出させて導電性シールド層 6 と接触させることにより、グランド端子等の外部接続端子に接続された配線に導電性シールド層 6 を接続してもよい。なお、図 1 は、便宜のため、導電性シールド層 6 の図示を省略する。

#### [0025]

配線基板 1 とチップ積層体 2 との間にシリコンスペーサを形成する場合、シリコンスペーサは、半導体チップ 2 0 の基板の熱伝導率と同等の熱伝導率を有しているが、表面 1 b に沿って環状等の複雑な形状に加工することが困難である。このため、表面 1 b に沿って半導体チップ 3 を囲むようにシリコンスペーサを形成する場合、ダイボンダを用いて複数のシリコンスペーサを形成する必要がある。スペーサの構成部材の数が増加するほど加工

時間が長くなり、コストが増加する。

#### [0026]

これに対し、本実施形態の半導体装置では、シリコンよりも加工が容易な金属やセラミック等の材料を用いて配線基板 1 とチップ積層体 2 との間にスペーサを形成することにより、一つのスペーサだけで半導体チップ 3 を連続的に囲むことができる。よって、コストの増加を抑制できる。さらに、これらの材料は、シリコンよりも熱伝導率が高いため、スペーサの熱抵抗を低減できる。よって、半導体装置の放熱性を高めることができるため、半導体装置の信頼性を向上できる。

### [0027]

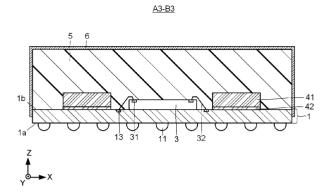

(半導体装置の第2の構造例)

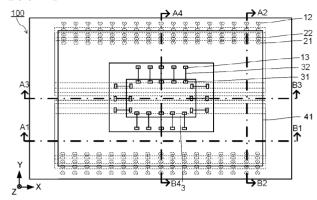

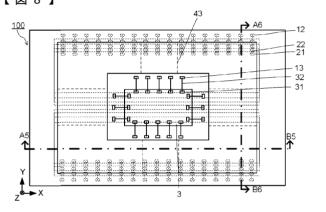

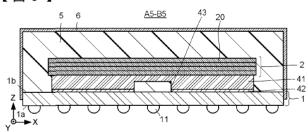

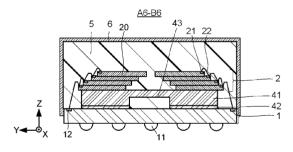

図8は、半導体装置の第2の構造例を示す平面模式図である。図9ないし図12は、半導体装置の第2の構造例を説明するための断面模式図である。図8ないし図12は、X軸と、X軸に垂直なY軸と、X軸およびY軸に垂直なZ軸と、を示す。図8は、X-Y平面の一例を示す。図8は、便宜のため、一部の構成要素を図示しないまたは点線で図示する。図9は、図8の線分A5-B5におけるX-Z断面の一例を示す。図10は、図8の線分A5-B5におけるX-Z断面の他の例を示す。図11は、図8の線分A5-B5におけるX-Z断面の他の例を示す。図12は、図8の線分A6-B6におけるY-Z断面の他の例を示す。

#### [0028]

半導体装置100は、配線基板1と、チップ積層体2と、半導体チップ3と、スペーサ41と、絶縁封止層5と、導電性シールド層6と、を具備する。なお、配線基板1、チップ積層体2、および導電性シールド層6については、半導体装置の第1の構造例と同じであるため、ここでは説明を省略し、第1の構造例の説明を適宜援用できる。

#### [0029]

スペーサ41は、凹部43を有する。凹部43は、表面1bにおけるスペーサ41の外側の領域とスペーサ41の内側の領域とを接続する通路を形成する。図8は、X軸方向に延在する2つの凹部43と、を図示するが、凹部43の数は図8に示す数に限定されない。さらに、図9および図10に示す凹部43は、配線基板1に面して設けられているが、これに限定されず、凹部43は、図11および図12に示すように最下段の半導体チップ20に面して設けられていてもよい。また、凹部43の形状は、スペーサ41の外側の領域とスペーサ41の内側の領域とを接続可能であれば特に限定されない。凹部43は、例えば予め所望の形状に加工されたスペーサ41を形成するための部材を準備する際に、該部材に形成される。スペーサ41のその他の説明は、第1の構造例におけるスペーサ41の説明と同じである。

### [ 0 0 3 0 ]

絶縁封止層 5 は、凹部 4 3 からなる通路内を延在するとともに半導体チップ 3 を覆う。 絶縁封止層 5 のその他の説明は、第 1 の構造例における絶縁封止層 5 と同じである。

#### [0031]

スペーサ 4 1 に凹部 4 3 を形成することにより、絶縁封止層 5 を形成する封止工程において、封止樹脂が凹部 4 3 を介して配線基板 1 とチップ積層体 2 との間の領域に流れやすくなるため、半導体チップ 3 を十分に封止することができ、ボイドの発生を抑制できる。よって、高い信頼性を有する半導体装置を提供できる。

#### [0032]

なお、半導体装置の第 2 の構造例は、半導体装置の他の構造例と適宜組み合わせることができる。

#### [0033]

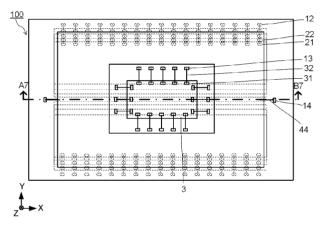

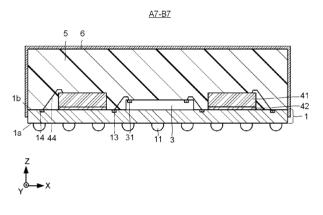

(半導体装置の第3の構造例)

図13は、半導体装置の第3の構造例を示す平面模式図である。図14および図15は、半導体装置の第3の構造例を説明するための断面模式図である。図13ないし図15は、X軸と、X軸に垂直なY軸に垂直なZ軸と、を示す。図13は、X

10

20

30

40

10

20

30

40

50

- Y 平面の一例を示す。図 1 3 は、便宜のため、一部の構成要素を図示しないまたは点線で図示する。図 1 4 は、図 1 3 の線分 A 7 - B 7 における X - Z 断面の一例を示す。図 1 5 は、図 1 3 の線分 A 7 - B 7 における X - Z 断面の他の例の一部を示す。

#### [0034]

半導体装置100は、配線基板1と、チップ積層体2と、半導体チップ3と、スペーサ41と、絶縁封止層5と、導電性シールド層6と、を具備する。なお、チップ積層体2、半導体チップ3、および導電性シールド層6については、半導体装置の第1の構造例と同じであるため、ここでは説明を省略し、第1の構造例の説明を適宜援用できる。

#### [0035]

配線基板1は、表面1bにボンディングパッド14をさらに具備する。ボンディングパッド14は、配線基板1の内部配線を介して複数の外部接続端子11に接続される。ボンディングパッド14は、例えばボンディングパッド12およびボンディングパッド13に適用可能な材料を含む。配線基板1のその他の説明は、第1の構造例における配線基板1と同じである。

#### [0036]

スペーサ41は、導体である表面を有し、配線基板1に電気的に接続される。図13および図14に示すスペーサ41は、ボンディングワイヤ44を介して配線基板1のボンディングパッド14に電気的に接続されているが、これに限定されず、スペーサ41は、図15に示すようにバンプ45を介して配線基板1のボンディングパッド14に電気的に接続されていてもよい。ボンディングパッド14は、例えば外部接続端子11のグランド端子に接続される。バンプ45は、スペーサ41の表面に形成される。スペーサ41の表面にかっき処理を施す場合、バンプ45は、めっき処理により形成された導電膜の表面に形成される。バンプ45の材料は、例えば外部接続端子11に適用可能な材料等が挙げられる。スペーサ41のその他の説明は、第1の構造例におけるスペーサ41と同じである。

#### [0037]

絶縁封止層 5 は、ボンディングワイヤ 4 4 またはバンプ 4 5 を覆うとともに半導体チップ 3 を覆う。絶縁封止層 5 のその他の説明は、第 1 の構造例における絶縁封止層 5 と同じである。

# [0038]

スペーサ41と配線基板1に電気的に接続することにより、スペーサ41を例えばグランド端子等の外部接続端子に接続することができる。これにより、スペーサ41を用いて電磁シールドを形成することができるため、絶縁封止層5内の半導体チップ20や配線基板1の配線層から放射される不要電磁波の漏洩を防止することができるため、高い信頼性を有する半導体装置を提供できる。なお、これに限定されず、スペーサ41はフローティング状態であってもよい。

### [0039]

なお、半導体装置の第3の構造例は、半導体装置の他の構造例と適宜組み合わせることができる。

### [0040]

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる

# 【符号の説明】

### [0041]

1 ... 配線基板、1 a ... 表面、1 b ... 表面、2 ... チップ積層体、3 ... 半導体チップ、4 ... スペーサ、5 ... 絶縁封止層、6 ... 導電性シールド層、1 1 ... 外部接続端子、1 2 ... ボンディングパッド、1 3 ... ボンディングパッド、1 4 ... ボンディングパッド、2 0 ... 半導体チ ップ、 2 1 … 接続パッド、 2 2 … ボンディングワイヤ、 3 1 … 接続パッド、 3 2 … ボンディングワイヤ、 4 1 … スペーサ、 4 2 … 接着層、 4 3 … 凹部、 4 4 … ボンディングワイヤ、 4 5 … バンプ、 1 0 0 … 半導体装置。

# 【図面】

# 【図1】

【図2】

10

# 【図3】

【図4】

30

20

# 【図5】

# 【図6】

【図7】

# 【図8】

【図9】

# 【図10】

40

10

20

# 【図11】

# 【図12】

<u>A6-B6</u>

# 【図13】

# 【図14】

30

10

20

# 【図15】