### (19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第6419029号 (P6419029)

(45) 発行日 平成30年11月7日(2018.11.7)

(24) 登録日 平成30年10月19日(2018.10.19)

| (51) Int.Cl. |               |           | FΙ   |       |   |

|--------------|---------------|-----------|------|-------|---|

| H04L         | <i>2</i> 5/02 | (2006.01) | HO4L | 25/02 | R |

| H04L         | <i>2</i> 5/03 | (2006.01) | HO4L | 25/03 | C |

| H04B         | 3/04          | (2006.01) | HO4B | 3/04  | A |

請求項の数 4 (全 9 頁)

| (21) 出願番号 | 特願2015-128718 (P2015-128718) | (73) 特許権者          | <b>š</b> 000006013 |  |  |

|-----------|------------------------------|--------------------|--------------------|--|--|

| (22) 出願日  | 平成27年6月26日 (2015.6.26)       |                    | 三菱電機株式会社           |  |  |

| (65) 公開番号 | 特開2017-17370 (P2017-17370A)  | 東京都千代田区丸の内二丁目7番3号  |                    |  |  |

| (43) 公開日  | 平成29年1月19日 (2017.1.19)       | (74) 代理人 100123434 |                    |  |  |

| 審査請求日     | 平成29年10月5日 (2017.10.5)       |                    | 弁理士 田澤 英昭          |  |  |

|           |                              | (74) 代理人           | 100101133          |  |  |

|           |                              |                    | 弁理士 濱田 初音          |  |  |

|           |                              | (74) 代理人           | 100199749          |  |  |

|           |                              |                    | 弁理士 中島 成           |  |  |

|           |                              | (74) 代理人           | 100156351          |  |  |

|           |                              |                    | 弁理士 河村 秀央          |  |  |

|           |                              | (74) 代理人           | 100188880          |  |  |

|           |                              |                    | 弁理士 坂元 辰哉          |  |  |

|           |                              | (74) 代理人           | 100197767          |  |  |

|           |                              | /                  | 弁理士 辻岡 将昭          |  |  |

|           |                              |                    | 最終頁に続く             |  |  |

# (54) 【発明の名称】信号受信装置

### (57)【特許請求の範囲】

# 【請求項1】

伝送ケーブルの先端に取り付けられているケーブル側コネクタと接続される基板側コネクタと、

一端が前記基板側コネクタの信号受信端子と接続されており、前記伝送ケーブルでの信号の損失を補償するイコライザ回路と、

前記イコライザ回路の他端と接続されており、前記伝送ケーブルにより伝搬された信号を受信する受信デバイスとを備え、

前記ケーブル側コネクタ及び前記基板側コネクタには、前記伝送ケーブルのケーブル長に対応する複数の識別用端子が用意されており、

前記複数の識別用端子の中で、前記伝送ケーブルのケーブル長を識別するための信号線が接続されている識別用端子を検出し、前記イコライザ回路の回路構成を前記検出した識別用端子に対応する回路構成に設定する回路構成設定回路を設けた信号受信装置であって

前記イコライザ回路が、

前記基板側コネクタの信号受信端子とグランドとの間に接続されている誘導性回路と、 前記基板側コネクタの信号受信端子と前記受信デバイスとの間に接続されている容量性 回路とから構成されており、

前記誘導性回路は、一端が前記基板側コネクタの信号受信端子と接続されている複数の 第1のスイッチと、一端が前記第1のスイッチの他端と接続されている複数の第1の抵抗

<u>素子と、一端が前記複数の第1の抵抗素子の他端と接続され、他端がグランドと接続され</u>ているインダクタ素子とから構成され、

前記容量性回路は、前記基板側コネクタの信号受信端子と前記受信デバイスとの間に接続されているキャパシタ素子と、一端が前記基板側コネクタの信号受信端子と接続されている複数の第2のスイッチと、一端が前記第2のスイッチの他端と接続され、他端が前記受信デバイスと接続されている複数の第2の抵抗素子とから構成されていることを特徴とする信号受信装置。

### 【請求項2】

前記回路構成設定回路は、

各々の識別用端子と前記イコライザ回路の回路構成との対応関係を記憶しており、

前記複数の識別用端子の中で、前記伝送ケーブルのケーブル長を識別するための信号線が接続されている識別用端子を検出すると、前記イコライザ回路の回路構成を前記検出した識別用端子に対応する回路構成に設定することを特徴とする請求項 1 記載の信号受信装置。

### 【請求項3】

前記回路構成設定回路は、

各々の識別用端子と前記第1及び第2のスイッチの開閉状態との対応関係を記憶しており、

前記複数の識別用端子の中で、前記伝送ケーブルのケーブル長を識別するための信号線が接続されている識別用端子を検出すると、前記第1及び第2のスイッチの開閉状態を前記検出した識別用端子に対応する開閉状態に設定することを特徴とする請求項<u>1</u>記載の信号受信装置。

### 【請求項4】

前記複数の第1の抵抗素子における各々の抵抗素子と、前記複数の第2の抵抗素子における各々の抵抗素子との間にペアが決められており、

前記回路構成設定回路は、ペアの抵抗素子のうち、一方の抵抗素子である第1の抵抗素子と接続されている第1のスイッチを閉状態に設定する際には、他方の抵抗素子である第2の抵抗素子と接続されている第2のスイッチを閉状態に設定し、一方の抵抗素子である第1の抵抗素子と接続されている第1のスイッチを開状態に設定する際には、他方の抵抗素子である第2の抵抗素子と接続されている第2のスイッチを開状態に設定することを特徴とする請求項1記載の信号受信装置。

【発明の詳細な説明】

# 【技術分野】

#### [0001]

この発明は、伝送ケーブルでの信号の高周波損失を補償して伝送波形を改善するイコライザ回路を備えている信号受信装置に関するものである。

# 【背景技術】

#### [0002]

伝送ケーブルを通して信号伝送を行う際、伝送ケーブルのケーブル長が長い場合、伝送ケーブルの周波数特性の影響によって、信号の低周波成分の減衰よりも、高周波成分の減衰が大きくなる。

これにより、信号受信端でのアイパターンの開口が狭くなる現象が発生し、信号に重畳されているデータを正しく認識できなくなる状況が発生することがある。

このような状況の発生を回避するために、伝送ケーブルと信号受信端との間にイコライザ回路を接続することで、伝送ケーブルでの信号の高周波損失を補償する技術が知られている。

イコライザ回路は、伝送ケーブルの周波数特性と相反する周波数特性を持たせた回路であり、イコライザ回路を接続することで、伝送ケーブル全体の周波数特性を平坦にすることができる。イコライザ回路は、一般的にインダクタ素子、キャパシタ素子及び抵抗素子で構成される。

10

20

30

- -

40

#### [0003]

ただし、伝送ケーブルに対して、適正なイコライザ回路を実現するには、伝送ケーブルの周波数特性を考慮しなければならない。

伝送ケーブルの周波数特性は、ケーブル長や材質等によって変化するため、以下の特許 文献 1 に開示されている信号受信装置では、インダクタ素子、キャパシタ素子及び抵抗素 子の値が異なる複数のイコライザ回路を用意しておき、複数のイコライザ回路の中から、 使用対象の伝送ケーブルに対応するイコライザ回路を選択するようにしている。

【先行技術文献】

【特許文献】

[0004]

【特許文献1】実開平5 43635号公報(図1)

【発明の概要】

【発明が解決しようとする課題】

[0005]

従来の信号受信装置は以上のように構成されているので、複数のイコライザ回路の中から、使用対象の伝送ケーブルに対応するイコライザ回路を選択することができるが、複数のイコライザ回路を用意するには、少なくとも、イコライザ回路の数分のインダクタ素子やキャパシタ素子を用意する必要がある。このため、回路の大型化や高コスト化を招いてしまうという課題があった。

[0006]

この発明に係る信号受信装置は、伝送ケーブルの先端に取り付けられているケーブル側 コネクタと接続される基板側コネクタと、一端が基板側コネクタの信号受信端子と接続さ れており、伝送ケーブルでの信号の損失を補償するイコライザ回路と、イコライザ回路の 他端と接続されており、伝送ケーブルにより伝搬された信号を受信する受信デバイスとを 備え、ケーブル側コネクタ及び基板側コネクタには、伝送ケーブルのケーブル長に対応す る複数の識別用端子が用意されており、回路構成設定回路が、複数の識別用端子の中で、 伝送ケーブルのケーブル長を識別するための信号線が接続されている識別用端子を検出し 、イコライザ回路の回路構成を、その検出した識別用端子に対応する回路構成に設定する ようにし、イコライザ回路は、基板側コネクタの信号受信端子とグランドとの間に接続さ れている誘導性回路と、基板側コネクタの信号受信端子と受信デバイスとの間に接続され ている容量性回路とから構成されており、誘導性回路は、一端が基板側コネクタの信号受 信端子と接続されている複数の第1のスイッチと、一端が第1のスイッチの他端と接続さ れている複数の第1の抵抗素子と、一端が複数の第1の抵抗素子の他端と接続され、他端 がグランドと接続されているインダクタ素子とから構成され、容量性回路は、基板側コネ クタの信号受信端子と受信デバイスとの間に接続されているキャパシタ素子と、一端が基 板側コネクタの信号受信端子と接続されている複数の第2のスイッチと、一端が第2のス イッチの他端と接続され、他端が受信デバイスと接続されている複数の第2の抵抗素子と から構成されている。

【課題を解決するための手段】

[0007]

この発明に係る信号受信装置は、伝送ケーブルの先端に取り付けられているケーブル側コネクタと接続される基板側コネクタと、一端が基板側コネクタの信号受信端子と接続されており、伝送ケーブルでの信号の損失を補償するイコライザ回路と、イコライザ回路の他端と接続されており、伝送ケーブルにより伝搬された信号を受信する受信デバイスとを備え、ケーブル側コネクタ及び基板側コネクタには、伝送ケーブルのケーブル長に対応する複数の識別用端子が用意されており、回路構成設定回路が、複数の識別用端子の中で、伝送ケーブルのケーブル長を識別するための信号線が接続されている識別用端子を検出し、イコライザ回路の回路構成を、その検出した識別用端子に対応する回路構成に設定するようにしたものである。

【発明の効果】

10

20

30

40

#### [ 0 0 0 8 ]

この発明によれば、回路構成設定回路が、複数の識別用端子の中で、伝送ケーブルのケーブル長を識別するための信号線が接続されている識別用端子を検出し、イコライザ回路の回路構成を、その検出した識別用端子に対応する回路構成に設定するように構成したので、インダクタ素子やキャパシタ素子の素子数を抑えて、回路の小型化や低コスト化を図ることができる効果がある。

【図面の簡単な説明】

# [0009]

【図1】この発明の実施の形態1による信号受信装置を示す構成図である。

【 図 2 】 伝送ケーブルのケーブル長 L <sub>1</sub> , L <sub>2</sub> と識別用端子 I D 1 , I D 2 の対応関係を示す説明図である。

【図3】識別用端子ID1,ID2とスイッチ31-1~31-N,42-1~42-Nの開閉状態(ON/OFFの状態)との対応関係を示す説明図である。

【発明を実施するための形態】

# [0010]

以下、この発明をより詳細に説明するために、この発明を実施するための形態について、添付の図面にしたがって説明する。

# [0011]

# 実施の形態1.

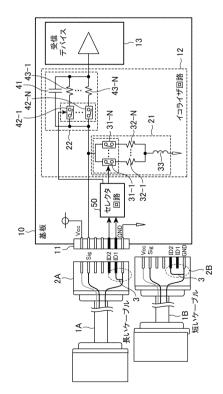

図1はこの発明の実施の形態1による信号受信装置を示す構成図である。

図 1 では、ケーブル長が長い伝送ケーブル 1 A、または、ケーブル長が短い伝送ケーブル 1 Bが、信号受信装置に接続される例を示している。

図 1 において、コネクタ 2 A は伝送ケーブル 1 A の先端に取り付けられているケーブル側コネクタであり、コネクタ 2 B は伝送ケーブル 1 B の先端に取り付けられているケーブル側コネクタである。

コネクタ 2 A , 2 B には、伝送ケーブル 1 A , 1 B によって伝搬される信号の信号受信端子 S i g のほか、伝送ケーブル 1 A , 1 B のケーブル長 L  $_1$  , L  $_2$  に対応する識別用端子 1 D 1 , 1 D 2 が用意されている。

# [0012]

識別用端子 ID1 は伝送ケーブル 1AO ケーブル長  $L_1$  に対応し、識別用端子 ID2 は伝送ケーブル 1BO ケーブル長  $L_2$  に対応している。  $L_1 > L_2$  である。

図 1 の例では、伝送ケーブル 1 A のケーブル長が  $L_1$  であるため、伝送ケーブル 1 A のケーブル長を識別するための信号線 3 が識別用端子 I D 1 に接続されている。また、伝送ケーブル 1 B のケーブル長が  $L_2$  であるため、伝送ケーブル 1 B のケーブル長を識別するための信号線 3 が識別用端子 I D 2 に接続されている。

#### [0013]

基板10は信号受信装置の基板であり、基板10には伝送ケーブル1Aのコネクタ2A 又は伝送ケーブル1Bのコネクタ2Bと接続される基板側コネクタであるコネクタ11が 設けられている。

コネクタ11にも、コネクタ2A,2Bと同様に、伝送ケーブル1A,1Bによって伝搬される信号の信号受信端子Sigのほか、伝送ケーブル1A,1Bのケーブル長L $_1$ ,L。に対応する識別用端子ID1,ID2が用意されている。

なお、コネクタ11の識別用端子ID1,ID2は、電源端子Vccによって5V程度の電圧が印加されているが、ケーブル長を識別するための信号線3が識別用端子ID1に接続されると、識別用端子ID1の電圧がグランド電位に低下し、ケーブル長を識別するための信号線3が識別用端子ID2に接続されると、識別用端子ID2の電圧がグランド電位に低下する。

### [0014]

イコライザ回路12はコネクタ11の信号受信端子Sigと受信デバイス13との間に接続され、伝送ケーブル1A又は伝送ケーブル1Bでの信号の高周波損失を補償する回路

20

10

30

40

であり、誘導性回路21と容量性回路22から構成されている。

受信デバイス13は伝送ケーブル1A又は伝送ケーブル1Bにより伝搬された信号を受信するデバイスである。

### [0015]

誘導性回路 2 1 はコネクタ 1 1 の信号受信端子 S i g とグランドとの間に接続されている。

誘導性回路 2 1 は、N個のスイッチ 3 1 - 1 ~ 3 1 - Nと、N個の抵抗素子 3 2 - 1 ~ 3 2 - Nと、インダクタ素子 3 3 とから構成されている。

スイッチ 3 1 - n (n = 1 , 2 , · · · · , N) は一端がコネクタ 1 1 の信号受信端子 S i g と接続されている第 1 のスイッチである。

抵抗素子 3 2 - n (n = 1 , 2 , · · · , N) は一端がスイッチ 3 1 - n の他端と接続されている第 1 の抵抗素子である。

インダクタ素子33は一端が抵抗素子32-1~32-Nの他端と接続され、他端がグランドと接続されているコイルである。

# [0016]

容量性回路22はコネクタ11の信号受信端子Sigと受信デバイス13との間に接続されている。図1の例では、コネクタ11の信号受信端子Sigに対する接続位置は、誘導性回路21よりも容量性回路22の方が受信デバイス13に近い側である。

容量性回路 2 2 は、キャパシタ素子 4 1 と、N個のスイッチ 4 2 - 1 ~ 4 2 - Nと、N個の抵抗素子 4 3 - 1 ~ 4 3 - Nとから構成されている。

キャパシタ素子41はコネクタ11の信号受信端子Sigと受信デバイス13との間に接続されているコンデンサである。

スイッチ  $4 \ 2 \ - \ n \ (n = 1 \ , 2 \ , \cdot \cdot \cdot \cdot , N \ )$  は一端がコネクタ  $1 \ 1 \ n$  信号受信端子 S i g と接続されている第  $2 \ n$  スイッチである。

抵抗素子 4 3 - n ( n = 1 , 2 ,  $\cdot \cdot \cdot \cdot$  , N ) は一端がスイッチ 4 2 - n の他端と接続され、他端が受信デバイス 1 3 と接続されている第 2 の抵抗素子である。

#### [0.017]

セレクタ回路 5 0 は伝送ケーブル 1 A , 1 B のケーブル長 L  $_1$  , L  $_2$  に対応する識別用端子 I D 1 , I D 2 の中で、伝送ケーブル 1 A , 1 B のケーブル長 L  $_1$  , L  $_2$  を識別するための信号線 3 が接続されている識別用端子 I D を検出し、イコライザ回路 1 2 の回路構成を、その検出した識別用端子 I D に対応する回路構成に設定する回路構成設定回路である。

即ち、セレクタ回路 5 0 は、識別用端子ID1,ID2とイコライザ回路12の回路構成との対応関係として、識別用端子ID1,ID2とスイッチ31-1~31-N,42-1~42-Nの開閉状態(ON/OFFの状態)との対応関係を記憶しており、識別用端子ID1,ID2の中で、信号線3が接続されている識別用端子IDを検出すると、スイッチ31-1~31-N,42-1~42-Nの開閉状態を信号線3が接続されている識別用端子IDに対応する開閉状態に設定する。

# [0018]

次に動作について説明する。

図 2 は伝送ケーブルのケーブル長  $L_1$  ,  $L_2$  と識別用端子 I D 1 , I D 2 の対応関係を示す説明図である。図 2 の例では、伝送ケーブル 1 A のケーブル長  $L_1$  が識別用端子 I D 1 に対応し、伝送ケーブル 1 B のケーブル長  $L_2$  が識別用端子 I D D D に対応している旨を示している。

# [0019]

図 3 は識別用端子 I D 1 , I D 2 とスイッチ 3 1 - 1 ~ 3 1 - N , 4 2 - 1 ~ 4 2 - N の開閉状態 (O N / O F F の状態) との対応関係を示す説明図である。

図3では、信号線3が識別用端子ID1に接続されている場合、スイッチ31-1,42-1がON(閉状態)で、スイッチ31-1,42-1以外のスイッチがOFF(開状態である例を示し、信号線3が識別用端子ID2に接続されている場合、スイッチ31-

10

20

30

40

N , 4 2 - NがO Nで、スイッチ 3 1 - N , 4 2 - N以外のスイッチがO F F である例を示しているが、これはあくまでも一例であり、スイッチ 3 1 - 1 ~ 3 1 - N , 4 2 - 1 ~ 4 2 - Nの開閉状態の組み合わせは、使用する可能性がある伝送ケーブルの周波数特性によって個別に決定される。

ただし、伝送ケーブルのケーブル長が長い程、インダクタ素子33と直列に接続される抵抗素子の抵抗値が小さくなって、キャパシタ素子41と並列に接続される抵抗素子の抵抗値が大きくなるように、スイッチ31-1~31-N,42-1~42-Nの開閉状態の組み合わせが決定される。

### [0020]

コネクタ11の識別用端子ID1,ID2には、電源端子Vccによって5V程度の電圧が印加されている。

例えば、伝送ケーブル1Aのコネクタ2Aが基板1のコネクタ11に接続された場合、 伝送ケーブル1Aのケーブル長を識別するための信号線3が、コネクタ11の識別用端子 ID1に接続される。このとき、この信号線3はグランドにも接続されるため、識別用端 子ID1の電圧がグランド電位に低下する。

一方、伝送ケーブル1Bのコネクタ2Bが基板1のコネクタ11に接続された場合、伝送ケーブル1Bのケーブル長を識別するための信号線3が、コネクタ11の識別用端子ID2に接続される。このとき、この信号線3はグランドにも接続されるため、識別用端子ID2の電圧がグランド電位に低下する。

セレクタ回路 5 0 は、グランド電位の識別用端子を検出することで、信号線 3 が識別用端子 I D 1 に接続されているのか、識別用端子 I D 2 に接続されているのかを検出する。

#### [0021]

セレクタ回路50は、信号線3が識別用端子ID1に接続されていることを検出すると、予め記憶している図3の対応関係を参照して、識別用端子ID1に対応するスイッチ31-1~31-N,42-1~42-Nの開閉状態を認識する。

セレクタ回路 5 0 は、識別用端子 I D 1 に対応するスイッチ 3 1 - 1 ~ 3 1 - N , 4 2 - 1 ~ 4 2 - Nの開閉状態を認識すると、スイッチ 3 1 - 1 ~ 3 1 - N , 4 2 - 1 ~ 4 2 - Nの開閉状態を識別用端子 I D 1 に対応するスイッチ 3 1 - 1 ~ 3 1 - N , 4 2 - 1 ~ 4 2 - Nの開閉状態に設定する。

これにより、イコライザ回路 1 2 の回路構成が、伝送ケーブル 1 A のケーブル長 L  $_1$  に対応する回路構成となる。即ち、イコライザ回路 1 2 の周波数特性が、伝送ケーブル 1 A の周波数特性と相反する周波数特性を持つ回路となる。

### [0022]

セレクタ回路50は、信号線3が識別用端子ID2に接続されていることを検出すると、予め記憶している図3の対応関係を参照して、識別用端子ID2に対応するスイッチ31-1~31-N,42-1~42-Nの開閉状態を認識する。

セレクタ回路 5 0 は、識別用端子 I D 2 に対応するスイッチ 3 1 - 1 ~ 3 1 - N , 4 2 - 1 ~ 4 2 - Nの開閉状態を認識すると、スイッチ 3 1 - 1 ~ 3 1 - N , 4 2 - 1 ~ 4 2 - Nの開閉状態を識別用端子 I D 2 に対応するスイッチ 3 1 - 1 ~ 3 1 - N , 4 2 - 1 ~ 4 2 - Nの開閉状態に設定する。

これにより、イコライザ回路 1 2 の回路構成が、伝送ケーブル 1 B のケーブル長 L  $_2$  に対応する回路構成となる。即ち、イコライザ回路 1 2 の周波数特性が、伝送ケーブル 1 B の周波数特性と相反する周波数特性を持つ回路となる。

# [0023]

伝送ケーブル1A又は伝送ケーブル1Bでの導体損失及び誘電体損失によって、伝送ケーブル1A又は伝送ケーブル1Bにより伝搬される信号の周波数が高周波になるほど信号の減衰が大きくなり、また、信号の伝搬距離が長くなるほど信号の減衰が大きくなり、信号の高周波成分が大きく減衰すると、上述したように、伝送波形に歪みが生じて、信号に重畳されているデータを正しく認識できなくなる。しかし、この実施の形態1では、イコライザ回路12の周波数特性が、伝送ケーブル1A又は伝送ケーブル1Bの周波数特性と

20

10

30

40

相反する周波数特性を持つ回路となることで、伝送波形の歪みを補償することができるので、信号に重畳されているデータを正しく認識できるようになる。

#### [0024]

以上で明らかなように、この実施の形態 1 によれば、セレクタ回路 5 0 が、識別用端子 ID1, ID2の中で、伝送ケーブル 1 A, 1Bのケーブル長  $L_1$ ,  $L_2$  を識別するための信号線 3 が接続されている識別用端子 ID を検出し、イコライザ回路 1 2 の回路構成を、信号線 3 が接続されている識別用端子 ID に対応する回路構成に設定するように構成したので、インダクタ素子やキャパシタ素子の素子数を抑えて、回路の小型化や低コスト化を図ることができる効果を奏する。

即ち、この実施の形態 1 によれば、使用する可能性がある伝送ケーブルの数が増えれば、その数分だけ抵抗素子 3 2 , 4 3 の数を増やす必要があるが、インダクタ素子 3 3 やキャパシタ素子 4 1 の素子数は 1 個のままで足りるため、インダクタ素子やキャパシタ素子の素子数を抑えることができる。

# [0025]

この実施の形態 1 では、セレクタ回路 5 0 が、信号線 3 が接続されている識別用端子 I D を検出すると、予め記憶している図 3 の対応関係を参照して、その検出した識別用端子 I D に対応するスイッチ 3 1 - 1 ~ 3 1 - N , 4 2 - 1 ~ 4 2 - Nの開閉状態を認識する例を示しているが、セレクタ回路 5 0 が、図 3 の対応関係を特に記憶せずに、信号線 3 が接続されている識別用端子 I D に対応するスイッチ 3 1 - 1 ~ 3 1 - N , 4 2 - 1 ~ 4 2 - N の開閉状態が一意的に決まる論理回路が形成されているようにしてもよい。

#### [0026]

この実施の形態 1 では、使用する可能性がある伝送ケーブルが、伝送ケーブル 1 A , 1 B の 2 本である例を示しているが、使用する可能性がある伝送ケーブルが 3 本以上であってもよいことは言うまでもない。

使用する可能性がある伝送ケーブルが3本以上である場合、コネクタ2A,2B,11 に用意する識別用端子IDを3個以上にすればよい。

### [0027]

#### 実施の形態2.

上記実施の形態 1 では、誘導性回路 2 1 が N 個の抵抗素子 3 2 - 1 ~ 3 2 - Nを備え、容量性回路 2 2 が N 個の抵抗素子 4 3 - 1 ~ 4 3 - Nを備えているものを示しているが、例えば、抵抗素子 3 2 - n と抵抗素子 4 3 - n をペアの抵抗素子としてもよい。即ち、抵抗素子 3 2 - 1 と抵抗素子 4 3 - 1 をペアの抵抗素子、抵抗素子 3 2 - 2 と抵抗素子 4 3 - Nをペアの抵抗素子としてもよい。

# [0028]

この場合、ペアの抵抗素子のうち、一方の抵抗素子である抵抗素子32-nと接続されているスイッチ31-nをONに設定する際には、他方の抵抗素子である抵抗素子43-nと接続されているスイッチ42-nをONに設定し、一方の抵抗素子である抵抗素子32-nと接続されているスイッチ31-nをOFFに設定する際には、他方の抵抗素子である抵抗素子である抵抗素子である抵抗素子43-nと接続されているスイッチ42-nをOFFに設定するように、スイッチ31-1~31-N,42-1~42-Nの開閉状態の組み合わせを決定するようにしてもよい。

スイッチ 3 1 - 1 ~ 3 1 - N , 4 2 - 1 ~ 4 2 - Nの開閉状態の組み合わせが上記のように決定されている場合、セレクタ回路 5 0 は、ペアの抵抗素子を常に同じ状態に設定することになるので、簡易な制御回路でセレクタ回路 5 0 を構築することができるようになる。

また、スイッチ31-1~31-N,42-1~42-Nの開閉状態の組み合わせが上記のように決定されている場合、抵抗素子32-nと抵抗素子43-nを1つの抵抗素子にまとめることできる。このため、スイッチ31-1~31-Nの系統、または、スイッチ42-1~42-Nの系統だけで、上記1つの抵抗素子の抵抗値を設定することが可能

10

20

30

40

になるため、スイッチの数を半分に削減することができる。

### [0029]

なお、本願発明はその発明の範囲内において、各実施の形態の自由な組み合わせ、あるいは各実施の形態の任意の構成要素の変形、もしくは各実施の形態において任意の構成要素の省略が可能である。

# 【符号の説明】

# [0030]

1 A , 1 B 伝送ケーブル、2 A , 2 B コネクタ(ケーブル側コネクタ)、3 信号線、1 0 基板、1 1 コネクタ(基板側コネクタ)、1 2 イコライザ回路、1 3 受信デバイス、2 1 誘導性回路、2 2 容量性回路、3 1 - 1 ~ 3 1 - N スイッチ(第1のスイッチ)、3 2 - 1 ~ 3 2 - N 抵抗素子(第1の抵抗素子)、3 3 インダクタ素子、4 1 キャパシタ素子、4 2 - 1 ~ 4 2 - N スイッチ(第2のスイッチ)、4 3 - 1 ~ 4 3 - N 抵抗素子(第2の抵抗素子)、5 0 セレクタ回路(回路構成設定回路)。

# 【図1】

# 【図2】

| ケーブル長          | 識別用端子 |  |  |

|----------------|-------|--|--|

| L <sub>1</sub> | ID1   |  |  |

| L <sub>2</sub> | ID2   |  |  |

# 【図3】

| 識別用端子 | スイッチ31-1 | <br>スイッチ31-N | スイッチ42-1 | <br>スイッチ42-N |

|-------|----------|--------------|----------|--------------|

| ID1   | ON       | OFF          | ON       | OFF          |

| ID2   | OFF      | ON           | OFF      | ON           |

# フロントページの続き

(72)発明者 岡南 佑紀

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

(72)発明者 明星 慶洋

東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内

審査官 川口 貴裕

(56)参考文献 特開平10-079874 (JP,A)

特開平06-326916(JP,A)

特表2012-509607(JP,A)

特表2001-519107(JP,A)

(58)調査した分野(Int.CI., DB名)

H04L 25/02

H 0 4 L 2 5 / 0 3

H04B 3/04