#### INSTITUT NATIONAL DE LA PROPRIÉTÉ INDUSTRIELLE

**PARIS**

11) N° de publication :

*2 674 653*

(à n'utiliser que pour les commandes de reproduction)

21) N° d'enregistrement national :

91 11262

(51) Int Cl<sup>5</sup> : G 06 F 15/70; H 04 N 3/00

# (12)

## **DEMANDE DE BREVET D'INVENTION**

**A1**

- (22) Date de dépôt : 12.09.91.

- (30) **Priorité**: 28.03.91 KR 9104871.

- (71) Demandeur(s): SAMSUNG ELECTRONICS CO., LTD — KR.

- 43 Date de la mise à disposition du public de la demande : 02.10.92 Bulletin 92/40.

- 56 Liste des documents cités dans le rapport de recherche : Le rapport de recherche n'a pas été établi à la date de publication de la demande.

- 60 Références à d'autres documents nationaux apparentés :

- 72 Inventeur(s): Paik Joon-ki, Park Yong-chul et Myung Chan-kyu.

- 73) Titulaire(s) :

- 74 Mandataire : Cabinet Nony & Cie.

- 54 Procédé et dispositif de détection de bord pour un système de traitement d'image.

- Dispositif et procédé de détection de bord pour un système de traitement d'image. Le dispositif comporte un moyen de conversion pour convertir les données d'élément d'image d'entrée en valeurs à états multiples, un moyen de concordance pour effectuer le produit scalaire des valeurs à états multiples et des valeurs préalablement spécifiées, et un moyen de décision pour prendre une décision selon le résultat du produit scalaire. Le dispositif peut éliminer le bruit sans filtres passe-bas supplémentaire. Par conséquent, il simplifie la circuiterie et peut effectuer le processus en temps réel.

FR 2 674 653 - A1

# Procédé et dispositif de détection de bord pour un système de traitement d'image.

La présente invention a trait à un système de traitement d'image et plus particulièrement à un procédé et à un dispositif de détection de bord d'un système de traitement d'image utilisant des éléments logiques à seuil linéaires à états multiples.

5

10

15

Dans un système de traitement de signaux d'image, qui est l'un des domaines d'application les plus importants de la présente invention, un prétraitement est recommandé du fait qu'il peut améliorer la précision de détection de vecteurs de mouvement en éliminant des facteurs indésirables dans l'image tels qu'un bruit. Un prétraitement peut également réduire la charge de calcul en établissant une correspondance entre une image à résolution complète, habituellement représentée par 8 bits par élément d'image, et une image de type différent représentée par moins de 8 bits par élément d'image.

Plusieurs types de prétraitement ont été proposés dans le but précité. Par exemple, le Procédé Band Extract 20 Representative Point (BERP) a été utilisé par Uomori et al dans "Automatic Image Stabilizing System by Full-Digital Signal Processing", dans IEEE Transactions on Consumer Electronics Vol. 36, N°3, (pages 510-519) publié en Août 1990, qui peut être considéré comme étant une sorte de 25 procédé de filtrage à bande passante. Bien que le procédé BERP peut efficacement filtrer à la fois les composantes de fréquence spatiale extrêmement élevée telles qu'un bruit et la composante à basse fréquence telle que la zone plane en intensité, il nécessite cependant plus de 2 bits par 30 élément d'image pour représenter l'image BERP. Cependant, l'information de bord détectée peut être représentée par l bit par élément d'image. Par conséquent, le procédé de

détection de bord peut simplifier l'équipement. Il existe différentes approches pour une détection de bord telles que : (i) l'utilisation de gradients spatiaux d'image, (ii) l'utilisation du Laplacien, (iii) l'utilisation de différences de moyennes, (iv) concordance ou ajustement à une 5 configuration préalablement spécifiée, et (v) la détection de passages par zéro filtrés par le Laplacien du Gaussien (LOG) dans l'image. Les deux inconvénients majeurs des détecteurs de bord énumérés en (i)-(iv) sont qu'ils fonctionnent bien uniquement avec certaines images, mais une per-10 formance de la détection de bord est sérieusement dégradée lorsque du bruit est présent du fait qu'ils détectent une composante à fréquence élevée dans le signal d'image. D'autre part, l'approche (v) présente l'effet de la réduction de bruit, mais présente l'inconvénient potentiel que 15 la quantité de calcul augmente considérablement pour éliminer une grande quantité de bruit. C'est-à-dire que l'approche (v) exige le filtrage passe-bas plus important pour détecter un bord complètement du fait qu'un bruit et qu'une information de bord sont situées dans une région de fré-20 quence élevée différente: Par conséquent, la fenêtre doit devenir encore plus grande pour une détection de bord.

Par conséquent, la présente invention a pour objet de proposer un procédé de détection de bord pouvant réduire le bruit sans accroître la taille de la fenêtre.

25

Un autre but de la présente invention est de proposer un dispositif de détection de bord pouvant simplifier la réalisation de l'équipement et opérer en temps réel.

Afin d'atteindre le premier but, un procédé de détection de bord de la présente invention comporte les étapes consistant à :

convertir les données d'élément d'image d'entrée en un ensemble de valeurs à états multiples ;

effectuer le produit scalaire dudit ensemble de valeurs à états multiples et d'un ensemble de valeurs préalablement spécifiées ; et

5

10

15

20

30

prendre une décision selon le résultat dudit produit scalaire.

Afin d'atteindre le second but, un dispositif de détection de bord de la présente invention comporte :

un moyen de conversion afin de convertir les données d'élément d'image d'entrée en valeurs à états multiples ;

un moyen de concordance afin d'effectuer le produit scalaire desdites valeurs à états multiples et de valeurs préalablement spécifiées ; et

un moyen de décision afin de prendre une décision selon le résultat dudit produit scalaire.

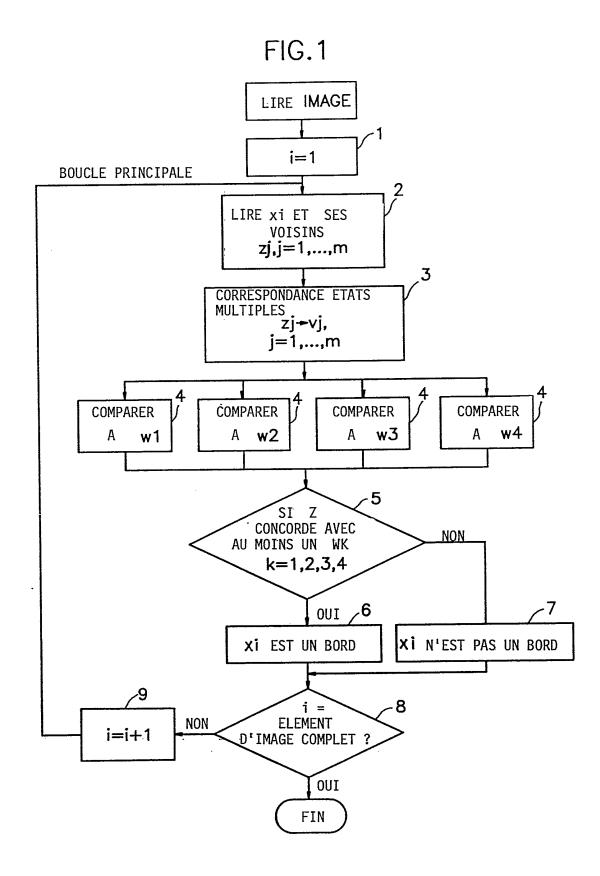

La Figure l est un organigramme qui représente la circulation de signaux d'un dispositif de détection de bord d'un système de traitement d'image selon la présente invention.

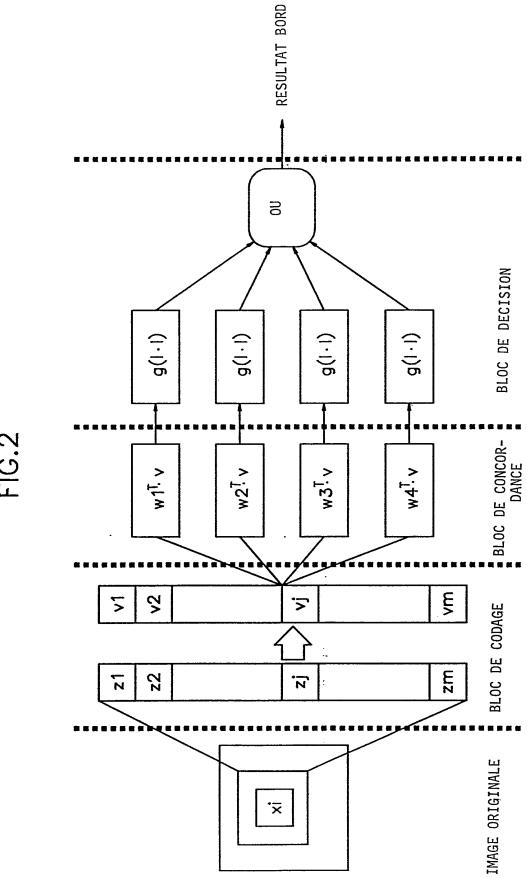

La Figure 2 est un schéma synoptique représentant le dispositif de détection de bord selon la présente invention.

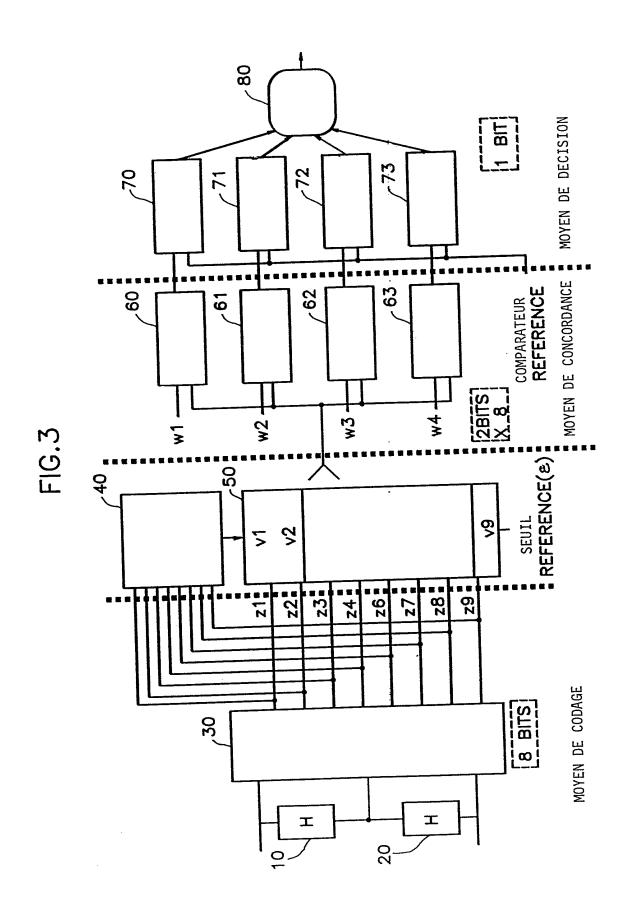

La Figure 3 est un schéma synoptique représentant un mode de réalisation préféré du didpositif de détection de bord selon la présente invention.

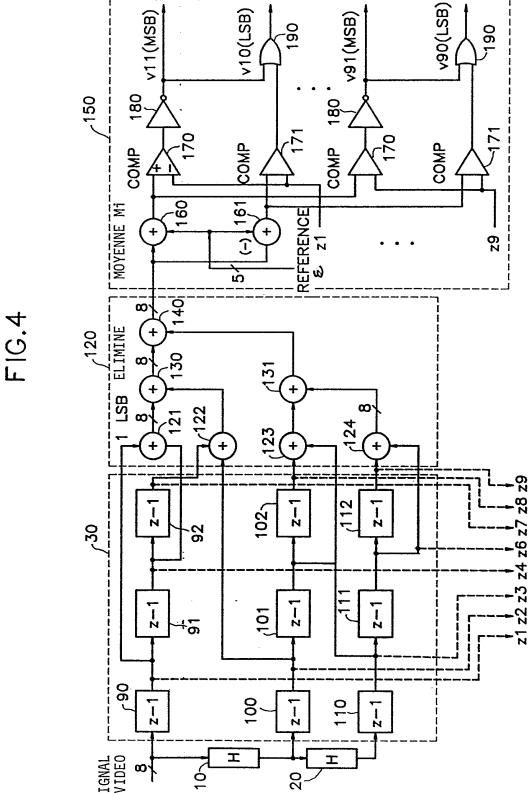

La Figure 4 est un schéma synoptique représentant un circuit de codage du dispositif de détection de bord selon la présente invention. La Figure 5 représente des configurations de bord préalablement spécifiées utilisées pour le produit scalaire de la présente invention.

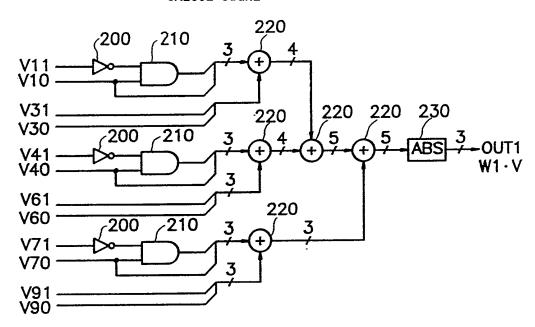

La Figure 6A représente un circuit afin d'effectuer le produit scalaire W<sub>1</sub>.V d'un organe de concordance du dispositif de détection de bord selon la présente invention.

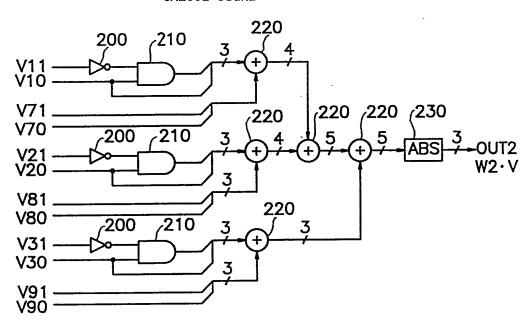

La Figure 6B représente un circuit afin d'effectuer le produit scalaire W<sub>2</sub>.V du moyen de concordance du 10 dispositif de détection de bord selon la présente invention.

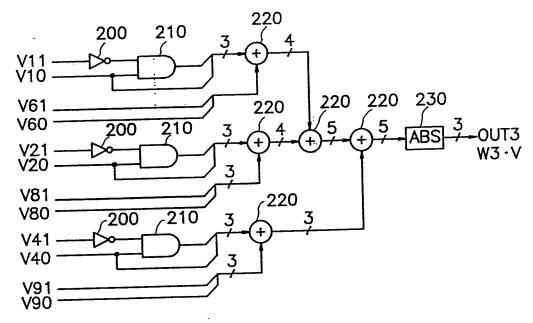

La Figure 6C représente un circuit afin d'effectuer le produit scalaire  $W_3$ . V du moyen de concordance du dispositif de détection de bord selon la présente invention.

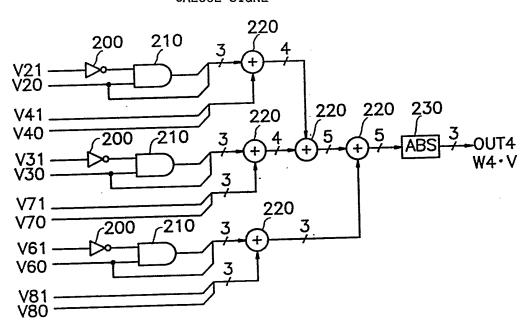

La Figure 6D représente un circuit afin d'effec-15 tuer le produit scalaire W<sub>4</sub>.V du moyen de concordance du dispositif de détection de bord selon la présente invention.

La Figure 7 est une table de vérité pour le résultat du produit scalaire de W et de V du dispositif de détection de bord selon la présente invention.

La Figure 8 représente une carte de Karnaugh et l'équation caractéristique afin d'obtenir le produit scalaire dans le dispositif de détection de bord selon la présente invention.

La Figure 9 est un schéma de circuit logique du 25 circuit de valeur absolue du moyen de concordance du dispositif de détection de bord selon la présente invention.

La Figure 10 est un schéma de circuit logique

du circuit de décision du dispositif de détection de bord selon la présente invention.

La Figure 11 est un diagramme temporel afin d'expliquer le fonctionnement du dispositif de détection de bord selon la présente invention.

La présente invention est basée sur la possibilité de séparation linéaire d'une logique à seuil linéaire à états multiples qui peut être expliquée par les définition et théorème suivants. La possibilité de séparation linéaire de signaux d'entrée binaires a été expliquée dans P.M Lewis II et C.L. Coates, Logique à Seuil, John Wiley and Sons, 1967. La définition d'une fonction linéairement séparable d'une entrée à états multiples est tout d'abord donnée ici.

Soit P un ensemble de vecteurs à L dimensions.

15 Chaque composante d'un vecteur quelconque dans P prend l'une de M=j+k+l valeurs dans {-j..., -l, 0, l, ..., k}, c'est-à-dire,

$$P = \{x | x_i \in \{-j, ..., -1, 0, 1, ..., k\}, i=1, ..., L\}$$

Le nombre de vecteurs différents dans P devient  $^{L} \text{ et nous appellerons -j et k les valeurs extrêmes de } \\ \text{l'état d'entrée. Soit P}_{0} \text{ et P}_{1} \text{ deux sous-ensembles mutuel-lement exclusifs de P tels P}_{0} \text{ U P}_{1} = \text{P.}$

Etant donné le vecteur poids W, une fonction logique F définie par

25

$$F(X) = \begin{bmatrix} 1, & w^{T}X \geqslant \theta \\ 0, & w^{T}X < \theta, \end{bmatrix}$$

5

10

dans laquelle  $\theta$  est une valeur de seuil, est de la classe

linéairement séparable si et seulement si

5

15

$$\mathbf{W}^{\mathrm{T}}\mathbf{X} > \mathbf{W}^{\mathrm{T}}\mathbf{Y}$$

,  $\forall \mathbf{X} \in \mathbf{P}_{1}$ , et  $\forall \mathbf{Y} \in \mathbf{P}_{0}$ .

L'analyse de la possibilité de séparation linéaire à états multiples est en général une tâche compliquée. Cependant, une classe particulière de fonctions logiques, qui seront utilisées dans le détecteur de bord proposé, peuvent être montrées comme étant linéairement séparables, selon le théorème suivant.

Soit X un vecteur d'entrée à L dimensions dont les composantes sont toutes des valeurs extrêmes et soit  $P_1 = \{X\}$  et  $P_0 = P - \{X\}$ , c'est-à-dire,

$$P_1 = \{ X | X_i \in \{-j, k\}, i=1,..., L \} \text{ et } P_0 = P - P_1, \text{ dans}$$

laquelle P, -j et k sont donnés dans la définition qui précède. Il existe alors une fonction linéairement séparable F qui sépare le vecteur d'entrée X d'autres.

La démonstration du théorème ci-dessus est la suivante. On démontrera ce théorème en utilisant la définition qui précède et en montrant qu'il existe un vecteur poids W qui satisfait

$$\mathbf{w}^{\mathrm{T}}\mathbf{x} > \mathbf{w}^{\mathrm{T}}\mathbf{y}$$

,  $\forall \mathbf{x} \in \mathbf{P}_{1}$  et  $\forall \mathbf{y} \in \mathbf{P}_{0}$ .

Considérons le vecteur poids suivant

$$W_{i} = \begin{bmatrix} 1, & X_{i} = k, \\ -1, & X_{i} = -j, \end{bmatrix}$$

$i = 1, ..., L.$

On obtient alors l'inégalité suivante

$$w_i x_i \geqslant w_i Y_i$$

,  $\forall i$ .

En sommant ces inégalités pour i = 1, ..., L , on obtient

$$w^Tx > w^Ty$$

.

du fait que pour au moins un i, l'égalité n'est pas obtenue.

On peut également considérer un ensemble P<sub>-1</sub> {-X},

5 dans lequel X et W sont définis dans l'équation précédente

respectivement. On obtient alors une sorte de fonction

discriminante de catégories multiples d'entrées à états

multiples telle que

$$w^{T}(-x) < w^{T}x < w^{T}x$$

,  $\forall y \in P_{0}$ .

Afin d'utiliser la logique à seuil linéaire à états multiples pour une détection de bord, on tracera la valeur d'intensité continue d'un élément d'image pour plusieurs états discrets.

Utilisons une fenêtre locale l x l pour détecter

un bord en un emplacement donné d'élément d'image. On suppose que la dimension de l'image est n = n<sub>1</sub> x n<sub>2</sub>. Soit

X<sub>i</sub>, i = l, ..., r, la i-ème valeur d'élément d'image dans

l'image lexicographiquement ordonnée et Z<sub>j</sub>, j = l,..., r,

la j-ème valeur d'élément d'image dans les valeurs d'élément d'image lexicographiquement ordonnées à l'intérieur

de la fenêtre locale centrée par X<sub>i</sub>, où r = l x l. Alors

pour la fenêtre locale correspondant à X<sub>i</sub>, Z<sub>j</sub> peut être

obtenue par la correspondance

$$z_j = x_k$$

,  $j=1$  , ...,  $r$

25 où

$$K = i + \left\{ \lfloor (j-1)/1 \rfloor - \lfloor 1/2 \rfloor \right\} \quad n_2 + \left\{ (j-1) \mod 1 - \lfloor 1/2 \rfloor \right\}.$$

La notation [1/2] désigne la part entière de la division résultante, et i mod l est égal à la valeur du reste de la division de l'entier i par l'entier l.

Après obtention du réseau dimensionnel Z<sub>j</sub>, la moyenne locale correspondant au i-ème élément d'image est égale à

$$M_{i} = \frac{1}{r} \sum_{j=1}^{r} Z_{j}$$

.

Alors, l'état pour la j-ème entrée à la logique à seuil linéaire à états multiples, V<sub>j</sub>,est défini par

$$v_{j} = \begin{bmatrix} -1 & z_{j} < M_{i} - \varepsilon \\ 0 & M_{i} - \varepsilon \leqslant z_{j} \leqslant M_{i} + \varepsilon \\ 1 & z_{j} > M_{i} + \varepsilon \end{bmatrix}$$

15

où & est la sécurité contre des données de bruit. Plus la quantité de bruit à supprimer est élevée, plus & doit être grand.

Nous définissons quatre paires de bords bidirectionnels dont les directions sont 0 et 180, 90 et 270, 45 et 225 et 135 et 315 degrés, respectivement.

Tout d'abord, un bord droit est défini par des 20 états d'entrée ascendants de la droite vers la gauche dans la fenêtre locale. Pour l = 3, par exemple, le bord droit et sa contrepartie bidirectionnelle, le bord gauche, sont respectivement donnés par

$$\begin{bmatrix} 1 \times -1 \\ 1 \times -1 \\ 1 \times -1 \end{bmatrix} \qquad \text{et} \qquad \begin{bmatrix} -1 \times 1 \\ -1 \times 1 \\ -1 \times 1 \end{bmatrix}$$

où x représente l'état indifférent.

La seconde paire de bords désignés par les bords supérieur et inférieur sont définis de la même manière, c'est-à-dire

$$\begin{bmatrix} -1 & -1 & -1 \\ x & x & x \\ 1 & 1 & 1 \end{bmatrix} \qquad \text{et} \qquad \begin{bmatrix} 1 & 1 & 1 \\ x & x & x \\ -1 & -1 & -1 \end{bmatrix}$$

La troisième paire de bords désignés par les bords supérieur droit et inférieur gauche sont donnés par

10

$$\begin{bmatrix} x & -1 & -1 \\ 1 & x & -1 \\ 1 & 1 & x \end{bmatrix}$$

et

$$\begin{bmatrix} x & 1 & 1 \\ -1 & x & 1 \\ -1 & -1 & x \end{bmatrix}$$

Enfin, la quatrième paire de bords désignés par les bords supérieur gauche et inférieur droit sont donnés par

15

$$\begin{bmatrix} -1 & -1 & x \\ -1 & x & 1 \\ x & 1 & 1 \end{bmatrix}$$

et

$$\begin{bmatrix} 1 & 1 & x \\ 1 & x & -1 \\ x & -1 & -1 \end{bmatrix}$$

Pour 1 = 5, le bord droit, par exemple, possède l dans la première colonne, -l dans la dernière colonne 20 et x (état indifférent) dans les autres colonnes.

En utilisant la fonction discriminante à catégories multiples présentée ci-dessus  $(W^T(-x) \not\subset W^T Y \not\subset W^T X)$ ,  $\forall \ Y \in P_0$ , à la fois les bords droit et gauche peuvent être détectés par le même vecteur poids désigné par  $W_-$ , du fait qu'ils sont constitués par des valeurs extrêmes et que le bord gauche est égal au bord droit avec inversion de signe. De la même manière, les bords supérieur et inférieur, les bords supérieur droit et inférieur gauche, et les bords supérieur gauche et inférieur droit

25

sont détectés par  $W_1$ ,  $W_2$ , et  $W_3$ , respectivement. Comme représenté par le théorème décrit ci-dessus, un vecteur poids possible pour détecter le bord droit ou le bord gauche, par exemple pour 1=3, est égal à

$$W_{-} = [1 \times -1 1 \times -1 1 \times -1]^{T} .$$

En clair, en fonction de cette équation, le reste des vecteurs poids, c'est-à-dire,  $W_i$ ,  $W_j$ , et  $W_k$  peuvent être obtenus par disposition appropriée des éléments de  $W_k$ .

En variante , l'algorithme LMS peut également 10 être utilisé pour obtenir le vecteur poids.

En fonction de la définition ci-dessus des bords, le bord est détecté en réunissant logiquement les sorties de quatre circuits logiques à seuil linéaire à états multiples avec des vecteurs poids correctement formés. La procédure de détection de bord complète est décrite par l'algorithme suivant.

- 1. Choisir la taille de la fenêtre locale 1.

- 2. Le faire pour i = 1, ..., n

- 2.1 Former Z

- 2.2 Calculer l'état d'entrée V, en fixant  $V_0 = 1$ .

- 2.3 Calculer les quatre produits scalaires W\_TV, W\_IV, W\_VV, et W\_VV. Si au moins l'un d'entre eux est supérieur à ou égal au seuil de sortie θ, ou inférieur à ou égal à -θ, auquel cas la sortie de la porte OU est égale à l, un bord est détecté à l'emplacement i, autrement, il n'y a pas de bord.

25

20

15

Pour la mise en œuvre de l'algorithme ci-dessus, la fonction non linéaire g(u) donnée ci-après est utilisée,

$$g(u) = \begin{bmatrix} 1 & u \geqslant \theta \\ 0 & -\theta \leqslant u \leqslant \theta \\ -1 & u \leqslant \theta \end{bmatrix}$$

où  $\theta$  est une valeur de seuil.  $\theta$  est fixé égal à six lorsque le vecteur poids ci-dessus est utilisé.

En ce qui concerne le choix de la taille de masque, les points suivants doivent être pris en compte. Plus la taille de masque est grande, meilleure est la commande de bruit par suite de l'opération de calcul de moyenne locale au cours de l'étape (2.2) dans l'algorithme ci-dessus. Cependant, il existe deux inconvénients à accroître la taille de masque, à savoir, (i) il devient plus difficile de détecter des bords dans des directions autres que 0, 45, 90, 135, 180, 225, 270 et 315 degrés et (ii) puisque davantage d'entrées sont nécessaires pour la logique à seuil linéaire à états multiples, davantage de connexions et de calculs sont nécessaires. La taille de masque l = 3 a été constatée très efficace du fait que cette fenêtre est la plus sensible à des bords dans une direction quel-conque, puisqu'elle est la plus petite fenêtre symétrique.

une circulation de signaux dans le procédé de détection de bord selon la présente invention. En utilisant la Figure 1, une mise en œuvre de logiciel peut être directement réalisée. Au cours de la première étape, l'indice i représente la position d'élément d'image ordonnée lexicographiquement. Au cours de la seconde étape, on obtient les éléments adjacents, Z, , j = 1,..., m de la configuration d'image locale centrée sur un i-ème élément d'image X;.

Au cours de la troisième étape, Z représente un ensemble d'éléments d'image dans une fenêtre locale comprenant le i-ème élément d'image  $X_{i}$  et m le nombre d'éléments d'image dans la fenêtre locale. Egalement, au cours de la troisième étape, on établit une correspondance entre  $Z_{j}$ , j = 1,...,met des valeurs d'états multiples correspondantes  $V_{j}$ , j = 1, ..., m. Au cours de la quatrième étape,  $V = [V_1, \dots, V_m]^T$ est comparé à des configurations de bord préalablement spécifiées  $\mathbf{W}_1$ ,  $\mathbf{W}_2$ ,  $\mathbf{W}_3$  et  $\mathbf{W}_4$ , respectivement. Au cours de la cinquième étape, si V concorde avec au moins l'une des 10 configurations de bord préalablement spécifiées  $\mathbf{W}_1$ ,  $\mathbf{W}_2$ ,  $W_3$  et  $W_4$  au cours de la sixième étape, on décide que le i-ème élément d'image  $\mathbf{X}_{\mathbf{i}}$  est un bord. Autrement, au cours de la septième étape, il est décidé que le i-ème élément d'image  $X_{i}$  n'est pas un bord. Au cours de la huitième 15 étape, si le i-ème élément d'image  ${\tt X}_i$  n'est pas un élément d'image complet, au cours de la neuvième étape, i est augmenté de l et le processus revient à la seconde étape et effectue une boucle principale de façon répétitive. Autrement, à la huitième étape, l'opération prend fin. 20

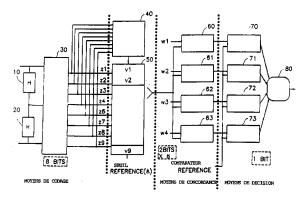

La Figure 2 représente un schéma synoptique général d'un dispositif de détection de bord selon la présente invention. La structure et le fonctionnement du dispositif sont les suivants.

Le dispositif de détection de bord représenté sur la Figure 3 est constitué de trois blocs, un bloc de codage afin de convertir les données lexicographiquement ordonnées  $Z_1, \ldots, Z_m$  en un état multiple  $V_1, \ldots, V_m$  après qu'une donnée d'image originale  $X_i$  a été ordonnée lexicographiquement en utilisant une fenêtre locale, un bloc de concordance afin d'effectuer un produit scalaire de données à états multiples  $V_1, \ldots, V_m$  et des configurations de bord préalablement spécifiées  $W_1, W_2, W_3$  et  $W_4$  corres-

pondant à W\_, W, , w, , et W, , respectivement, et un bloc de décision afin de comparer les données résultantes respectives du produit scalaire à une valeur de seuil de sortie, afin d'effectuer une réunion logique des résultats comparés et de décider si la donnée d'image originale  $X_{\hat{1}}$  est un bord ou non.

5

20

25

30

Les trois blocs ci-dessus accomplissent les fonctions suivantes.

Tout d'abord, un concept de fenêtre est nécessaire pour décider si la donnée d'image originale X<sub>i</sub> est un bord ou non par corrélation d'un élément d'image adjacent.

Ainsi, le bloc de codage dispose les éléments d'image adjacents, Z<sub>1</sub>, Z<sub>2</sub>,..., Z<sub>m</sub>, unidimensionnellement, et procure une valeur moyenne possédant une valeur d'intensité et convertit les éléments d'image adjacents Z<sub>1</sub>, Z<sub>2</sub>, ..., Z<sub>m</sub>, en valeurs à états multiples correspondantes, V<sub>1</sub>, V<sub>2</sub>,..., V<sub>m</sub>.

Si  $V_j$ ,  $j=1,\ldots,m$ , possède M états (M>2),  $\lceil \log_2 M \rceil$  est nécessaire pour représenter  $V_j$ . La notation  $\lceil \log_2 M \rceil$  désigne  $\log_2 M$ , si M est un multiple de 2, et autrement elle désigne la partie entière de  $\log_2 M+1$ . Ici, en introduisant la valeur moyenne et un paramètre de commande de bruit  $\mathcal{E}$ , le bloc de concordance sépare les éléments d'image respectifs en trois niveaux qui ont une valeur au-dessus de la moyenne  $+\mathcal{E}$ , une valeur au-dessous de la moyenne  $-\mathcal{E}$ , et une valeur entre la moyenne  $+\mathcal{E}$  et la moyenne  $-\mathcal{E}$ , respectivement. Ici, l'effet de réduction de bruit apparaît surtout selon le paramètre  $\mathcal{E}$ .

Un bloc de concordance délivre le degré de concordance de la donnée d'image convertie et de quatre configurations de bord préalablement spécifiées, respectivement. C'est-à-dire que le bloc de concordance effectue le produit scalaire des données d'image converties,  $V_1$ ,  $V_2$ ,...,  $V_m$ ;  $V_1$ , et des quatre configurations de bord préalablement spécifiées respectives,  $W_1$ ,  $W_2$ ,  $W_3$  et  $W_4$  qui sont attendues par rapport à une direction horizontale, une direction verticale et deux directions diagonales. Ici,  $W_1^T$ .  $V_1^T$ .  $V_2^T$  représente le produit scalaire des données d'image converties  $V_1$ ,  $V_2$ ,...,  $V_m$ ;  $V_1$ , et de la configuration de bord préalablement spécifiée  $V_1$  qui est espérée par rapport à la direction horizontale.

Un traitement en temps réel peut être réalisé, qui est basé sur le système de traitement d'image en effectuant l'opération des quatre produits scalaires simultanément.

Un bloc de décision accomplit une fonction de

comparaison de valeurs de sortie des produits scalaires

W1 .V, W2 .V, W3 .V, W4 .V, respectivement à une constante

donnée et décide qu'il s'agit d'un bord si au moins une

parmi les valeurs de sortie est supérieure à la constante

donnée. Et la constante donnée pour une comparaison avec

les valeurs de sortie des produits scalaires peut être

commandée par l'utilisateur en utilisant un microcalculateur.

La Figure 3 représente un mode de réalisation préféré du dispositif de détection de bord selon la présente invention. La structure et le fonctionnement du dispositif sont les suivants.

25

30

Un moyen de codage comporte un premier dispositif de retard 10 afin de délivrer un signal retardé d'une ligne de balayage horizontal de données d'image entrées, un second dispositif de retard 20 qui est monté en série avec le premier dispositif de retard 10, pour délivrer un signal retardé de deux lignes de balayage horizontal, un circuit

de fenêtre 3 x 3 30, qui est connecté à la borne d'entrée du moyen de codage, à la borne de sortie du premier dispositif de retard 10 et à la borne de sortie du second dispositif de retard 20, afin de mémoriser neuf données d'élément d'image dans le circuit de fenêtre locale 3 x 3, un circuit de calcul de moyenne 40 pour délivrer une valeur moyenne de huit données d'élément d'image à l'exception des données de l'élément d'image central dans la fenêtre locale 3 x 3, et un codeur à trois états 50 pour séparer les huit données d'élément d'image respectives en trois niveaux en utilisant la valeur moyenne et la valeur de seuil donnée & et pour convertir les huit données d'élément d'image en code correspondant à trois niveaux.

5

10

25

30

Un moyen de concordance comporte les circuits

de produit scalaire 60, 61, 62, 63 afin d'effectuer le

produit scalaire des configurations de bord préalablement

spécifiées respectives W<sub>1</sub>, W<sub>2</sub>, W<sub>3</sub> et W<sub>4</sub> et des sorties

du codeur à trois états 50.

Un moyen de décision comporte des comparateurs 70, 71, 72, 73 afin de comparer les sorties des circuits de produit scalaire respectifs 60, 61, 62, 63 à la donnée constante et délivrer le signal de concordance et une porte OU 80 pour sommer logiquement les sorties des comparateurs 70, 71, 72, 73.

La Figure 4 représente un mode de réalisation préféré du moyen de codage. Le circuit de fenêtre 3 x 3 30 comporte trois registres 90, 91, 92 comprenant respectivement un ensemble de huit bascules de type D connectées en parallèle et reliées en série à une borne d'entrée pour appliquer un signal vidéo numérique balayé séquentiellement représenté par huit bits, et trois registres 100, 101, 102 comprenant respectivement un ensemble de huit bascules de

type D connectées en parallèle et reliées en série à une borne de sortie du premier dispositif de retard 10 pour appliquer le signal de sortie du premier dispositif de retard 10 et trois registres 110, 111, 112 comprenant respectivement un ensemble de huit bascules de type D con-5 nectées en parallèle et reliées en série à la borne de sortie du second dispositif de retard 20 afin d'appliquer le signal de sortie du second dispositif de retard 20, si bien que neuf données d'élément d'image sont mémorisés dans un circuit de fenêtre 3x3 30. Un circuit de calcul 10 de moyenne réelle 120 comporte des additionneurs 121, 122, 123, 124 pour additionner par deux les signaux de sortie des huit registres 90, 91, 92, 100, 102, 110, 111, 112, à l'exception du signal de sortie du registre 101, et des additionneurs 130, 131 pour additionner par deux les signaux 15 subsistant après élimination du bit de plus faible poids LSB des signaux de sortie des additionneurs 121, 122, 123, 124 et un additionneur 140 afin d'additionner les signaux subsistant après élimination d'un bit de plus faible poids LSB des signaux de sortie des additionneurs 130, 131, et 20 pour délivrer un signal subsistant après élimination d'un bit de plus faible poids LSB de son signal de sortie.

Les signaux de sortie des huit registres 90, 91, 92, 100, 102, 110, 111, 112 et le signal de sortie de l'additionneur 140 sont temporairement mémorisés dans des registres (non représentés) pour une application à l'étage suivant. C'est-à-dire que le circuit de calcul de la moyenne 120 calcule une valeur moyenne comme suit.

25

Soient Z<sub>1</sub>, Z<sub>2</sub>, Z<sub>3</sub>, Z<sub>4</sub>, Z<sub>6</sub>, Z<sub>7</sub>, Z<sub>8</sub>, et Z<sub>9</sub> les 30 sorties des registres 90, 91, 92, 100, 102, 110, 111, 112. Soient A, B, C et D la somme de deux données choisies parmi les sorties des registres, A, B, C et D sont représentés par

$$A = Z_1 + Z_2$$

$B = Z_3 + Z_4$   $C = Z_6 + Z_7$  et  $D = Z_8 + Z_9$ .

Ici, soient E, F, G et H les valeurs subsistantes après élimination d'un bit LSB des valeurs A, B, C , D. Alors, E, F, G et H sont représentés par

5

$$E = \frac{A}{2} = \frac{z_1 + z_2}{2}$$

$$F = \frac{B}{2} = \frac{z_3 + z_4}{2}$$

$$G = \frac{C}{2} = \frac{z_6 + z_7}{2}$$

et

$$H = \frac{D}{2} = \frac{z_8 + z_9}{2}$$

Et, soient I et J les sommes de E et F, et de G et H, respectivement, alors I et J sont représentés par

$$I = E + F = \frac{Z_1 + Z_2 + Z_3 + Z_4}{2}$$

et  $J = G + H = \frac{Z_6 + Z_7 + Z_8 + Z_9}{2}$

10 Ici, soient K et L les valeurs restantes après élimination d'un bit LSB de I et J, respectivement, alors K et L sont représentés par

$$K = \frac{E+F}{2} = \frac{Z_1 + Z_2 + Z_3 + Z_4}{4}$$

et  $L = \frac{G+H}{2} = \frac{Z_6 + Z_7 + Z_8 + Z_9}{4}$

Et, en supposant que la valeur obtenue en additionnant K et

L et en éliminant un bit de plus faible poids LSB de la

valeur résultante est une valeur moyenne M, alors M est

représenté par

$$M = \frac{K+L}{2} = \frac{Z_1 + Z_2 + Z_3 + Z_4 + Z_6 + Z_7 + Z_8 + Z_9}{8}$$

La valeur moyenne obtenue M n'est pas une valeur moyenne 20 exacte. Mais la différence entre la valeur moyenne exacte et la valeur moyenne obtenue n'altère pas la qualité d'un bord résultant du fait que la valeur moyenne obtenue est utilisée pour un codage à trois états de l'étage suivant.

Et, le circuit codeur à trois états 150 comporte l'additionneur 160 afin d'additionner la valeur moyenne M et un paramètre & ayant un effet de réduction de bruit et 5 afin de produire une valeur M + E; l'additionneur 161 afin d'additionner la valeur moyenne M et le paramètre - € et afin de délivrer une valeur M - E ; huit comparateurs 170 afin de comparer des données d'élément d'image respectives Z<sub>1</sub>, Z<sub>2</sub>,..., Z<sub>9</sub>,à l'exception des données de l'élément d'ima-10 ge centrale  $Z_5$ , à la valeur M + E; huit comparateurs 171 afin de comparer les données d'élément d'image respectives  $\mathbf{z}_1$ ,  $\mathbf{z}_2$ ,...,  $\mathbf{z}_9$  à l'exception des données de l'élément d'image centrale  $Z_{\varsigma}$ , à la valeur M -  $\epsilon$ ; huit inverseurs 180 afin de délivrer les signaux de bit de plus fort poids MSB  $V_{11}$ , 15  $v_{21}$ , ...,  $v_{91}$ , des comparateurs 170 ; et huitiportes OU 190 pour effectuer une réunion logique, c'est-à-dire sommer logiquement les signaux de bit de plus faible poids LSB  $v_{10}, v_{20}, \ldots, v_{90},$  des signaux à trois états et les sorties des comparateurs 171, respectivement. Ainsi, le décodeur 20à trois états 150 délivre une valeur 11 si la donnée d'élément d'image respective est inférieure à la valeur  $M - \mathcal{E}$ , et une valeur 01 si les données d'élément d'image respectives sont supérieures à la valeur M + E , et autrement, une valeur 00. Ici, on suppose que le bit de plus fort 25 poids MSB est un bit de signe et que le bit de plus faible poids LSB est un bit d'amplitude, ainsi, les valeurs 11, 00 et 01, correspondent aux trois états, -1, 0, 1, respectivement.

La Figure 5 représente les quatre configurations de bord préalablement spécifiées  $W_1$ ,  $W_2$ ,  $W_3$  et  $W_4$ .

30

Les Figures 6A, 6B, 6C, 6D représentent les cir-

cuits afin d'effectuer les produits scalaires des moyens de concordance de la présente invention.

Les moyens de concordance effectuent les produits scalaires entre deux compléments d'éléments des quatre configurations de bord préalablement spécifiées respectives  $W_1$ ,  $W_2$ ,  $W_3$  et  $W_4$ , et les valeurs converties  $V_{11}$ ,  $V_{10}$ ,  $V_{21}$ ,  $V_{20}$ , ...,  $V_{91}$ ,  $V_{90}$ .

La Figure 7 représente une table de vérité pour le produit scalaire.

La Figure 8 représente une carte de Karnaugh en vue de la simplification du circuit de produit scalaire.

Les équations logiques simplifiées de la Figure 8 sont

$$v_{j 1}(MSB) = \overline{v_{j 1}} v_{j 0} w_{j 1} + v_{j 1} \overline{w_{j 1}} w_{j 0}$$

15

$$v_{j 0}(LSB) = v_{j 0}w_{j 0}$$

.

5

Ces équations logiques peuvent encore être simplifiées en utilisant les propriétés des quatre configurations de bord préalablement spécifiées.

Tout d'abord, dans le cas où  $W_{j,1} = W_{j,0} = 1$ ,

$$U_{j 1}(MSB) = \overline{V_{j 1}}V_{j 0}$$

$$U_{j 0}(LSB) = V_{j 0}.$$

En second lieu, dans le cas où  $W_{j} = W_{j} = 0$ ,

$$U_{j,1}(MSB) = U_{j,0}(LSB) = 0$$

C'est-à-dire que le produit scalaire délivré est toujours "0" indépendamment des données d'image et ainsi est sans influence sur le bord résultant.

En troisième lieu, dans le cas où  $W_{j\ 1}=0$ ,  $W_{j\ 0}=1$ ,

$$U_{j,1}(MSB) = V_{j,1}$$

$$U_{j 0}(LSB) = V_{j 0}$$

.

10

15

En résultat, pour la réalisation d'un circuit, les quatre configurations de bord préalablement spécifiées existent implicitement, et seules des valeurs à trois états restent avoir une influence sur la sortie du produit scalaire. Egalement, les sorties de produit scalaire obtenues sont représentées par deux bits et seulement six éléments d'image à l'exception d'éléments d'image avec une valeur de poids 0 parmi neuf éléments d'image sont utilisés pour la réalisation des circuits.

Une réalisation de circuits utilisant les équations logiques ci-dessus est représentée ci-après.

Tout d'abord, le circuit de concordance de  $W_1$ .V délivre  $(\overline{V_{11}}.V_{10})V_{10}$ ,  $(V_{31})V_{30}$ ,  $(\overline{V_{41}}.V_{40})V_{40}$ ,  $V_{61}V_{60}$ ,  $(\overline{V_{71}}.V_{70})V_{70}$ ,  $V_{91}V_{90}$ .

En second lieu, le circuit de concordance de  $W_2$ . V délivre  $(\overline{V_{11}}.V_{10})V_{10}, V_{71}V_{70}, (\overline{V_{21}}.V_{20})V_{20}, V_{81}V_{80}, (\overline{V_{31}}.V_{30}) V_{30}, V_{91}V_{90}$ .

En troisième lieu, le circuit de concordance de  $w_3$ . V délivre  $(\overline{v_{11}}.v_{10})v_{10}$ ,  $v_{61}v_{60}$ ,  $(\overline{v_{21}}.v_{20})v_{20}$ ,  $v_{81}v_{80}$ ,  $(\overline{v_{41}}.v_{40})v_{40}$ ,  $v_{91}v_{90}$ .

En quatrième lieu, le circuit de concordance de  $w_4 \cdot v$  délivre  $(\overline{v_{21}} \cdot v_{20}) v_{20}$ ,  $v_{41} v_{40}$ ,  $(\overline{v_{31}} \cdot v_{30}) v_{30}$ ,  $v_{71} v_{70}$ ,  $(\overline{v_{61}} \cdot v_{60}) v_{60}$ ,  $v_{81} v_{80}$ .

Ces équations logiques sont réalisées en utilisant trois inverseurs 200 et trois portes ET 210, comme représenté sur les Figures 6A, 6B, 6C et 6D.

5

25

30

Ensuite, les sorties des portes ET 210 et les sorties des inverseurs 200 dans le circuit de concordance correspondant sont additionnées pour un produit scalaire.

Ici, l'addition est réalisée en utilisant cinq additionneurs 220 et en ajoutant un circuit de valeur absolue 230. L'adjonction du circuit de valeur absolue 230 est utilisée pour obtenir le même résultat de bord dans le cas où la valeur finale de l'addition possède une valeur négative du fait que les sorties des portes ET 210 sont représentées par complément à deux. Egalement, l'addition des sorties des portes ET 210 et des sorties des inverseurs 200 utilise le procédé de calcul de signe.

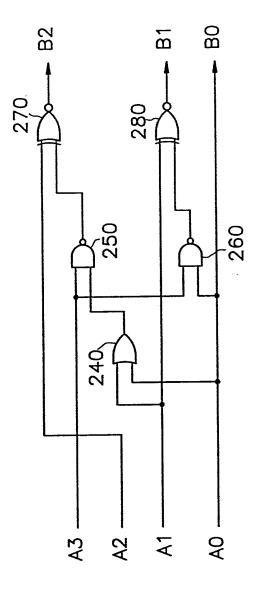

Le circuit de valeur absolue 230 représenté sur 20 les Figures 6A, 6B, 6C et 6D pour obtenir la valeur absolue est représenté plus en détail sur la Figure 9.

Sur la Figure 9, on suppose qu'une donnée d'entrée de quatre bits est  $A_3$ ,  $A_2$ ,  $A_1$ ,  $A_0$  et qu'une donnée de sortie est  $B_2B_1B_0$ . Le circuit de valeur absolue 230 est constitué de la porte OU 240 pour effectuer une réunion logique de la donnée d'entrée  $A_1$  et  $A_0$ , et d'une porte NON ET 250 pour délivrer "0" lorsque la sortie de la porte OU 240 et la donnée d'entrée  $A_3$  sont toutes "1", une porte NON ET 260 pour délivrer "0" lorsque les données d'entrée  $A_3$  et  $A_0$  sont des "1", et une porte NON OU exclu-

sif 270 pour délivrer "1" lorsque la donnée d'entrée  $A_2$  et la sortie de la porte NON ET 250 n'ont pas les mêmes valeurs, et une porte NON OU exclusif 280 pour délivrer "1" lorsque la donnée d'entrée  $A_1$  et la sortie de la porte NON OU 260 n'ont pas les mêmes valeurs. Ainsi, les valeurs de sortie des portes NON OU exclusif 270, 280 et d'une donnée d'entrée  $A_0$ , respectivement, deviennent la sortie  $B_2B_1B_0$  du circuit de valeur absolue 230.

5

25

30

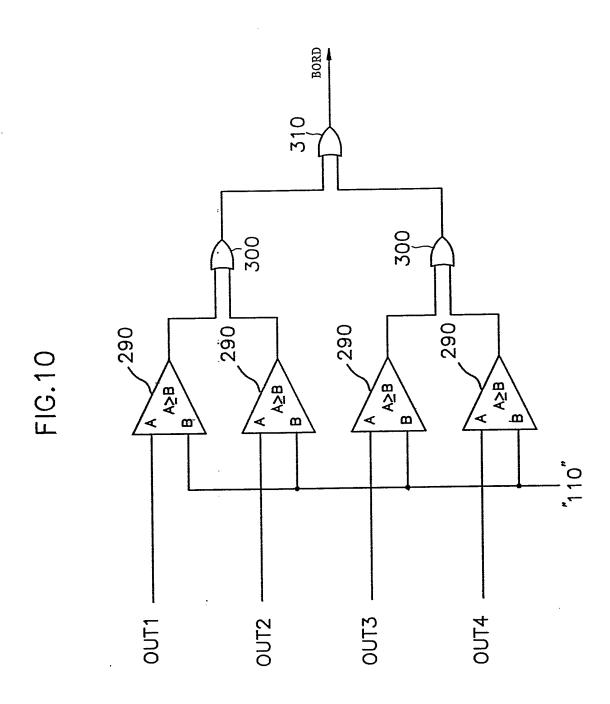

La Figure 10 représente un mode de réalisation préféré du moyen de décision du dispositif de détection de 10 bord de l'invention. Le moyen de décision est constitué de quatre comparateurs 290 pour entrer les signaux de sortie OUT1, OUT2, OUT3 et OUT4 des circuits de valeur absolue 230 et une valeur de seuil "110" représentant un bord, et de deux portes OU 300 pour effectuer une réunion logique de 15 deux signaux choisis parmi les signaux de sortie des quatre comparateurs 290 respectivement, et d'une porte OU 310 pour effectuer la réunion logique de deux signaux de sortie de deux portes OU 300. Et, si au moins un signal de sortie choisi parmi les signaux de sortie OUT1, OUT2, OUT3 et OUT4 20 est supérieur à ou égal à "6", la sortie de la porte OU 310 devient "1", et est déterminée comme étant un bord.

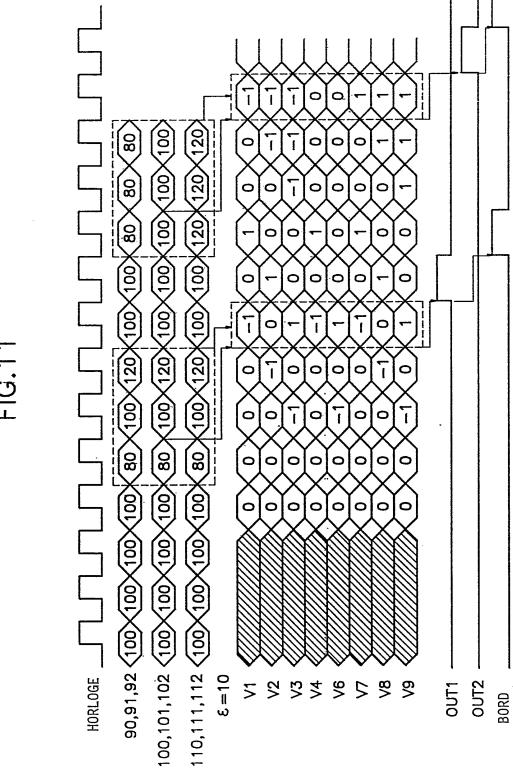

La Figure 11 est un diagramme temporel représentant le fonctionnement du circuit de détection de bord de la présente invention.

On suppose que les données d'image d'entrée représentées sur la Figure 11 sont mémorisées dans le circuit fenêtre 3x3 90, 91, 92, 100, 101, 102, 110, 111 et 112. Ici,  $\xi$  est fixé à 10. Et les valeurs à trois états  $V_1$ ,  $V_2$ ,  $V_3$ ,  $V_4$ ,  $V_6$ ,  $V_7$ ,  $V_8$ ,  $V_9$  sont représentées sur la Figure 11. Ici, deux configurations d'entrée dans la zone carrée entourée par un pointillé sont égales à la configuration de bord

préalablement spécifiée correspondante. Ainsi, la première zone carrée entourée par un pointillé est égale à  $W_1$  et la seconde zone carrée entourée par un pointillé est égale à  $W_2$ . Par conséquent, le signal de sortie BORD devient "1" lorsqu'au moins un des signaux de sortie OUT1 et OUT2 est "1".

5

15

20

Le dispositif de détection de bord selon la présente invention présente les avantages suivants.

Tout d'abord, en utilisant le paramètre de ré10 duction de bruit dans un procédé de codage à états multiples,

elle peut réduire grandement l'effet de bruit sans utiliser

des filtres passe-bas supplémentaires.

En second lieu, elle peut grandement simplifier l'équipement et minimiser le temps d'opération en utilisant une fenêtre locale 3x3 qui est la plus petite fenêtre symétrique bidimensionnelle.

En troisième lieu, en utilisant plusieurs circuits logiques à seuil linéaires simultanément, elle peut utiliser les propriétés invariantes en rotation de circuits logiques à seuil linéaires à couches multiples.

### REVENDICATIONS

1. Procédé de détection de bord pour un système de traitement d'image, caractérisé en ce qu'il comporte les étapes consistant à :

convertir les données d'élément d'image d'entrée en un ensemble de valeurs à états multiples ;

effectuer le produit scalaire dudit ensemble de valeurs à états multiples et de valeurs préalablement spécifiées ; et

prendre une décision selon le résultat dudit 10 produit scalaire.

2. Dispositif de détection de bord pour un système de traitement d'image, caractérisé en ce qu'il comporte :

un moyen de conversion (10,20) pour convertir les données d'élément d'image d'entrée en valeurs à états multiples;

un moyen de concordance (60,61,62,63) pour effectuer le produit scalaire desdites valeurs à états multiples et de valeurs préalablement spécifiées ; et

un moyen de décision (70,71,72,73,80) pour prendre une décision selon le résultat dudit produit scalaire.

20

25

30

15

5

- Dispositif de détection de bord pour un système de traitement d'image selon la revendication 2, caractérisé en ce que ledit moyen de conversion comporte en outre un moyen de mémorisation (30) afin de mémoriser lesdites données d'élément d'image.

- 4. Dispositif de détection de bord pour un système de traitement d'image selon la revendication 3, caractérisé en ce que lesdits moyens de mémorisation (30) mémorisent l x l données afin de mémoriser des éléments d'image adjacents autour de l'élément d'image central.

5

20

25

30

Dispositif de détection de bord pour un système de traitement d'image selon la revendication 4, caractérisé en ce que ledit moyen de conversion comporte un circuit (40) de calcul de la valeur moyenne afin de calculer une valeur moyenne desdites 1 x l données; et

un circuit d'établissement de correspondance (50) pour convertir lesdites 1 x l données en lesdites valeurs à états multiples en utilisant ladite valeur moyenne et une constante arbitraire.

- 10 6. Dispositif de détection de bord pour un système de traitement d'image selon la revendication 5, caractérisé en ce que ladite constante arbitraire est un paramètre de réduction de bruit.

- Dispositif de détection de bord pour un système

de traitement d'image selon la revendication 6, caractérisé en ce que ledit l est égal à 3.

- 8. Dispositif de détection de bord pour un système de traitement d'image selon la revendication 7, caractérisé en ce que lesdits moyens de mémorisation (30) comportent :

un premier dispositif de retard (10) afin de retarder lesdites données d'élément d'image d'entrée d'une ligne de balayage horizontal;

un second dispositif de retard (20), qui est connecté en série avec ledit premier dispositif de retard afin de retarder lesdites données d'élément d'image d'entrée de deux lignes de balayage horizontal;

trois premiers registres (90), (91), (92), qui sont connectés en série à une borne d'entrée, afin d'entrer lesdites données d'élément d'image d'entrée;

trois seconds registres (100), (101), (102), qui sont connectés en série avec ledit premier dispositif de retard, afin d'entrer ledit signal retardé d'une ligne de balayage horizontal;

5

10

15

20

25

trois troisièmes registres (110), (111), (112), qui sont connectés en série avec ledit second dispositif de retard, afin d'entrer ledit signal retardé de deux lignes de balayage horizontal.

- 9. Dispositif de détection de bord pour un système de traitement d'image selon la revendication 8, caractérisé en ce que lesdits premiers, seconds, troisièmes registres (90), (91), (92), (100), (101), (102), (110), (111), (112) sont constitués respectivement d'une pluralité de bascules de type D.

- 10. Dispositif de détection de bord pour un système de traitement d'image selon la revendication 9, caractérisé en ce que ledit circuit de calcul de valeur moyenne (120) comporte :

quatre premiers additionneurs (121), (122), (123), (124) pour additionner quatre paires de signaux de sortie desdits premiers, seconds et troisièmes registres à l'exception d'un parmi lesdits seconds registres possédant une donnée d'élément d'image central;

deux seconds additionneurs (130), (131) pour additionner deux signaux de sortie choisis parmi les signaux de sortie subsistant après élimination du bit de plus faible poids de la sortie desdits quatre premiers additionneurs;

un troisième additionneur (140) pour additionner des signaux de sortie subsistant après élimination du bit de plus faible poids des sorties desdits seconds deux additionneurs et délivrer un signal subsistant après élimination du bit de plus faible poids du signal additionné.

30 11. Dispositif de détection de bord pour un système de traitement d'image selon la revendication 10, caractérisé en ce que ledit circuit d'établissement de correspondance (150) convertit lesdites données d'élément d'image d'entrée en des valeurs à trois états.

12. Dispositif de détection de bord pour un système de traitement d'image selon la revendication ll, caractérisé en ce que lesdites valeurs à trois états sont ll, 01 et 00 en représentation de nombres binaires de complément à deux, respectivement.

5

15

20

25

13. Dispositif de détection de bord pour un système de traitement d'image selon la revendication 12, caractérisé en ce que ledit circuit d'établissement de correspondance (150) comporte :

un quatrième additionneur (160) pour additionner un signal de sortie dudit troisième additionneur et ladite constante arbitraire ;

un cinquième additionneur (161) pour additionner un signal de sortie dudit troisième additionneur et la valeur négative de ladite constante arbitraire;

huit premiers comparateurs (170) pour comparer les huit données d'élément d'image à l'exclusion desdites données d'élément d'image central avec le signal de sortie dudit quatrième additionneur, respectivement;

huit seconds comparateurs (171) pour comparer lesdits huit données d'élément d'image à un signal de sortie dudit cinquième additionneur ;

huit inverseurs (180) pour inverser les signaux de sortie desdits premiers comparateurs respectivement et délivrer le signal de bit de plus fort poids de ladite valeur à trois états respectivement ; et

huit portes OU (190) pour effectuer une réunion

30 logique d'un signal de sortie desdits huit inverseurs et

des signaux de sortie desdits seconds huit comparateurs

et délivrer le signal de bit de plus faible poids de ladite valeur à trois états respectivement.

5

10

- 14. Dispositif de détection de bord pour un système de traitement d'image selon la revendication 13, caractérisé en ce que ledit moyen de concordance effectue le produit scalaire de ladite valeur à trois états et desdites quatre configurations de bord préalablement spécifiées.

- Dispositif de détection de bord pour un système de traitement d'image selon la revendication 14, caractérisé en ce que lesdites quatre configurations de bord préalablement spécifiées sont constituées des matrices 3 x 3 correspondantes.

- de traitement d'image selon la revendication 15, caractérisé en ce que chacune desdites quatre configurations de bord préalablement spécifiées comporte une première configuration (W<sub>1</sub>) possédant -1 dans la première colonne, 0 dans la seconde colonne, 1 dans la troisième colonne; une seconde confiquration (W<sub>2</sub>) possédant -1 dans la première rangée, 0 dans la seconde rangée, 1 dans la troisième rangée; une troisième configuration (W<sub>3</sub>) possédant -1, -1, 0 dans la première rangée, -1, 0, 1 dans la seconde rangée, 0, 1, 1 dans la troisième rangée; et une quatrième configuration (W<sub>4</sub>) possédant 0, -1, -1 dans la première rangée, 1, 0, -1 dans la seconde rangée, 1, 1, 0 dans la troisième rangée.

- 17. Dispositif de détection de bord pour un système

25 de traitement d'image selon la revendication 16, caractérisé

en ce que ledit circuit de produit scalaire (60) de ladite

valeur à trois états et de ladite première configuration

comporte:

- trois inverseurs (200) pour inverser le bit de

30 plus fort poids de la première, quatrième et septième valeurs desdites valeurs à trois états, respectivement;

trois portes ET (210) pour délivrer logiquement

des signaux de sortie desdits trois inverseurs et le bit de plus faible poids de ladite première, quatrième et septième valeur desdites valeurs à trois états, respectivement;

cinq huitièmes additionneurs (220) pour additionner les troisième, sixième, neuvième valeurs desdites valeurs à trois états et les signaux de sortie desdites trois portes ET en utilisant le calcul du signe; et

un circuit de valeur absolue (230) pour obtenir une valeur absolue lorsque le signal de sortie final desdits cinq huitièmes additionneurs est une valeur négative.

10

15

20

25

30

18. Dispositif de détection de bord pour un système de traitement d'image selon la revendication 17, caractérisé en ce que ledit circuit de produit scalaire (61) de ladite valeur à trois états et de ladite seconde configuration comporte :

trois inverseurs (200) pour inverser le bit de plus fort poids des première, seconde et troisième valeurs desdites valeurs à trois états, respectivement;

trois portes ET (210) pour délivrer logiquement des signaux de sortie desdits trois inverseurs et le bit de plus faible poids des première, seconde et troisième valeurs desdites valeurs à trois états, respectivement;

cinq neuvièmes additionneurs (220) pour additionner les septième, huitième et neuvième valeurs desdites valeurs à trois états et les signaux de sortie desdites trois portes ET en utilisant le calcul de signes ; et

un circuit de valeur absolue (230) pour obtenir une valeur absolue lorsque le signal de sortie final desdits neuvièmes cinq additionneurs est une valeur absolue.

19. Dispositif de détection de bord pour un système de traitement d'image selon la revendication 18, caractérisé

en ce que ledit circuit de produit scalaire (62) de ladite valeur à trois états et de ladite troisième configuration comporte :

trois inverseurs (200) pour inverser le bit de plus fort poids des première, seconde et quatrième valeurs desdites valeurs à trois états, respectivement;

5

10

15

20

25

30

trois portes ET (210) pour produire logiquement des signaux de sortie desdits trois inverseurs et le bit de plus faible poids des première, seconde et quatrième valeurs desdites valeurs à trois états, respectivement;

cinq dixièmes additionneurs (220) pour additionner les sixième, huitième et neuvième valeurs desdites valeurs à trois états et les signaux de sortie desdites trois portes ET en utilisant le calcul de signe ; et

un circuit de valeur absolue (230) pour obtenir une valeur absolue lorsque le signal de sortie final desdits dixièmes cinq additionneurs est une valeur négative.

20. Dispositif de détection de bord pour un système de traitement d'image selon la revendication 19, caractérisé en ce que ledit circuit de produit scalaire (63) de ladite valeur à trois états et de ladite quatrième configuration comporte :

trois inverseurs (200) pour inverser le bit de plus fort poids des seconde, troisième et sixième valeurs desdites valeurs à trois états, respectivement;

trois portes ET (210) pour produire logiquement des signaux de sortie desdits trois inverseurs et le bit de plus faible poids des seconde, troisième et sixième valeurs desdites valeurs à trois états, respectivement;

cinq onzièmes additionneurs (220) pour additionner les quatrième, septième et huitième valeurs desdites valeurs à trois états et les signaux de sortie desdites trois portes ET en utilisant le calcul de signe ; et un circuit de valeur absolue (230) pour obtenir une valeur absolue lorsque le signal de sortie final desdits onzièmes cinq additionneurs est une valeur négative.

21. Dispositif de détection de bord pour un système de traitement d'image selon la revendication 20, caractérisé en ce que ledit circuit de valeur absolue (230) comporte :

une porte OU (240) pour effectuer une réunion logique des deux bits de plus faible poids de quatre bits d'entrée;

une cinquième porte NON ET (250) pour entrer un signal de sortie de ladite porte OU et le bit de plus fort poids desdits quatre bits d'entrée;

5

20

25

une seconde porte NON ET (260) pour entrer le bit de plus fort poids et le bit de plus faible poids desdits quatre bits d'entrée ;

une première porte NON OU exclusif (270) pour entrer un signal de sortie provenant de ladite première porte NON ET et le second bit de plus fort poids desdits quatre bits d'entrée ; et

une seconde porte NON OU exclusif (280) pour entrer un signal de sortie de ladite seconde porte NON ET et ledit second bit de plus faible poids desdits quatre bits d'entrée,

si bien qu'une sortie de ladite première porte NON OU exclusif est le bit de plus fort poids de ladite valeur absolue, le bit de plus faible poids dudit huitième additionneur est le bit de plus faible poids de ladite valeur absolue, une sortie de ladite seconde porte NON OU exclusif est le bit médian de la valeur absolue.

22. Dispositif de détection de bord pour un système 30 de traitement d'image selon la revendication 21, caractérisé en ce que ledit moyen de décision comporte :

quatre troisièmes comparateurs (270) pour entrer un signal de sortie de quatre circuits de valeur absolue et une valeur de seuil donnée, respectivement;

deux portes OU (300) pour effectuer une réunion

logique de deux signaux de sortie choisis parmi les signaux

de sortie desdits troisièmes quatre comparateurs; et

une porte OU (310) pour effectuer une réunion

logique de signaux de sortie desdites deux portes OU.

FIG.5

$$w1 = \begin{bmatrix} -1 & 0 & 1 \\ -1 & 0 & 1 \\ -1 & 0 & 1 \end{bmatrix}$$

$$w4 = \begin{array}{c|cccc} 0 & -1 & -1 \\ \hline 1 & 0 & -1 \\ \hline 1 & 1 & 0 \end{array}$$

FIG.6A

CALCUL SIGNE

FIG.6B

## CALCUL SIGNE

FIG.6C

CALCUL SIGNE

FIG.6D

CALCUL SIGNE

FIG.7

| DONNEES<br>COD |          | CONFIGURA<br>BORD PREAI<br>SPECIFIEE |          | RESULTAT PRODUIT<br>SCALAIRE |          |  |  |

|----------------|----------|--------------------------------------|----------|------------------------------|----------|--|--|

| Vj1(MSB)       | Vj0(LSB) | Wj1(MSB)                             | WjO(LSB) | Uj1(MSB)                     | Uj0(LSB) |  |  |

| 0              | 0        | 0                                    | 0        | 0                            | .0       |  |  |

| 0              | 0        | 0                                    | 1        | 0                            | 0        |  |  |

| 0              | 0        | 1                                    | 0        | X                            | X        |  |  |

| 0              | 0        | 1                                    | 1        | 0                            | 0        |  |  |

| 0              | 1        | 0                                    | 0        | 0                            | 0        |  |  |

| 0              | 1        | 0                                    | 1        | 0                            | 1        |  |  |

| 0              | 1        | 1                                    | 0        | X                            | X        |  |  |

| 0              | 1        | 1                                    | 1        | 1                            | 1        |  |  |

| 1              | 0        | 0                                    | 0        | X                            | X        |  |  |

| 1              | 0        | 0                                    | 11       | X                            | X        |  |  |

| 1              | 0        | 11                                   | 0        | X                            | X        |  |  |

| 1              | 0        | 1                                    | 11       | X                            | X        |  |  |

| 1              | 1        | 0                                    | 0        | 0                            | 0        |  |  |

| 1              | 11       | 0                                    | 1        | 11                           | 1        |  |  |

| 1              | 1        | 1                                    | 0        | X                            | X        |  |  |

| 1              | 1        | 1 1                                  | 1 .      | 0                            | 1        |  |  |

FIG.8

| √Vj1 Vj0                     |     |   |   |   |   | √Vj1 Vj0               |   |     |      |     |     |      |     |

|------------------------------|-----|---|---|---|---|------------------------|---|-----|------|-----|-----|------|-----|

| Vj1                          | Vj0 | 0 | 0 | 0 | X | Vj                     | 1 | Vj0 | 0    | 0   | 0   | X    |     |

|                              |     | 0 | 0 | 1 | X |                        |   |     | 0    | 1   | 1   | X    |     |

|                              |     | 0 | 1 | 0 | X |                        |   |     | 0    | 1   | 1   | X    |     |

|                              |     | X | Χ | Χ | X |                        |   |     | X    | X   | X   | X    |     |

| Uj1(MSB)=Vj1Vj0Wj1+Vj1Wj1Wj0 |     |   |   |   |   | ⁄j1 <del>Wj1</del> Wj0 |   | Uj  | jO(l | _SB | )=\ | /jOV | VjO |

FIG.9