# (19) **日本国特許庁(JP)**

# (12)公開特許公報(A)

(11)特許出願公開番号

特開2006-49508 (P2006-49508A)

(43) 公開日 平成18年2月16日 (2006.2.16)

(51) Int.C1. F I **HO 1 L 27/146 (2006.01)** HO 1 L 27 テーマコード (参考)

HO1L 27/146 (2006.01) HO4N 5/335 (2006.01) HO1L 27/14 A 4M118 HO4N 5/335 U 5CO24

審査請求 未請求 請求項の数 5 OL (全 12 頁)

(21) 出願番号 (22) 出願日 特願2004-227025 (P2004-227025) 平成16年8月3日 (2004.8.3) (71) 出願人 000004112

株式会社ニコン

東京都千代田区丸の内3丁目2番3号

(74)代理人 100072718

弁理士 古谷 史旺

(74)代理人 100116001

弁理士 森 俊秀

(72) 発明者 大河内 直紀

東京都千代田区丸の内3丁目2番3号 株

式会社ニコン内

F ターム (参考) 4M118 AA10 AB01 BA14 CA04 CA20

DD09 DD12 EA01 FA06 FA33

GB15

5C024 CX41 GX02 GX16 GY39 HX01

HX40

#### (54) 【発明の名称】 固体撮像装置

# (57)【要約】

【課題】 固体撮像装置において、受光素子の占有面積拡大に有効な単位画素の素子構造を提供する。

【解決手段】 本発明の固体撮像装置は、複数の単位画素を半導体基板に形成する。この単位画素は、入射光に応じて信号電荷を生成する受光素子と、受光素子で生成された信号電荷を取り込み、信号電荷に応じた画素信号を出力するJFET(接合型電界効果トランジスタ)とを備える。特に、このJFETは、縦型JFETであり、半導体基板の基板深さ方向に電流経路を形成するチャネル領域と、このチャネル領域を挟み込むように深さ方向に形成され、信号電荷によってチャネル領域のチャネル幅を制御するゲート領域とを備える。

【選択図】 図2

#### 【特許請求の範囲】

# 【請求項1】

入射光に応じて信号電荷を生成する受光素子と、

前記受光素子で生成された前記信号電荷を取り込み、前記信号電荷に応じた画素信号を 出力するJFET(接合型電界効果トランジスタ)と

を有する単位画素を半導体基板に複数形成した固体撮像装置であって、

前記JFETは、

前記半導体基板の基板深さ方向に電流経路を配置したチャネル領域と、

前記チャネル領域を挟み込むように前記基板深さ方向に形成され、前記信号電荷を蓄積し、蓄積した前記信号電荷によって前記チャネル領域のチャネル幅を制御するゲート領域と

を有する縦型JFETである

ことを特徴とする固体撮像装置。

### 【請求項2】

請求項1に記載の固体撮像装置において、

前記チャネル領域の底に位置するドレイン部は、前記半導体基板と同一の導電型であり、前記半導体基板と電気的に接触して基板電位が印加される

ことを特徴とする固体撮像装置。

#### 【請求項3】

請求項1または請求項2に記載の固体撮像装置において、

前記JFETに縦型構造を採用したことにより、横型JFETよりも単位画素内における占有面積を縮小し、その縮小分によって前記単位画素内に隙間箇所を確保し、

前記JFETに隣接する前記受光素子は、前記隙間箇所に受光領域を拡張して形成される

ことを特徴とする固体撮像装置。

#### 【請求項4】

請求項3に記載の固体撮像装置において、

前記隙間箇所に受光領域を拡張することにより、前記受光領域は略十字形状または略丁字形状をなす

ことを特徴とする固体撮像装置。

### 【請求項5】

請求項3ないし請求項4のいずれか1項に記載の固体撮像装置において、

前記隙間箇所を挟んで前記JFETの反対側に、前記ゲート領域の電荷をリセットする リセットドレインを配置し、

前記リセットドレインの電荷排出線を基板垂直方向に配線することにより、前記電荷排出線を階段状に配線する場合よりも、前記リセットドレインの単位画素内における占有面積を縮小し、

前記JFETおよび前記リセットドレイン双方の面積縮小に伴って前記隙間箇所を拡大し、前記隙間箇所に延在する前記受光領域を更に拡げた

ことを特徴とする固体撮像装置。

#### 【発明の詳細な説明】

### 【技術分野】

### [ 0 0 0 1 ]

本発明は、単位画素内にJFET(接合型電界効果トランジスタ)を備えた固体撮像装置に関する。

### 【背景技術】

### [0002]

従来、単位画素内に増幅素子を個別に備え、信号電荷を増幅素子で増幅(例えば電流増幅)してから出力するタイプの固体撮像装置が提案されている。

10

20

30

40

下記の特許文献1には、このような増幅素子として、JFETを単位画素内に備えた固 体撮像装置が開示されている。

[0003]

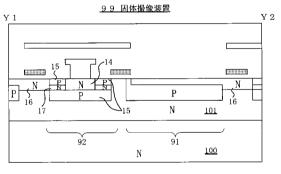

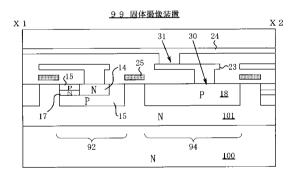

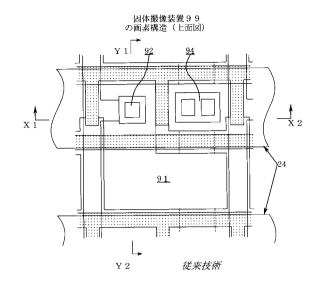

図8は、この固体撮像装置99の画素構造を示す上面図である。

図 9 は、図 8 中に示す Y 1 - Y 2 の断面図である。

図 1 0 は、図 8 中に示す X 1 - X 2 の断面図である。

これらの図において、固体撮像装置99は、N型半導体基板100を土台に形成される 。 こ の N 型 半 導 体 基 板 1 0 0 の 表 面 に は 、 N 型 エ ピ タ キ シ ャ ル 層 1 0 1 が 設 け ら れ る 。 こ のN型エピタキシャル層101の表面には、複数の単位画素が形成される。これらの単位 画素は、受光素子91、JFET92、およびリセットドレイン94を備えて概略構成さ れる。

[0004]

この内、JFET92は、半導体面に平行して横向きに電流経路を形成するN型チャネ ル領域 1 7 と、その N 型チャネル領域 1 7 を挟む P 型ゲート領域 1 5 と、 N 型ソース領域 14と、N型ドレイン領域16とによって構成される。(以下、本明細書では、このJF ET92のように、チャネル領域が半導体面に沿って主として横向きに形成されたJFE Tを、横型JFETと呼ぶ。)

[00005]

一方、リセットドレイン 9 4 は、 P 型電荷排出領域 1 8 と、遮光配線 2 4 とを、接続線 2 3 で接続することによって構成される。この接続線2 3 による接続経路は、図10 に示 すようにコンタクトホール30,31の位置をずらすことによって、階段状にレイアウト される。

また、JFET92とリセットドレイン94との中間には、リセット電極25が設けら れる。このリセット電極25の電圧制御により、P型ゲート領域15内の不要電荷を、P 型電荷排出領域18に排出することができる。

【特許文献1】特開平11-87680号公報(図1~3)

【発明の開示】

【発明が解決しようとする課題】

[0006]

図8に示した固体撮像装置99の例では、JFET92およびリセットドレイン94が 、単位画素のほぼ半分の面積を占有する。そのため、受光素子91の占有面積は、単位画 素 の 残 り 半 分 程 度 の 矩 形 範 囲 ま で 狭 め ら れ る 。 そ の 結 果 、 固 体 撮 像 装 置 9 9 の 受 光 効 率 が 低下するという点で改善の余地があった。

そこで、本発明では、固体撮像装置において、受光素子の占有面積拡大に有効な単位画 素の素子構造を提供することを目的とする。

【課題を解決するための手段】

[0007]

《 1 》

本発明の固体撮像装置は、複数の単位画素を半導体基板に形成する。この単位画素は、 入射光に応じて信号電荷を生成する受光素子と、この受光素子で生成された信号電荷を取 り込み、信号電荷に応じた画素信号を出力するJFET(接合型電界効果トランジスタ)

特に、このJFETは、下記構成を備えた縦型JFETである。

(a)半導体基板の基板深さ方向に電流経路を配置したチャネル領域。

( b )このチャネル領域を挟み込むように深さ方向に形成され、信号電荷を蓄積し、蓄積 した信号電荷によってチャネル領域のチャネル幅を制御するゲート領域。

[0008]

《 2 》

なお好ましくは、JFETのドレイン部は、チャネル領域の底に位置する。このドレイ ン部は半導体基板と同一の導電型であり、半導体基板と電気的に接触することにより基板

20

30

40

電位が印加される。

# [0009]

《 3 》

また好ましくは、JFETに縦型構造を採用することにより、横型JFETよりも単位画素内における占有面積を縮小する。その縮小分によって単位画素内に隙間箇所を確保する。JFETに隣接する受光素子は、この隙間箇所に受光領域を拡張して形成される

[0010]

《 4 》

なお好ましくは、この隙間箇所に受光領域を拡張することにより、受光領域を略十字形状または略T字形状とする。

10

[0011]

**《** 5 **》**

また好ましくは、この隙間箇所を挟んでJFETの反対側に、ゲート領域の電荷をリセットするリセットドレインを配置する。このリセットドレインの電荷排出線を基板垂直方向に配線することにより、電荷排出線を階段状に配線する場合よりも、単位画素内における占有面積を縮小する。このようにして、JFETおよびリセットドレイン双方の面積縮小によって、隙間箇所を拡大する。その結果、隙間箇所に延在する受光領域を更に拡げる

### 【発明の効果】

### [0012]

(1)

本発明では、単位画素内に縦型JFETを配置する。すなわち、JFETのチャネル領域は、半導体基板の基板深さ方向に配置される。また、JFETのゲート領域は、このチャネル領域を挟み込むように、主として深さ方向に形成される。

この縦型JFETは、素子構造が基板深さ方向にレイアウトされるため、従来の横型JFETに比べて横の拡がりが小さくなり、占有面積を縮小できる。

例えば、このJFETの面積縮小分で、受光素子の受光領域を拡大することにより、固体撮像装置の受光効率向上(例えば感度向上)を実現することができる。

また例えば、このJFETの面積縮小分だけ単位画素を面積縮小することにより、固体撮像装置の受光効率(例えば感度)を維持したまま、固体撮像装置の画素数を増やすことが可能になる。

[0013]

(2)

ところで、従来の横型JFETでは、横向きに延びるチャネル領域の端にドレイン領域(図9中のN型ドレイン領域16)を設けている。そのため、横型JFETのドレイン領域も横に拡がることになり、この点からも横型JFETの占有面積は大きくなった。

そこで、本発明では、縦型JFETのドレイン部を、チャネル領域の底に位置させることが好ましい。この場合、チャネル領域の底に、ドレイン部の全部または一部を収めることが可能になり、縦型JFETの占有面積を更に縮小できる。

さらに、このドレイン部は基板の深奥部に位置するため、ドレイン部を半導体基板と一体化させることが容易である。そこで、本発明では、半導体基板からドレイン部に基板電位を印加することが好ましい。この場合、基板表面側からドレイン部に電圧供給する配線構造などを省くことが可能になり、単位画素内における縦型JFETの占有面積を更に縮小することができる。

### [0014]

(3)

上述したように、縦型JFETは、従来の横型JFETよりも単位画素内における占有面積を縮小することが可能になる。そこで、本発明では、この縮小分によって単位画素内に隙間箇所を確保し、受光素子の受光領域を拡張することが好ましい。この場合、固体撮像装置の受光効率を高めることが可能になる。

20

30

40

10

20

30

40

50

### [0015]

(4)

なお、本発明では、受光領域を拡張して略十字形状または略T字形状にすることが好ましい。この場合、受光領域の縦横比を等方に近づけることが可能になる。その結果、オンチップマイクロレンズの集光効率が改善され、撮像エリア周辺におけるシェーディングを抑制できる。

# [0016]

(5)

また、本発明では、リセットドレインの電荷排出線を基板垂直方向に配線することにより、リセットドレインの占有面積を縮小することが好ましい。この場合、縦型JFETとリセットドレインの中間に隙間箇所を大きく確保できる。その結果、その隙間箇所に延在する受光領域を更に拡げ、固体撮像装置の受光効率を一段と高めることができる。

【発明を実施するための最良の形態】

# [0017]

《第1実施形態》

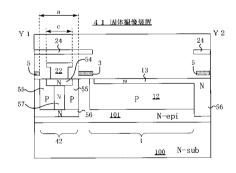

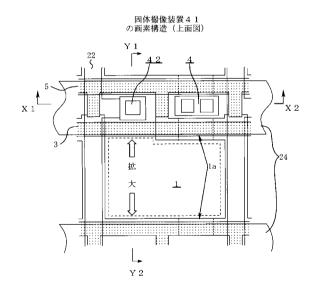

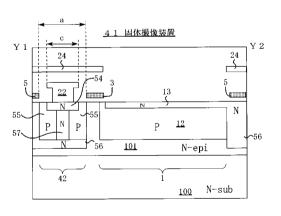

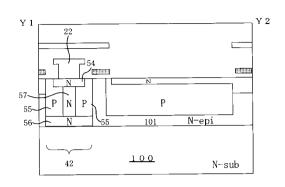

- 図1は、第1実施形態における固体撮像装置41の画素構造を示す上面図である。

- 図2は、図1中に示すY1-Y2箇所の断面図である。

- 図3は、図1中に示すX1-X2箇所の断面図である。

これら図において、固体撮像装置41は、高濃度のN型半導体基板100を土台に形成される。このN型半導体基板100の受光面側には、低濃度のN型エピタキシャル層10 1が設けられる。このN型エピタキシャル層101の表面は、複数の単位画素に区分される。これらの単位画素の1つ1つは、縦型JFET42、受光素子1、およびリセットドレイン4から概略構成される。

[ 0 0 1 8 ]

まず、縦型JFET42は、下記の素子構造を有する。

- ( a ) N 型ソース領域 5 4 ・・N 型エピタキシャル層 1 0 1 の表面側に形成される。

- ( b ) N 型チャネル領域 5 7 ・・N 型ソース領域 5 4 の底から基板深さ方向に形成される。この N 型チャネル領域 5 7 の長さは、例えば 3 μ m 以上に設定することが好ましい。

- ( c ) P型ゲート領域 5 5 ・・N型チャネル領域 5 7 の周囲を対称に取り囲むように形成される。

- (d) N型ドレイン領域 5 6・・N型チャネル領域 5 7の底に位置する。なお、単位画素の境界域にN型ドレイン領域 5 6を延在させることにより、N型ドレイン領域 5 6を単位画素の分離領域に兼用してもよい。

# [ 0 0 1 9 ]

一方、受光素子1は、N型エピタキシャル層101および埋込P型領域12のPN接合と、受光素子1の表面空乏化を阻止する表面N型層13とによって構成される。

また、リセットドレイン 4 は、 P 型電荷排出領域 1 8 と、遮光配線 2 4 とを、接続線 2 3 で接続することによって構成される。

[0020]

その他、固体撮像装置41には、転送電極3、垂直信号線22、およびリセット電極5などが設けられる。

この転送電極3は、絶縁膜を介して、埋込P型領域12とP型ゲート領域55との間に電位を印加する。この転送電極3の電位制御により、埋込P型領域12からP型ゲート領域55へ信号電荷が転送される。

転送された信号電荷は、P型ゲート領域55において蓄積される。この信号電荷の蓄積量に応じて、N型チャネル領域57内のチャネル幅が変化する。

#### [0021]

一方、N型ソース領域54は、垂直信号線22を介して、不図示の定電流源に接続される。また、N型ドレイン領域56には、定電位が印加される。その結果、縦型JFET4 2は、一種のソースホロワ回路として作用し、信号電荷の蓄積量に応じた画素信号を垂直

20

30

40

50

信号線22に出力する。

# [ 0 0 2 2 ]

また、リセット電極 5 は、絶縁膜を介して、P型ゲート領域 5 5 とP型電荷排出領域 1 8 との間に電位を印加する。このリセット電極 5 の電位制御により、P型ゲート領域 5 5 の不要電荷を、P型電荷排出領域 1 8 に排出することができる。

さらに、固体撮像装置41には、オーバーフロー制御領域1aが設けられ、受光素子1から溢れた過剰電荷を、リセットドレイン4へ排出する。

### [0023]

「発明との対応関係]

以下、発明と第1実施形態との対応関係について説明する。なお、ここでの対応関係は、参考のために一解釈を例示するものであり、本発明を徒らに限定するものではない。

請求項記載の受光素子は、受光素子1に対応する。

請求項記載の縦型JFETは、縦型JFET42に対応する。

請求項記載のチャネル領域は、N型チャネル領域57に対応する。

請求項記載のゲート領域は、P型ゲート領域55に対応する。

### [0024]

「縦型JFET42の製造方法]

次に、縦型JFET42の製造方法を説明する。なお、ここでは説明を簡明にするため、公知のフォトリソ工程などは説明から省略する。

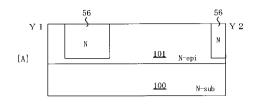

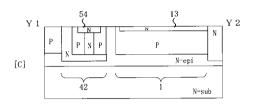

図4[A]~[C]は、縦型JFET42の製造工程の一例を示す図である。

#### [0025]

まず、この図4[A]に示すように、高濃度のN型半導体基板100の表面に、低濃度のN型エピタキシャル層101を3~10μm程度の厚さでエピタキシャル成長させる。このN型エピタキシャル層101に対して、リンなどを3μm以上の深さまでイオン注入することにより、N型ドレイン領域56を形成する。

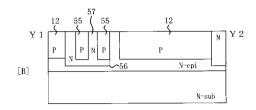

### [0026]

続いて、図4[B]に示すように、ボロンなどをイオン注入することにより、P型ゲート領域55および埋込P型領域12を形成する。このとき、P型ゲート領域55の中央部分をマスクで覆うことにより、P型ゲート領域55の中央部分にN型領域を残し、N型チャネル領域57とする。なお、この中心箇所に改めてN型不純物をイオン注入することにより、N型チャネル領域57を確実に形成してもよい。

# [0027]

さらに、図4[C]に示すように、ヒ素などをイオン注入することにより、N型ソース領域54および表面N型層13を形成する。

続いて、図2に示すように、リセット電極5および垂直信号線22などの配線構造を形成することにより、縦型JFET42が完成する。

### [0028]

[第1実施形態の効果など]

第1実施形態では、縦型JFET42を単位画素内に設ける。この縦型JFET42では、N型ソース領域54、N型チャネル領域57、およびN型ドレイン領域56を基板深さ方向に配置するため、従来の横型JFETよりも横の拡がりが小さく、占有面積を縮小できる。例えば、縦型JFET42の占有面積(図2,図3に示すaxb)を、垂直信号線22のコンタクトホールの面積(図2,図3に示すcxd)近くまで縮小することが可能になる。

#### [0029]

第1実施形態では、図2に示す長さaの縮小分だけ、受光素子1の受光領域の短辺側を拡幅する(図1参照)。その結果、固体撮像装置41の受光効率(例えば感度)を高めることが可能になる。

### [0030]

更に、第1実施形態では、N型チャネル領域57に対して軸対称にP型ゲート領域55

を設ける。その結果、N型チャネル領域 5 7 にはほぼ対称な電界が作用し、ほぼ軸対称なチャネル(電流経路)を形成することができる。

#### [0031]

このチャネルの断面は、P型ゲート領域 5 5 内の信号電荷の量に応じて、ほぼ軸対称性に拡大縮小する。したがって、チャネル断面が局地的に狭くなってピンチオフするといった不具合が殆どなくなり、ピンチオフ余裕を拡げることができる。その結果、ピンチオフ電圧のバラツキが小さくなり、ピンチオフ余裕が極端に狭いために生じる欠陥画素の数を低減することができる。

### [0032]

さらに、チャネルの断面がほぼ軸対称に拡大縮小することから、ドレイン電圧 - 電流特性などによる信号歪みが小さくなり、(例えばソースホロワの帰還ゲインを小さくしても)歪みの少ない良質な画素信号を得ることができる。

次に、別の実施形態について説明する。

### [0033]

### 《第2実施形態》

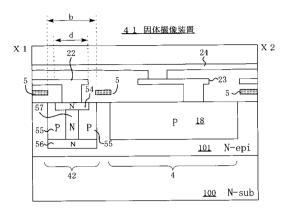

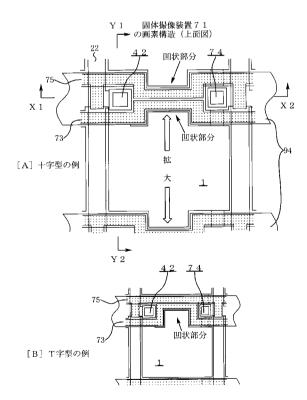

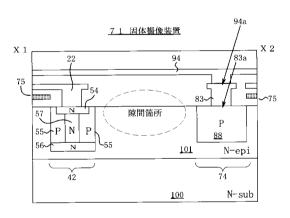

図5は、第2実施形態における固体撮像装置71の画素構造を示す上面図である。

図6は、図5中に示すX1-X2箇所の断面図である。

固体撮像装置71の単位画素は、縦型JFET42、受光素子1、およびリセットドレイン74を備える。

このリセットドレイン74は、P型電荷排出領域88と、遮光配線94とを、接続線83で接続することによって構成される。このとき、接続線83のコンタクトホール83aと、遮光配線94のコンタクトホール94aとの位置を縦に揃える。その結果、P型電荷排出領域88の電荷排出線は、基板垂直方向にほぼ一直線となる。したがって、従来の階段状接続(図10参照)に比べて配線スペースの無駄が少なくなり、リセットドレイン74の占有面積を縮小することができる。

### [0034]

一方、 縦型 J F E T 4 2 については、第 1 実施形態と同様の縦型構造にすることにより 、占有面積を縮小する。

さらに、縦型JFET42およびリセットドレイン74との中間には、リセット電極(図10に示すリセット電極25)を形成しない。代わりに、単位画素の境界域にリセット電極75が設けられる。このリセット電極75の電位制御により、P型ゲート領域55内の不要電荷は、単位画素の境界域を超えて、隣接画素のP型電荷排出領域88に排出される。

# [0035]

上述した構成により、縦型JFET42とリセットドレイン74との中間には、図6に示すような大きな隙間箇所を無理なく確保することができる。

この隙間箇所をなるべく基板表面に露出させるように、遮光配線94、リセット電極7 5、および転送電極73に、図5に示すような凹状部分を設ける。受光素子1の受光領域 は、この凹状部分まで拡張してレイアウトできる。

#### [0036]

このとき、図 5 [ A ]に示すように、受光領域の両方の側辺を拡張することにより、十字型の受光領域を得ることができる。

また、図 5 [ B ]に示すように,受光領域の片側の側辺のみを拡張することにより、 T 字型の受光領域を得ることができる。

### [0037]

[発明との対応関係]

以下、発明と第2実施形態との対応関係について説明する。なお、ここでの対応関係は、参考のために一解釈を例示するものであり、本発明を徒らに限定するものではない。 請求項記載の受光素子は、受光素子1に対応する。

請求項記載の縦型JFETは、縦型JFET42に対応する。

50

40

20

請 求 項 記 載 の チャ ネ ル 領 域 は 、 N 型 チャ ネ ル 領 域 5 7 に 対 応 す る 。

請求項記載のゲート領域は、P型ゲート領域55に対応する。

請求項記載のリセットドレインは、リセットドレイン74に対応する。

請求項記載の電荷排出線は、接続線83および遮光配線94に対応する。

#### [0038]

「第2実施形態の効果など]

以上説明した構成により、第2実施形態においても、第1実施形態と同一の効果を得ることができる。

### [0039]

さらに、第2実施形態では、縦型JFET42およびリセットドレイン74の双方を、それぞれコンタクトホール1個分の面積まで最小化する。したがって、単位画素内において、最大限まで受光領域を拡大できる。これにより、現行の固体撮像装置はもとより、今後、高画素化、画素縮小が進んでも、本発明による方法を用いることによって、高い受光効率を維持しつつ、固体撮像装置に画質向上をもたらすことができる。

#### [0040]

また、第2実施形態では、受光領域を十字型またはT字型に拡大する。その結果、受光領域の縦横比を等方に近づけることができる。この場合、不図示のオンチップマイクロレンズの集光効率が向上し、撮像エリア周辺におけるシェーディングを抑制できる。

次に、別の実施形態について説明する。

### [0041]

《第3実施形態》

図7は、第3実施形態における固体撮像装置の画素断面図である。

第3実施形態の構成上の特徴は、縦型JFET42のN型ドレイン領域56が、高濃度のN型半導体基板100まで到達している点である。なお、その他の構成については、第1実施形態または第2実施形態と同一のため、重複説明を省略する。

### [0042]

このような構成は、例えば、N型ドレイン領域56のイオン注入深さをコントロールすることにより実現できる。また例えば、N型エピタキシャル層101を若干薄く形成することによっても実現できる。

## [0043]

このN型ドレイン領域 5 6 は、高濃度のN型半導体基板 1 0 0 と電気的に接触することにより、N型半導体基板 1 0 0 の基板電位が印加される。その結果、基板表面側からN型ドレイン領域 5 6 に電圧供給する配線を省くことが可能になり、単位画素内における縦型JFET 4 2 の占有面積を更に縮小することができる。

### [0044]

### 《実施形態の補足事項》

なお、上述した実施形態では、縦型JFETの面積縮小分を用いて受光領域を拡大し、 固体撮像装置の受光効率の向上を達成している。しかしながら、本発明はこれに限定され るものではない。例えば、縦型JFET42の面積縮小分を用いて単位画素を縮小するこ とにより、固体撮像装置の受光効率を維持したまま、高画素化を達成してもよい。

# [ 0 0 4 5 ]

また、上述した第3実施形態では、縦型JFET42のN型ドレイン領域56に基板電位を印加する場合について説明した。しかしながら、本発明はこれに限定されるものではない。例えば、基板裏面側からの配線によりN型ドレイン領域56に電位を印加してもよい。また、撮影エリア外の周辺回路から、N型ドレイン領域56に電位を印加してもよい。また、N型チャネル領域57の片端(ドレイン)をN型半導体基板100と直に接触させてもよい。この場合、図7に示すN型ドレイン領域56の形成工程を省略することができる。

### [0046]

なお、上述した実施形態では、説明を簡明にするため、半導体の導電型を明記した。し

20

40

50

かしながら、本発明はこれらの導電型に限定されるものではない。例えば、導電型の一部 または全部を逆にすることも容易である。

[0047]

また、上述した実施形態で上げた素子構造のサイズは特定の画素サイズの場合についての例示であり、画素サイズやデザインルールに応じてそのサイズも拡大・縮小することが好ましい。

[0048]

なお、上述した実施形態では、純粋に縦型チャネル領域のみで構成する場合について説明した。しかしながら、本発明はこれに限定されるものではない。例えば、主たる縦型チャネル領域の一部を屈曲するなどして、占有面積拡大が実質的に問題とならない範囲で、部分的に横型チャネル領域を設けるなどしても勿論かまわない。

[0049]

さらに、本発明は、その精神またはその主要な特徴から逸脱することなく、他のいろいるな形で実施することができる。そのため、上述した実施形態は、あらゆる点で単なる例示に過ぎず、限定的に解釈してはならない。本発明は、特許請求の範囲によって示されるものであって、本発明は明細書本文にはなんら拘束されない。さらに、特許請求の範囲の均等範囲に属する変形や変更は、全て本発明の範囲内である。

【産業上の利用可能性】

[0050]

以上説明したように、本発明は、固体撮像装置などに利用可能な技術である。

【図面の簡単な説明】

[0051]

- 【図1】第1実施形態における固体撮像装置41の画素構造を示す上面図である。

- 【図2】図1中に示すY1-Y2箇所の断面図である。

- 【図3】図1中に示すX1-X2箇所の断面図である。

- 【図4】縦型JFET42の製造工程の一例を示す図である。

- 【図5】第2実施形態における固体撮像装置71の画素構造を示す上面図である。

- 【図6】図5中に示すX1・X2箇所の断面図である。

- 【図7】第3実施形態における固体撮像装置の画素断面図である。

- 【図8】従来の固体撮像装置の画素構造を示す上面図である。

- 【図9】従来の固体撮像装置の画素断面図である。

- 【図10】従来の固体撮像装置の画素断面図である。

【符号の説明】

[0052]

- 1 受光素子

- 3 転送電極

- 5 リセット電極

- 1 2 埋込 P 型 領 域

- 1 3 表面 N 型層

- 1 8 P型電荷排出領域

- 22 垂直信号線

- 2 3 電荷排出線

- 2 4 遮光配線

- 25 リセット電極

- 30 コンタクトホール

- 3 1 コンタクトホール

- 4 1 固体撮像装置

- 4 2 縦型JFET

- 4 2 縦型JFET

- 5 4 N型ソース領域

10

20

30

40

- 5 5 P型ゲート領域

- 5 6 N型ドレイン領域

- 5 7 N型チャネル領域

- 7 1 固体撮像装置

- 74 リセットドレイン

- 7 5 リセット電極

- 8 3 接続線

- 88 P型電荷排出領域

- 9 4 遮光配線

- 9 9 固体撮像装置

- 100 N型半導体基板

- 101 N型エピタキシャル層

【図1】 【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図9】

【図10】