(19) **日本国特許庁(JP)**

## (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2006-311144 (P2006-311144A)

(43) 公開日 平成18年11月9日(2006.11.9)

5 J O 2 2

(51) Int.C1.

. . . . . .

テーマコード (参考)

HO3M 1/74 HO3M 1/38 (2006.01) (2006.01) HO3M 1/74 HO3M 1/38

FI

審査請求 未請求 請求項の数 9 OL (全 14 頁)

(21) 出願番号 (22) 出願日 特願2005-130524 (P2005-130524) 平成17年4月27日 (2005.4.27)

(71) 出願人 000001889

三洋電機株式会社

大阪府守口市京阪本通2丁目5番5号

(74)代理人 100105924

弁理士 森下 賢樹

(72) 発明者 高野 洋

大阪府守口市京阪本通2丁目5番5号 三

洋電機株式会社内

F ターム (参考) 5J022 AA02 AB04 BA08 CA10 CB02

CE08 CF01 CF07

(54) 【発明の名称】デジタルアナログ変換器、およびそれを用いた逐次比較型アナログデジタル変換器

#### (57)【要約】

【課題】 デジタルアナログ変換器の出力電圧範囲は、 供給される電源電圧のレベルに応じて、決定されがちで ある。

【解決手段】 デジタルアナログ変換器10にて、それぞれ重み付けされるている複数の容量C10~C36は、一端がコンパレータ30の入力端子Aに繋がる経路に対して並列に接続され、他端が電源線またはグラウンド線に接続され得る。スイッチS10~S32は、対応する容量C10~C32の他端を電源線またはグラウンド線に選択的に接続する。電源電圧とグラウンド電位との間の電圧範囲内にて、本デジタルアナログ変換器10の出力電圧範囲の大きさおよび位置が所望の値に設定されるよう、複数の容量C10~C36による容量分割比の取り得る範囲が設定される。

【選択図】 図1

#### 【特許請求の範囲】

#### 【請求項1】

高電位側基準電圧と低電位側基準電圧とをもとに、分解能に対応した数の電圧レベルを 生成可能なデジタルアナログ変換器であって、

一端が出力ノードに対して並列に接続され、他端が前記高電位側基準電圧および前記低電位側基準電圧のいずれかに接続される、それぞれ重み付けされた複数の容量と、

前記複数の容量の少なくとも一つの容量における接続先を、前記高電位側基準電圧と前記低電位側基準電圧との間で切り替えるためのスイッチと、を備え、

前記高電位側基準電圧と前記低電位側基準電圧との間の電圧範囲内にて、本デジタルアナログ変換器の出力電圧範囲の大きさおよび位置が所定の目標値に設定されるよう、前記複数の容量による容量分割比の取り得る範囲が設定されることを特徴とするデジタルアナログ変換器。

#### 【請求項2】

前記複数の容量は、本デジタルアナログ変換器の出力電圧範囲の大きさを調整するための複数の調整用容量と、所定の分解能でデジタル信号にした場合の各桁に対応する電圧幅を生成するための複数の容量と、を含むことを特徴とする請求項1に記載のデジタルアナログ変換器。

#### 【請求項3】

それぞれ重み付けされた複数の容量を利用したデジタルアナログ変換器であって、 各桁に対応する電圧幅を生成するための容量をそれぞれ複数設けたことを特徴とするデジタルアナログ変換器。

#### 【請求項4】

初期状態にて、各桁に対応する電圧幅を生成するための複数の容量のうち、一部の容量が高電位側基準電圧に接続され、他の容量が低電位側基準電圧に接続され、容量分割による本デジタルアナログ変換器の初期出力電圧が生成されることを特徴とする請求項3に記載のデジタルアナログ変換器。

#### 【請求項5】

本デジタルアナログ変換器の出力電圧範囲の大きさを調整するための調整用容量をさらに備えることを特徴とする請求項3または4に記載のデジタルアナログ変換器。

#### 【請求項6】

前記調整用容量は複数設けられ、初期状態にて、その一部の容量が高電位側基準電圧に接続され、他の容量が低電位側基準電圧に接続され、容量分割による本デジタルアナログ変換器の初期出力電圧が所定の目標値に設定されることを特徴とする請求項 5 に記載のデジタルアナログ変換器。

#### 【請求項7】

前記複数の調整用容量のそれぞれの容量値が独立の変数として調整されることにより、本デジタルアナログ変換器の出力電圧範囲の位置が調整されることを特徴とする請求項2または6に記載のデジタルアナログ変換器。

#### 【請求頃8】

請求項1から7のいずれかに記載のデジタルアナログ変換器の出力電圧をリファレンス 40 電圧として利用することを特徴とする逐次比較型アナログデジタル変換器。

#### 【請求項9】

請求項1から7のいずれかに記載のデジタルアナログ変換器と、

前記デジタルアナログ変換器の出力電圧と、入力アナログ信号とを比較するコンパレータと、

前記コンパレータの出力結果に応じて、前記デジタルアナログ変換器の容量分割比を変化させる逐次比較レジスタと、

を備えることを特徴とする逐次比較型アナログデジタル変換器。

#### 【発明の詳細な説明】

#### 【技術分野】

50

10

20

#### [0001]

本発明は、容量分割における分割比率を調整することにより、所望のアナログ信号を生成するデジタルアナログ変換器、およびそれを用いた逐次比較型アナログデジタル変換器に関する。

#### 【背景技術】

#### [0002]

カメラ、通信機、および家電製品など多くの電子機器がデジタル化してきている。しかしながら、自然界は音声や映像などアナログ情報に満ちているため、アナログ信号とデジタル信号との間の変換技術が益々重要になってきている。アナログデジタル変換器(以下、AD変換器と適宜表記する。)には多様な方式が存在するが、その中の一つに逐次比較型AD変換器がある(例えば、非特許文献1参照。)。

#### [0003]

逐次比較型 A D 変換器は、逐次比較レジスタ(S A R; Succesive Approximation re Register)、デジタルアナログ変換器(以下、D A 変換器と適宜表記する。)、およびコンパレータを含む。当該コンパレータは、アナログ入力電圧と当該 D A 変換器からのアナログ出力電圧とを比較する。

【非特許文献 1 】 Jean Sauerbrey etc、「A 0.5V,1μW Successive Approximation ADC」、ESSCIRC2002、ρ. 2 4 7 - 2 5 0

## 【発明の開示】

【発明が解決しようとする課題】

#### [0004]

コンパレータには入力電圧範囲が存在する。したがって、上記コンパレータにリファレンス電圧を供給する上記 D A 変換器の出力電圧範囲は、その入力電圧範囲に対応させる必要がある。上記 D A 変換器に供給されるべき高電位側基準電圧および低電位側基準電圧の少なくとも一方のレベルを調整するか、当該 D A 変換器の出力電圧範囲に対応するコンパレータを使用する必要があった。

#### [0005]

上記高電位側基準電圧に電源電圧 V D D、上記低電位側基準電圧にグラウンド電位 G N D を採用した場合、上記 D A 変換器の出力電圧範囲は、基本的に電源電圧 V D D からグラウンド電位の範囲となる。この場合、この電圧範囲に対応した入力電圧範囲を持つコンパレータを用意する必要がある。

#### [0006]

これに対し、DA変換器に供給される基準電圧を調整して両電圧範囲を対応させようとすると、DA変換器において低電源電圧の条件下で中間的な基準電圧がスイッチを通過電ではPMOSを介して、グラウンド電位はNMOSを介して回路内部に供給されるが、電圧はPMOSを介して、グラウンド電位はNMOSを介して回路内部に供給されるが、低電源電圧のとき、電源電圧とグラウンド電位間の中間的な電位を利用すると、PMOSおよびNMOSのカットオフ領域に近づくため、速度が遅くなったり、正確な電位が伝わりにくくなることがある。アナログ回路がデジタル回路と同一基板上に混載されることがりにくくなることがある。アナログ回路がデジタル回路と同一基板上に混載されることがにより、低電源電圧への対応はますます重要になってきている。また、広い力電圧範囲を持つコンパレータ方式はいくつか提案されているが、回路が複雑でコスト増につながる。この点、回路構成が簡素で低電源電圧下で動作可能であり、かつ所望の出力電圧範囲を設定可能なDA変換器があれば、逐次比較型AD変換器を効率的に設計することができる。

#### [0007]

本発明はこうした状況に鑑みなされたものであり、その目的は、所与の基準電圧のレベルに関係なく所望の出力電圧範囲を設定可能なDA変換器、およびそれを用いた逐次比較型AD変換器を提供することにある。

#### 【課題を解決するための手段】

#### [0008]

50

20

30

20

30

40

50

上記課題を解決するために、本発明のある態様のデジタルアナログ変換器は、高電位側基準電圧と低電位側基準電圧とをもとに、分解能に対応した数の電圧レベルを生成可能なデジタルアナログ変換器であって、一端が出力ノードに対して並列に接続され、他端が高電位側基準電圧および低電位側基準電圧のいずれかに接続される、それぞれ重み付けされた複数の容量と、複数の容量の少なくとも一つの容量における接続先を、高電位側基準電圧と低電位側基準電圧との間で切り替えるためのスイッチと、を備える。高電位側基準電圧と低電位側基準電圧との間の電圧範囲内にて、本デジタルアナログ変換器の出力電圧範囲の大きさおよび低電位側基準電圧のして、本デジタルアナログ変換器の出力電圧範囲の大きさおよび低電位側基準電圧のして、高電位側基準電圧および低電位側基準電圧のレベルに関係なく、所望の出力電圧範囲を設定することができる。

[0009]

複数の容量は、本デジタルアナログ変換器の出力電圧範囲の大きさを調整するための複数の調整用容量と、所定の分解能でデジタル信号にした場合の各桁に対応する電圧幅を生成するための複数の容量と、を含んでもよい。この態様によると、調整用容量を設けたことにより、容量分割比の取り得る範囲を調整することができ、所望の出力電圧範囲を設定することができる。

[ 0 0 1 0 ]

本発明の別の態様もまた、デジタルアナログ変換器である。このデジタルアナログ変換器は、それぞれ重み付けされた複数の容量を利用したデジタルアナログ変換器であって、各桁に対応する電圧幅を生成するための容量をそれぞれ複数設けた。この態様によると、取り得る容量分割比の数を多くすることができるため、総容量の面積を小さくすることができる。

[0011]

初期状態にて、各桁に対応する電圧幅を生成するための複数の容量のうち、一部の容量が高電位側基準電圧に接続され、他の容量が低電位側基準電圧に接続され、容量分割による本デジタルアナログ変換器の初期出力電圧が生成されてもよい。この態様によると、初期出力電圧に対応する電圧幅を生成するための容量を別途に設けなくても、初期出力電圧を生成することができる。

[0012]

本デジタルアナログ変換器の出力電圧範囲の大きさを調整するための調整用容量をさらに備えてもよい。この態様によると、高電位側基準電圧および低電位側基準電圧のレベルに関係なく、所望の出力電圧範囲を設定することができる。例えば、出力電圧範囲を、高電位側基準電圧と低電位側基準電圧との間の電圧範囲より狭めることができる。

[0013]

調整用容量は複数設けられ、初期状態にて、その一部の容量が高電位側基準電圧に接続され、他の容量が低電位側基準電圧に接続され、容量分割による本デジタルアナログ変換器の初期出力電圧が所定の目標値に設定されてもよい。複数の調整用容量のそれぞれの容量値が独立の変数として調整されることにより、本デジタルアナログ変換器の出力電圧範囲の位置が調整されてもよい。この態様によると、出力電圧範囲の大きさだけでなく、位置も調整することができ、さらに柔軟に出力電圧範囲を設定することができる。

[0014]

本発明のさらに別の態様は、逐次比較型アナログデジタル変換器である。この逐次比較型アナログデジタル変換器は、デジタルアナログ変換器の出力電圧をリファレンス電圧として利用する。この態様によると、逐次比較型アナログデジタル変換器のリファレンス電圧として効率的な範囲の電圧をデジタルアナログ変換器から供給することができる。

[0015]

本発明のさらに別の態様もまた、逐次比較型アナログデジタル変換器である。この逐次比較型アナログデジタル変換器は、デジタルアナログ変換器と、デジタルアナログ変換器の出力電圧と、入力アナログ信号とを比較するコンパレータと、コンパレータの出力結果に応じて、デジタルアナログ変換器の容量分割比を変化させる逐次比較レジスタと、を備

20

30

40

50

える。この態様によると、コンパレータが、その入力電圧範囲に適した範囲のリファレンス電圧を受けることができ、回路全体を効率化することができる。

#### [0016]

なお、以上の構成要素の任意の組合せや、本発明の構成要素や表現を方法、装置、システムなどの間で相互に置換したものもまた、本発明の態様として有効である。

#### 【発明の効果】

#### [0017]

本発明によれば、所与の基準電圧のレベルに関係なく所望の出力電圧範囲を設定可能となる。

#### 【発明を実施するための最良の形態】

#### [0018]

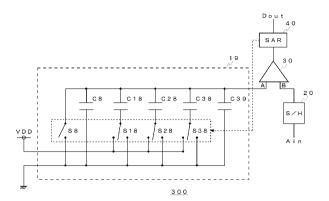

図1は、本発明の実施形態におけるDA変換器10の構成およびそれを含む逐次比較型AD変換器100の構成を示す。逐次比較型AD変換器100は、DA変換器10、サンプル・ホールド回路20、コンパレータ30、および逐次変換レジスタ40を含む。DA変換器10は、電源電圧VDDおよびグラウンド電位GNDの2つの電圧レベルを基に、その分解能に対応した数の電圧レベルを生成する。例えば、3ビットの分解能の場合、少なくとも7つの電圧レベルを生成する。DA変換器10は、生成した電圧レベルをコンパレータ30の第1入力端子Aに供給する。DA変換器10の詳細な構成については後述する。

#### [0019]

サンプル・ホールド回路 2 0 は、入力アナログ信号 A i n を所定のタイミングでサンプルし、所定の期間保持する。逐次比較型 A D 変換器 1 0 0 では A D 変換にある程度の時間が必要なため、その間にアナログ入力信号の値が変化しないようサンプル値を保持する必要がある。サンプル・ホールド回路 2 0 は、保持している値の電圧レベルをコンパレータ 3 0 の第 2 入力端子 B に供給する。なお、サンプル・ホールド回路 2 0 には、スイッチトキャパシタ型などを採用することができる。

#### [0020]

コンパレータ30は、DA変換器10から供給された電圧と、サンプル・ホールド回路20から供給された電圧とを比較し、その比較結果に応じてハイレベル信号またはローレベル信号を逐次変換レジスタ40に出力する。例えば、サンプル・ホールド回路20から供給された電圧がDA変換器10から供給された電圧より高い場合、ハイレベル信号を出力し、低い場合、ローレベル信号を出力してもよい。

#### [0021]

逐次変換レジスタ40は、コンパレータ30の比較結果に応じて、DA変換器10を構成する後述するスイッチ群を制御する。DA変換器10は、この制御にしたがい、新たなリファレンス電圧を生成し、コンパレータ30の第1入力端子Aに供給する。コンパレータ30は、この電圧とサンプル・ホールド回路20から供給されている電圧とを再度比較し、比較結果を再度逐次変換レジスタ40に出力する。この処理を繰り返すことにより、各桁の値を決定していく。逐次変換レジスタ40は、桁ごとにデジタル値を保持する保持レジスタを備えてもよく、すべての桁の値が確定したら、当該保持レジスタの内容を変換後のデジタル信号として外部に出力してもよい。配線の形態に応じて、シリアルに出力してもよいし、パラレルに出力してもよい。

#### [0022]

次に、DA変換器10の詳細な構成について説明する。図1のDA変換器10は、3ビットの分解能でデジタル信号をアナログ信号に変換するものである。コンパレータ30の第1入力端子Aに繋がる経路には、それぞれ重み付けされた複数の容量が並列に接続される。

#### [0023]

調整用第1容量 С 1 0 および調整用第 2 容量 С 1 2 は、 D A 変換器 1 0 の出力電圧範囲の幅および位置を調整する。この調整方法の詳細は後述する。調整用第 1 容量 С 1 0 およ

20

30

40

50

び調整用第2容量C12は、特に断り書きがない限り同じ容量値とする。調整用第1容量C10および調整用第2容量C12の一端は、コンパレータ30の第1入力端子Aに繋がる経路に接続される。調整用第1容量C10の他端は、調整用スイッチS10の一端に接続される。調整用第2容量C12の他端は、低電位側の基準電位を供給するグラウンド線に接続される。

#### [0024]

調整用スイッチ S 1 0 の他端は、高電位側の基準電位を供給する電源線および上記グラウンド線に対して選択的に接続可能な構成である。調整用スイッチ S 1 0 は、逐次変換レジスタ 4 0 からの制御により、調整用第 1 容量 C 1 0 を当該電源線または当該グラウンド線のいずれかに接続する。

[ 0 0 2 5 ]

n - 1 桁第 1 容量 C 2 0 および n - 1 桁第 2 容量 C 2 2 は、主に最上位ビットの次のビットの値を決定するための電圧幅を生成するための容量である。 n - 1 桁第 1 容量 C 2 0 および n - 1 桁第 2 容量 C 2 2 は、同じ容量値であり、調整用第 1 容量 C 1 0 および調整用 2 容量 C 1 2 の容量値の 1 / 2 の値である。 n - 1 桁第 1 容量 C 2 0 および n - 1 桁第 2 容量 C 2 2 の一端は、コンパレータ 3 0 の第 1 入力端子 A に繋がる経路に接続される。それらの他端は、それぞれ n - 1 桁第 1 スイッチ S 2 0 および n - 1 桁第 2 スイッチ S 2 0 一端に接続される。

[0026]

n-1桁第1スイッチS20およびn-1桁第2スイッチS22の他端は、上記電源線および上記グラウンド線に対して選択的に接続可能な構成である。n-1桁第1スイッチS20およびn-1桁第2スイッチS22は、逐次変換レジスタ40からの制御により、n-1桁第1容量C20およびn-1桁第2容量C22を当該電源線または当該グラウンド線のいずれかに接続する。

[0027]

n - 2 桁第 1 容量 C 3 0 、 n - 2 桁第 2 容量 C 3 2 、 n - 2 桁第 3 容量 C 3 4 および n - 2 桁第 4 容量 C 3 6 は、主に最上位ビットから 2 ビット下位のビットの値を決定するための電圧幅を生成するための容量である。図 1 では、最下位ビットの値を決定するための電圧幅を生成するための容量である。 n - 2 桁第 1 容量 C 3 0 、 n - 2 桁第 2 容量 C 3 2 、 n - 2 桁第 3 容量 C 3 4 および n - 2 桁第 4 容量 C 3 6 は、同じ容量値であり、調整用第 1 容量 C 1 0 および調整用第 2 容量 C 1 2 の容量値の 1 / 4 の値である。 n - 2 桁第 1 容量 C 3 0 、 n - 2 桁第 2 容量 C 3 2 、 n - 2 桁第 3 容量 C 3 4 および n - 2 桁第 4 容量 C 3 6 の一端は、コンパレータ 3 0 の第 1 入力端子 A に繋がる経路に接続される。 n - 2 桁第 3 容量 C 3 4 および n - 2 桁第 4 容量 C 3 6 の他端は、上記グラウンド線に接続される。

[0028]

n-2桁第1容量C30およびn-2桁第2容量C32の他端は、それぞれn-2桁第1スイッチS30およびn-1桁第2スイッチS32の一端に接続される。n-2桁第1スイッチS30およびn-1桁第2スイッチS32の他端は、上記電源線および上記グラウンド線に対して選択的に接続可能な構成である。n-2桁第1スイッチS30およびn-2桁第2スイッチS30およびn-2桁第1容量C30およびn-2桁第2容量C32を当該電源線または当該グラウンド線のいずれかに接続する。

[0029]

さらに、コンパレータ 3 0 の第 1 入力端子 A に繋がる経路と上記グラウンド線との間にリセット用スイッチ S 0 が設けられる。リセット用スイッチ S 0 は、オンすることにより、コンパレータ 3 0 の第 1 入力端子 A をグラウンド電位に設定することができる。逐次変換レジスタ 4 0 などからの制御により、オンオフ制御される。

[0030]

次に、本実施形態における逐次比較型AD変換器100の動作について説明する。初期

20

30

40

50

状態にて、DA変換器10は、リセット用スイッチS0がオンで、調整用スイッチS10、n-1桁第1スイッチS20、n-1桁第2スイッチS22、n-2桁第1スイッチS30およびn-2桁第2スイッチS32はすべてグラウンド線に接続される。したがって、DA変換器10全体の容量はディスチャージされ、コンパレータ30の第1入力端子Aはグラウンド電位となる。

#### [0031]

次に、逐次比較型 A D 変換器 1 0 0 にアナログ信号 A i n が入力されると、サンプル・ホールド回路 2 0 は、そのアナログ信号 A i n の電圧を所定のタイミングでサンプリングし、コンパレータ 3 0 の第 2 入力端子 B に供給する。コンパレータ 3 0 の第 2 入力端子 B に供給する。コンパレータ 3 0 の第 2 入力端子 B にサンプリングされた電圧が現れると、リセット用スイッチ S 0 がオフに切り替えられ、調整用スイッチ S 1 0、n - 1 桁第 1 スイッチ S 2 0 および n - 2 桁第 1 スイッチ S 3 0 はすべて上記グラウンド線から上記電源線に切り替えられる。その結果、調整用第 1 容量 C 1 0、n - 1 桁第 1 容量 C 2 0、n - 2 桁第 1 容量 C 3 0 および n - 2 桁第 3 容量 C 3 4 からなる合成容量と、調整用第 2 容量 C 1 2、n - 1 桁第 2 容量 C 2 2、n - 2 桁第 2 容量 C 3 2 および n - 2 桁第 4 容量 C 3 6 からなる合成容量との直列回路が形成される。対をなしている容量の容量値が等しいことを前提とすると、1 対 1 の容量分割となり、コンパレータ 3 0 の第 1 入力端子 A の電圧は、電源電圧 V D D の 1 / 2 の電圧となる。

#### [0032]

次に、コンパレータ30は、DA変換器10から供給される電源電圧VDDの1/2の電圧と、サンプル・ホールド回路20から供給される電圧とを比較する。後者の電圧が前者の電圧以上の場合、ハイレベルの信号を逐次変換レジスタ40に出力し、後者の電圧が前者の電圧未満の場合、ローレベルの信号を出力する。

#### [0033]

逐次変換レジスタ40は、コンパレータ30からの出力信号を最上位ビットの値として保持する。その出力信号がローレベルの信号である場合、 n - 1 桁第2スイッチS22に制御信号を出力して、接続先を上記グラウンド線から上記電源線に切り替える。すると、調整用第1容量C10、 n - 1 桁第1容量C20、 n - 1 桁第2容量C22、 n - 2 桁第1容量C30および n - 2 桁第3容量C34からなる合成容量と、調整用第2容量C12、 n - 2 桁第2容量C32および n - 2 桁第4容量C36からなる合成容量との直列回路が形成される。この場合、5対3の容量分割となり、コンパレータ30の第1入力端子Aは、電源電圧VDDの3/8の電圧となる。

#### [0034]

一方、逐次変換レジスタ40は、コンパレータ30からの出力信号がハイレベルの信号である場合、 n - 1 桁第1スイッチS20に制御信号を出力して、接続先を上記電源線から上記グラウンド線に切り替える。すると、調整用第1容量C10、 n - 2 桁第1容量C30および n - 2 桁第3容量C34からなる合成容量と、調整用第2容量C12、 n - 1 桁第1容量C20、 n - 1 桁第2容量C22、 n - 2 桁第2容量C32および n - 2 桁第4容量C36からなる合成容量との直列回路が形成される。この場合、3対5の容量分割となり、コンパレータ30の第1入力端子Aは、電源電圧VDDの5/8の電圧となる。

## [0035]

次に、最上位ビットがローレベル信号の場合、コンパレータ30は、DA変換器10から供給される電源電圧VDDの3/8の電圧と、サンプル・ホールド回路20から供給されている電圧とを比較する。後者の電圧が前者の電圧以上の場合、ハイレベルの信号を逐次変換レジスタ40に出力し、後者の電圧が前者の電圧未満の場合、ローレベルの信号を出力する。

## [0036]

逐次変換レジスタ40は、コンパレータ30からの出力信号を最上位ビットの次のビットの値として保持する。その出力信号がローレベルの信号である場合、n・2桁第2スイッチS32に制御信号を出力して、接続先を上記グラウンド線から上記電源線に切り替える。すると、調整用第1容量C10、n-1桁第1容量C20、n-1桁第2容量C22

30

40

50

、n-2桁第1容量C30、n-2桁第2容量C32およびn-2桁第3容量C34からなる合成容量と、調整用第2容量C12およびn-2桁第4容量C36からなる合成容量との直列回路が形成される。この場合、11対5の容量分割となり、コンパレータ30の第1入力端子Aは、電源電圧VDDの5/16の電圧となる。

#### [0037]

一方、逐次変換レジスタ40は、コンパレータ30からの出力信号がハイレベルの信号である場合、 n - 2 桁第1スイッチS30に制御信号を出力して、接続先を上記電源線から上記グラウンド線に切り替える。すると、調整用第1容量 C 10、 n - 1 桁第1容量 C 20、 n - 1 桁第2容量 C 22および n - 2 桁第3容量 C 34からなる合成容量と、調整用第2容量 C 12、 n - 2 桁第1容量 C 30、 n - 2 桁第2容量 C 32および n - 2 桁第4容量 C 36からなる合成容量との直列回路が形成される。この場合、9対7の容量分割となり、コンパレータ30の第1入力端子Aは、電源電圧VDDの7/16の電圧となる

## [0038]

次に、最上位ビットがローレベル信号で、その次のビットもローレベル信号の場合、コンパレータ30は、DA変換器10から供給される電源電圧VDDの5/16の電圧と、サンプル・ホールド回路20から供給されている電圧とを比較する。後者の電圧が前者の電圧以上の場合、ハイレベルの信号を逐次変換レジスタ40に出力し、後者の電圧が前者の電圧未満の場合、ローレベルの信号を出力する。

#### [0039]

一方、最上位ビットがローレベル信号で、その次のビットはハイレベル信号の場合、コンパレータ30は、DA変換器10から供給される電源電圧VDDの7/16の電圧と、サンプル・ホールド回路20から供給されている電圧とを比較する。後者の電圧が前者の電圧以上の場合、ハイレベルの信号を逐次変換レジスタ40に出力し、後者の電圧が前者の電圧未満の場合、ローレベルの信号を出力する。

#### [0040]

次に、最上位ビットの次のビットの処理にて、最上位ビットがハイレベル信号の場合、コンパレータ30は、DA変換器10から供給される電源電圧VDDの5/8の電圧と、サンプル・ホールド回路20から供給されている電圧とを比較する。後者の電圧が前者の電圧以上の場合、ハイレベルの信号を逐次変換レジスタ40に出力し、後者の電圧が前者の電圧未満の場合、ローレベルの信号を出力する。

#### [0041]

逐次変換レジスタ40は、コンパレータ30からの出力信号を最上位ビットの次のビットの値として保持する。その出力信号がローレベルの信号である場合、n-2桁第2スイッチS32に制御信号を出力して、接続先を上記グラウンド線から上記電源線に切り替える。この場合、7対9の容量分割となり、コンパレータ30の第1入力端子Aは、電源電圧VDDの9/16の電圧となる。

#### [0042]

一方、逐次変換レジスタ40は、コンパレータ30からの出力信号がハイレベルの信号である場合、n-2桁第1スイッチS30に制御信号を出力して、接続先を上記電源線から上記グラウンド線に切り替える。この場合、5対11の容量分割となり、コンパレータ30の第1入力端子Aは、電源電圧VDDの11/16の電圧となる。

#### [0043]

次に、最上位ビットがハイレベル信号で、その次のビットはローレベル信号の場合、コンパレータ30は、DA変換器10から供給される電源電圧VDDの9/16の電圧と、サンプル・ホールド回路20から供給されている電圧とを比較する。後者の電圧が前者の電圧以上の場合、ハイレベルの信号を逐次変換レジスタ40に出力し、後者の電圧が前者の電圧未満の場合、ローレベルの信号を出力する。

#### [0044]

一方、最上位ビットがハイレベル信号で、その次のビットもハイレベル信号の場合、コ

20

30

40

50

ンパレータ30は、DA変換器10から供給される電源電圧VDDの11/16の電圧と、サンプル・ホールド回路20から供給されている電圧とを比較する。後者の電圧が前者の電圧以上の場合、ハイレベルの信号を逐次変換レジスタ40に出力し、後者の電圧が前者の電圧未満の場合、ローレベルの信号を出力する。以上の処理により、サンプル・ホールド回路20によりサンプリングされたアナログ信号Ainが3ビットのデジタル信号Doutに変換される。

[0045]

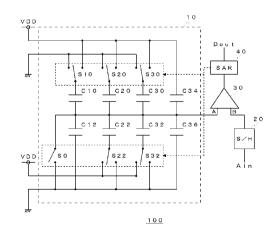

図 2 は、第 1 比較例における D A 変換器 1 8 の構成およびそれを含む逐次比較型 A D 変換器 2 0 0 の構成を示す。第 1 比較例における逐次比較型 A D 変換器 2 0 0 の構成は、図 1 に示した実施形態における逐次比較型 A D 変換器 1 0 0 の構成と基本的に同じである。両者は、 D A 変換器 1 8 の構成、およびコンパレータ 3 0 の入力電圧範囲が異なる。

[0046]

図 2 の D A 変換器 1 8 も、 3 ビットの分解能でデジタル信号をアナログ信号に変換するものである。コンパレータ 3 0 の第 1 入力端子 A に繋がる経路には、それぞれ重み付けされた複数の容量が並列に接続される。

[0047]

n 桁容量 C 1 8 は、主に最上位ビットの値を決定するための電圧幅を生成するための容量である。n 桁容量 C 1 8 の一端は、コンパレータ 3 0 の第 1 入力端子 A に繋がる経路に接続され、他端は、n 桁スイッチ S 1 8 の一端に接続される。n 桁スイッチ S 1 8 の他端は、高電位側の基準電位を供給する電源線および低電位側の基準電位を供給するグラウンド線に対して選択的に接続可能な構成である。n 桁スイッチ S 1 8 は、逐次変換レジスタ4 0 からの制御により、n 桁容量 C 1 8 を当該電源線または当該グラウンド線のいずれかに接続する。

[0048]

n-1桁容量C28は、主に最上位ビットの次のビットの値を決定するための電圧幅を生成するための容量である。n-1桁容量C28は、n桁容量C18の容量値の1/2の値である。n-1桁容量C28の一端は、コンパレータ30の第1入力端子Aに繋がる経路に接続され、その他端は、n-1桁スイッチS28の一端に接続される。n-1桁スイッチS28の他端は、上記電源線および上記グラウンド線に対して選択的に接続可能な構成である。n-1桁スイッチS28は、逐次変換レジスタ40からの制御により、n-1桁容量C28を当該電源線または当該グラウンド線のいずれかに接続する。

[0049]

n - 2 桁第 1 容量 C 3 8 および n - 2 桁第 2 容量 C 3 9 は、主に最上位ビットから 2 ビット下位のビットの値を決定するための電圧幅を生成するための容量である。 n - 2 桁第 1 容量 C 3 8 および n - 2 桁第 2 容量 C 3 9 は、同じ容量値であり、 n 桁容量 C 1 8 の容量値の 1 / 4 の値である。 n - 2 桁第 1 容量 C 3 8 および n - 2 桁第 2 容量 C 3 9 の一端は、コンパレータ 3 0 の第 1 入力端子 A に繋がる経路に接続される。

[0050]

n - 2 桁第 1 容量 C 3 8 の他端は、n - 2 桁スイッチ S 3 8 に接続され、n - 2 桁第 2 容量 C 3 9 の他端は、上記グラウンド線に接続される。n - 2 桁スイッチ S 3 8 の他端は、上記電源線および上記グラウンド線に対して選択的に接続可能な構成である。n - 2 桁スイッチ S 3 8 は、逐次変換レジスタ 4 0 からの制御により、n - 2 桁第 1 容量 C 3 8 を当該電源線または当該グラウンド線のいずれかに接続する。さらに、コンパレータ 3 0 の第 1 入力端子 A に繋がる経路と上記グラウンド線との間にリセット用スイッチ S 8 が設けられる。

[0051]

次に、第1比較例における逐次比較型 A D 変換器 2 0 0 の動作について説明する。初期状態にて、 D A 変換器 1 8 は、リセット用スイッチ S 8 オンで、 n 桁スイッチ S 1 8 、 n - 1 桁スイッチ S 2 8 および n - 2 桁スイッチ S 3 8 はすべてグラウンド線に接続される。したがって、 D A 変換器 1 8 全体の容量はディスチャージされ、コンパレータ 3 0 の第

1 入力端子 A はグラウンド電位となる。

#### [0052]

次に、逐次比較型 A D 変換器 2 0 0 にアナログ信号 A i n が入力されると、サンプル・ホールド回路 2 0 は、そのアナログ信号 A i n の電圧を所定のタイミングでサンプリングし、コンパレータ 3 0 の第 2 入力端子 B に供給する。コンパレータ 3 0 の第 2 入力端子 B にけいプリングされた電圧が現れると、リセット用スイッチ S 8 がオフに切り替えられ、n 桁スイッチ S 1 8 の接続先が上記グラウンド線から上記電源線に切り替えられる。その結果、n 桁容量 C 1 8 と、n - 1 桁容量 C 2 8、n - 2 桁第 1 容量 C 3 8 および n - 2 桁第 2 容量 C 3 9 からなる合成容量との直列回路が形成される。1 対 1 の容量分割となり、コンパレータ 3 0 の第 1 入力端子 A は、電源電圧 V D D の 1 / 2 の電圧となる。

#### [0053]

次に、コンパレータ30は、DA変換器10から供給される電源電圧VDDの1/2の電圧と、サンプル・ホールド回路20から供給される電圧とを比較する。後者の電圧が前者の電圧以上の場合、ハイレベルの信号を逐次変換レジスタ40に出力し、後者の電圧が前者の電圧未満の場合、ローレベルの信号を出力する。

#### [0054]

逐次変換レジスタ40は、コンパレータ30からの出力信号を最上位ビットの値として保持する。その出力信号がローレベルの信号である場合、 n - 1 桁スイッチS28に制御信号を出力して、接続先を上記グラウンド線から上記電源線に切り替える。この場合、 3 対 1 の容量分割となり、コンパレータ30の第1入力端子Aは、電源電圧VDDの1 / 4 の電圧となる。一方、コンパレータ30からの出力信号がハイレベルの信号である場合、 n 桁スイッチS18に制御信号を出力して、接続先を上記電源線から上記グラウンド線に切り替え、かつ n - 1 桁スイッチS28に制御信号を出力して、接続先を上記グラウンド線に切り替え、かつ n - 1 桁スイッチS28に制御信号を出力して、接続先を上記グラウンド線 の第1入力端子Aは、電源電圧VDDの3/4の電圧となる。

#### [0055]

以下、同様の原理により、逐次変換レジスタ40は、コンパレータ30からの出力信号のレベルに応じて、n桁スイッチS18、n-1桁スイッチS28およびn-2桁スイッチS30を制御することにより、電源電圧VDDの1/8の電圧、3/8の電圧、5/8の電圧および7/8の電圧をDA変換器18に生成させることができる。

#### [0056]

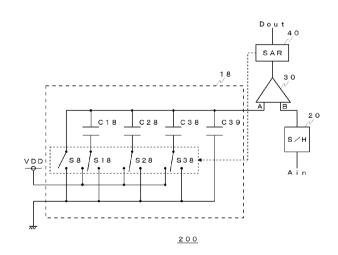

図3は、第2比較例におけるDA変換器19の構成およびそれを含む逐次比較型AD変換器300の構成を示す。第2比較例における逐次比較型AD変換器300の構成は、図2に示した第1比較例における逐次比較型AD変換器200の構成と基本的に同じである。両者は、DA変換器19の構成、およびコンパレータ30の入力電圧範囲が異なる。

#### [0057]

図3のDA変換器19も、3ビットの分解能でデジタル信号をアナログ信号に変換するものである。図2のDA変換器18と異なる点は、コンパレータ30の第1入力端子Aに繋がる経路と上記グラウンド線との間に、調整用容量C8が挿入された点である。調整用容量C8は、n桁容量C18の容量値の2倍の値である。

## [ 0 0 5 8 ]

次に、第2比較例における逐次比較型 A D 変換器 3 0 0 の動作について説明する。第2比較例における逐次比較型 A D 変換器 3 0 0 の動作は、第1比較例における逐次比較型 A D 変換器 2 0 0 の動作と基本的に同様である。調整用容量 C 8 が挿入されたため、以下の点が異なる。第1比較例における D A 変換器 1 8 の取り得る出力電圧は、電源電圧 V D D の 1 / 2 の電圧を中心に、1 / 4 の電圧、3 / 4 の電圧、1 / 8 の電圧、3 / 8 の電圧、5 / 8 の電圧および 7 / 8 の電圧であった。これに対し、第2比較例における D A 変換器 1 9 の取り得る出力電圧は、電源電圧 V D D の 1 / 4 の電圧を中心に、1 / 8 の電圧、3 / 8 の電圧、1 / 1 6 の電圧、3 / 1 6 の電圧、5 / 1 6 の電圧および 7 / 1 6 の電圧となる。

10

20

30

20

30

40

50

[0059]

次に、実施形態、比較例 1、および比較例 2におけるコンパレータ 3 0の入力電圧範囲について説明する。実施形態におけるコンパレータ 3 0の第 1 入力端子 A には D A 変換器 1 0 から電源電圧 V D D の 1 / 2 の電圧を中心に、電源電圧 V D D の 5 / 1 6 から 1 1 / 1 6 の範囲の電圧が印加される。 n - 2 桁第 3 容量 C 3 4 および n - 2 桁第 4 容量 C 3 6 も、上記電源線に接続可能な構成にすれば、電源電圧 V D D の 1 / 4 から 3 / 4 の範囲の電圧が印加され得る。

[0060]

比較例1におけるコンパレータ30の第1入力端子AにはDA変換器18から電源電圧 VDDの1/2の電圧を中心に、電源電圧VDDの1/8から7/8の範囲の電圧が印加される。n-2桁第2容量C39も、上記電源線に接続可能な構成にすれば、電源電圧VDDからグラウンド電位の範囲の電圧が印加され得る。

[0061]

比較例 2 におけるコンパレータ 3 0 の第 1 入力端子 A には D A 変換器 1 9 から電源電圧 V D D の 1 / 4 の電圧を中心に、電源電圧 V D D の 1 / 1 6 から 7 / 1 6 の範囲の電圧が印加される。 n - 2 桁第 2 容量 C 3 9 も、上記電源線に接続可能な構成にすれば、電源電圧 V D D の 1 / 2 の電圧からグラウンド電位の範囲の電圧が印加され得る。

[0062]

本実施形態は、比較例1と比較すると、DA変換器10の出力電圧範囲を1/2にすることができ、コンパレータ30の入力電圧範囲も1/2にすることができる。これにより、コンパレータの設計を簡素化することができ、コスト削減にもつながる。また、低電源電圧化にも対応することができる。

[0063]

本実施形態は、比較例2と比較し、出力電圧範囲自体をシフトすることができる。すなわち、本実施形態は、その出力電圧範囲の下限がグラウンド電位ではなく、その出力電圧範囲が電源電圧VDDとグラウンド電位との間の中間に位置する。後述するように、電源電圧VDDとグラウンド電位との間でその出力電圧範囲を任意に設定することができる。したがって、逐次比較型AD変換器100に入力されるアナログ信号Ainの範囲に対し、その出力電圧範囲を容易に対応させることができる。また、本実施形態の容量群は、比較例1における容量で1/2にして、2倍の数設けたものであるため、総容量の面積は比較例1におけるそれと基本的に同じである。この点、比較例2における総容量の面積は、調整用容量C8が追加された分、増大する。したがって、本実施形態は、出力電圧範囲の縮小を容量の面積を増大させずに実現することができる。

[0064]

次に、本実施形態にて、縮小した出力電圧範囲を設計者が任意のレベルにシフト可能な点について説明する。本実施形態にて、DA変換器10の総容量値TCは下記式1のように表される。

- C 2 0 = C 2 2 = C / 2

- C 3 0 = C 3 2 = C 3 4 = C 3 6 = C / 2

- C 1 0 = C a ; C 1 2 = C b

とすると、

$T C = C a + C b + 2 \times C / 2 + 4 \times C / 4$

= C a + C b + 2 C ... (式1)

[0065]

本実施形態にて、出力電圧範囲 V W は、総容量値 T C と、総容量値 T C から調整用第 1 容量 C 1 0 の容量値 C a および調整用第 2 容量 C 1 2 の容量値 C b を除いた残りの容量値との比で決定されるので、下記式 2 のように表される。

VW={2C/(Ca+Cb+2C)} x V D D ... (式2)

[0066]

本実施形態にて、最上位ビットを決定するために、最初にコンパレータ30の第1入力

端子Aに印加されるべき電圧Ainiは、下記式3のように表される。

Aini = (Ca+C) / (Ca+Cb+2C) x V D D ... (式3)

#### [0067]

上記出力電圧範囲VWの中心値は、当該初期電圧Ainiに設定される。設計者は、当該出力電圧範囲VWの両端が電源電圧VDDからグラウンド電位の範囲外に出ないよう、上記容量Ca、Cbを設定する必要がある。

#### [0068]

これまで、3ビット変換のDA変換器10について説明した。以下、本発明がその他のビット数にも容易に拡張できる点について説明する。すなわち、上記式2にて、2Cに相当する電荷を蓄える容量群の数を調整すればよい。上述したように、3ビット変換の場合、6個の容量を用い、ある容量値の容量を2個、その容量値の1/2の容量値の容量を4個設けた。この点、4ビット変換の場合、8個の容量を用い、ある容量値の容量を2個、その容量値の1/2の容量値の容量を2個、その容量値の1/2の容量値の容量を2個、および初めの容量値の1/4の容量値の容量を4個設ければよい。そして、スイッチで所定数の容量を電源線に接続し、残りの容量をグラウンド線に接続することにより、少なくとも15通りの電圧を生成することができる

#### [0069]

以上説明したように本実施形態によれば、DA変換器の出力電圧範囲を、電源電圧とグラウンド電位との間の電圧範囲と異ならせることができる。例えば、DA変換器のの出力電圧範囲の中心値を任意のレベルに設定することができる。したがって、電圧のレベルに拘束されずに、出力電圧範囲の幅および位置を任意に設定することができる。まって、コンパレータにおけるリファレンス電圧として利用する場合、コンパレータに入力される比較対象とすべき電圧に対して、最適の入力電圧範囲およびコンパレータに入力される比較対象とすべき電圧に対して、最適のリファレンス電圧を供給することができる。しかも、総容量の面積を増大させることもない。また、電圧を昇圧したり、降圧したりする回路構成も必要ない。さらに、本の本で換器を集積化し、スイッチをトランジスタで構成した場合、そのトランジスタは、領電圧とグラウンド電位を切り替えるだけでよいことから、動作保証マージンの大きい領域で切替制御を行うことができる。

#### [0070]

以上、本発明をいくつかの実施の形態をもとに説明した。この実施の形態は例示であり、それらの各構成要素や各処理プロセスの組合せにいるいろな変形例が可能なこと、またそうした変形例も本発明の範囲にあることは当業者に理解されるところである。

#### [0071]

実施形態にて、調整用第1容量 С 1 0 および調整用第 2 容量 С 1 2 が設けられない構成も本発明の範囲にある。この場合、比較例 1 に相当する出力電圧範囲を小さな総容量の面積で実現することができる。具体的には、この変形例は、比較例 1 の実質的に 1 / 2 の面積にすることができる。これは、各桁の電圧幅を生成するための容量を 2 つにしたことにより、桁ごとに 1 つの容量を電源線に接続し、もう 1 つの容量をグラウンド線に接続した状態で初期電圧を生成することができるためである。

## [ 0 0 7 2 ]

また、比較例 2 にて、調整用容量 C 8 を複数、例えばに 2 つに分割し、その一部を電源線およびグラウンド線に選択的に接続可能な構成とした例も本発明の範囲にある。この場合も、上記式 2 を実現する回路構成となり、総容量の面積に関する部分を除き、実施形態と同様の効果を奏することができる。

#### [0073]

さらに、上記式2の2Cの項を実現するために、容量の数を増やして、その分容量値を減少させるなど、実施形態に示した回路と等価な回路も本発明の範囲にある。また、ある容量に対して、電源電圧VDDと異なる電圧を印加し、それに応じてその容量値を変化させるなど、Q=CVの関係式を満たす範囲内での変形も本発明の範囲にある。

20

10

30

#### 【図面の簡単な説明】

[0074]

【図1】本発明の実施形態におけるDA変換器の構成およびそれを含む逐次比較型AD変換器の構成を示す図である。

【図2】第1比較例におけるDA変換器の構成およびそれを含む逐次比較型AD変換器の構成を示す図である。

【図3】第2比較例におけるDA変換器の構成およびそれを含む逐次比較型AD変換器の構成を示す図である。

#### 【符号の説明】

#### [0075]

1 0 D A 変換器、 2 0 サンプル・ホールド回路、 3 0 コンパレータ、 4 0 逐次変換レジスタ、 1 0 0 逐次比較型 A D 変換器、 S 0 リセット用スイッチ、 C 1 0 調整用第 1 容量、 C 1 2 調整用第 2 容量、 C 2 0 n - 1 桁第 1 容量、 C 2 2 n - 1 桁第 2 容量、 C 3 0 n - 2 桁第 1 容量、 C 3 2 n - 2 桁第 2 容量、 C 3 4 n - 2 桁第 1 スイッチ、 S 2 2 n - 1 桁第 2 スイッチ、 S 3 0 n - 2 桁第 1 スイッチ、 S 3 0 n - 2 桁第 1 スイッチ、 S 3 0 n - 2 桁第 1 スイッチ。

## 【図1】

#

#### 【図2】

## 【図3】