## (19) 대한민국특허청(KR)

## (12) 등록특허공보(B1)

(51) 국제특허분류(Int. Cl.)

**H01L 21/336** (2006.01) **H01L 21/265** (2006.01)

(21) 출원번호 **10-2009-0134669**

(22) 출원일자 **2009년12월30일** 심사청구일자 **2009년12월30일**

(65) 공개번호 10-2011-0077966

(43) 공개일자 2011년07월07일

(56) 선행기술조사문헌

KR1020030056882 A\*

KR1020060001045 A\* KR1020060077491 A\*

\*는 심사관에 의하여 인용된 문헌

(73) 특허권자

(45) 공고일자

(11) 등록번호

(24) 등록일자

#### 주식회사 하이닉스반도체

경기도 이천시 부발읍 경충대로 2091

2012년03월16일

2012년02월29일

10-1124565

(72) 발명자

#### 진숭우

경기도 이천시 대월면 경충대로2041번길 167, 현 대사원아파트 107-105

#### 이안배

서울특별시 영등포구 신길로62가길 1-2, 301호 ( 신길동)

(뒷면에 계속)

(74) 대리인

특허법인 아주양헌

전체 청구항 수 : 총 1 항

심사관 : 장지혜

#### (54) 발명의 명칭 고속 반도체 소자의 제조방법

#### (57) 요 약

컨택저항을 줄여 소자의 고속 동작을 가능하게 하는 고속 반도체 소자의 제조방법을 제시한다. 본 발명에 따른 고속 반도체 소자의 제조방법은, 게이트 및 소스/드레인이 형성된 반도체기판 상에 충간절연막을 형성하는 단계와, 충간절연막을 식각하여 소스/드레인을 노출하는 컨택홀을 형성하는 단계와, 컨택홀에 의해 노출된 소스/드레인에 컨택 저항을 감소시키기 위한 불순물 이온을 주입하되, NMOS 영역에는 인(P) 이온과 카본(C) 이온을 주입하는 단계, 및 불순물 이온이 주입된 반도체기판을 열처리하는 단계를 포함한다.

#### 대 표 도 - 도4

## (72) 발명자

## 주영환

서울특별시 도봉구 덕릉로66길 17, 1711동 605호 (창동, 주공아파트)

## 장일식

충청북도 청주시 흥덕구 백봉로 148, 신관 남자기 숙사 210호 (봉명동)

## 차재춘

경기도 이천시 대월면 경충대로2041번길 167, 현대 전자아파트 101동 1305호

#### 특허청구의 범위

#### 청구항 1

게이트 및 소스/드레인이 형성된 반도체기판 상에 층간절연막을 형성하는 단계;

상기 층간절연막을 식각하여 상기 소스/드레인을 노출하는 컨택홀을 형성하는 단계;

상기 컨택홀에 의해 노출된 상기 소스/드레인에 컨택 저항을 감소시키기 위한 불순물 이온을 주입하되, NMOS 영역에는 인(P) 이온과 카본(C) 이온을 주입하는 단계; 및

상기 불순물 이온이 주입된 반도체기판을 열처리하는 단계를 포함하는 것을 특징으로 하는 반도체 소자의 제조 방법.

#### 청구항 2

청구항 2은(는) 설정등록료 납부시 포기되었습니다.

제1항에 있어서,

상기 불순물 이온을 주입하는 단계에서,

인(P) 이온을 주입한 후 카본(C) 이온을 주입하거나,

카본(C) 이온을 주입한 후 인(P) 이온을 주입하는 것을 특징으로 하는 반도체 소자의 제조방법.

#### 청구항 3

청구항 3은(는) 설정등록료 납부시 포기되었습니다.

제1항에 있어서,

상기 불순물 이온을 주입하는 단계에서,

#### 청구항 4

청구항 4은(는) 설정등록료 납부시 포기되었습니다.

제1항에 있어서,

상기 불순물 이온을 주입하는 단계에서,

상기 카본(C) 이온은 이온주입 또는 클러스터 방식으로 주입하는 것을 특징으로 하는 반도체 소자의 제조방법.

### 청구항 5

청구항 5은(는) 설정등록료 납부시 포기되었습니다.

제4항에 있어서,

상기 카본(C) 이온을 이온주입 방식으로 주입할 경우,

1 ~ 80KeV의 에너지와,  $1 \times 10^{13}$  ~  $1 \times 10^{16}$  원자/cm의 도우즈로 주입하는 것을 특징으로 하는 반도체 소자의 제조 방법.

## 청구항 6

청구항 6은(는) 설정등록료 납부시 포기되었습니다.

제4항에 있어서,

상기 카본(C) 이온을 클러스터 방식으로 주입할 경우,

카본 이온 소스로  $C_7H_7$ 을 사용하여, 1KeV  $\sim$  200KeV의 에너지와,  $1\times 10^{13}$   $\sim$   $5\times 10^{16}$ 원자/cm의 도우즈로 주입하는 것을 특징으로 하는 반도체 소자의 제조방법.

#### 청구항 7

청구항 7은(는) 설정등록료 납부시 포기되었습니다.

상기 카본(C) 이온을 클러스터 방식으로 주입할 경우,

카본 이온 소스로  $C_{14}H_{14}$ 을 사용하여 1 KeV ~ 400 KeV의 에너지와,  $1 \times 10^{13}$  ~  $5 \times 10^{16}$ 원자/cm²의 도우즈로 주입하는 것을 특징으로 하는 반도체 소자의 제조방법.

#### 청구항 8

청구항 8은(는) 설정등록료 납부시 포기되었습니다.

제1항에 있어서.

상기 불순물 이온이 주입된 반도체기판을 열처리하는 단계는 급속열처리(RTA) 방식으로 수행하는 것을 특징으로 하는 반도체 소자의 제조방법.

#### 청구항 9

청구항 9은(는) 설정등록료 납부시 포기되었습니다.

제1항에 있어서,

상기 불순물 이온이 주입된 반도체기판을 열처리하는 단계 후에,

상기 반도체기판 상에 배리어막을 증착하는 단계;

상기 배리어막에 대해 열처리 공정을 실시하여 상기 컨택홀의 바닥에 실리사이드를 형성하는 단계; 및

상기 컨택홀에 의해 노출된 소스/드레인과 접속된 비트라인을 배선충을 형성하는 단계를 더 포함하는 것을 특징으로 하는 반도체 소자의 제조방법.

## 명 세 서

#### 발명의 상세한 설명

#### 기 술 분 야

[0001] 본 발명은 반도체 소자의 제조방법에 관한 것으로, 특히 고속 반도체 소자의 제조방법에 관한 것이다.

#### 배경기술

[0002] 반도체 소자의 고집적화로 그 크기가 작아지면서 컨택의 크기 또한 작아짐에 따라 컨택 저항이 증가하여 소자의 동작 속도가 저하되는 문제가 발생하고 있다. 이를 해결하기 위하여 2 ~ 3 개의 컨택을 묶는 방법을 사용하였지만 초고집적 반도체 소자에서는 한계를 나타내고 있다.

[0003] 일반적으로 컨택저항을 줄이기 위해 NMOS 및 PMOS 트랜지스터 영역에 컨택홀을 형성한 후 추가로 플러그 이온주입을 실시하는데, NMOS 트랜지스터의 경우 아세닉(75As) 소스를 이용하여 이온주입을 진행하였다. 최근에는 NMOS 트랜지스터의 컨택 저항을 더욱 줄이고 온 전류(on current) 특성을 개선하기 위하여 플러그 이온주입을 위한 불순물을 비소(75As)에서 인(31P)으로 변경하는 방법이 사용되고 있다. 그러나, 이 방법은 저항의 측면에서는 크게 개선된 것으로 확인되었지만 30nm급 이하의 반도체 소자에서는 인(31P) 이온의 빠른 확산속도로 인해단 채널 효과(short channel effect)가 심화되어 적용하지 못하는 한계를 나타내고 있다.

#### 발명의 내용

## 해결 하고자하는 과제

[0004] 본 발명이 이루고자 하는 기술적 과제는 컨택저항을 줄여 소자의 고속 동작을 가능하게 하는 고속 반도체 소자

의 제조방법을 제공하는 데 있다

#### 과제 해결수단

- [0005] 상기 기술적 과제를 달성하기 위하여 본 발명에 따른 고속 반도체 소자의 제조방법은, 게이트 및 소스/드레인이 형성된 반도체기판 상에 충간절연막을 형성하는 단계와, 상기 충간절연막을 식각하여 상기 소스/드레인을 노출하는 컨택홀을 형성하는 단계와, 상기 컨택홀에 의해 노출된 상기 소스/드레인에 컨택 저항을 감소시키기 위한 불순물 이온을 주입하되, NMOS 영역에는 인(P) 이온과 카본(C) 이온을 주입하는 단계, 및 상기 불순물 이온이 주입된 반도체기판을 열처리하는 단계를 포함하는 것을 특징으로 한다.

- [0006] 상기 불순물 이온을 주입하는 단계에서, 인(P) 이온을 주입한 후 카본(C) 이온을 주입하거나, 카본(C) 이온을 주입한 후 인(P) 이온을 주입할 수 있다.

- [0007] 상기 불순물 이온을 주입하는 단계에서, 상기 인(P) 이온은 1 ~ 50KeV의 에너지와,  $1 \times 10^{14}$  ~  $1 \times 10^{16}$  원자/cm의 도우즈로 주입할 수 있다.

- [0008] 상기 불순물 이온을 주입하는 단계에서, 상기 카본(C) 이온은 이온주입 또는 클러스터 방식으로 주입할 수 있다.

- [0009] 상기 카본(C) 이온을 이온주입 방식으로 주입할 경우, 1 ~ 80KeV의 에너지와,  $1 \times 10^{13}$  ~  $1 \times 10^{16}$ 원자/c㎡의 도우 즈로 주입할 수 있다.

- [0010] 상기 카본(C) 이온을 클러스터 방식으로 주입할 경우, 카본 이온 소스로 C<sub>7</sub>H<sub>7</sub>을 사용하여, 1KeV ~ 200KeV의 에 너지와. 1×10<sup>13</sup> ~ 5×10<sup>16</sup>원자/cm의 도우즈로 주입할 수 있다.

- [0011] 상기 카본(C) 이온을 클러스터 방식으로 주입할 경우, 카본 이온 소스로 C<sub>14</sub>H<sub>14</sub>을 사용하여 1KeV ~ 400KeV의 에 너지와, 1×10<sup>13</sup> ~ 5×10<sup>16</sup>원자/c㎡의 도우즈로 주입할 수 있다.

- [0012] 상기 불순물 이온이 주입된 반도체기판을 열처리하는 단계는 급속열처리(RTA) 방식으로 수행할 수 있다.

- [0013] 상기 불순물 이온이 주입된 반도체기판을 열처리하는 단계 후에, 상기 반도체기판 상에 배리어막을 증착하는 단계와, 상기 배리어막에 대해 열처리 공정을 실시하여 상기 컨택홀의 바닥에 실리사이드를 형성하는 단계, 및 상기 컨택홀에 의해 노출된 소스/드레인과 접속된 비트라인을 배선층을 형성하는 단계를 더 포함할 수 있다.

#### 발명의 실시를 위한 구체적인 내용

- [0014] 이하, 첨부된 도면을 참조하여 본 발명의 바람직한 실시예를 상세히 설명하기로 한다. 그러나, 본 발명의 실시예들은 여러 가지 다른 형태로 변형될 수 있으며, 본 발명의 범위가 아래에서 상술하는 실시예들로 인해 한정되는 것으로 해석되어서는 안된다.

- [0015] 일반적으로 인(P) 이온은 열처리 공정에 따른 활성화 효율은 우수하지만 확산도(diffusivity)가 매우 크기 때문에 단 채널 효과 측면에서 취약한 면이 있다. 그런데, 인(P) 이온과 함께 카본(C) 이온을 주입해주면 열공정 적용시 확산도가 더 큰 카본 이온은 확산되고, 대신 인(P) 이온은 활성화되는 현상이 발생한다. 즉, 카본(C) 이온이 인(P) 이온의 확산 장벽(diffusion barrier) 역할을 하게 된다. 본 발명은 이러한 특성을 이용하여 카본(C) 이온과 인(P) 이온을 함께 컨택 저항 개선을 위한 이온주입을 수행함으로써 단 채널 효과의 한계를 극복하고 컨택 저항 및 온 전류 특성을 개선하여 고속 반도체 소자의 제조가 용이하도록 하는 방법을 제시한다.

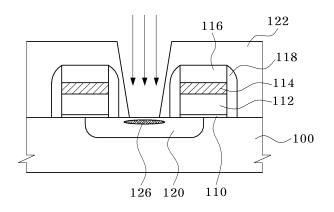

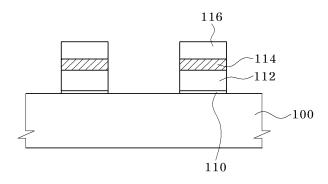

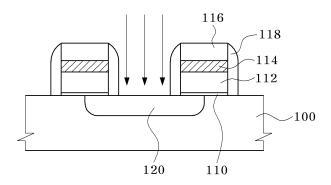

- [0016] 도 1 내지 도 5는 본 발명의 일 실시예에 따른 고속 반도체 소자의 제조방법을 설명하기 위하여 도시한 단면도 들이다.

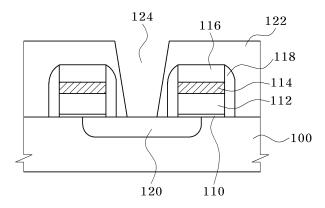

- [0017] 도 1을 참조하면, 반도체기판(100) 상에 게이트 스택을 형성한다. 구체적으로, 먼저 소자분리막(도시되지 않음)이 형성된 반도체기판(100) 상에 예를 들어 산화막을 성장시켜 게이트절연막(110)을 형성한 다음, 게이트절연막 위에 폴리실리콘막을 일정 두께 증착하여 게이트 도전층(112)을 형성한다. 상기 게이트 도전층(112) 위에 예를 들어 텅스텐실리사이드를 증착하여 게이트 금속층(114)을 형성하고, 게이트 금속층 위에 실리콘질화막을 증착하여 하드마스크층(116)을 형성한다. 상기 게이트 금속층(114)은 게이트의 저항을 감소시키는 역할을 하고, 하드마스크층(116)은 후속 게이트 금속층 및 게이트 도전층을 패터닝하기 위한 식각 공정에서 마스크로 사용하

기 위함이다.

- [0018] 다음에, 사진식각 공정으로 하드마스크층을 식각하여 게이트가 형성될 영역을 한정하는 하드마스크 패턴을 형성한 다음, 하드마스크 패턴을 마스크로 이용하여 게이트 금속층(114), 게이트 도전층(112) 및 게이트절연막(110)을 차례로 식각하여 게이트 스택을 형성한다.

- [0019] 도 2를 참조하면, 게이트 스택이 형성된 반도체기판의 전면에 예를 들어 산화막과 같은 절연막을 증착한 후 절연막을 에치백하여 게이트 스택의 측벽에 절연막 스페이서(118)를 형성한다. 다음, 게이트 스택 및 절연막 스페이서가 형성된 반도체기판(100)에 N형 및 P형의 불순물을 이온주입하여 소스/드레인(120)을 형성한다. 이때, PMOS 트랜지스터 영역에는 P형 불순물을 주입하고, NMOS 트랜지스터 영역에는 N형 불순물을 주입한다.

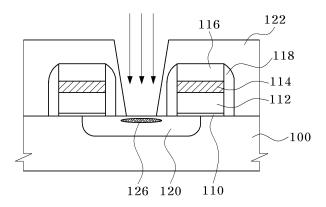

- [0020] 도 3을 참조하면, 소스/드레인이 형성된 반도체기판 상에 절연막을 증착하여 충간절연막(122)을 형성한다. 충간 절연막(122)은 저압 화학기상증착(Low Pressure Chemical Vapor Deposition; LPCVD) 또는 플라즈마 화학기상증 착(Plasma Enhanced CVD; PECVD) 방법을 사용하여 산화막 또는 질화막으로 형성할 수 있다. 또는, 아몰퍼스 카 본(amorphous carbon) 막을 PECVD 방식으로 증착하여 형성할 수 있다. 다음에, 충간절연막(122)을 식각하여 소 스/드레인을 노출시키는 컨택홀(124)을 형성한다.

- [0021] 도 4를 참조하면, 상기 컨택홀에 의해 노출된 소스/드레인에 컨택저항을 줄이기 위한 불순물 주입을 실시한다. PMOS 트랜지스터에는 P형 불순물이온을 주입하고 NMOS 트랜지스터에는 N형 불순물을 주입한다. PMOS 트랜지스터의 경우 보론(B) 계열의 3가 원소를 이온주입한다.

- [0022] NMOS 트랜지스터의 경우 인(31P) 이온을 주입하는데, 이때 카본(carbon; C) 이온을 함께 주입한다. 이때, 카본 이온은, 1 ~ 80KeV의 에너지,  $1 \times 10^{13}$  ~  $1 \times 10^{16}$ 원자/c㎡의 도우즈, 0 ~ 45°의 틸트 각도, 그리고 0 ~ 360°의 트위스트 각도로 주입할 수 있다. 그리고, 인 이온은, 1 ~ 50KeV의 에너지,  $1 \times 10^{14}$  ~  $1 \times 10^{16}$ 원자/c㎡의 도우즈, 0 ~ 45°의 틸트 각도, 그리고 0 ~ 360°의 트위스트 각도로 주입할 수 있다. 이때, 카본 이온을 먼저 주입한 다음에 인 이온을 주입할 수도 있고, 반대로 인 이온을 먼저 주입한 다음에 카본 이온을 주입할 수도 있다.

- [0023] 카본 이온은 분자 타입의 도펀트 가스 형태를 이온주입하는 클러스터 방식으로 주입할 수 있다. 이 경우 카본 소스로 C<sub>7</sub>H<sub>7</sub> 또는 C<sub>14</sub>H<sub>14</sub>을 사용할 수 있다. 카본 소스로 C<sub>7</sub>H<sub>7</sub>을사용할 경우에는 1KeV ~ 200KeV의 에너지, 1×  $10^{13}$  ~  $5\times10^{16}$ 원자/cm의 도우즈, 0 ~  $45^{\circ}$  의 틸트 각도, 그리고 0 ~  $360^{\circ}$  의 트위스트 각도로 주입할 수 있다. 카본 소스로 C<sub>14</sub>H<sub>14</sub>을 사용할 경우에는 1KeV ~ 400KeV의 에너지,  $1\times10^{13}$  ~  $5\times10^{16}$ 원자/cm의 도우즈, 0 ~  $45^{\circ}$  의 틸트 각도, 그리고 0 ~  $360^{\circ}$  의 트위스트 각도로 주입할 수 있다.

- [0024] 다음에, 저항 감소를 위한 불순물이 주입된 반도체기판에 대해 열처리 공정을 실시하여 불순물들이 확산 및 활성화되도록 한다. 열처리 공정은 급속 열처리(RTA) 방식으로 수행할 수 있다.

- [0025] 이와 같이, 컨택 저항 개선을 위해 NMOS 트랜지스터 영역에 인(P) 이온과 카본(C) 이온을 함께 주입하면, 열처리 과정에서 확산도가 더 큰 카본(C) 이온으로 인해 인(P)의 확산이 억제되어 단 채널 효과를 억제하면서 컨택저항을 효과적으로 줄일 수 있게 된다.

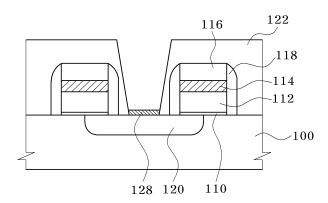

- [0026] 도 5를 참조하면, 추가 불순물 이온주입이 수행된 반도체기판 상에 티타늄(Ti), 코발트(Co), 니켈(Ni)과 같은 배리어 금속을 증착한 후 열처리 공정을 실시하여, 반도체기판의 소스/드레인과 비트라인 사이의 접촉저항을 더욱 줄이기 위한 실리사이드(128)를 형성한다.

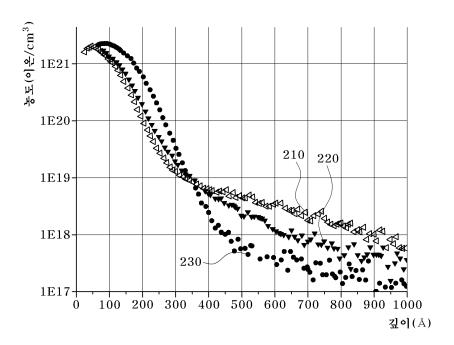

- [0027] 도 6은 컨택 저항 개선을 위해 NMOS 영역에 인 이온만을 주입할 때와 카본 이온을 함께 주입한 경우를 비교하기 위하여 깊이에 따른 불순물 농도를 나타낸 그래프이다.

- [0028] 도시된 바와 같이, NMOS 영역에 인 이온만을 주입한 경우(210)에 비해 인 이온과 카본 이온을 함께 주입한 경우 (220, 230), 불순물이 분포된 깊이가 얕아진 것을 알 수 있다. 이는, 카본(C) 이온에 의해 인(P) 이온의 확산이 억제되어 불순물 분포 깊이가 얕아진 것으로, 이에 따라 단 채널 효과가 개선되고 컨택 저항이 감소될 수 있다. 실제 본 발명을 적용한 결과 NMOS 트랜지스터의 컨택 저항은 30% 정도 개선되었고 NMOS 트랜지스터의 전류는 3% 이상 개선되는 효과가 있었다.

- [0029] 본 발명에 따르면, 컨택저항 감소를 위한 추가 불순물 이온을 주입할 때 NMOS 영역에 카본 이온과 인 이온을 혼합하여 주입함으로써 단 채널 효과의 한계를 극복하고 컨택 저항 및 온 전류 특성을 개선하고 고속 반도체 소자

의 제조가 용이하도록 할 수 있다.

[0030] 이상 본 발명을 바람직한 실시예를 들어 상세하게 설명하였으나, 본 발명은 상기 실시예에 한정되지 않으며, 본 발명의 기술적 사상 내에서 당 분야에서 통상의 지식을 가진 자에 의하여 여러 가지 변형이 가능함은 당연하다.

## 도면의 간단한 설명

- [0031] 도 1 내지 도 5는 본 발명의 일 실시예에 따른 고속 반도체 소자의 제조방법을 설명하기 위하여 도시한 단면도 들이다.

- [0032] 도 6은 컨택 저항 개선을 위해 NMOS 영역에 인 이온만을 주입한 경우와 카본 이온을 함께 주입한 경우를 비교하기 위하여 나타낸 그래프이다.

## 도면

## 도면1

### 도면2

## 도면3

## 도면4

## *도면5*

# 도면6