(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11) 特許番号

特許第3581554号 (P3581554)

(45) 発行日 平成16年10月27日 (2004.10.27)

(24) 登録日 平成16年7月30日 (2004.7.30)

(51) Int.C1.7

FI

HO4N 1/028

HO4N 1/028

Z

請求項の数 7 (全 13 頁)

(21) 出願番号 特願平10-37593

(22) 出願日 平成10年2月19日(1998.2.19)

(65) 公開番号 特開平11-234472

(43) 公開日 平成11年8月27日 (1999.8.27) 審査請求日 平成13年11月30日 (2001.11.30) |(73)特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

||(74) 代理人 100065385

弁理士 山下 穣平

(72) 発明者 小塚 開

東京都大田区下丸子3丁目30番2号 キ

ヤノン株式会社内

審査官 渡辺 努

(58) 調査した分野 (Int. Cl. <sup>7</sup>, DB名) H04N 1/024-1/036

(54) 【発明の名称】イメージセンサ及び画像読取装置

# (57)【特許請求の範囲】

#### 【請求項1】

第1及び第2の光電変換装置を複数実装したイメージセンサであって、

各々の前記光電変換装置は、複数の受光素子と、前記複数の受光素子からの信号が読み出される共通出力線と、前記複数の受光素子の信号を前記共通出力線に読み出すための<u>走査を行う</u>走査手段と、前段の前記光電変換装置の前記走査手段の走査終了後に、次段の前記光電変換装置の前記走査手段の読み出し走査が開始するように、前記複数の受光素子の信号の読み出しを開始させるためのスタート信号を受け、所定時間遅延し、前記スタート信号を前記走査手段に対して出力する遅延手段とを有し、解像度切換信号に応じて、前記共通出力線から前記第1の解像度の信号を読み出す第1の解像度モードと、前記共通出力線から前記第1の解像度よりも小さい第2の解像度の信号を読み出す第2の解像度モードとの切り替えが可能であり、

10

前記イメージセンサは、さらに、前記第1の解像度モードが選択された場合には、前記第1の光電変換装置内の前記走査手段が第1の位置を走査中に、前記第2の光電変換装置内の前記複数の受光素子からの信号の読み出しを開始させるためのスタート信号を出力し、前記第2の解像度モードが選択された場合には、前記第1の光電変換装置内の前記走査手段が前記第1の位置よりも走査開始位置に近い第2の位置を走査中に、前記第2の光電変換装置内の前記複数の受光素子からの信号の読み出しを開始させるためのスタート信号を出力するように制御するとともに、前記第1の解像度モードが選択された場合には、前記第2の光電変換装置内の前記走査手段が第1の位置を走査中に、前記第1の光電変換装置

内の前記複数の受光素子からの信号の読み出しを開始させるためのスタート信号を出力し、前記第2の解像度モードが選択された場合には、前記第2の光電変換装置内の前記走査手段が前記第1の位置よりも走査開始位置に近い第2の位置を走査中に、前記第1の光電変換装置内の前記複数の受光素子からの信号の読み出しを開始させるためのスタート信号を出力するように制御するスタート信号切り換え手段を有することを特徴とするイメージセンサ。

#### 【請求項2】

請求項1に記載のイメージセンサ<u>に</u>おいて、<u>各々の前記光電変換装置は、前記複数の受光</u> <u>素子からの信号を蓄積する複数の蓄積容量を有し、前記走査手段は、前記複数の蓄積容量</u> <u>に蓄積された信号を順次前記共通出力線に読み出すように走査する</u>ことを特徴とするイメ ージセンサ。

#### 【請求項3】

請求項1又は2に記載のイメージセンサにおいて、前記走査手段は、前記第2の解像度モードが選択された場合に、前記複数の受光素子の信号を間引いて前記共通出力線に読み出すように走査することを特徴とするイメージセンサ。

#### 【請求項4】

請求項1乃至2のいずれか1項に記載のイメージセンサにおいて、前記走査手段は、前記第2の解像度モードが選択された場合に、前記複数の受光素子の信号を所定毎の信号を加算して前記共通出力線から読み出すように走査することを特徴とするイメージセンサ。

### 【請求項5】

請求項1乃至<u>4</u>のいずれか1項に記載のイメージセンサにおいて、<u>前記スタート信号切り</u> <u>換え手段は、前記スタート信号を送る側に設けられている</u>ことを特徴とするイメージセン サ。

#### 【請求項6】

請求項1乃至<u>4</u>のいずれか1項に記載のイメージセンサにおいて、<u>前記スタート信号切り</u> <u>換え手段は、前記スタート信号を受ける側に設けられている</u>ことを特徴とするイメージセ ンサ。

# 【請求項7】

請求項1乃至6のいずれか1項に記載のイメージセンサを有し、前記イメージセンサを構成する前記複数の光電変換装置が配列されている方向と垂直な方向に前記イメージセンサを走査することを特徴とする画像読取装置。

# 【発明の詳細な説明】

#### [0001]

# 【発明の属する技術分野】

本発明は、1次元の光電変換素子とこれを駆動する駆動回路とを備えた光電変換装置を複数実装したイメージセンサに関するものであり、更に詳しくは、解像度切り換え機能を有するイメージセンサ及び2次元の画像を読み出すイメージスキャナやファクシミリ、電子複写機等に用いる画像読取装置に関するものである。

# [0002]

### 【従来技術】

近年、情報処理システムの分野では、1次元の画像読み取り装置として、従来の光学系を用いた縮尺系のラインセンサに対して、複数の半導体光センサチップをマルチ実装した、 等倍系の密着型イメージセンサの開発が積極的に行われている。

# [0003]

### (従来技術1)

例えば、特開平5-227362号公報には、新規に解像度制御用のコントロール端子を設け、ユーザが利用条件にあわせて解像度を切り換えることが可能な密着型イメージセンサが提案されている。

# [0004]

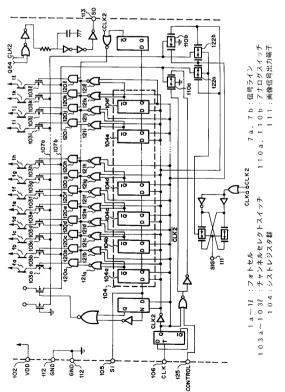

図7は当該公開公報に提案されている密着型イメージセンサ用集積回路の回路図である。

20

10

30

30

40

20

30

50

この従来技術においては、イメージセンサチップにコントロール端子(1 2 5 )を設け、その端子にユーザが、ハイレベルまたはローレベルの信号を入力することにより高解像度モードと低解像度モードの解像度切り換えを実現している。図 7 について概略説明すれば、スタートパルスSIと、クロックパルスCLKとをシフトレジスタ群 1 0 4 に供給する。スタートパルスSIによってシフトレジスタ 1 0 4 a が起動されると、その出力はノアゲート 1 2 1 a およびアンドゲート 1 2 0 a を通ってチャンネルセレクトスイッチ 1 0 3 a に入力され、これをオンにし、フォトセル 1 0 1 a からの信号を信号ライン 1 0 7 a に取り出す。他のシフトレジスタ 1 0 4 b ~ 1 0 4 f も順次起動していき、各フォトセル 1 0 1 b ~ 1 0 1 1 からの信号を信号ライン 1 0 7 a 、 1 0 7 b に出力する。

#### [0005]

ここで、コントロール信号入力端子125にコントロール信号 "H"が入力されると、アナログスイッチ110a,110b,122a,122bが切り換えられ、画像出力端子111に16ドット/ミリの読み取り密度で画像信号が得られる。また、コントロール信号 "L"が入力されると、アナログスイッチ110aが常にオン状態となり、画像出力端子111にはフォトセル101a~1011全体の半分の8ドット/ミリの読み取り密度で画像信号が得られる。つまり、センサIC上のフォトセル101a~1011は常に全数が動作しているが、外部に出力画像信号を取り出す際に、コントロール信号によって一部を間引いて出力させることができる。そのため、画像信号の電圧レベルは常に一定となり、後段の画像処理回路の構成は従来のもので対応が可能となる。

#### [0006]

#### (従来技術2)

一方、高速化の要求に対して、例えば、特開平2-210950号公報にはスタート信号を遅延させる手段を有するイメージセンサチップ、及び密着型イメージセンサが提案されており、センサ信号を読み出す前に定電流回路を立ち上げることにより、高速読み出しを実現している。すなわち、受光要素を有するイメージセンサチップを複数個配列することによって構成されるマルチチップ型の光電変換装置に用いられるイメージセンサチップ及びこれを用いた光電変換装置において、受光要素による光信号読み出し動作のスタート信号を遅延させる遅延手段と、前記光信号読み出し動作が終了する前に、次段のイメージセンサチップに対するスタート信号に用いられる信号を有し、前記光信号読み出し信号を増幅する増幅回路内の定電流回路を、前記遅延手段の遅延開始を示すスタート信号によって、立ち上げることを特徴としている。

#### [0007]

また、特開平2-210949号公報には、上記特開平2-210950号公報に用いる1チップの構成を示しており、クロック信号のハイレベルに同期する内部クロック 1、クロック信号のローレベルに同期する内部クロック 2を用いてシフトレジスタを駆動するイメージセンサチップ、及び密着型イメージセンサが提案されており、これによりデューティ100%の高速読み出しを実現している。

#### [0008]

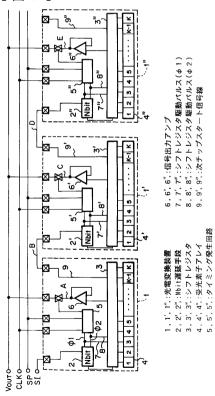

図 8 に、従来例として、上記特開平 2 - 2 1 0 9 4 9 号公報及び特開平 2 - 2 1 0 9 5 0 40 号公報に記載された内容から想定されるイメージセンサチップの等価回路図を示す。

#### [0009]

図8において、光電変換装置(1、1 、1 )がマルチ実装されており、各光電変換装置を駆動するクロック(CLK)、及びスタートパルス(SP)が共通接続されている。また、各光電変換装置(1、1 、1 )は、Nbitの遅延手段(Nbitプレシフトレジスタ2、2 、2 )、Kbitのシフトレジスタ(3、3 、3 )、Kbitの受光素子アレイ(4、4 、4 )、タイミング発生回路(5、5 、5 )、信号出力アンプ(6、6 、6 )を有している。

# [0010]

また、次チップスタート信号(9、9 、9 )は各光電変換装置のビットが読み出しを

50

終了する時よりNビット前(K-Nビット)時の信号を、シフトレジスタ3、3、3の最終レジスタの手前Nビット部分から次チップのスタート信号として出力する。

#### [0011]

また、クロック信号 C L K とスタートパルス信号 S P により駆動されるタイミング発生回路 (5、5、5)により、受光素子 4、4、4を駆動するパルス、及び、シフトレジスタ 3、3、3を駆動する駆動パルス 1 (7、7、7)、 2 (8、8、8)が生成される。スタートパルス信号 S P が各イメージセンサチップに共通に接続されているのは、各イメージセンサチップの動作開始の同期を取るためである。

#### [0012]

また、信号出力アンプ6、6 、6 は、受光素子アレイ4、4 、4 からシフトレジスタのシフト信号によってオン / オフするスイッチを介して 1 本の信号出力線に読み出される画像信号を増幅し、タイミング発生回路 5 、 5 の制御信号によって信号出力Voutされる。なお、信号出力アンプ6、6 、6 内には定電流回路が備えられ、スタート信号の入力と同時に、電源供給が始まり、スタート信号からNビットのクロック信号入力時には定常の増幅動作を可能としている。

#### [0013]

図 9 は C L K に対するシフトレジスタ 3 の駆動パルス 1 (7、7、7)、 2 (8、8、8)のタイミングチャートである。

### [0014]

尚、図 9 は、図 8 における遅延手段 2 を 4 ビットとした場合のタイミングである。従って 20、シフトレジスタ 3 , 3 " はスタートパルス信号 S P から 4 ビット遅延して、最初のシフトレジスタの動作を開始する。

## [0015]

ここで、図9に示すように、シフトレジスタ3の駆動パルス 1 (7、7、7)はCLKのハイレベルに同期したパルスとなり、 2 (8、8、8)はCLKのローレベルに同期したパルスとなる。信号出力 Voutは 1、 2 に同期して取り出される。従って、シフトレジスタ3の1bit目が 1 に対応する場合、奇数 bitは 1 同期、偶数 bitは 2 同期の信号出力となる。

# [0016]

同図 A は光電変換装置(1)の信号出力、同図 C は光電変換装置(1)の信号出力、同図 E は光電変換装置(1)の信号出力であり、全体の信号出力 V o u t は図に示すようになる。また、各々の光電変換装置は、最終ビットの 4 ビット前の信号を次の光電変換装置のスタート信号(B,D)として出力している。

# [ 0 0 1 7 ]

こうして、マルチチップ型の密着型イメージセンサとして大きな原稿を直接読み出すことが可能となり、チップ間の読み出し休息時間や、信号出力レベルの差異をなくすことができる。

### [0018]

# 【発明が解決しようとする課題】

しかしながら、上記の従来技術1に開示されている密着型イメージセンサの解像度切り換え方式においては、画素を読み飛ばすことにより解像度を切り換えているため、例えば、クロックレートが同一の場合には、解像度を半分にしても読み出し時間は、解像度が通常の場合でも半分の場合でも変わらない。仮に、受光素子が600dpiの光学解像度で配置され、高解像度モードで600dpi、低解像度モードで300dpiの解像度が得られるとすると、例えば、600dpi時に6msec/lineの読み取り速度が得られる場合、300dpi時でも6msec/lineの読み取り速度となり、解像度を落としても読み取り速度が変わらない。従って、同一のクロックレートを用いて600dpi時に5msec/lineの読み取り速度、300dpi時に5msec/lineの読み取り速度、300dpi時に3msec/lineの読み取り速度というように、解像度に応じた読み取り速度を実現することができないという問題がある。

#### [0019]

また、奇数ビットと偶数ビットの信号出力線が分離しているため、偶数ビットと奇数ビットのレベル差も生じやすいという問題もある。

#### [0020]

更に、従来技術 1 で開示されている解像度切り換えを従来技術 2 で開示されている密着型イメージセンサに適用した場合には、解像度切り換え時に光電変換装置の継ぎ目の部分で、不連続部が生じるという問題が生じる。

# [0021]

例えば、従来技術 2 において、プレシフトレジスタのビット数を 1 0 ビットとすると、高解像度モード時には次チップスタート信号を出力してから 1 0 ビット後に次の光電変換装置の 1 ビット目が出力されるため光電変換装置の継ぎ目の部分での信号は不連続にならないが、低解像度モード時には次チップスタート信号が出力されてから 5 ビット後に信号出力が終了するため、次の光電変換装置の 1 ビット目が出力されるまでの間、 5 ビット分の不連続部分が光電変換装置の継ぎ目で生じることになる。従って、従来技術 2 を従来技術 1 に用いようとしても、連続性のある高解像度と低解像度の画像信号を得ることは困難である。

# [0022]

# (本発明の目的)

本発明の目的は、解像度切り換え時に、解像度に応じた読み取り速度が実現可能で、かつ高速な<u>イメージセンサ、及びイメージセンサを有する画像読取装置</u>を提供することにある

#### [0023]

# 【課題を解決するための手段】

本発明のイメージセンサは、上記目的を達成するため、第1及び第2の光電変換装置を複 数実装したイメージセンサであって、各々の前記光電変換装置は、複数の受光素子と、前 記複数の受光素子からの信号が読み出される共通出力線と、前記複数の受光素子の信号を 前記共通出力線に読み出すための走査を行う走査手段と、前段の前記光電変換装置の前記 走査手段の走査終了後に、次段の前記光電変換装置の前記走査手段の読み出し走査が開始 するように、前記複数の受光素子の信号の読み出しを開始させるためのスタート信号を受 け、所定時間遅延し、前記スタート信号を前記走査手段に対して出力する遅延手段とを有 し、解像度切換信号に応じて、前記共通出力線から前記第1の解像度の信号を読み出す第 1の解像度モードと、前記共通出力線から前記第1の解像度よりも小さい第2の解像度の 信号を読み出す第2の解像度モードとの切り替えが可能であり、前記イメージセンサは、 さらに、前記第1の解像度モードが選択された場合には、前記第1の光電変換装置内の前 記走査手段が第1の位置を走査中に、前記第2の光電変換装置内の前記複数の受光素子か らの信号の読み出しを開始させるためのスタート信号を出力し、前記第2の解像度モード が選択された場合には、前記第1の光電変換装置内の前記走査手段が前記第1の位置より も走査開始位置に近い第2の位置を走査中に、前記第2の光電変換装置内の前記複数の受 光素子からの信号の読み出しを開始させるためのスタート信号を出力するように制御する とともに、前記第1の解像度モードが選択された場合には、前記第2の光電変換装置内の 前記走査手段が第1の位置を走査中に、前記第1の光電変換装置内の前記複数の受光素子 からの信号の読み出しを開始させるためのスタート信号を出力し、前記第2の解像度モー ドが選択された場合には、前記第2の光電変換装置内の前記走査手段が前記第1の位置よ りも走査開始位置に近い第2の位置を走査中に、前記第1の光電変換装置内の前記複数の 受光素子からの信号の読み出しを開始させるためのスタート信号を出力するように制御す るスタート信号切り換え手段を有することを特徴とする。

#### [0024]

また、本発明の画像読取装置は、上記イメージセンサを有し、前記イメージセンサを構成 する前記複数の光電変換装置が配列されている方向と垂直な方向に前記イメージセンサを 走査することを特徴とする。

10

20

30

### [0028]

### (作用)

本発明においては、マルチチップ実装された密着型イメージセンサにおいて、次のチップのシフトレジスタを起動するスタート信号を解像度切り換え信号により選択する手段を設けているため、解像度切り換え時においても、光電変換装置の継ぎ目において不連続ビットが生じない。

#### [0029]

また、本発明は、4 画素(a,b,c,d)を1プロックとし、高解像度モードでは同期クロック 1 でa,cのビットを、同期クロック 1 に反転した同期クロック 2 でb,dのビットを駆動し、低解像度モードでは、同期クロック 1 でa+bのビットを、同期クロック 2 でc+dのビットを画素加算により読み出す手段を設けているため、同一のクロックレートを用いても、解像度に応じた読み取りスピードが実現可能となる。また、解像度を複数段階に分けて、それぞれの解像度に応じて、隣接のチップの読み出し用スタート信号を送出することにより、一連の受光素子の読み出しに途切れを生じさせないようにしている。

### [0030]

# 【発明の実施の形態】

以下、本発明による実施形態について、図面を用いて詳細に説明する。

#### [0031]

#### (実施形態1)

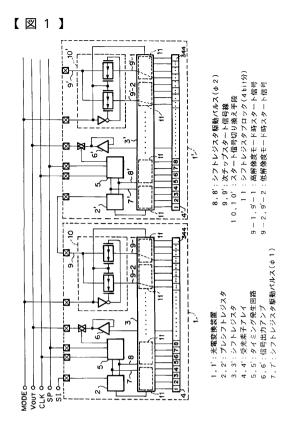

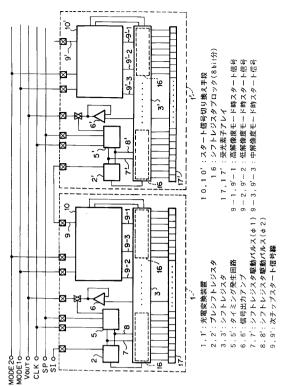

図1は本発明の実施形態1における光電変換装置を用いた密着型イメージセンサの回路ブロック図、図2は図1における8ビット分のシフトレジスタと受光素子の回路ブロック図、図4は図2の動作を示すタイミングチャート、図3は4画素分の受光素子の等価回路図である。

### [0032]

図 1 において、光電変換装置( 1 、 1 )がマルチ実装され、密着型イメージセンサが形成されている。尚、同図には 2 チップ分のみを図示しているが、本実施形態では例えば 1 5 チップを 1 列に配置しマルチ実装して、密着型イメージセンサを構成している。

# [0033]

各々の光電変換装置1,1′には、光電変換装置を駆動するクロック(CLK)、スタートパルス(SP)、解像度切り換え信号(MODE)が共通接続されている。

# [0034]

また、本実施形態においては、MODE信号がハイレベルの場合は高解像度モード(600 dpi)、MODE信号がローレベルの場合は低解像度モード(300dpi)の解像度が得られる構成としている。

# [0035]

さらに、本実施形態の各々の光電変換装置(1、1 )は、4bitの遅延を有するプレシフトレジスタ(2、2 )、シフトレジスタ(3、3 )、344ビットの受光素子アレイ(4、4 )、タイミング発生回路(5、5 )、信号出力アンプ(6、6 )を有している。ここで、シフトレジスタ(3、3 )は4ビット分のシフトレジスタブロック(11)から構成されている。

#### [0036]

また、高解像度モード時のスタート信号(9-1、9 -1)、及び低解像度時のスタート信号(9-2、9 -2)をスタート信号切り換え手段(10、10 )を用いて選択することにより、次チップスタート信号(9、9 )が得られる構成となっている。

# [0037]

また、次チップスタート信号(9、9 )を切り換える切り換え手段10は、次チップスタート信号(9、9 )を次段に出力するようなスタート信号を送る側のチップに設けた構成のみでなく、複数のスタート信号が次段に出力された後に、次チップスタート信号切り換え手段10から出力されるようなスタート信号を受け取る側のチップに設けた構成の

20

40

30

40

50

ものでもよい。また、低解像度読み出しの場合に、隣り合う 2 画素を加算して読み出すだけではなく、例えば偶数ビットの画素を間引いて読み出すことも可能である。

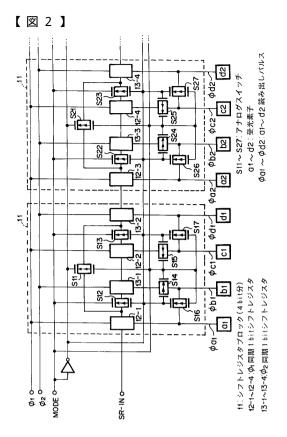

[0038]

図 2 は 8 ビット分のシフトレジスタと受光素子の回路ブロック図である。シフトレジスタは 4 ビットを 1 ブロックとするシフトレジスタブロック(1 1 )から構成されており、シフトレジスタブロック(1 1 )は 1 同期の 1 ビットシフトレジスタ(1 2 - 1 ~ 1 2 - 4 )、 2 同期の 1 ビットシフトレジスタ(1 3 - 1 ~ 1 3 - 4 )、及びモード信号を切り換えるアナログスイッチ(S 1 1 ~ S 2 7 )で構成されている。

[0039]

また、シフトレジスタブロック(11)は読み出しパルス線( a1 ~ d2)で受光素 1/子(a1 ~ d2)と接続されている。

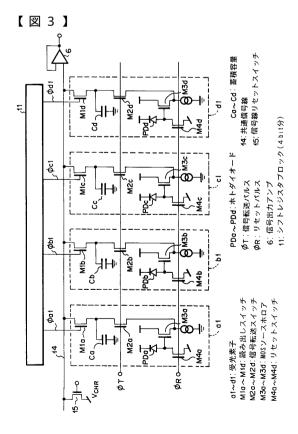

[0040]

図3は図2における受光素子4画素分の等価回路であり、各々の受光素子(a1~d1)は、光電変換手段となるホトダイオード(PDa~PDd)、読み出しスイッチ(M1a~M1d)、信号転送スイッチ(M2a~M2d)、MOSソースホロア(M3a~M3d)、上記光電変換手段をリセットする手段であるリセットスイッチ(M4a~M4d)、一時的に電荷を蓄積する蓄積容量(Ca~Cd)で構成されている。

[0041]

以下、本実施形態の動作について説明する。

[0042]

図3に示す各受光素子a1~d1において、ホトダイオード(PDa~PDd)にて光電変換により生成した光キャリアはMOSソースホロア(M3a~M3d)で電荷電圧変換され、信号転送パルス(T)にて全画素一括で蓄積容量(Ca~Cd)に転送される。続いて、シフトレジスタ11から順次ハイとなる読み出しパルス(a1~d1)によって順次読み出しスイッチ(M1a~M1d)をオン状態にし、共通信号線(14)に信号電圧が容量分割し読み出される。

[0043]

本実施形態においては、高解像度モード時には読み出しパルス( a 1 ~ d 1)は順次オンしていくが、低解像度モード時には、隣接する 2 ビット、すなわちシフトレジスタ 1 1 から走査する a 1 と b 1 が同時にオンし、続いて c 1 と d 1 が同時にオンする構成となる。従って、低解像度モードにおいては 2 画素の容量分割加算により、信号電圧を高解像度モード時より大きくすることが可能となる。尚、上記の容量分割加算については、例えば、特開平 4 - 4 6 8 2 号公報に開示されている。

[0044]

次に、図2、図3を用いてシフトレジスタ部の動作を説明する。

[0045]

図2において、MODE信号がハイレベルの場合は、S11、S21、S16、S17、S26、S27のアナログスイッチがオフ状態となり、一方、S12、S13、S14、S15、S22、S23、S24、S25がオン状態となる。従って、解像度切り換えの無い、通常のシフトレジスタ動作となり、各受光素子用の読み出し制御パルス a1から d2までは時系列的に順次オン状態となる。なお、図2においては、画像信号の出力線を図示していないが、制御パルス a1から d2による順次ハイとなるのに同期して、各受光素子a1からd2の受光電荷が出力線に出力される。

[0046]

次に、MODE信号がローレベルの場合は、S11、S21、S16、S17、S26、S27のアナログスイッチがオン状態となり、一方、S12、S13、S14、S15、S22、S23、S24、S25がオフ状態となる。従って、シフトレジスタ(12-1)にシフトパルスが入力されると、シフトレジスタ(12-1)から a1と b1が 1同期で出力され、a1とb1の受光素子の信号を同時に読み出す。続いて、シフトパルスはアナログスイッチS11を介してシフトレジスタ(13-2)に入力され、シフトレ

20

30

40

50

ジスタ(13-2)から c1と d1が 2同期で出力され、c1とd1の受光素子の信号を同時に読み出す。本低解像度読み出しのモードの場合も、不図示の出力線に受光素子a1とb1、c1とd1、a2とb2、c2とd2というように対の受光素子の加算電荷が順次読み出される。

### [0047]

このとき、シフトレジスタ(13-1)とシフトレジスタ(12-2)はシフトパルスが入力されないため動作しない。同様にして、シフトレジスタ(12-3)から a2と b2が 1同期で出力され、a2とb2の受光素子の信号を同時に読み出し、シフトレジスタ(13-4)から c2と d2が 2同期で出力され、c2とd2の受光素子の信号を同時に読み出す。

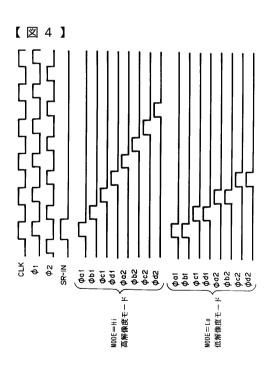

[0048]

以上の動作のタイミングチャートを図4に示す。図4において、クロック信号CLKと、同期信号 1 , 2 が高解像度モードと低解像度モードに共通に供給され、シフトレジスタのスタート信号SRがハイとなると共に高解像度モードと低解像度モードのそれぞれの画像信号出力が得られる。同図より、同一のクロックレートにおいて、低解像度モードにおいては、高解像度モード時の2倍の読み出し速度で読み出すことが可能であることがわかる。

[0049]

次に、次チップスタート信号の切り換え手段について説明する。

[0050]

図1において、プレシフトレジスタ(2、2 )は4ビットの遅延を有するため、4ビット前の信号を次チップのスタート信号として出力しなければならない。プレシフトレジスタ(2、2 )によって、スタート信号SPから時間調節の必要がなく、前段の光電変換装置の読み出しが終了した後、同一タイミングに従って空隙のない連続的な画像信号を得ることができる。従って、高解像度モードの場合には、光電変換装置(1、1 )はそれぞれ344ビットの信号を有するため、341ビット目のシフトレジスタ信号(9-1、9 -1)を次チップスタート信号として用いる。

[0051]

また、低解像度モードにおいては、2画素加算信号が1ビットとなるため、光電変換装置(1、1 )は等価的に177ビットの信号を有することになる。従って、受光素子換算で337ビット目のシフトレジスタ信号(9-2、9-2)を次チップスタート信号として用いる。すなわち、次チップスタート信号を切り換えるスタート信号切り換え手段を設けることにより、解像度を切り換えても光電変換装置の継ぎ目の部分において画素信号は連続性を保つことが可能となる。

[0052]

尚、上記実施形態においては、光電変換装置のビット数を344ビットとしたが、4の倍数のビット数であれば幾つでも構わない。

[0053]

また、解像度も [ 高解像モード / 低解像モード ] が [ 6 0 0 d p i / 3 0 0 d p i ] の場合に限らず、例えば、 [ 4 0 0 d p i / 2 0 0 d p i ] 等の解像度でも構わない。

[0054]

更に、本実施形態は高解像度モードと低解像度モードの解像度比が 2 倍の場合を示したが、例えば、 6 画素を 1 ブロックとし、光電変換装置の画素数を 6 の倍数とすることで、 [600dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dpi/20dp

[0055]

また、電子複写機として、上記密着型イメージセンサを読み出す方向を主走査方向とし、その主走査方向に垂直な方向を副走査方向として、機構的に副走査方向にも画像原稿に対応して走査することにより、2次元状の読み取り信号を得て、この読み取り信号に応じて光学感光体に露光することにより、且つ複数の解像度に応じて被転写紙に転写することが

でき、機能的な自由度を増加することができる。

### [0056]

(実施形態2)

図 5 は本発明の実施形態 2 における光電変換装置を用いた密着型イメージセンサの回路ブロック図である。

#### [0057]

本実施形態においては、上記実施形態1に対して、更に解像度制御用の端子(MODE2)を追加し、高解像度モード(1200dpi)、中解像度モード(600dpi)、低解像度モード(300dpi)の3種類の解像度切り換えが可能な構成を示している。但し、各モードの解像度数は例示であり、目的に応じて任意に設定できるものである。

#### [0058]

図5において、各々の光電変換装置(1、1 )は、4 b i t の遅延を有するプレシフトレジスタ(2、2 )、光信号を順次読み出すためのシフトレジスタ(3、3 )、6 8 8 ビットの受光素子アレイ(1 7、1 7 )、タイミング発生回路(5、5 )、信号出力アンプ(6、6 )を有している。ここで、シフトレジスタ(3、3 )は8 ビット分のシフトレジスタブロック(1 6)から構成されている。また、高解像度モード時のスタート信号(9 - 1、9 - 1)、中解像度モード時のスタート信号(9 - 3、9 - 3)及び低解像度時のスタート信号(9 - 2、9 - 2)を、スタート信号切り換え手段(10、10 )を用いて選択することにより、次チップスタート信号(9、9 )が得られる構成となっている。

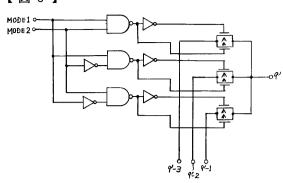

#### [0059]

図6にスタート信号切り換え回路10の概略図を示す。図において、MODE1,2の入力に対して、高解像度モード時のスタート信号(9・1、9 ・1)、中解像度モード時のスタート信号(9・3、9 ・3)、及び低解像度時のスタート信号(9・2、9 ・2)に対応した次チップスタート信号(9、9 )を得ることのできる構成例を示す。本例のように切り換え回路10は、2つの各ビットのMODE1,2から3種の信号を選択出力すればよく、論理回路としては、種々の回路が想定されるので、詳細な説明は省略する。

# [0060]

また、次チップスタート信号(9、9 )を切り換える切り換え手段10は、次段に出力するような送る側のチップに設けた構成のみでなく、複数のスタート信号が次段に出力された後に、スタート信号を受け取る側のチップに設けた構成のものでもよい。また、低解像度読み出しの場合に、隣り合う2画素を加算して読み出すだけではなく、例えば偶数ビットの画素を間引いて読み出すことも可能である。

# [0061]

本実施形態においては、高解像度モード時は1画素で1ビット、中解像度モード時は2画素加算により2画素で1ビット、低解像度モード時は4画素加算により4画素で1ビットとなる。従って、シフトレジスタブロック(16)は8画素分が1ブロックとなり、実施形態1と同様に構成することができる。

#### [0062]

本実施形態に示すように、本発明においては、解像度モードを3種類、もしくはそれ以上に設定することも可能であり、かつ、各々の解像度に応じた読み取り速度が実現でき、光電変換装置の継ぎ目においても信号の不連続を生じさせないようにすることが可能となる

#### [0063]

また、本発明は1次元光電変換装置のみならず、2次元光電変換装置に応用しても有効であることは言うまでもない。本発明を2次元光電変換装置に応用する場合は画素レベルの解像度切り換えの他に、水平方向のみの解像度切り換え、垂直方向のみの解像度切り換え等も実現可能である。

# [0064]

50

10

20

30

# 【発明の効果】

以上説明したように、本発明により、解像度切り換え時においても光電変換装置の継ぎ目 において信号が不連続にならず、かつ、解像度に応じた読み取り速度が得られるため、そ の効果は絶大である。

# [0065]

また、当該イメージセンサを用いた電子複写機等に用いることにより、高画質、通常画質 等という被転写紙に要求される画質に応じて出力することができ、機能上の自由度を増加 できる。

### 【図面の簡単な説明】

- 【図1】本発明の実施形態1における密着型イメージセンサの回路ブロック図である。

- 【図2】本発明の実施形態による8ビット分のシフトレジスタと受光素子の回路ブロック 図である。

- 【図3】本発明の実施形態による受光素子の等価回路図(4画素分)である。

- 【図4】本発明の実施形態による動作を示すタイミングチャートである。

- 【図5】本発明の実施形態2における光電変換装置を用いた密着型イメージセンサの回路 ブロック図である。

- 【図6】本発明の実施形態によるスタート信号切り換え回路の一例の回路図である。

- 【図7】従来技術(1)における密着型イメージセンサ用集積回路の回路図である。

- 【図8】従来技術(2)におけるイメージセンサチップの等価回路図である。

- 【図9】従来技術(2)におけるタイミングチャートである。

### 【符号の説明】

- 光電交換装置 1, 1

- 2 、 2 プレシフトレジスタ

- 3, 3 シフトレジスタ

- 4 \ 4 受光素子アレイ

- 5 、 5 タイミング発生回路

- 7、7 シフトレジスタ駆動パルス (1)

- 8 \ 8 シフトレジスタ駆動パルス(2)

- 9 \ 9 次チップスタート信号線

- 9-1、9-1 高解像モード時スタート信号線

- 9 2 \ 9 2 低解像モード時スタート信号線

- 10、10 スタート信号切り換え手段

- 11 シフトレジスタブロック(4ビット分)

- 12-1~12-4 1同期1ビットシフトレジスタ

- 1 3 1 ~ 1 3 4 2 同期 1 ビットシフトレジスタ

- 14 共通信号線

- a 1 ~ d 2 受光素子

- a 1 ~ d 2 a 1 ~ d 2 読み出しパルス

- M 1 a ~ M 1 d 読み出しスイッチ

- M4a~M4d リセットスイッチ

- PDa~PDd ホトダイオード

20

10

30

【図6】

【図7】

【図8】

| ** 7. *********************************                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   | 48i - Innonn |   | 1-49il-1011 | ביייין ווין ויייל וווייינון ווייינון ווייינון ווייינון ווייינון ווייינון ווייינון ווייינון ווייינון ווייינון ו |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--------------|---|-------------|----------------------------------------------------------------------------------------------------------------|

| \$ \frac{2}{2} \fra | 8 | S            | Q | <u> </u>    | ,<br>Tuo'                                                                                                      |