(19) **日本国特許庁(JP)**

# (12)特 許 公 報(B2)

(11)特許番号

特許第4754201号 (P4754201)

(45) 発行日 平成23年8月24日(2011.8.24)

(24) 登録日 平成23年6月3日(2011.6.3)

(51) Int. Cl.

F 1

HO1L 23/12 (2006.01)

HO1L 23/12 5O1Z

請求項の数 6 (全 14 頁)

(21) 出願番号 特願2004-298611 (P2004-298611) (22) 出願日 平成16年10月13日 (2004.10.13)

(65) 公開番号 特開2006-114595 (P2006-114595A)

(43) 公開日 平成18年4月27日 (2006. 4. 27) 審査請求日 平成19年6月19日 (2007. 6. 19)

||(73)特許権者 500174247

エルピーダメモリ株式会社 東京都中央区八重洲2-2-1

||(74)代理人 100123788

弁理士 宮崎 昭夫

(74)代理人 100106138

弁理士 石橋 政幸

(74)代理人 100127454

弁理士 緒方 雅昭

|(72)発明者 清水 浩也

茨城県土浦市神立町502番地 株式会社

日立製作所 機械研究所内

|(72)発明者 片桐 光昭

東京都中央区八重洲二丁目2番1号 エル

ピーダメモリ株式会社内

最終頁に続く

(54) 【発明の名称】半導体装置

### (57)【特許請求の範囲】

## 【請求項1】

開口部を含む基板であって、前記開口部は、当該開口部を挟んで対向する第1及び第2の領域によって規定され、前記基板は、前記第1の領域に配置された第1の接続端子群と 前記第2の領域に配置された第2の接続端子群とをさらに備える、前記基板と、

直線状に並べられた複数のパッドを含む半導体チップであって、当該半導体チップは前記基板の前記開口部から前記複数のパッドが露出するように前記基板に実装され、前記複数のパッドは、第1のパッド群と当該第1のパッド群との間に前記複数のパッドのうちの残りのいかなるパッドも挟み込むことなく前記第1のパッド群に隣接して配置される第2のパッド群とを含み、当該第1及び第2の

パッド群の各々は、電源パッドとグランドパッドと 2 つの信号パッドとを含む、前記半導体チップと、

前記第1のパッド群を前記第1の接続端子群のうちの対応する複数の端子群に接続する 第1の配線群と、

前記第2のパッド群を前記第2の接続端子群のうちの対応する複数の端子群に接続する 第2の配線群と、を備え、

前記第1の領域及び前記第2の領域は、前記第1の配線群が第1の方向に延伸し、前記第2の配線群が前記第1の方向と反対の第2の方向に延伸するように配置され、

前記第1のパッド群に含まれる全てのパッドから延伸する全ての配線は前記第1の方向 に延伸し、

前記第2のパッド群に含まれる全てのパッドから延伸する全ての配線は前記第2の方向 に延伸することを特徴とする半導体装置。

### 【請求項2】

前記複数のパッドは、第3のパッド群と、前記第2のパッド群と前記第3のパッド群とに挟まれた第4のパッド群とをさらに含み、前記第3及び第4のパッド群の各々は、電源パッドとグランドパッドと2つの信号パッドとを含み、前記第3のパッド群を前記第2の接続端子群のうちの対応する複数の端子群に接続する第3の配線群と、前記第4のパッド群を前記第1の接続端子群のうちの対応する複数の端子群に接続する第4の配線群とをさらに含むことを特徴とする請求項1に記載の半導体装置。

#### 【請求項3】

10

前記第3のパッド群に含まれる全てのパッドから延伸する全ての配線は前記第2の方向 に延伸し、

前記第4のパッド群に含まれる全てのパッドから延伸する全ての配線は前記第1の方向に延伸することを特徴とする請求項2に記載の半導体装置。

### 【請求項4】

前記第1及び第2のパッド群の夫々において、前記電源パッドと前記グランドパッドとが、前記2つの信号パッドの間にはさまれていることを特徴とする請求項1に記載の半導体装置。

### 【請求項5】

20

前記半導体チップは、複数の入出力回路を含み、前記第1及び第2のパッド群の夫々の前記<u>2つ</u>の信号パッドは、前記複数の入出力回路のうちの2つの入出力回路にそれぞれ対応して電気的に接続され、前記第1及び第2のパッド群の夫々の前記電源パッドと前記グランドパッドの各々は、前記2つの入出力回路に共通に電気的に接続されることを特徴とする請求項1に記載の半導体装置。

#### 【請求項6】

前記半導体チップ上の全ての前記電源パッドと前記グランドパッドの総数を、前記半導体チップ上に配置可能な前記複数のパッドの総数で除した値が、0.4よりも大きいことを特徴とする請求項1に記載の半導体装置。

## 【発明の詳細な説明】

30

### 【技術分野】

## [0001]

本発明は、半導体装置に係り、特にコンピュータなどの記憶素子に用いられるDRAM (Dynamic Random Access Memory)のうち、ファインピッチ・ボール・グリッド・アレイ (FBGA: Fine Pitch Ball Grid Array)に用いる半導体チップに利用して有効な技術に関する。

## 【背景技術】

### [0002]

従来の半導体装置としては、例えば、特開2001-185576号公報(特許文献1)に示されるものがある。この特許文献1の半導体装置では、半導体装置の電源系インダクタンスを低減するために、信号線用パッド(信号用パッド)と電源電位用パッド(電源パッド)と接地電位用パッド(グランドパッド)とが、配線基板における半導体ペレット(半導体チップ)をボンディングした第一主面に形成されているとともに、第二主面に形成された信号用端子、電源電位用端子、接地電位用端子にスルーホール導体で互いに電気的に独立して接続されており、電源電位用パッドと接地電位用パッドとが信号線用パッドの両脇にそれぞれ配置されているように構成したものである。

#### [0003]

【特許文献 1 】特開 2 0 0 1 - 1 8 5 5 7 6 号公報

#### 【発明の開示】

### 【発明が解決しようとする課題】

#### [0004]

しかし、特許文献 1 では、半導体装置の電源系インダクタンスを低減するのに有効な手段が示されているものの、半導体装置に用いられる半導体チップのサイズシュリンクについては開示されていない。

## [0005]

DRAMに代表される半導体装置においては、半導体チップのシュリンク、つまりサイズの縮小が望まれている。半導体チップを形成するシリコンウェハから取得できるチップ数を増すことにより、最終的な半導体装置のコストを低減できるためである。

### [0006]

このため、半導体メーカでは、チップ内部の製造プロセスの改良により、半導体装置を構成するトランジスタ、キャパシタなどの素子やチップ内にはりめぐらせる配線の寸法を縮小することに努力が向けられている。このような努力により、同一容量のDRAMにおいて、チップサイズが格段に縮小されつつある。

### [0007]

一方、半導体チップとパッケージ、実装基板またはメモリモジュールとの間で信号をやりとりしたり、電源電位・接地電位をチップ内部に供給したりするためのパッドについても、チップ内配線や半導体素子の製造工程と類似の技術を用いて、原理的には同様なサイズ縮小が得られるようになっている。

#### [00008]

しかし、これらのパッドには、パッケージに代表されるチップ外部と信号などをやりとりする必要がある。従って、パッケージングなど「後工程」と呼称される製造工程で利用できる寸法を有することが必要である。配線基板を用いたFGBAやテープ基板を用いたFBGAの場合、ワイヤボンディングや比較的柔軟なテープ基板11によりパッド6とパッケージ内部の配線9を信頼性良く接続する必要がある。これらの後工程における接続技術はチップ内部の加工寸法ほど急速に進歩しているわけではないため、チップ内部の加工寸法が大幅に縮小しても、半導体チップとパッケージの接続手段の制約によって現状と同一のパッド寸法及びパッドピッチでしか行えない事態が生じる。現在の半導体製造技術で用いられている半導体チップのパッドは、1辺が概略80~100μmの正方形ないし長方形で形成され、パッドピッチがそれよりも大きな寸法で形成されている。

## [0009]

また、特許文献1に開示されているように、信号パッドの両脇に電源パッドとグランドパッドをチップ主面に配置することは、電気的特性の面からは好適であるが、このことは同時にパッド数の増加を招き、チップのサイズ縮小即ちチップシュリンクの実現を妨げるという問題があった。一方で、チップシュリンクのみに注目して、電源パッド、グランドパッドの数を減少させ過ぎると、電気的な特性、即ち、電源やグランド配線のインダクタンスを十分に小さいものとすることができず、結果的に半導体装置を高速で動作させることができないという問題があった。

### [0010]

このような状況は、半導体素子の製造工程の改良により、半導体チップ 4 のサイズを縮小できる状況にあるにもかかわらず、チップ主面に配置すべきパッドの制約により、更なるチップサイズの縮小ができない事態をもたらしている。

#### [0011]

本発明者らは、十分な電気的特性、即ち、低ノイズ化を実現できる電源やグランド配線の低インダクタンス化を達成しつつ、チップサイズの縮小を実現しうる技術として検討を 重ねた結果、上記課題を解決する手段を見出した。

## [0012]

本発明の目的は、低い電源系インダクタンスを維持して半導体装置の高速動作を確保しつつ、半導体チップのシュリンクを可能としてコスト低減を図ることができる半導体装置を提供することにある。

### 【課題を解決するための手段】

10

20

30

#### [0013]

本発明の一態様は、開口部を含む基板であって、前記開口部は、当該開口部を挟んで対向する第1及び第2の領域によって規定され、前記基板は、前記第1の領域に配置された第1の接続端子群と前記第2の領域に配置された第2の接続端子群とをさらに備える、前記基板と、

直線状に並べられた複数のパッドを含む半導体チップであって、当該半導体チップは前記基板の前記開口部から前記複数のパッドが露出するように前記基板に実装され、前記複数のパッドは、第1のパッド群と当該第1のパッド群との間に前記複数のパッドのうちの残りのいかなるパッドも挟み込むことなく前記第1のパッド群に隣接して配置される第2のパッド群とを含み、当該第1及び第2の

パッド群の各々は、電源パッドとグランドパッドと2つの信号パッドとを含む、前記半導体チップと、

前記第1のパッド群を前記第1の接続端子群のうちの対応する複数の端子群に接続する 第1の配線群と、

前記第2のパッド群を前記第2の接続端子群のうちの対応する複数の端子群に接続する 第2の配線群と、を備え、

前記第1の領域及び前記第2の領域は、前記第1の配線群が第1の方向に延伸し、前記 第2の配線群が前記第1の方向と反対の第2の方向に延伸するように配置され、

<u>前記第1のパッド群に含まれる全てのパッドから延伸する全ての配線は前記第1の方向</u>に延伸し、

前記第2のパッド群に含まれる全てのパッドから延伸する全ての配線は前記第2の方向に延伸することを特徴とする半導体装置を提供する。

#### 【発明の効果】

#### [0020]

本発明の半導体装置によれば、低い電源系インダクタンスを維持して半導体装置の高速動作を確保しつつ、半導体チップのシュリンクを可能としてコスト低減を図ることができる。

【発明を実施するための最良の形態】

### [0021]

以下、本発明の複数の実施例について図を用いて説明する。各実施例の図における同一符号は同一物または相当物を示す。

## [0022]

まず、本発明の第1実施例の半導体装置を図1から図4及び図7を用いて説明する。本実施例において、本発明に係る半導体装置は、用途的には、DDR2規格のDRAMであって、パッケージとしてはFBGAを用いるものである。

#### [0023]

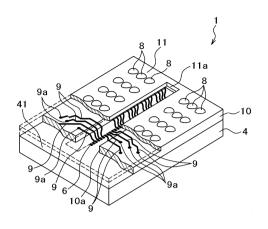

本実施例の半導体装置1の全体構成に関して図1を参照しながら説明する。図1は本発明の第1実施例の半導体装置の一部断面斜視図である。

### [0024]

本実施例の半導体装置 1 は、半導体チップ 4 と、外部接続端子を構成する複数の半田ボール 8 と、パッド 6 と半田ボール 8 とを電気的に接続する配線 9 と、接着層 1 0 と、テープ基板 1 1 と、を主要構成要素として構成されている。半導体チップ 4 は、半導体素子(DRAM素子)を構成する複数のバッファ 4 a (図 2 参照)と、チップ主面 4 1 の中央部に配列された複数のパッド 6 とを有する。

#### [0025]

この半導体装置 1 は、FBGAを用いるDRAMの一例であり、ワイヤやガラス含浸工ポキシ樹脂を用いる配線基板を使用することなく、半導体チップ 4 のパッド 6 と半田ボール 8 とを配線 9 を介して接続することにより構成されている。半導体チップ 4 の主面 4 1 側には、接着層 1 0 を介してテープ基板 1 1 が接着されている。接着層 1 0 及びテープ基板 1 1 の中央部には帯状の開口部 1 0 a、 1 1 a がそれぞれ形成されている。接着層 1 0

10

20

30

40

の開口部10aは、テープ基板11の開口部11aに対して、中心が一致して同じ長さに 形成されると共に、若干幅広に形成されている。半導体チップ4は、パッド6が配列され ている方向の辺の長さが11mmより小さいものである。

### [0026]

パッド6はこれらの開口部10a、11aの中心部に位置して配列されている。パッド6の配列は一列で直線状になっている。なお、半導体装置1の中央に位置する開口部10a、11aは、半導体チップ4、主面41にあるパッド6、及び配線9などを保護するために、樹脂封止がなされることが多い。

### [0027]

配線9は、パッド6に電気的に接続されると共に、半田ボール8への接続部9aを有している。接続部9aは、配線9の一部を構成するものであり、パッド接続側と反対側に位置して設けられ、テープ基板11のチップ主面側から反対側に貫通してグリッド状に配置された半田ボール8に接続されている。配線9は、例えば銅、金などにより形成されており、電解めっき工程を経るため、めっき時の給電の必要性から、外部へ接続するための給電配線が接続部9aから延長して形成される場合もある。

#### [0028]

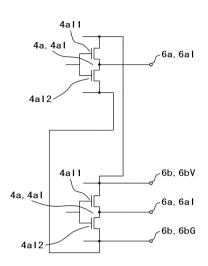

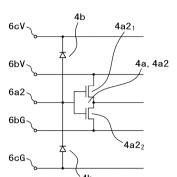

次に、半導体装置 1 の半導体チップ 4 内にある半導体素子を構成する入出力バッファ 4 a 1 に関して、図 2 を参照しながら説明する。図 2 は本実施例における半導体チップ 4 内にある入出力バッファ 4 a 1 の回路図の一部である。

## [0029]

半導体装置1の半導体チップ4におけるパッド6は、信号パッド6aと電極パッド6bとから構成されている。信号パッド6aは、2つの入出力バッファ4a1にデータを入出力する2つの入出力パッド6a1からなっている。電極パッド6bは、半導体素子に電源電圧を供給する電源パッド6bVと、半導体素子に接地電圧を供給するグランドパッド6bGとに分けられる。

### [0030]

電源パッド6bVは入出力バッファ4a1を構成する一方のトランジスタ4a11の電源に接続され、グランドパッド6bGは入出力バッファ4a1を構成する他方のトランジスタ4a12のグランドに接続されている。従って、1つの入出力バッファ4a1については、これに接続される信号パッド6a1を流れる信号に伴う信号線とは逆向きの帰還電流が対応する電源パッド6bVまたはグランドパッド6bGを通じて流れることになる。このため、入出力バッファ4a1の特性を電気的に良好なものにする(即ち、入出力バッファ4a1の動作時のノイズを低減する)ためには、入出力バッファ4a1の電源やグランドに接続される電源パッド6b1、グランドパッド6b2を信号パッド6aに隣接して配置するのが好適である。

## [0031]

しかしながら、全てのバッファ4aから信号パッド6a、電源パッド6bV、グランドパッド6bGをチップ主面41に引き出して配置すると、バッファ4aの信号パッド数の3倍のパッド数を設けることが必要になる。このことがチップシュリンクを図る面から大きな障害となっている。

## [0032]

そこで、本実施例では、各入出力バッファ4a1から1個ずつの電源パッド6bV及びグランドパッド6bGをチップ主面41に引き出すのではなく、図2に示すように、複数個の入出力バッファ4a1をひとまとめにして、電源とグランドを共通にした電源パッド6bV及びグランドパッド6bGをチップ主面41に引き出すこととしている。具体的には、電源パッド6bVは、一方の入出力バッファ4a1を構成する一方のトランジスタ4a11の電源と、他方の入出力バッファ4a1を構成する一方のトランジスタ4a11の電源とに共通して接続されると共に、グランドパッド6bGは、一方の入出力バッファ4a1を構成する他方のトランジスタ4a12のグランドと、他方の入出力バッファ4a1を構成する他方のトランジスタ4a12のグランドとに共通して接続される。このような

10

20

30

40

10

20

30

40

50

構成をとることにより、入出力バッファ4aに係わるパッド数の増加を防止して、チップシュリンクに対して好適なパッド数とすることができる。

### [0033]

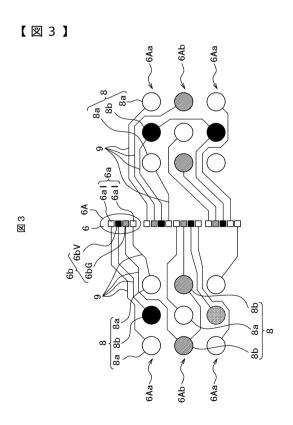

次に、パッド6と半田ボール8と配線9に関して図3を参照しながら説明する。図3は本実施例の半導体装置におけるパッド6と半田ボール8と配線9との配置関係を説明する模式図である。

#### [0034]

パッド 6 は、複数の入出力バッファ 4 a に共通する一対の電源パッド 6 b V 及びグランドパッド 6 b G と、その入出力バッファ 4 a と信号のやり取りをする複数の信号パッド 6 a 1 とからなるパッド群 6 A を有している。このパッド群 6 A は、複数のパッド群 (4つのパッド群 6 A を図示)から構成されている。

#### [0035]

各パッド群6Aにおける各信号パッド6a1は、当該パッド群6Aにおける電源パッド6bV及びグランドパッド6bGの何れかに隣接するように設けられている。また、各パッド群6Aにおける各信号パッド6a1から延びる各配線9は、隣接した電源パッド6bVまたはグランドパッド6bGから延びる配線9に沿って延びるように設けられている。かかる構成によって、低い電源系インダクタンスを維持しつつ、パッド数及び配線数の低減して、半導体チップのシュリンクを可能とし、コスト低減を図ることができる。

#### [0036]

各配線 9 は、各パッド 6 からパッド群 6 A 毎に同一方向に延びるように設けられている。これによって、低い電源系インダクタンスを確実に得ることができる。

#### [0037]

パッド6の配列は一列で構成され、半田ボール8はパッド6の配列の両側にグリッド状に設けられ、配線9はパッド群6A毎に交互に異なる側に延びるように設けられている。これによって、低い電源系インダクタンスを確実に得ることができるとともに、パッド6と半田ボール8と配線9との配置を最もコンパクトにすることができ、格段の半導体チップ4の小型化を図ることができる。

#### [0038]

具体的には、パッド群6Aは、2つの入出力バッファ4a1に共通する一対の電源パッド6bV及びグランドパッド6bGと、その2つの入出力バッファ4a1と信号のやり取りをする2つの信号パッド6a1とからなるパッド群6Aを複数有している。また、半田ボール8はパッド6の配列の両側に3列のグリッド状にそれぞれ設けられている。さらに、3列の半田ボール8は、両側に信号をやり取りする半田ボール8aが位置され中央に外部電源に接続される半田ボール8bが位置される行6Aaと、両側に外部電源に接続される半田ボール8bが位置される行6Aaと、両側に外部電源に接続される半田ボール8bが位置され中央に信号をやり取りする半田ボール8aが位置される行6Abとが交互に設けられている。そして、各パッド群6Aは2つの信号パッド6a1、6a1の間に一対の電源パッド6bV及びグランドパッド6bGを配置し、一対の電源パッド6bV及びグランドパッド6bGを配置し、一対の電源パッド6bV及びグランドパッド6bGから延びる配線9は2つの信号パッド6a1、6a1から延びる配線9の間を延びるように形成されている。

#### [0039]

図3では、DDR2のデータピン規格、即ち、チップ内では入出力バッファ4aに接続される半田ボール8の配置を基に、図2に示すような2個の入出力バッファ4aをひとまとめにした上で、好適なパッド6の配置例と配線9の引き回し例を示すものである。このようなパッド配置により、ひとまとめにした2個のバッファ4aに接続される2個の信号パッド6aからボールへと引き出される信号配線9と、同様にバッファ4aの電源及びグランドに接続される電源パッド6bV及びグランドパッド6bGから半田ボール8bに引き出される配線9は、縦に並ぶパッド列を中心軸とすると、それぞれが同じ側に引き出されることになる。このように、一組にしたバッファ4aの信号配線9と電源配線9、グランド配線9が同一の方向に並ぶことにより、それらの配線9、9間の相互インダクタンスが増加し、電源やグランドの実効的インダクタンスは低減することになる。これらの実効

10

20

30

40

50

### [0040]

なお、図3においては、半田ボール8に比べ寸法のスケールが小さいパッド6を拡大して描いてある。

### [0041]

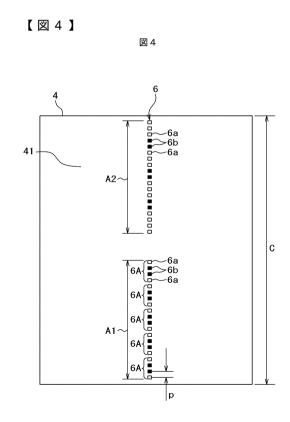

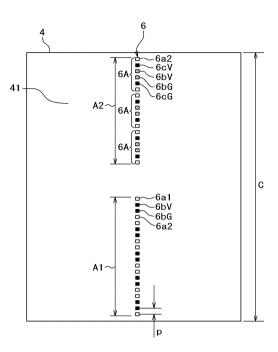

次に、半導体チップ4のパッド数に関して図4を参照しながら説明する。図4は本実施例における半導体チップ4の最適なパッド数を説明するためのチップ平面図である。

## [0042]

パッド6をごくおおざっぱに分けると、メモリセルと外部の素子や半導体装置、電子機器と信号をやりとりするための信号パッド6 a と、半導体装置自身に電源電位や接地電位を供給するための電源パッド6 b、グランドパッド6 bに大別できる。信号パッド6 a は、更に詳細には、データを入出力するパッド6 a 1 と、半導体装置を外部から制御したり、データを格納または取り出したりする番地の情報を半導体装置1に入力するためのパッドなどに分けられる。これらの信号パッド6 a は、当該半導体装置1の仕様、つまりメモリの容量や種別により決まっており、任意に数を決めることはできない。

### [0043]

一方、電源パッド 6 b V やグランドパッド 6 b G は、半導体装置 1 の電気的特性を確保するため、同一種類のパッドが複数準備されるが、上述したように複数の D R A M 素子に共用化してその数を低減することが可能であり、本実施例はこのことを利用してなされたものである。

### [0044]

本実施例では、図4に示すように、各パッド6の中心を紙面の縦方向に一致させて一列に配列されているが、チップ主面41に配置される半導体メモリ素子、トランジスタ、チップ内配線の配置上の都合などから、図4の紙面横方向に数百μm程度ずれたパッドが配置されることもある。また、本実施例では、図4に示すように、パッド6が等間隔に配置されているが、上記同様の理由で部分的にパッドピッチが大きくなることもある。パットの損耗を防ごされているが、上記同様の理由で部分的にパッドピッチが大きくなることもある。パットの損耗を防じまるため、概略80~100μm程度エッジからパッド6を離して配置されることが望ましい。DRAMの場合には、チップの概略中央付近には、半導体装置1を制御するため望までは、日本の場合には、チップの概略中央付近には、半導体装置1を制御するためまでとが多い。例外もあって、チップ中央付近に集中して半導体装置の制御回路を配置するとが多い。例外もあって、チップ中央付近に集中して半導体装置の制御回路を配置するのではなく、分散して配置する場合もある。このような場合、図で紙面上下に2分割して配置される場合もある。

### [0045]

図4において、パッド6が配置される方向に沿った半導体チップ4の長辺の長さCと、パッド6の配置が可能な領域の長さA(=A1+A2)と、パッド配置時の最小ピッチρとを表記してある。長さAと長さCとの間には、A<Cなる関係が成り立つ。パッド6はパッド配置が可能な領域Aに配置されているが、配置されるパッド6として信号パッド6はaと電源パッド6bまたはグランドパッド6bとがある。長さA1には入出力バッファ4a1が全て配置され、長さA2には入力バッファやその他の素子が混在されている。通常のDRAMでは、このような入出力バッファの電源またはグランドと、入出力バッファ以外の電源またはグランドは、チップ内部で分離して形成されている。更に、通常このような入出力バッファは、チップの主面において、ある領域にまとめて配置されるため、入出力バッファに接続される信号パッドも入出力バッファの電源やグランドに接続される電源パッド、グランドパッドも、チップ主面に分散して配置されるのではなく、ある程度の範

囲を区切って配置されるのが普通である。

### [0046]

そして、本実施例では、電源パッド 6 b V 及びグランドパッド 6 b G の総数を N 1 (電極パッド 6 b の総数 N 1 ) としたとき、パッド配置の可能な領域 A ( = A 1 + A 2 ) に配置できるパッドの総数 ( A / p ) と N 1 の間に、N 1 / ( A / p ) > 0 . 4 なる関係を満たすように、電極パッド 6 b の総数 N 1 を調整したものである。この点からも、低い電源系インダクタンス及び半導体チップ 4 の小型化を図ることができる。

### [0047]

また、本実施例では、パッド配置の可能な領域 A 1 における電極パッド 6 b の総数 N 2 としたとき、パッド配置の可能な領域に配置できるパッドの総数 ( A 1 / p ) と総数 N 2 の間に、N 2 / ( A 1 / p ) > 0 . 1 2 なる関係を満たすように電源パッドとグランドパッドの総数を調整したものである。この点からも、低い電源系インダクタンス及び半導体チップ 4 の小型化を図ることができる。

### [0048]

電極パッド 6 b の総数 N 1 、 N 2 の調整が重要な意味を持つのは、半導体チップ 1 のサイズが小さいときである。なぜなら、十分に半導体チップ 4 の寸法が大きいときには、配置できるパッド 6 の数も大きくでき、半導体装置 1 の仕様から決定される信号パッド 6 a 以外に、電気的特性を向上させる電極パッド 6 b の総数 N 1 、 N 2 を比較的容易に増加できるためである。

## [0049]

半導体チップ4の寸法が小さいとき、数を減らすことのできない信号パッド6aの数はそのままで、電極パッド6bの総数N1、N2を減ずることになるが、本実施例のように、最小ピッチpにパッド6を配置したときに配置できる長さAの全パッド数(A/p)に対する電極パッド6bの総数N1の比を0.4より大きくしたり、最小ピッチpにパッド6を配置したときに配置できる長さA1の全パッド数(A1/p)に対する電極パッド6bの総数N2の比を0.12より大きくしたりすれば、数百MHzの高いクロック周波数に同期して半導体装置が動作する場合でも、電源インダクタンスやグランドインダクタンスを低いレベルに維持できるので、ノイズによる誤動作が無く、高速での動作を可能にする。

## [0050]

なお、図4においては、作図の関係上、実際のDRAMよりもパッド6の総数を減じて描いてある。

### [0051]

次に、本発明の第2実施例について図5及び図6を用いて説明する。図5は本発明の第2実施例の半導体装置の半導体チップにおける入力バッファの回路図、図6は第2実施例における半導体チップ4の最適なパッド数を説明するためのチップ平面図である。この第2実施例は、次に述べる通り第1実施例と相違するものであり、その他の点については第1実施例と基本的には同一である。

### [0052]

図5に示す入力バッファ4a2は、第1実施例で述べた入出力バッファ4a1に比べると、次のように相違する。入力バッファ4a2に接続される信号パッド6a2は、半導体チップ4の内部で、少なくとも2個の保護ダイオード4bを介して、専用の電源パッド6cV、専用のグランドパッド6cGに接続されている。一方で、入出力バッファ4a1と同様、バッファを構成する一方のトランジスタ4a21に接続される電源パッド6bV、バッファを構成する他方のトランジスタ4a22のグランドパッド6bGも存在する。

## [0053]

このような、入力バッファ4 a 2 におけるパッド6 の場合、主たる電源パッドやグランドパッドは、保護ダイオード4 b が接続されている電源パッド6 c V とグランドパッド6 c G である。なぜなら、信号パッド6 a 2 から M O S トランジスタ 4 a 2 1 、 4 a 2 2 を経て電源パッド6 b V やグランドパッド6 b G に至る経路の静電容量よりも、信号パッド

10

20

30

40

6 a 2 から、各々の保護ダイオード4 b を経て専用の電源パッド6 c V、専用のグランドパッド6 c G に至る経路の静電容量の方が桁違いに大きいため、このような半導体装置が動作する高周波数の帯域では、直列のインピーダンスが低いことになり、入力パッドに流れる信号電流に対応した帰還電流はこれらの電源パッド6 c V、グランドパッド6 c G を経て逆方向に流れやすいためである。

### [0054]

このため、入力バッファ4a2において、より高速動作の特性を向上させるためには、 入力バッファ4a2の電源やグランドに接続される電源パッド6bV、グランドパッド6 bGではなく、保護ダイオード4bに接続される電源パッド6cV、グランドパッド6c Gを見極めた上で、適正に配置することが必要となる。

### [0055]

第2実施例では、パッド配置パッド群6Aを構成する最も外側のパッドに信号パッド6a2に配置し、その内側に隣接して保護ダイオード4bに接続される電源パッド6cV、グランドパッド6cGを配置し、その内側に入力バッファ4a2の電源やグランドに接続される電源パッド6bV、グランドパッド6bGを配置している。

#### [0056]

そして、保護ダイオード4bに接続される電源パッド6cV、グランドパッド6cG、及び入力バッファ4a2の電源やグランドに接続される電源パッド6bV、グランドパッド6bGの総数N3を、パッド6を配置可能な領域A2に配置できるパッドの総数(A/p)と総数N3の間に、N3/(A/p)>0.3なる関係を満たすようにしたものである。このように、特に高速動作時に重要になる電源パッドとグランドパッドを確保することにより、低ノイズ化即ち高速動作を可能にすることができる。一方で、不用意に電源パッドやグランドパッドを増加させることがないので、チップシュリンクに対しても有効である。

### [0057]

なお、第2実施例では、パッド配置の可能な領域A2における電極パッド6bの総数N4としたとき、パッド配置の可能な領域に配置できるパッドの総数(A2/p)と総数N4の間に、N4/(A2/p)>0.18なる関係を満たすように電源パッドとグランドパッドの総数を調整したものである。この点からも、低い電源系インダクタンス及び半導体チップ4の小型化を図ることができる。

### [0058]

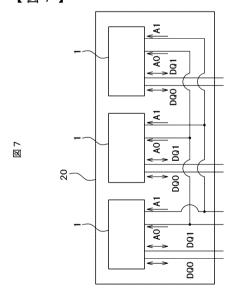

ここで、図7を用いて、入出力バッファ4a1の電源やグランドが電気的により厳しいことを説明する。図7は第2実施例の半導体装置1をメモリモジュール基板20に搭載した状態を示す図である。図7において、DQ×(×は数字)で示したピンが入出力バッファ4a1に接続される入出力ピンを示している。一方、A×(×は数字)と表記されているピンは、アドレスピンや制御ピンに代表される入力専用ピンであり、入力バッファ4a2に接続されている。また、図7中の矢印は当該ピンの信号の方向を示しており、入出力ピンDQ0、DQ1は両方向に信号が伝送されるのに対し、入力専用ピンA0、A1は外部から半導体装置1に向けてのみ信号が伝送される。

### [0059]

図7に示すように、入出力ピンDQ0、DQ1と入力専用ピンA0、A1は、半導体装置外部の配線トポロジーが異なり、入出力ピンDQ0、DQ1は各ピンつまりパッドが外部の別のLSIや半導体装置に直接1対1で接続されるのに対し、アドレスなど入力専用ピンA0、A1は、別のDRAMの同種のピンが束ねられた後に外部のLSIや半導体装置に接続される。このことが、入出力ピンDQ0、DQ1に対して、より電気的な配慮が必要な理由を示している。つまり、アドレスなどの入力専用ピンA0、A1には、複数のDRAMに分岐した後の信号が到達するため、分岐がない場合に比べ、生じる電源やグランドのノイズが小さい。入出力ピンDQ0、DQ1は途中に分岐が無く、外部のデバイスと1対1で接続されているため、よりノイズが生じやすく、対応する電源やグランドパッドの数を増加させる必要がある。

10

20

30

10

20

30

40

50

#### [0060]

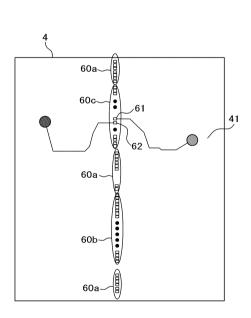

次に、本発明の第3実施例について図8を用いて説明する。図8は本発明の第3実施例における半導体チップ4のパッドの配置を説明するためのチップ平面図である。この第3 実施例は、次に述べる通り第1実施例と相違するものであり、その他の点については第1 実施例と基本的には同一である。

### [0061]

先に述べたように、通常DRAMに代表される半導体装置では、設計と製造上の理由から、半導体チップ4上にパッドを配置する際、例えば、入出力バッファ4a1に接続される信号パッド(データパッド)6a1と、入力専用バッファ4a2に接続される信号パッド(入力専用パッド)6a2を、ある程度領域を決めた上で配置する。特に、入力ピンが接続されるパッドにおいては、先に述べたように、入出力ピンが接続される入出力パッドに比べ、その傾向が顕著で、図8に示すように、入力パッドが配置されている領域の内側には電源パッドやグランドパッドが配置されていない場合もある。図8において、60aが電源パッドやグランドパッドの配置領域を、60bが入出力バッファの接続されるデータパッドの配置領域を示している。なお、図8中の小さな黒丸はパッドを省略していることを示す。また、データパッドの配置領域60bは、データピンが電気的に厳しい状況にあるので、データパッドだけを並べるのではなく、データパッドと電源パッド、グランドパッドを組み合わせて配置することが望ましい。

### [0062]

ここで問題になるのは、60cで示した入力パッドの配置領域である。チップサイズを低減するため、この領域には電源パッドやグランドパッドが置かれない。個々の入力ピンを見れば先に述べたように、ノイズは低いはずであるが、入力パッドの数が多いため、同時に動作する場合もあることを考慮すると、電気的には貧弱な電源グランド系であるといえる。

## [0063]

この第3実施例では、入力パッド領域60cの電源グランド系の弱点を補うために、図8に示すように、入力パッドの配置領域60cのパッド並びの概略中央に電源パッド61、グランドパッド62をペアで配置することにより、入力ピンの電気的特性を飛躍的に改善できる。なお、この際、配置する電源パッド61、グランドパッド62は、何れも、入力パッドに付随する保護ダイオードにつながるそれぞれ電源、グランドに接続されていることが最も良い結果を得られることは言うまでもない。

## [0064]

図8では、追加した電源パッドグランドパッドから、電源の半田ボール、グランドの半田ボールへの配線引出例を示した。このように、ペアとなる電源とグランドの配線は、中央のパッド配列を軸にして、別々の方向に引き出すことにより優れた効果が得られる。

#### [0065]

この第3実施例においては、入力パッドの配置領域の内側に少なくとも1個以上の電源電圧を供給する電極パッドと少なくとも1個以上の接地電圧を供給する電極パッドを設けたものである。

### [0066]

また、入力パッドの配置領域の外側にも、少なくとも1個以上の電源電圧を供給する電極パッドと少なくとも1個以上の接地電圧を供給する電極パッドを設けたものである。

### [0067]

また、入力パッドの配置領域の内側にある少なくとも1個以上の電源電圧を供給する電極パッドと、少なくとも1個以上の接地電圧を供給する電極パッドとを有し、入力パッドの配置領域の外側にある少なくとも1個以上の接地電圧を供給する電極パッドと、少なくとも1個以上の電源電圧を供給する電極パッドとを有し、半導体装置の外部接続端子の間には、接続手段である配線が形成されていて、入力パッドの配置領域の内側にある任意の接地電圧を供給する電極パッドと、入力パッドの配置領域の内側にある任意の接地電圧を供給する電極パッドとを、または、入力パッドの配置領域の内側にある任意の接地電圧を

供給する電極パッドと、入力パッドの配置領域の外側にある任意の電源電圧を供給する電極パッドとを選択し、選択した2個の電極パッドの中心を結ぶ直線によって、半導体装置を2分した時、外部接続端子と、外部接続端子と任意に選択した電極パッドを接続する接続手段がそれぞれ2分した半導体装置の領域のうち同一の領域内に存在するような電極パッドの選択が可能である構成としている。

### [0068]

また、電源電圧を供給する電極パッドと接地電圧を供給する電極パッドは、それぞれ、少なくとも1個以上の半導体チップ内のDRAM素子内にある入力バッファに接続される保護ダイオードの電源に接続されている電極パッドであり、また、少なくとも1個以上の半導体チップ内のDRAM素子内にある入力バッファに接続される保護ダイオードとは別の保護ダイオードのグランドに接続されている電極パッドである。

[0069]

本発明は、FBGAを用いるDRAMの一例では、ガラス含浸エポキシ樹脂によって形成されたコアを核とする配線基板を備え、半導体チップ4を配線基板の表面に搭載し、半導体チップの主面にあるパッドと配線基板上のパッドをワイヤで接続する形式の半導体装置に適用可能である。

【図面の簡単な説明】

[0070]

【図1】本発明の第1実施例の半導体装置の一部断面斜視図である。

【図2】第1実施例における半導体チップ内にある入出力バッファの回路図である。

【図3】第1実施例の半導体装置におけるパッドと半田ボールと配線との配置関係を説明 する模式図である。

【図4】第1実施例における半導体チップの最適なパッド数を説明するためのチップ平面図である。

【図 5 】本発明の第 2 実施例の半導体装置の半導体チップにおける入力バッファの回路図である。

【図 6 】第 2 実施例における半導体チップ 4 の最適なパッド数を説明するためのチップ平面図である。

【図7】第2実施例の半導体装置1をメモリモジュール基板に搭載した状態を示す図である。

【図8】本発明の第3実施例における半導体チップのパッドの配置を説明するためのチップ平面図である。

【符号の説明】

[0071]

1…半導体装置、2…コア、3…配線基板、4…半導体チップ、4a…バッファ、4a 1…入出力バッファ、4a2…入力バッファ、4b…保護ダイオード、6…パッド、6a …信号パッド、6a1…入出力パッド、6a2…入力パッド、6b…電極パッド、6bV …電源パッド、6bG…グランドパッド、6d…信号パッド、6A…パッド群、8…外部 接続端子(半田ボール)、9…配線、9a…接続部、10…接着層、11…テープ基板、 11a…テープ開口部、20…メモリモジュール基板、41…チップ主面、60a…電源 パッドやグランドパッドの配置領域、60b…入出力バッファの接続されるデータパッド の配置領域、60c…入力パッドの配置領域、61…電源パッド、62…グランドパッド 10

20

30

【図1】

【図2】

【図5】 図5

【図6】

図 6

【図7】

【図8】

図8

## フロントページの続き

(72)発明者 長内 文由紀

東京都中央区八重洲二丁目2番1号 エルピーダメモリ株式会社内

(72)発明者 高橋 康

東京都中央区八重洲二丁目2番1号 エルピーダメモリ株式会社内

(72)発明者 成井 誠司

東京都中央区八重洲二丁目2番1号 エルピーダメモリ株式会社内

## 審査官 坂本 薫昭

(56)参考文献 特開平6-350052(JP,A)

特開平7-38011(JP,A)

特開平10-284678(JP,A)

特開平11-204717(JP,A)

特開2002-9198(JP,A)

特開2002-217377(JP,A)

(58)調査した分野(Int.CI., DB名)

H01L 23/12