### (19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第4470182号 (P4470182)

(45) 発行日 平成22年6月2日(2010.6.2)

(24) 登録日 平成22年3月12日(2010.3.12)

| (51) Int.Cl.                           |                                | F I           |                     |                |                |        |

|----------------------------------------|--------------------------------|---------------|---------------------|----------------|----------------|--------|

| HO1L 29/78                             | (2006.01)                      | HO1L          | 29/78               | 301G           |                |        |

| HO1L 21/336                            | (2006.01)                      | HO1L          | 29/78               | 301Y           |                |        |

| HO1L 21/824                            | 2 (2006.01)                    | HO1L          | 27/10               | 621C           |                |        |

| HO1L 27/108                            | (2006.01)                      | HO1L          | 27/10               | 671Z           |                |        |

| HO1L 21/28                             | (2006.01)                      | HO1L          | 21/28               | 301R           |                |        |

|                                        |                                |               |                     | 請求項の数 5        | (全 12 頁)       | 最終頁に続く |

| (21) 出願番号 特願2006-228670 (P2006-228670) |                                |               | (73) 特許権者 500174247 |                |                |        |

| (22) 出願日                               | 平成18年8月25日 (2006.8.25)         |               |                     | エルピーダメニ        | モリ株式会社         |        |

| (65) 公開番号                              | ・号 特開2008-53491 (P2008-53491A) |               |                     | 東京都中央区月        | <b>【重洲2−2−</b> | 1      |

| (43) 公開日                               | 平成20年3月6日(2                    | 2008.3.6)     | (74) 代理人            | 100115738      |                |        |

| 審査請求日                                  | 平成19年9月13日 (                   | (2007. 9. 13) |                     | 弁理士 鷲頭         | 光宏             |        |

|                                        |                                |               | (74) 代理人            | 100121681      |                |        |

|                                        |                                |               |                     | 弁理士 緒方         | 和文             |        |

|                                        |                                |               | (74) 代理人            | 100130982      |                |        |

|                                        |                                |               |                     | 弁理士 黒瀬         | 泰之             |        |

|                                        |                                |               | (74) 代理人            | 100127199      |                |        |

|                                        |                                |               |                     | 弁理士 三谷         | 拓也             |        |

|                                        |                                |               | (72) 発明者            | 高石 芳宏          |                |        |

|                                        |                                |               |                     | <b>【重洲2-2-</b> | 1 エルピー         |        |

|                                        |                                |               | ダメモリ株式会社内           |                |                |        |

|                                        |                                |               |                     |                | • •            |        |

|                                        |                                |               |                     | 最              | 終頁に続く          |        |

## (54) 【発明の名称】半導体装置の製造方法

#### (57)【特許請求の範囲】

## 【請求項1】

半導体基板上に、ゲート絶縁膜を介してポリシリコンからなる下部電極膜及び犠牲膜を 順次に堆積する堆積工程と、

前記下部電極膜及び犠牲膜をパターニングし、ゲート下部電極及び犠牲膜パターンを形成するパターニング工程と、

前記パターニング工程の後に、前記ゲート下部電極の側壁をドライ酸化によって酸化する酸化工程と、

前記酸化工程の後に、前記ゲート下部電極及び犠牲膜パターンの側壁を覆う側壁酸化膜を形成する側壁形成工程と、

前記側壁形成工程の後に、<u>リンをドープしたポリシリコン膜を前記半導体基板上に堆積した後に、CMP法によって前記犠牲膜の表面が露出するまで平坦化することによって、</u>前記半導体基板に接続する導電材料を、隣接する前記ゲート下部電極及び犠牲膜パターンの間に前記側壁酸化膜と自己整合的に埋め込む導電材料埋め込み工程と、

前記導電材料埋め込み工程の後に、前記犠牲膜パターンをエッチング除去し、前記ゲート下部電極を露出する除去工程と、

前記除去工程の後に、前記側壁酸化膜の間に挟まれ前記ゲート下部電極の表面に接するゲート上部電極を、タングステン及びチタンの少なくとも一方を含む材料<u>を前記半導体基板上に堆積した後に、CMP法によって、前記犠牲膜パターンをエッチング除去して形成</u>された溝の部分のみに残存させて形成する上部電極形成工程と、

前記上部電極形成工程の後に、所定のマスクパターンを用い、前記導電材料埋め込み工程で埋め込んだ導電材料の一部を除去して前記半導体基板に接続するコンタクトプラグを 形成するプラグ形成工程と、

前記プラグ形成工程の後に、前記上部電極および前記コンタクトプラグを覆う層間絶縁膜を形成する工程と、

を有することを特徴とする半導体装置の製造方法。

#### 【請求頃2】

前記除去工程と前記上部電極形成工程との間に、前記下部電極の表面にコバルトシリサイド層を形成する工程を更に有する、請求項1に記載の半導体装置の製造方法。

#### 【請求項3】

前記導電材料埋め込み工程と前記除去工程との間に、前記コンタクトプラグと前記半導体基板とのコンタクト抵抗を低減するための熱処理工程とを更に有する、請求項1<u>又は2</u>に記載の半導体装置の製造方法。

## 【請求項4】

前記堆積工程に先立って、前記半導体基板上に溝を形成する溝形成工程と、前記溝内に 絶縁膜を埋め込む分離領域形成工程と、前記溝内の絶縁膜の上部分を除去する絶縁膜除去 工程とを更に有する、請求項1~3の何れか一項に記載の半導体装置の製造方法。

## 【請求項5】

前記堆積工程は、堆積した下部電極膜を平坦化する平坦化工程を含む、請求項<u>4</u>に記載の半導体装置の製造方法。

【発明の詳細な説明】

### 【技術分野】

## [0001]

本発明は、半導体装置の製造方法に関し、更に詳しくは、ポリメタルゲート電極構造を有するトランジスタを備える半導体装置の製造方法に関する。

## 【背景技術】

# [0002]

半導体装置の微細化・高集積化・高性能化に伴い、DRAM装置のワード線抵抗の低減が重要な課題の一つである。ワード線の材料として、従来は、タングステン・シリサイド(WSi₂)とポリシリコンの積層構造であるタングステン・ポリサイド電極が一般的であった。しかし、最近になって、ワード線の抵抗値のより低減化をはかるため、WSi₂とポリシリコンの積層構造に代えて、タングステン(W)などの金属膜とポリシリコン膜の積層構造を使用するポリメタル電極が一般的になってきている。タングステン膜をするポリメタル電極をDRAM装置に採用することにより、ワード線の抵抗値が従来比1/3以下に低減できる。なお、このタングステン・ポリメタル電極では、Wとポリシリコンの界面における反応を抑え、また、その界面の接触抵抗を低減するために、ポリシリコンカ上に薄いWSi₂とWN(窒化タングステン)を堆積し、その上にWを形成する積層構造が一般的に採用される。DRAM装置の一般的な構造は、例えば特許文献1に記載がある。また、ポリメタル電極については、例えば特許文献2に記載がある。

## [0003]

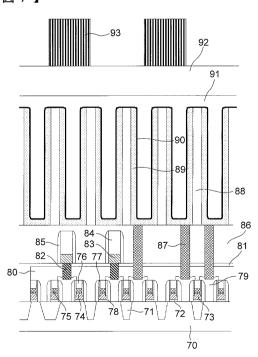

図7は、一般的なDRAM装置におけるゲート電極として、ポリメタル電極構造を採用した例を断面図で示すものである。半導体基板(シリコン基板)70の主面には、素子分離領域71が形成され、素子分離領域71は、素子形成領域(アクティブ領域)を区画している。素子形成領域には、図示しない拡散層を含む活性層が形成され、活性層の上には、ゲート絶縁膜72を介してポリシリコンで形成されたゲート下部電極73が形成されている。ゲート下部電極73上には、W/WNで構成されるゲート上部電極75が設けられる。ゲート下部電極73とゲート上部電極75との界面には、接触抵抗低減のためにWSi2層74が形成される。ゲート上部電極75上には、ゲート電極加工時のマスクとなり、また、セルコンタクト79を構成するポリシリコンパッドと、ゲート上部電極75との間の電気的な絶縁を取るために必要なマスク酸化膜76が形成されている。また、ゲート

10

20

30

40

電極構造全体の側壁には、第1の側壁(サイドウオール)酸化膜78が形成され、第1の側壁酸化膜78は、セルコンタクト79を自己整合的に形成する際に使用され、セルコンタクト79とゲート電極構造とを絶縁している。ゲート電極構造より上部の構造は、ビット線、容量素子、アルミ配線などを含むDRAMの一般的な構造である。

[0004]

DRAM装置のゲート電極の形成に際しては、ゲート電極パターンを形成するエッチングの後に、ゲート電極の側面及び拡散層を酸化する酸化工程が採用される。これは、主にDRAM装置のリフレッシュ特性の向上と、DRAMセルのトランジスタ(Tr)特性の信頼性向上のためである。一般に、タングステンは酸化されやすいため、ポリメタルゲート電極の側面酸化時には、水素雰囲気下で酸化(WH酸化)を行う。しかしながら、このWH酸化時には問題が発生する。まず、WH酸化時にWが飛散して、シリコン基板に吸着しリフレッシュ特性を悪化させる問題である。また、WH酸化時にゲートポリシリコンを多ングステンの界面に存在するWSi₂層が酸化され、ゲート電極内で界面抵抗が増加する問題もある。これら問題を解決するために、タングステンを用いたポリメタル電極の形成に際して、ゲートポリシリコンの側壁の一部を含みWの側壁に保護窒化膜77を形成し、Wの飛散と界面抵抗の増加とを防止する窒化膜保護プロセスが用いられている。

【特許文献1】特開平11-340436号公報

【特許文献 2 】特開 2 0 0 1 - 3 2 6 3 5 0 号公報

【発明の開示】

【発明が解決しようとする課題】

[0005]

DRAM装置の微細化に伴い、ワード線の線幅が小さくなると、保護室化膜の膜厚分の影響が大きくなってくる。これは、ワード線の線幅から保護室化膜厚の2倍に相当する幅だけWの幅を細くしなければならないからである。また、配線抵抗低減のためにWの膜厚を厚くすると、ワード線のパターン加工が困難になるためその膜厚を厚くできず、ポリメタルゲート電極を用いても、ワード線の配線抵抗の増加が問題となってくる。

[0006]

更に、側面酸化を水素雰囲気中で行い、ウェット雰囲気下での酸化になるため、ワード線のポリシリコン膜とゲート絶縁膜の界面に酸化が侵攻してバーズビークが形成される。ワード線幅が小さくなると、ワード線両側から酸化が侵攻して、バーズビークがつながってしまい、見かけ上ゲート絶縁膜が厚くなり、セルTrの特性を悪化させるおそれがある。そのために、側面酸化量は大きくとれず、リフレッシュ特性にも影響が発生する。

[0007]

本発明は、上記従来技術の問題に鑑み、ゲート電極にポリメタル電極を用いる半導体装置の製造プロセスにおいて、ゲート側面酸化時に発生するバーズビークを低減でき、また上部メタル電極の幅を充分に大きくでき、上部メタル電極の膜厚も厚く形成できるため、DRAM装置が微細化してもリフレッシュ特性を悪化することなく、またゲート電極の配線抵抗が低減できる半導体装置の製造方法、及び、そのような製造方法によって得られる半導体装置の構造を提供することを目的とする。

【課題を解決するための手段】

[ 0 0 0 8 ]

上記目的を達成するために、本発明の半導体装置の製造方法は、半導体基板上に、ゲート絶縁膜を介して下部電極膜及び犠牲膜を順次に堆積する堆積工程と、

前記下部電極膜及び犠牲膜をパターニングし、ゲート下部電極及び犠牲膜パターンを形成するパターニング工程と、

前記ゲート下部電極及び犠牲膜パターンの側壁を覆う側壁酸化膜を形成する側壁形成工程と、

前記犠牲膜パターンをエッチング除去し、前記ゲート下部電極を露出する除去工程と、 前記側壁酸化膜の間に挟まれ前記ゲート下部電極の表面に接するゲート上部電極を形成 する上部電極形成工程と、 10

20

30

40

を有することを特徴とする。

## 【発明の効果】

#### [0009]

本発明の半導体装置の製造方法によると、ポリメタル構造のゲート電極を用いた半導体装置の製造に際して、犠牲膜を除去した部分にゲート上部電極を形成できるので、ゲート下部電極の形成工程とゲート上部電極の形成工程との間に、DRAM装置のリフレッシュ特性やセルTrの信頼性向上のためなどの酸化工程を、ゲート上部電極に熱的影響を与えることなく、またゲート上部電極とゲート下部電極の界面の抵抗値を増加させないで行うことができ、高性能なDRAM装置の実現が可能である。また、犠牲膜を除去した後にゲート上部電極を形成することで、ゲート上部電極のより厚膜化が可能となる。

[0010]

本発明の好ましい半導体装置の製造方法では、前記パターニング工程と前記側壁形成工程との間に、前記ゲート下部電極の側壁を酸化する酸化工程を更に有する。この酸化工程により、DRAM装置のリフレッシュ特性が改善可能であり、また、Trの信頼性が向上する。

#### [0011]

また、前記側壁形成工程と前記除去工程との間に、前記半導体基板に接続する導電プラグを前記側壁酸化膜と自己整合的に形成する工程と、前記導電プラグと前記半導体基板とのコンタクト抵抗を低減するための熱処理工程とを更に有することも好ましい。この場合、上部電極を低抵抗の金属膜で形成しても、その熱処理の影響を受けないで良好な上部電極の形成が可能である。

[0012]

前記上部電極形成工程の後に、所定のマスクパターンを用い、前記導電プラグの一部を選択的に除去するプラグ除去工程を更に有することも本発明の好適な態様である。

#### [0013]

前記下部電極膜をポリシリコンで構成し、前記ゲート上部電極を、タングステン及びチタンの少なくとも一方を含む金属膜で構成することが好ましい。なお、ゲート上部電極に使用する金属は、これらの金属に限らない。

[0014]

前記堆積工程に先立って、前記半導体基板上に溝を形成する溝形成工程と、前記溝内に 絶縁膜を埋め込む分離領域形成工程と、前記溝内の絶縁膜の上部分を除去する絶縁膜除去 工程とを更に有することも好ましい。この場合、三次元構造の拡散層が得られる。

[0015]

前記堆積工程は、堆積したゲート下部電極膜を平坦化する平坦化工程を含むことが好ましい。この場合、上部電極の形成が容易である。

【発明を実施するための最良の形態】

[0016]

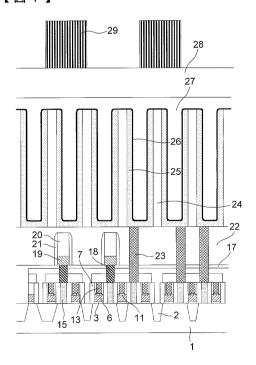

次に、本発明の実施形態について図面を参照して説明する。図1に本発明の第1の実施形態に係る製造方法で製造される半導体装置の断面図を示す。この半導体装置は、DRAM装置として構成される。図1において、半導体基板1の主面には、素子分離領域2が形成され、素子分離領域2は、素子形成領域を区画している。素子形成領域には、図示しない拡散層を含む活性層が形成され、活性層の上には、ゲート絶縁膜(例えば、酸化膜)3を介してポリシリコンで形成されたゲート下部電極6が形成されている。ゲート下部電極6上には、W/TiN/Tiの積層膜などの金属材料で構成されたゲート上部電極13が形成される。本実施形態では、ゲート下部電極6とゲート上部電極13とを別々に形成している。このゲート電極構造の形成は、例えば以下のように行われる。

[0017]

先ず始めに、ゲート下部電極6と、犠牲膜としても使用するマスク窒化膜とを形成する。この後に、リフレッシュ向上及びセルTrの信頼性向上のために、ゲートの側壁を酸化する。このとき、ゲート上部電極のメタル層はまだ形成されていないため、メタル層の異

10

20

30

40

20

30

40

50

常酸化、飛散、メタルとゲート下部電極のポリシリコンとの界面の酸化に伴う界面抵抗の増加などの問題は発生しない。次に、ゲート及びマスク窒化膜の側壁に第1の側壁酸化膜7を形成する。更に、ビットコンタクト18及び容量コンタクト用のポリシリコンプラグ23と、セルの拡散層とを接続するために、セルコンタクト15用のポリシリコン・パッドを形成する。その後に接触抵抗低減のため、高温の熱処理を行う。ここでは、ゲート上部電極13のメタル層がまだ形成されていないため、メタル層に熱的影響を与えることなく熱処理を任意に追加できる。

## [0018]

次に、ゲート下部電極6上のマスク窒化膜を除去した後に、その除去した部分にメタルで形成されたゲート上部電極13を形成する。この後は、ゲート上部電極13のメタル層に影響のない程度の低温の熱処理でDRAM装置が形成できる。このため、ゲート上部電極13の形成前に、リフレッシュ特性向上に必要な十分な熱処理を追加できるため、DRAM装置のリフレッシュ特性の劣化が抑制できる。上記構造を用いることにより、DRAM装置のワード線抵抗値の増加が防止でき、かつリフレッシュ特性、セルのTrの信頼性などを悪化することなく、ポリメタル構造が可能になるため、高性能なDRAM装置が実現できる。

#### [0019]

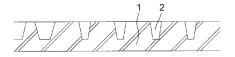

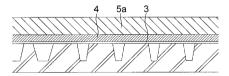

以下、図1の半導体装置を製造するプロセスについて詳細に説明する。図2A~図2Qは、図1の半導体装置を製造する工程を順次に示す断面図である。まず、図2Aに示すように、シリコン基板1上に素子分離領域(STI)2を形成し、素子形成領域を区画する。次に、素子形成領域内で、ウェル形成及びトランジスタの閾値調整用等のイオン注入を行った後に、図2Bに示すように、酸化膜又は酸窒化膜などのゲート絶縁膜3を形成し、ゲート電極の下部電極膜となるポリシリコン膜4を70nm厚みに成膜する。次に、このポリシリコン膜4上に、ゲート電極加工に必要なマスク窒化膜(犠牲酸化膜)5aを140nm程度の厚みに堆積する。

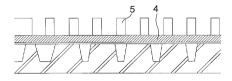

#### [0020]

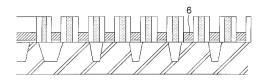

次に、図2Cに示すように、公知のフォトリソグラフィエ程を用い、セルアレイ部のワード線となる部分に窒化膜を残して、マスク窒化膜(犠牲膜パターン)5を形成する。次に、図2Dに示すように、マスク窒化膜5をマスクにして、ポリシリコン膜4をエッチングし、ポリシリコンのゲート下部電極6を形成する。なお、この工程では、ゲートパターンを有するレジストマスクを用いて、窒化膜5a及びポリシリコン膜4をパターニングしてもよい。ゲート下部電極6の形成後に、リフレッシュ対策の側面酸化を行う。このとき、ゲート上部電極が形成されていないため、Wの酸化及び飛散を気にすることなく、酸化条件が設定できる。具体的には、高温のドライ酸化を用いることで、ゲート電極へのバーズビーク侵攻を抑制しつつ、側面酸化膜の膜厚を厚くすることが出来る。この側面酸化は、セルのリフレッシュ特性の向上、及び、セルTrの信頼性向上に、特に有効である。

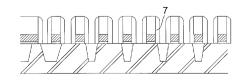

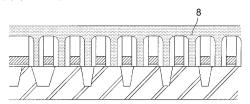

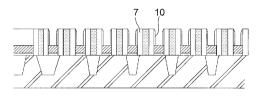

## [0021]

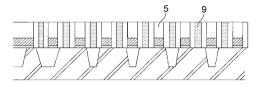

次に、CVD及びエッチングにより、図2Eに示すように、ゲート下部電極6及びマスク窒化膜5の側壁に、第1の側壁酸化膜7を形成する。次に、図2Fに示すように、セルコンタクトプラグを形成するためのPドープポリシリコン膜8を、200nm程度の厚みとなるように全面に堆積する。次に、図2Gに示すように、堆積したPドープポリシリコン膜8を公知のCMP技術にて平坦化し、マスク窒化膜5上のポリシリコン膜8を除去し、ゲート電極の間のみにセルコンタクト9用のポリシリコンプラグを残す。この時点でゲート電極のメタル部であるゲート上部電極を形成していないので、ゲート上部電極のメタルの反応を気にする必要はなく、拡散層とセルコンタクト9の界面の接触抵抗を下げるために、高温の熱処理を追加する。

# [0022]

次に、図2Hに示すように、マスク窒化膜5を除去して、ゲート下部電極のポリシリコン膜6の表面を露出する。次に、図2Iに示すように、後に形成するビットコンタクト1

20

30

40

50

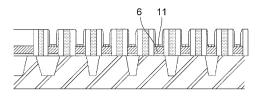

8 とゲート上部電極 1 3 との間の目ずれマージンを拡大するために、第 2 の側壁酸化膜 1 0 を第 1 の側壁酸化膜 7 の側壁表面に形成する。次に、図 2 」に示すように、露出したゲート下部電極 6 のポリシリコン膜上に、コバルトシリサイド層 1 1 を公知のサリサイド技術を用いて形成する。

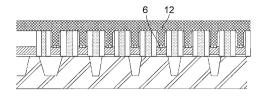

#### [0023]

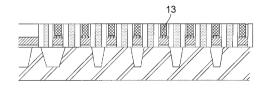

次に、図2Kに示すように、ゲート上部電極13となる、W/TiN/Tiの積層膜12を全面に堆積する。次に、図2Lに示すように、公知のCMP技術を用いて、マスク窒化膜を除去してできた溝の部分のみにW/TiN/Tiの積層膜を残し、ゲート上部電極13を形成する。これにより、ゲートポリメタル電極が形成できる。ゲート上部電極13の厚さは、除去したマスク窒化膜5の厚みで決定する。ゲート上部電極13であるメタルを直接にエッチングするのではなく、マスク窒化膜5をエッチング加工することから、ゲート上部電極13の厚膜化が可能になる。また、このメタル電極の形成前に、ゲート側壁酸化を行い、且つ、セルコンタクト・ポリシリコン形成後の高温熱処理を行うため、メタル電極に影響を与えることなく、側壁酸化や高熱処理が可能である。メタル電極形成後には、低温の熱処理のみで足りるので、ゲートポリメタル電極の低抵抗化及び界面抵抗の低抵抗化が実現できる。

#### [0024]

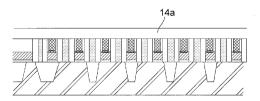

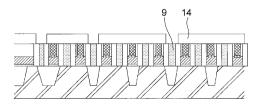

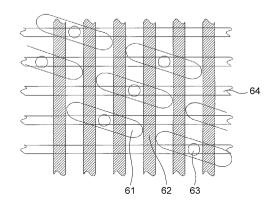

次に、図2Mに示すように、セルコンタクトを構成するポリシリコン・パッドを形成する際に利用する酸化マスクを形成するための酸化膜14aを堆積する。次に、図2Nに示すように、公知のフォトリソグラフィ工程を用いて、レジストパターンを形成し、このレジストパターンをマスクにして酸化膜14aをエッチングし、マスク酸化膜14とする。このときの平面レイアウトを図3に示す。図3に示すように、拡散層パターン61の上部にゲート電極62が相互に平行に延びている。拡散層パターン61の中央にはビットコンタクト63を配置する。このビットコンタクト63に接続するように、ゲート電極62と直交方向に延びるビット線64を配置する。

#### [0025]

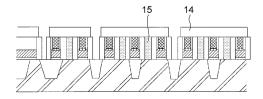

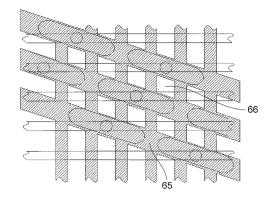

図4は、図3の構造を得るために形成した酸化膜マスク65のパターンを示している。 隣接するゲート電極62間のみにセルコンタクト用のポリシリコンを形成するため、図4 に示すような酸化膜マスク65のパターンで、ポリシリコン・プラグ9を加工する。これ により、素子分離領域66上のポリシリコンを除去し、拡散層パターン61の上部に隣接 して延びるゲート電極パターン62間にのみ、セルコンタクト用のポリシリコン・プラグ (パッド)が形成できる。

#### [0026]

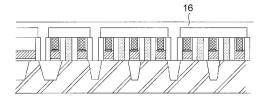

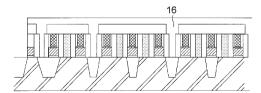

次に、図20に示すように、マスク酸化膜14をマスクにし、素子分離領域2上のポリシリコン・プラグ9を選択的にエッチング除去して、セルコンタクト用のポリシリコン・パッド15とする。次に、図2Pに示すように、第1の層間絶縁膜16を堆積して、セル上を平坦化する。次に、図2Qに示すように第1の層間絶縁膜16を周辺回路部分でエッチングするなど、周辺回路部分にゲート電極を含むTr構造を形成する。

## [0027]

次に、図1に示すように、周辺回路部及びメモリセル部に第2の層間絶縁膜17を形成し、更に、通常のDRAMプロセスにおける後工程で、ビットコンタクト18と、ビット線19、マスク窒化膜20及び側壁窒化膜21を含む配線構造と、第3の層間絶縁膜22と、容量コンタクト23と、容量素子形成のためのシリンダコア酸化膜24と、容量下部電極25、容量絶縁膜26及び容量上部電極27を含む容量素子と、その上を覆う第4の層間絶縁膜28と、第1アルミ配線29とを形成する。これにより、図1に示すDRAM装置が完成する。

#### [0028]

本発明の第1の実施形態に係る製造方法で作成した半導体記憶装置は、ゲート下部電極6とゲート上部電極13とを別々に形成することから、ゲートポリシリコンで形成されたゲート下部電極の形成後に、DRAM装置のリフレッシュ特性及びセルTrの信頼性に必

要なゲート側面酸化を行い、更には、より微細化したセル部の接触抵抗値低減のために高温の熱処理などを追加しても、ゲートポリメタル電極には影響がなく、高性能なDRAM 装置を実現できる。

### [0029]

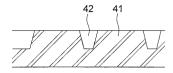

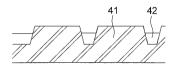

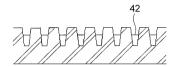

次に本発明の第2の実施形態に係る半導体装置の製造方法について、更に図面を参照して説明する。 図5A~5Eは本発明の第2の実施形態に係る半導体装置の製造プロセスを順次に示すもので、半導体装置をワード線(ゲート電極)と垂直な方向に沿う断面で示している。また、図6A~6Eは、同じ製造プロセスをワード線と平行な方向に沿う断面で示している。本実施形態に係る方法で製造される半導体装置は、フィン型の拡散層で形成されたセルTrを有する。図5A及び図6Aに示すように、シリコン基板41上に、素子分離領域(STI)42を形成する。次に、図5B及び図6Bに示すように、セルTrの拡散層を3次元的構造とするために、STI42の上部分をエッチングする。つまり、STI42の上部側壁部分で拡散層を露出させる。

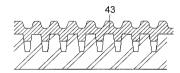

#### [0030]

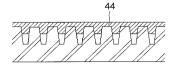

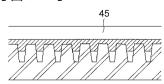

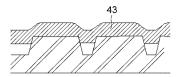

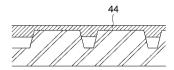

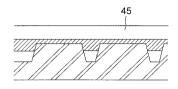

次に、図5C及び図6Cに示すように、3次元的構造になった拡散層に対して、チャネル注入を行い、トランジスタのチャネルになる部分に不純物をドーピングする。次いで、ゲート酸化を行い、基板の露出した表面上に図示しないゲート絶縁膜を形成する。そのゲート絶縁膜上に、ゲート下部電極となるポリシリコン膜43を堆積する。このとき、下地拡散層の表面形状を反映して、ポリシリコン膜43の表面が凸凹形状を有する。次に図5D及び図6Dに示すように、公知のCMP技術を用いてゲート下部電極となるポリシリコン膜を平坦化して、ゲート下部電極44を形成する。次に、ゲート下部電極44上にゲートマスク窒化膜45を堆積する。図5E及び図6Eに示す構造は、第1の実施形態における図2Bの工程で示す構造とほぼ同じであり、これ以降は、第1の実施形態における図2C以降の工程と同様な工程を経てDRAM装置が完成する。

#### [0031]

第2の実施形態に係る製造方法で作成した半導体装置は、フィン型などの三次元的拡散層構造に対して、カバレッジの良いポリシリコン電極でゲート下部電極を形成した後に平坦化する。この平坦化により、ゲート上部電極となるメタル電極に対しては、ゲート下部電極の表面が平坦面となるので、上部メタル電極の形成が容易になり、高性能なDRAM装置を実現できる。三次元構造の拡散層を有するTrでは、同一電圧及び同一しきい値で比較した際に、得られるオン電流が大きくなる。また、ゲート電極から基板に向かう電界が三方向になるので、基板バイアスへの依存度が小さくなり、S値が改善する結果としてトランジスタの能力が向上する利点がある。

## [0032]

以上、本発明をその好適な実施形態例に基づいて説明したが、本発明の半導体装置の製造方法は、上記実施形態例の構成にのみ限定されるものではなく、上記実施形態例の構成から種々の修正及び変更を施したものも、本発明の範囲に含まれる。例えば、上記実施形態では、ゲート上部電極にタングステンを使用したが、これに限らず、チタンやその他の低抵抗金属の使用が可能である。また、本発明の製造方法をDRAM装置の製造に適用した例を示したが、ポリメタル構造を有するゲート電極を備えるMOSFETであれば、他の半導体装置にも適用可能である。

#### 【図面の簡単な説明】

#### [0033]

【図1】本発明の第1の実施形態に係る製造方法で製造される半導体装置の構造を示す断面図である。

【図2A】本発明の第1の実施形態の製造方法における一工程段階を示す断面図である。

【図2B】本発明の第1の実施形態の製造方法における一工程段階を示す断面図である。

【図2C】本発明の第1の実施形態の製造方法における一工程段階を示す断面図である。

【図2D】本発明の第1の実施形態の製造方法における一工程段階を示す断面図である。

【図2E】本発明の第1の実施形態の製造方法における一工程段階を示す断面図である。

10

20

30

40

- 【図2F】本発明の第1の実施形態の製造方法における一工程段階を示す断面図である。

- 【図2G】本発明の第1の実施形態の製造方法における一工程段階を示す断面図である。

- 【図2H】本発明の第1の実施形態の製造方法における一工程段階を示す断面図である。

- 【図2Ⅰ】本発明の第1の実施形態の製造方法における一工程段階を示す断面図である。

- 【図2J】本発明の第1の実施形態の製造方法における一工程段階を示す断面図である。

- 【図2K】本発明の第1の実施形態の製造方法における一工程段階を示す断面図である。

- 【図2L】本発明の第1の実施形態の製造方法における一工程段階を示す断面図である。

- 【図2M】本発明の第1の実施形態の製造方法における一工程段階を示す断面図である。

- 【図2N】本発明の第1の実施形態の製造方法における一工程段階を示す断面図である。

- 【図20】本発明の第1の実施形態の製造方法における一工程段階を示す断面図である。

- 【図2P】本発明の第1の実施形態の製造方法における一工程段階を示す断面図である。

- 【図20】本発明の第1の実施形態の製造方法における一工程段階を示す断面図である。

- 【図3】本発明の第1の実施形態の製造方法における一工程段階を示す平面図である。

- 【図4】図3の工程段階で使用されるマスクの平面図である。

- 【図 5 A 】本発明の第 2 の実施形態の製造方法における一工程段階を示す、ゲート電極と 直交する方向に沿う断面図である。

- 【図5B】本発明の第2の実施形態の製造方法における一工程段階を示す、ゲート電極と 直交する方向に沿う断面図である。

- 【図5C】本発明の第2の実施形態の製造方法における一工程段階を示す、ゲート電極と 直交する方向に沿う断面図である。

- 【図5D】本発明の第2の実施形態の製造方法における一工程段階を示す、ゲート電極と 直交する方向に沿う断面図である。

- 【図5E】本発明の第2の実施形態の製造方法における一工程段階を示す、ゲート電極と 直交する方向に沿う断面図である。

- 【図 6 A 】本発明の第 2 の実施形態の製造方法における一工程段階を示す、ゲート電極と 平行な方向に沿う断面図である。

- 【図 6 B】本発明の第 2 の実施形態の製造方法における一工程段階を示す、ゲート電極と 平行な方向に沿う断面図である。

- 【図6C】本発明の第2の実施形態の製造方法における一工程段階を示す、ゲート電極と 平行な方向に沿う断面図である。

- 【図6D】本発明の第2の実施形態の製造方法における一工程段階を示す、ゲート電極と 平行な方向に沿う断面図である。

- 【図 6 E 】本発明の第 2 の実施形態の製造方法における一工程段階を示す、ゲート電極と 平行な方向に沿う断面図である。

- 【図7】従来例のDRAM装置の構造を示す断面図である。

- 【符号の説明】

- [0034]

- 1,41,70 シリコン基板(拡散層)

- 2,42,71 素子分離領域(STI)

- 3 , 7 2 ゲート絶縁膜

- 4,43 ポリシリコン膜

- 5 , 4 5 マスク窒化膜

- 76 マスク酸化膜

- 6 , 7 3 ゲート下部電極

- 7,78 第1の側壁酸化膜

- 8 ポリシリコン膜

- 9,79 セルコンタクト

- 10 第2の側壁酸化膜

- 11,74 シリサイド(Wsi<sub>2</sub>)層

- 12 メタル電極

10

30

30

40

20

- 13,75 ゲート上部電極(メタル)

- 1 4 マスク酸化膜

- 15 セルコンタクト

- 16,80 第1の層間絶縁膜

- 17,81 第2の層間絶縁膜

- 18,82 ビットコンタクト

- 19,83 ビット線

- 20,84 ビット線上マスク窒化膜

- 21,85 ビット線サイドウォール窒化膜

- 22,86 第3の層間絶縁膜

- 23,87 容量コンタクト用ポリシリコンプラグ

- 24,88 シリンダコア酸化膜

- 2 5 , 8 9 容量下部電極

- 2 6 , 9 0 容量絶縁膜

- 27,91 容量上部電極

- 28,92 第4の層間絶縁膜

- 29,93 第1アルミ配線

- 44 平坦化したゲートポリシリコン

- 6 1 拡散層パターン

- 62 ゲートパターン

- 63 ビットコンパターン

- 6.4 ビット線パターン

- 65 セルコンパッドパターン

- 77 保護窒化膜

# 【図1】

## 【図2A】

# 【図2B】

# 【図2C】

## 【図2D】

# 【図2E】

# 【図2F】

# 【図2G】

【図2H】

【図2I】

【図2M】

【図2N】

【図20】

【図2J】

【図2K】

【図2L】

【図2P】

【図2Q】

【図3】

【図4】

【図5A】

【図5B】

【図 6 B】

【図6C】

【図6D】

【図 6 E】

【図5C】

【図5D】

【図5E】

【図6A】

【図7】

## フロントページの続き

(51) Int.CI. F I

**H 0 1 L 29/423 (2006.01)** H 0 1 L 29/58 G

H 0 1 L 29/49 (2006.01)

審査官 松嶋 秀忠

(56)参考文献 特開平11-026757(JP,A)

特開2001-127288(JP,A)

特開2000-183347(JP,A)

特開平11-354641(JP,A)

特開2004-040118(JP,A)

1962 2 2 2 1 2 1 2 1 1 2 ( 5 1 , 7 )

特開2005-259939(JP,A) 特開2005-136376(JP,A)

特開平09-153610(JP,A)

特開2004-186703(JP,A)

(58)調査した分野(Int.CI., DB名)

H01L 29/78

H01L 21/28

H01L 21/336

H01L 21/8242

H01L 27/108

H01L 29/423

H01L 29/49