(19) **日本国特許庁(JP)**

## (12) 特 許 公 報(B2)

(11)特許番号

特許第3971500号 (P3971500)

(45) 発行日 平成19年9月5日(2007.9.5)

(24) 登録日 平成19年6月15日 (2007.6.15)

(51) Int.C1.

FI

HO1L 21/60 HO1L 23/50 HO1L 21/60 311W HO1L 23/50 A

請求項の数 2 (全 13 頁)

(21) 出願番号 特願平10-38316

(22) 出願日 平成10年2月20日 (1998. 2. 20)

(2006, 01)

(2006.01)

(65) 公開番号 特開平11-238763

(43) 公開日 平成11年8月31日 (1999. 8. 31) 審査請求日 平成17年1月19日 (2005. 1. 19) |(73)特許権者 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

||(74)代理人 100114627

弁理士 有吉 修一朗

(73)特許権者 598023090

株式会社ノース

東京都豊島区南大塚三丁目32番1号

|(74)代理人 100114627

弁理士 有吉 修一朗

(72)発明者 大沢 健治

東京都品川区北品川6丁目7番35号 ソ

二一株式会社内

最終頁に続く

(54) 【発明の名称】半導体素子実装用配線基板の製造方法

## (57)【特許請求の範囲】

#### 【請求項1】

金属ベースの表面にエッチングストップ膜を形成する工程と、

<u>該エッチングストップ膜上に</u>形成すべき配線膜に対してネガのパターンを有する第1の レジスト膜を形成する工程と、

上記第1のレジスト膜が形成された上記金属ベースの表面上に上記第1のレジスト膜上を含め、上記配線膜の所定部分上に形成すべきバンプ乃至パッドに対してネガのパターンを有する第2のレジスト膜を形成する工程と、

上記第2のレジスト膜をマスクとしてバンプ乃至パッド材料である金またはパラジウムを上記金属ベース表面に電解メッキすることによりバンプ乃至パッドを形成する工程と、第2のレジスト膜を除去でき第1のレジスト膜を除去できない除去手段により第2のレジスト膜のみ除去する工程と、

上記第1のレジスト膜をマスクとして上記金属ベース表面に配線膜材料<u>となる銅</u>を上記金属ベース表面に電解メッキすることにより配線膜を形成する工程と、

を有することを特徴とする半導体素子実装用配線基板の製造方法。

#### 【請求項2】

<u>上記第2のレジスト膜は上記配線膜先端にのみ金またはパラジウムをメッキするパターンである</u>

ことを特徴とする請求項1に記載の半導体素子実装用配線基板の製造方法。

#### 【発明の詳細な説明】

#### [0001]

### 【発明の属する技術分野】

本発明は、半導体素子実装用配線基板の製造方法に関する。

#### [0002]

#### 【従来の技術】

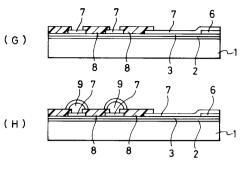

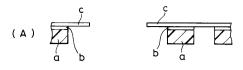

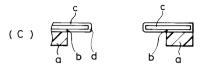

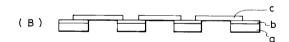

半導体素子を実装する技術の一つとしてTAB(Tape Automated Bonding)技術があり、図10(A)乃至(D)はその一つの従来例である配線基板の形成方法の概略を工程順に示すものである。例えば所定のパターンにパターニングされたポリイミド樹脂層(厚さ例えば75μm)aに接着剤bを介して銅層(厚さ例えば数~数十μm)cを接着することにより積層し、該銅層cをパターニングすることにより配線膜を形成したフィルム回路を用意する。図10(A)はそのフィルム回路を示す。

#### [0003]

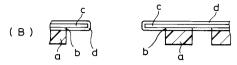

次に、図10(B)に示すように、電解メッキにより先ずニッケル膜(厚さ例えば2μm)を形成し、その後、電解メッキにより金メッキ膜(厚さ例えば1μm)を形成し、しかる後、図10(C)に示すように外形カット処理をして個々の半導体装置分毎に分離独立させる。 d はメッキ膜である。

#### [0004]

上記外形カット処理後、図10(D)に示すように、各配線膜cの内端を半導体素子eの各電極にボンディングする。このボンディングはAu/Alボンディングとなる。

#### [0005]

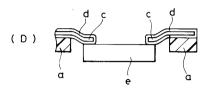

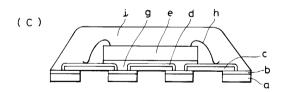

図11(A)乃至(C)は別の従来例である配線基板の形成方法の概略を工程順に示すものである。本従来例は、ワイヤボンドタイプのBGA/CSP用配線基板を対象とし、無電解メッキによりバンプの形成を行う。先ず、図11(A)に示すように、パターニングされた接着剤b付きポリイミド樹脂層(厚さ例えば50μm)aを銅層(厚さ例えば18μm)cに接着することにより積層し、その後、図11(B)に示すように該銅層cを選択的にエッチングし、その後、図11(C)に示すように、全面的にニッケル膜(膜厚2μm)を無電解メッキし、更に金膜(0.5μm)を無電解メッキにより形成し、その後、半導体素子をダイボンディングし、更にワイヤボンディングし、しかる後、樹脂封止する。図11(C)はその樹脂封止後の状態を示す。dはニッケル/金メッキ膜、eは半導体素子、gは接着剤、hはワイヤ、iは封止樹脂である。

#### [0006]

## 【発明が解決しようとする課題】

ところで、図10に示した従来方法には、電解メッキにより各配線毎に金膜を形成するので、先ず第1に電解メッキ用の引き回し配線を必要とし、設計が面倒であるという問題がある。第2に、引き回し配線領域が必要であるので、小型化が難しいという問題がある。第3に、電解メッキは部分的メッキが困難であるが故に配線の露出している面全面に金が付いてしまい、金の使用量が多くなりがちなので、その傾向を抑制するためには金膜を余り厚くすることができないという問題がある。これはボンディング性の向上を制約する要因になる。第4に、配線膜を成す銅膜の表面に直接金膜を形成することによりバンプを構成した場合、ボンディングをするとき印加される超音波が拡散しないようにするために金バンプの下地として例えばニッケル膜を超音波振動拡散防止用として必要であるが、これは半導体素子側にダメージを生じ易いという問題がある。

#### [0007]

また、図11に示した従来方法には、無電界メッキ法により金膜を形成するので、第1にメッキ速度が遅く、メッキに要する時間が非常に長くなり、また、TAB用の基板を形成する場合には、テープ状のメッキ設備が必要となり、設備費が高くなると言う問題がある。第2に、無電解メッキ法によれば、小径の開口部に対する金メッキが難しく、接着剤にじみ、メッキ気泡の発生が生じ易いという問題がある。第3に、無電解メッキ法には、メッキの安定性が悪く、膜質が不安定で、金膜に異状が生じ易いという問題がある。第4に、無電解メッキ法によれば、メッキ液の交換頻度が高く、3~4日で1回という頻度の交

10

20

30

換が必要であるという問題がある。

#### [0008]

本発明はこのような問題点を解決すべく為されたものであり、半導体素子実装用配線基板の製造方法において、バンプ乃至ボンディングパッドの形成に電界メッキ法を採用することにより上記無電解メッキ法の持つ欠点を回避しつつ各配線毎に引き回し配線を形成する必要性を無くすことにより従来の電界メッキ法の持っていた欠点を回避することを目的とする。

## [0009]

#### 【課題を解決するための手段】

請求項1の半導体素子実装用配線基板の製造方法は、金属ベースの表面に、配線膜形成用のネガパターンのレジスト膜(第1のレジスト膜)と、バンプ乃至パッド形成用のネガパターンのレジスト膜(第2のレジスト膜)を形成してこれらをマスクとしてバンプ乃至パッド材料膜を電解メッキすることによりバンプ乃至パッドを形成し、次に第2のレジスト膜のみ除去したうえで第1のレジスト膜をマスクとして電解メッキにより配線膜を形成するものである。

#### [0010]

従って、請求項1の半導体素子実装用配線基板の製造方法によれば、配線膜形成前の段階において、配線膜に対してネガのパターンを有するレジスト膜とパンプ乃至パッドに対してネガのパターンを有するレジスト膜をマスクとしてメッキすることによりバンプ乃至パッドを形成するので、そのメッキに際して金属ベースを電位伝達手段として用いることができる。従って、バンプ乃至パッドを電解メッキ用引出回路を設けなくても電解メッキにより形成する方法が持つ欠点は一切回避することができるのみならず、電界メッキ法が持つところの配線膜毎に電位を付与するために電解メッキ用引出回路を形成する必要もない。依って、電界メッキ法が従来持っていた欠点を回避することができる。

#### [0011]

請求項2の半導体素子実装用配線基板の製造方法は、金属ベースの表面に、形成すべき配線膜に対してネガのパターンを有するレジスト膜をマスクとしてバンプ乃至パッド材料を上記金属ベース表面に電解メッキすることによりバンプ乃至パッドを形成し、更に、該レジスト膜をマスクとして上記金属ベース表面のパッド上に配線膜材料を電解メッキすることにより配線膜を形成することを特徴とする。

## [0012]

従って、請求項2の半導体素子実装用配線基板の製造方法によれば、配線膜選択的形成用マスクとして形成したレジスト膜を、バンプ乃至パッド選択的形成用マスクとしても用い、バンプ乃至パッドの形成も配線膜の形成も金属ベースが完全に存在した状態で行われるので、そのメッキに際して金属ベースを電位伝達手段として用いることができる。従って、バンプ乃至パッドを電解メッキ用引出回路を設けなくても電解メッキにより形成することができる。従って、バンプ乃至パッド形成を無電解メッキにより形成する方法が持つ欠点は一切回避することができるのみならず、電界メッキ法が持つところの配線膜毎に電位を付与するために電解メッキ用引出回路を形成する必要もない。依って、電界メッキ法が従来持っていた欠点を回避することができる。

#### [0013]

しかも、ボンディングパッドを選択的に形成するためのマスクとなるレジスト膜と配線膜を選択的に形成するためのマスクとなるレジスト膜は共通なので、レジスト膜を選択的に 形成する一連の工程が1回分少なくて済むという利点もある。

## [0014]

#### 【発明の実施の形態】

本発明は、通常のBGA、CSPタイプの半導体素子実装用配線基板は勿論のこと、ワイヤボンディング型のBGA、CSPタイプの半導体素子実装用配線基板にも適用することができる。第1のレジスト膜として例えば液状レジストTHB-30(JSR)を用いる

20

30

40

ことができ(その場合、現像液としてはTHB-DI(JSR)0.5%テトラメチルアンモニウムハイドロオキサイドが好適)、第2のレジスト膜として例えばドライフィルムHN・240(日立化成製)を用いることができ[その場合、現像液としては炭酸ナトリウム1%水溶液[温度40 )が好適]、バンプ乃至パッドの形成後における第1のレジスト膜の除去は、レジスト膜として上記液状レジストTHB-30(JSR)を用いた場合、剥離剤として例えばTHB-SI(JSR)ジメチルスルホキシド+テトラメチルアンモニウムハイドロオキサイドを用いることにより行うことができ、配線膜の形成後における第2のレジスト膜の除去は、レジスト膜として例えばドライフィルムHN・240(日立化成製)を用いた場合、剥離剤として例えば水酸化ナトリウム5%水溶液(40 )を用いることにより行うことができる。バンプ乃至パッドは金膜で形成する場合が多いが、他の金属、例えばパラジウムを用いることもできうるものであり、材料は金に限定されない。

[0015]

### 【実施例】

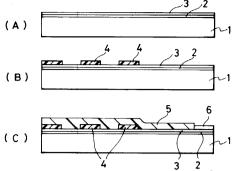

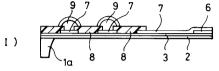

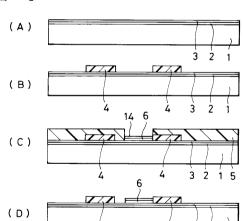

以下、本発明を図示実施例に従って詳細に説明する。図1(A)~(F)及び図2(G)~(J)は本発明半導体素子実装用配線基板の製造方法の第1の実施例を工程順(A)~(J)に示す断面図である。本実施例は本発明をT-BGA用の配線基板(リードフレーム)に適用したものである。

[0016]

( A ) 図 1 ( A ) に示すように、銅合金からなる板状の金属ベース(厚さ例えば 1 5 0  $\mu$  m ) 1 の表面にエッチングストッパとなるニッケル膜(厚さ例えば 2  $\mu$  m ) 2 を形成し、更にメッキ下地膜となる銅膜(厚さ例えば 0 . 1  $\mu$  m ) 3 を形成したものを用意する。

[0017]

(B)次に、図1(B)に示すように、例えば液状レジストTHB-30(JSR)からなる第1のレジスト膜4を選択的に形成する。具体的には、後で形成する配線膜(7)に対してネガのパターンを有するように選択的に形成する。この選択的形成はレジスト膜4の全面的形成の後、露光、現像処理を為すことにより行うが、レジスト膜4の材料として上記液状レジストTHB-30(JSR)を用いた場合、その現像の際に現像液として例えばTHB-D1(JSR)0.5%テトラメチルアンモニウムハイドロオキサイドを用いると良い。

[0018]

(C)次に、図1(C)に示すように、例えばドライフィルム  $HN \cdot 2 \cdot 4 \cdot 0$ (日立化成製)からなる第2のレジスト膜5を、形成すべきバンプ(6)に対してネガのパターンを有するように形成し、該第2のレジスト膜5をマスクとして例えば金を電解メッキすることによりバンプ(厚さ例えば2~10 $\mu$ m)6を形成する。尚、第2のレジスト膜5の選択的形成も、レジスト膜5の全面的形成の後、露光、現像処理を為すことにより行うが、レジスト膜5の材料として上記ドライフィルム  $HN \cdot 2 \cdot 4 \cdot 0$ (日立化成製)を用いた場合、その現像の際に現像液として炭酸ナトリウム1%水溶液(温度40)を用いると良い。

[0019]

(D)次に、水酸化ナトリウム約5%水溶液(40)を剥離液として用いることにより 40図1(D)に示すように、第2のレジスト膜5のみを除去する。尚、上記第1のレジスト膜4は、この剥離液には殆ど侵されず、殆どそのまま残存する。

[0020]

(Ε)次に、図1(Ε)に示すように、第1のレジスト膜4をマスクとして例えば銅を電解メッキすることにより配線膜(厚さ例えば25~30μm)7を形成する。

[0021]

(F)次に、THB-S1(JSR)ジメチルスルホキシド+テトラメチルアンモニウム ハイドロオキサイドを剥離液として用いることにより、図1(F)に示すように、第1の レジスト膜4を除去する。

[0022]

30

20

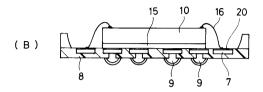

(G)次に、例えばポリイミド等から樹脂膜(厚さ例えば25µm)8を、図2(G)に 示すように選択的に形成する。この樹脂膜8が配線膜7を保持する絶縁ベースとなる。

#### [0023]

(H)次に、図2(H)に示すように、半田ボール電極9を形成する。この形成は、ニッ ケルメッキ、金又はニッケル及び半田を順次電解メッキすることにより行う。

#### [0024]

(Ⅰ)次に、図2(Ⅰ)に示すように、銅からなる金属ベース1をその裏面側から選択的 にエッチングする。エッチングするのは多数の配線膜7が形成された領域と対応する場所 であり、外周リング1aとすべき部分のみ残存させる。このエッチングに際し上記ニッケ ル膜2がエッチングストッパになり、折角形成した配線膜7がエッチングされることを阻 む。

#### [0025]

(J)次に、図2(J)に示すように、上記エッチングストッパとしての役割を果たした ニッケル膜2及び銅膜3をエッチングにより除去する。これにより各配線膜7が他の配線 膜7と電気的に導通した状態でなくなり、電気的に独立する。これでリードフレームが完 成した状態になる。

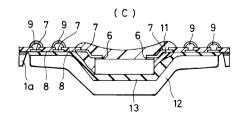

#### [0026]

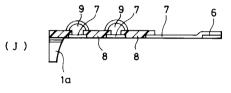

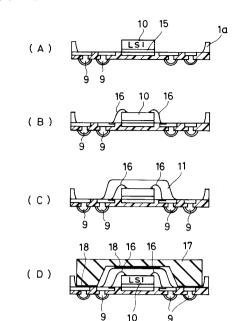

図3(A)~(C)は上記配線基板(リードフレーム)を半導体素子に実装する方法を工 程順に示す断面図である。先ず、図3(A)に示すように、各配線膜7のインナーリード 先端部の金からなるバンプァを、半導体素子10の各電極パッド10aにボンディングす る。

#### [0027]

次に、図3(B)に示すように、半導体素子10表面部を樹脂11により封止し、その後 図3(C)に示すように、スティフナー12を接着剤13を介して半導体素子10及び リードフレームの裏面に接着する。

#### [0028]

本実施例によれば、配線膜7形成前の段階において、配線膜7に対してネガのパターンを 有する第1のレジスト膜4とパンプ6に対してネガのパターンを有する第2のレジスト膜 5 をマスクとしてメッキすることによりバンプ 6 を形成するので、そのメッキに際して金 属ベース1を電位伝達手段として用いることができる。従って、バンプ6を電解メッキ用 引出回路を設けなくても電解メッキにより形成することができる。従って、バンプ6形成 を無電解メッキにより形成する方法が持つ欠点は一切回避することができるのみならず、 電界メッキ法が持つところの配線膜7毎に電位を付与するために電解メッキ用引出回路を 形成する必要もない。依って、電界メッキ法が従来持っていた欠点を回避することができ る。

#### [0029]

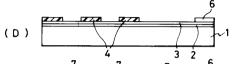

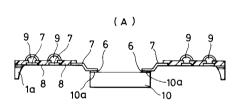

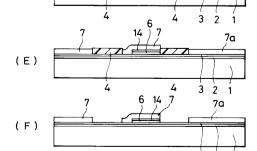

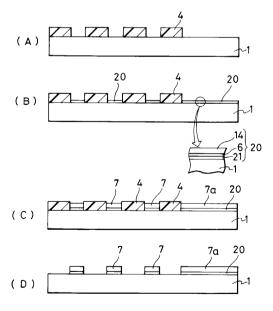

図4(A)~(F)及び図5(G)~(J)は本発明半導体素子実装用配線基板の製造方 法の第2の実施例を工程順(A)~(J)に示す断面図である。本実施例は本発明をワイ ヤボンディングタイプT-BGA用配線基板に適用したものである。

#### [0030]

(A)図4(A)に示すように、銅合金からなる板状の金属ベース(厚さ例えば150μ m) 1 の表面にエッチングストッパとなるニッケル膜(厚さ例えば 2 μm) 2 を形成し、 更にメッキ下地膜となる銅膜(厚さ例えば 0 . 1 μ m ) 3 を形成したものを用意する。

## [0031]

(B)次に、図4(B)に示すように、例えば液状レジストTHB-30(JSR)から なる第1のレジスト膜4を選択的に形成する。具体的には、後で形成する配線膜(7)に 対してネガのパターンを有するように選択的に形成する。現像は現像液として例えばTH B - D I ( J S R ) 0 . 5 % テトラメチルアンモニウムハイドロオキサイドを用いて行う

[0032]

50

30

40

(C)次に、図4(C)に示すように、例えばドライフィルム HN・240(日立化成製)からなる第2のレジスト膜5を、形成すべきボンディングパッド(6)に対してネガのパターンを有するように形成し、該第2のレジスト膜5をマスクとして先ず例えば金を電解メッキすることによりボンディングパッド(厚さ例えば2~10  $\mu$  m)6を形成し、更に例えばニッケルを電解メッキすることにより超音波振動拡散防止膜(膜厚例えば5  $\mu$  m)14を形成する。この超音波振動拡散防止膜14は後で半導体素子(10)の電極と配線膜7のパッド6とをワイヤ(16)にて超音波ボンディングによりボンディングするとき印加する超音波振動が拡散してしまいワイヤボンディングによりボンディングするとき印加する超音波振動が拡散してしまいワイヤボンディングに寄与しないことを阻む役割を果たす。尚、第2のレジスト膜5のパターニングのための現像には現像液として例えば炭酸ナトリウム1%水溶液(温度40)を用いる

10

20

30

(D)次に、例えば水酸化ナトリウム約5%水溶液(40)を剥離液として用いることにより図4(D)に示すように、第2のレジスト膜5のみを除去する。尚、上記第1のレジスト膜4はこの剥離液には殆ど侵されず、殆どそのまま残存する。

#### [0033]

(E)次に、図4(E)に示すように、第1のレジスト膜4をマスクとして例えば銅を電解メッキすることにより配線膜(厚さ例えば25~30μm)7を形成する。尚、7aは配線膜7のうちの半導体素子(10)をボンディングするチップボンディング領域である

[0034]

(F)次に、例えばTHB-SI(JSR)ジメチルスルホキシド+テトラメチルアンモニウムハイドロオキサイドを剥離液として用いることにより、図4(F)に示すように、 第1のレジスト膜4を除去する。

[0035]

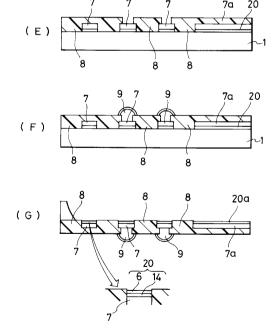

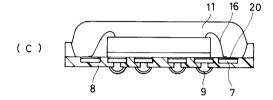

(G)次に、例えばポリイミド等から樹脂膜(厚さ例えば 2 5 μm) 8 を図 5 (G)に示すように選択的に形成する。この樹脂膜 8 が配線膜 7 を保持する絶縁ベースとなる。

[0036]

(H)次に、図5(H)に示すように、半田ボール電極9を形成する。この形成は、例えば、ニッケルメッキ、金又はニッケル及び半田を順次電解メッキすることにより行う。

[0037]

(I)次に、図5(I)に示すように、銅からなる金属ベース1をその裏面側から選択的にエッチングする。エッチングするのは多数の配線膜7が形成された領域と対応する場所であり、外周リング1aとすべき部分のみ残存させる。このエッチングに際し上記ニッケル膜2がエッチングストッパになり、折角形成した配線膜7がエッチングされることを阻む。

[0038]

(J)次に、図5(J)に示すように、上記エッチングストッパとしての役割を果たしたニッケル膜2及び銅膜3をエッチングにより除去する。これにより各配線膜7が他の配線膜7と電気的に導通した状態でなくなり、電気的に独立する。これでリードフレームが完成した状態になる。リードフレームの各配線膜7(7aも含む)の露出した面が半導体素子搭載側の面となる。

[0039]

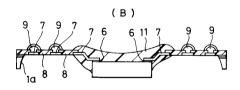

図6(A)乃至(D)は図4、図5に示した方法で製造されたリードフレームを用いての半導体素子の実装方法の一例を工程順に示す断面図である。図6に従ってその方法を説明すると、先ず、図6(A)に示すように、半導体素子10を配線膜7のチップボンディング領域7aにチップボンディングする。15は接着剤である。次いで、図6(B)に示すように、半導体素子10の電極と配線膜7のボンディングパッド6との間をワイヤボンディングにより接続する。16はそのワイヤである。このワイヤボンディングは超音波ボンディングにより行い、その際に、上記超音波振動拡散防止膜14が超音波振動の拡散を阻んで良好なワイヤボンディングに寄与することは前述の通りである。

[0040]

50

10

20

30

50

その後、図6(C)に示すように、上記半導体素子10及びワイヤ16を樹脂11により 封止する。その後、図6(D)に示すようにスティフナー兼ヒートスプレッダ17を接着 剤18を介して封止樹脂11及びリードフレームに接着する。

#### [0041]

本実施例においても上述した第 1 の実施例で享受した効果と同じ効果を享受することができる。

#### [0042]

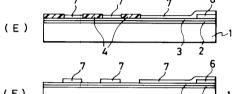

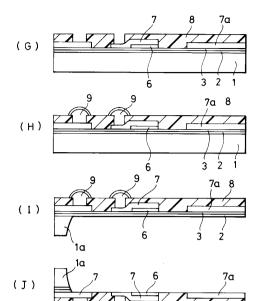

図7(A)~(D)及び図8(E)~(G)は本発明半導体素子実装用配線基板の製造方法の第3の実施例を工程順(A)~(G)に示す。本実施例は本発明をワイヤボンディングタイプT-CSP用配線基板(リードフレーム)に適用したものである。

#### [0043]

(A) 図7(A) に示すように、銅合金からなる板状の金属ベース(厚さ例えば  $150\mu$  m) 1 を用意し、その表面に、レジスト膜 4 を選択的に形成する。具体的には、後で形成する配線膜(7) に対してネガのパターンを有するように選択的に形成する。尚、金属ベース 1 として表面にエッチングストッパを成す例えばニッケル膜(厚さ  $2\mu$  m)を全面的に形成したものを用いても良い。

#### [0044]

(B)次に、図7(B)に示すように、上記レジスト膜4をマスクとして金属ベース1表面にメッキ膜20を電解メッキにより形成する。このメッキ膜20は図7(B)右下部に示すように、エッチングストッパを成すニッケル膜21と、ボンディングパッドを成す金膜(但し、本実施例における金膜6は配線膜全域の表面に形成され、この点が第2の実施例とは異なる。)6と、超音波振動拡散防止膜を成すニッケル膜14からなる三層構造を有している。従って、このメッキ膜20はレジスト膜4をマスクとする電解メッキをニッケル、金、ニッケルの順で3回行えばよいことになる。尚、金属ベース1としてその表面に全面的にエッチングストッパを成すニッケル膜を形成したものを用いることとした場合には、ニッケル膜21は形成する必要がない。

### [0045]

( C )次に、図 7 ( C )に示すように、上記レジスト膜 4 をマスクとして例えば銅を電解メッキすることにより配線膜(厚さ例えば 2 5 ~ 3 0  $\mu$  m ) 7 を形成する。尚、 7 a は配線膜 7 のうちの半導体素子( 1 0 )をボンディングするチップボンディング領域である。

#### [0046]

(D)次に、図7(D)に示すように、レジスト膜4を除去する。

#### [0047]

(E)次に、例えばポリイミド等から樹脂膜(厚さ例えば 2 5 μm) 8 を図 8 (E)に示すように選択的に形成する。この樹脂膜 8 が配線膜 7 を保持する絶縁ベースとなる。

#### [0048]

(F)次に、図8(F)に示すように、半田ボール電極9を形成する。この形成は、例えば、ニッケルメッキ、金又はニッケル及び半田を順次電解メッキすることにより行う。

#### [0049]

(G)次に、銅からなる金属ベース1をその裏面側から選択的にエッチングする。エッチ 40ングするのは多数の配線膜7が形成された領域と対応する場所であり、外周リング1aとすべき部分のみ残存させる。このエッチングに際し上記ニッケル膜2がエッチングストッパになり、折角形成した配線膜7がエッチングされることを阻む。

## [0050]

次に、図8(G)に示すように、上記エッチングストッパとしての役割を果たしたニッケル膜2をエッチングにより除去する。これにより各配線膜7表面の金膜6が露出し、ボンディングパッドとしての役割を果たし得る。また、金属ベース1としてその表面にエッチングストッパを成すニッケル膜を全面的に形成したものを用いた場合には、そのニッケル膜を除去することは単に金膜6を露出させるのみならず、各配線膜7を他の配線膜7から電気的に分離し独立させる役割も果たしたことになる。これでリードフレームが完成した

20

30

40

50

状態になる。リードフレームの各配線膜7(7a)の露出した面が半導体素子搭載側の面となる。

#### [0051]

本実施例は、ボンディングパッドを成す金膜6の選択的形成を、配線膜7の選択的形成に際してマスクとして用いたレジスト膜4をそのまま用いて行う点で、第1、第2の実施例と異なるが、メッキに際して金属ベース1を電位伝達手段として用いることができるという点では全く共通しており、パッド6を電解メッキ用引出回路を設けなくても電解メッキにより形成することができ、従って、バンプ6形成を無電解メッキにより形成する方法が持つ欠点は一切回避することができるのみならず、電界メッキ法が持つところの配線膜7毎に電位を付与するために電解メッキ用引出回路を形成する必要もないという効果を享有できるという点では第1、第2の実施例と共通している。依って、電界メッキ法が従来持っていた欠点を回避することができる。しかも、ボンディングパッド6を選択的に形成するためのマスクとなるレジスト膜と配線膜を選択的に形成するためのマスクとなるレジスト膜は共通なので、レジスト膜を選択的に形成する一連の工程が1回分少なくて済むという利点もある。

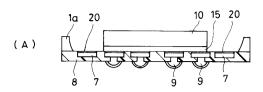

#### [0052]

図9(A)乃至(C)は図7、図8に示した方法で製造された配線基板(リードフレーム)を用いての半導体素子の実装方法の一例を工程順に示す断面図である。図9に従ってその方法を説明すると、先ず、図9(A)に示すように、半導体素子10をチップボンディングする。15は接着剤である。次いで、図9(B)に示すように、半導体素子10の電極と配線膜7のボンディングパッド6との間をワイヤボンディングにより接続する。16はそのワイヤである。このワイヤボンディングは超音波ボンディングにより行う。ニッケル膜14が超音波振動拡散防止の役割を果たすことは前述の通りである。

#### [0053]

その後、図9(C)に示すように、上記半導体素子10及びワイヤ16を樹脂11により 封止する。

## [0054]

#### 【発明の効果】

請求項1の半導体素子実装用配線基板の製造方法によれば、配線膜形成前の段階において、配線膜に対してネガのパターンを有するレジスト膜とパンプ乃至パッドに対してネガのパターンを有するレジスト膜をマスクとしてメッキすることによりバンプ乃至パッドを形成するので、そのメッキに際して金属ベースを電位伝達手段として用いることができる。従って、バンプ乃至パッドを無電解メッキにより形成することができる。従って、バンプ乃至パッドを無電解メッキにより形成する方法が持つ欠点は一切回避することができるのみならず、電界メッキ法が持つところの配線膜毎に電位を付与するために電解メッキ用引出回路を形成する必要もない。依って、電界メッキ法が従来持っていた欠点を回避することができる。

#### [0055]

請求項2の半導体素子実装用配線基板の製造方法によれば、配線膜選択的形成用マスクとして形成したレジスト膜を、バンプ乃至パッド選択的形成用マスクとしても用い、バンプ乃至パッドの形成も配線膜の形成も金属ベースが完全に存在した状態で行われるので、そのメッキに際して金属ベースを電位伝達手段として用いることができる。従って、バンプ乃至パッドを電解メッキにより形成することができる。従って、バンプ乃至パッドを無電解メッキにより形成する方法が持つ欠点は一切回避することができるのみならず、電界メッキ法が持つところの配線膜毎に電位を付与するために電解メッキ用引出回路を形成する必要もない。依って、電界メッキ法が従来持っていた欠点を回避することができる。

### [0056]

しかも、ボンディングパッド 6 を選択的に形成するためのマスクとなるレジスト膜と配線膜を選択的に形成するためのマスクとなるレジスト膜は共通なので、レジスト膜を選択的

に形成する一連の工程が1回分少なくて済むという利点もある。

### [0057]

請求項3の半導体素子実装用配線基板の製造方法によれば、金属ベースとしてエッチングストップ膜を表面に有するものを用いるので、配線膜及びバンプ乃至パッドの形成後、金属ベースを裏面からエッチングして金属ベースの不要部分を除去するエッチングの際にエッチングストップ膜により配線膜が侵食されるのを防止することができる。そして、そのエッチング後にそのエッチングストップ膜を除去することによりエッチングストップ膜により全配線膜が互いに電気的に接続された状態をなくし、つまり、各配線膜を電気的に独立した状態し、更に、パッド或いはバンプが露出する状態にすることができる。

#### 【図面の簡単な説明】

【図1】(A)乃至(F)は本発明半導体素子実装用配線基板の製造方法の第1の実施例の工程(A)~(F)を順に示す断面図である。

【図2】(G)乃至(J)は本発明半導体素子実装用配線基板の製造方法の第1の実施例の工程(G)~(J)を順に示す断面図である。

【図3】(A)~(C)は図1、図2に示した方法で製造した配線基板(リードフレーム)を用いて実装する方法の一例を工程順に示す断面図である。

【図4】(A)乃至(F)は本発明半導体素子実装用配線基板の製造方法の第2の実施例の工程(A)~(F)を順に示す断面図である。

【図5】(G)乃至(J)は本発明半導体素子実装用配線基板の製造方法の第2の実施例の工程(G)~(J)を順に示す断面図である。

【図 6 】(A)~(D)は図 4、図 5 に示した方法で製造した配線基板(リードフレーム)を用いて実装する方法の一例を工程順に示す断面図である。

【図7】(A)乃至(D)は本発明半導体素子実装用配線基板の製造方法の第3の実施例の工程(A)~(D)を順に示す断面図である。

【図8】(E)乃至(G)は本発明半導体素子実装用配線基板の製造方法の第3の実施例の工程(E)~(G)を順に示す断面図である。

【図9】(A)~(D)は図7、図8に示した方法で製造した配線基板(リードフレーム)を用いて実装する方法の一例を工程順に示す断面図である。

【図10】(A)乃至(D)は半導体素子実装用配線基板の製造方法の一つの従来例を工程順に示す断面図である。

【図11】(A)乃至(C)は半導体素子実装用配線基板の製造方法の別の従来例を工程順に示す断面図である。

#### 【符号の説明】

1 ・・・金属ベース、 2 ・・・エッチングストップ膜(エッチングストッパ)、 4 ・・・ 第 1 のレジスト膜(レジスト膜)、 5 ・・・第 2 のレジスト膜、 6 ・・・バンプ乃至パッ ド膜、 7 ・・・配線膜、 1 0 ・・・半導体素子、 2 1 ・・・エッチングストップ膜。 10

20

# 【図1】

【図2】

【図3】

【図4】

# 【図5】

# 【図6】

【図7】

【図8】

## 【図9】

## 【図10】

## 【図11】

## フロントページの続き

(72)発明者 飯島 朝雄

東京都豊島区南大塚三丁目37番5号 株式会社ノース内

(72)発明者 草野 英俊

東京都品川区北品川6丁目7番35号 ソニー株式会社内

## 審査官 石野 忠志

(56)参考文献 特開平09-213863(JP,A)

特開平09-213750(JP,A)

特開昭62-241347(JP,A)

特開昭63-216994(JP,A)

特開平05-326783(JP,A)

特開平06-077650(JP,A)

## (58)調査した分野(Int.CI., DB名)

H01L 21/60

H01L 23/50