# (10) **DE 10 2008 064 686 B4** 2014.04.10

(12)

## **Patentschrift**

(21) Aktenzeichen: 10 2008 064 686.5

(22) Anmeldetag: 21.05.2008

(43) Offenlegungstag: 27.11.2008

(45) Veröffentlichungstag

der Patenterteilung: 10.04.2014

(51) Int Cl.: **H01L 29/739** (2006.01)

H01L 29/78 (2006.01)

Innerhalb von neun Monaten nach Veröffentlichung der Patenterteilung kann nach § 59 Patentgesetz gegen das Patent Einspruch erhoben werden. Der Einspruch ist schriftlich zu erklären und zu begründen. Innerhalb der Einspruchsfrist ist eine Einspruchsgebühr in Höhe von 200 Euro zu entrichten (§ 6 Patentkostengesetz in Verbindung mit der Anlage zu § 2 Abs. 1 Patentkostengesetz).

| (30) Unionspriorität:                                                                   | (56) Ermittelter Stand der Technik: |

|-----------------------------------------------------------------------------------------|-------------------------------------|

| 2007-139509 25.05.2007 JP                                                               | DE 101 23 818 B4                    |

|                                                                                         | DE 103 61 714 A1                    |

| (62) Teilung aus:                                                                       | DE 199 60 563 A1                    |

| 10 2008 024 467.8                                                                       | DE 10 2004 022 455 A1               |

|                                                                                         | US 2002 / 0 050 603 A1              |

| (73) Patentinhaber:                                                                     | US 2002 / 0 088 991 A1              |

| Mitsubishi Electric Corp., Tokyo, JP                                                    | US 2008 / 0 079 081 A1              |

|                                                                                         | US 5 115 369 A                      |

| (74) Vertreter:                                                                         | JP 2002- 083 964 A                  |

| PRÜFER & PARTNER GbR, 81479, München, DE                                                | JP 2003-197 914 A                   |

|                                                                                         | JP 2001- 044 435 A                  |

| (72) Erfinder:                                                                          | JP 2004- 281 918 A                  |

| Kusunoki, Shigeru, Tokyo, JP; Mochizuki, Koichi, Tokyo, JP; Kawakami, Minoru, Tokyo, JP |                                     |

(54) Bezeichnung: Halbleitervorrichtung

(57) Hauptanspruch: Halbleitervorrichtung mit: einem Halbleitersubstrat (101);

einem Isolierfilm (14b), der zumindest einen Teil des Halbleitersubstrats (101) abdeckt;

einem Halbleiterelement (EL), das eine Elektrode hat; und einem Widerstandselement (4t), das an dem Isolierfilm (14b) angeordnet ist und mit der Elektrode elektrisch verbunden ist, um einen Widerstand für einen durch die Elektrode hindurch strömenden Strom zu bilden, wobei

das Widerstandselement (4t) eine leicht dotierte Halbleiterlage (23a) aufweist, so dass in Abhängigkeit von einer Potentialdifferenz zwischen dem Halbleitersubstrat (101) und dem Widerstandselement (4t) eine Verarmungsschicht und eine Inversionsschicht in der leicht dotierten Halbleiterlage (23a) erzeugt werden können.

#### **Beschreibung**

#### HINTERGRUND DER ERFINDUNG

Gebiet der Erfindung

**[0001]** Die vorliegende Erfindung bezieht sich auf eine Halbleitervorrichtung und insbesondere auf eine Halbleitervorrichtung mit einem Kanalbereich, der durch einen Teil eines Halbleitersubstrates gebildet ist, und einer Elektrode.

Beschreibung des zugehörigen Stands der Technik

[0002] Als Halbleitervorrichtungen sind Leistungshalbleiterchips wie zum Beispiel ein IGBT (Insolated-Gate-Bipolar-Transistor) und ein Leistungs-MOS-FET (Metal-Oxid-Semiconductor-Field-Effekt-Transistor) vorhanden. Gates von diesen Halbleiterchips haben hauptsächlich eine ebene Gatestruktur oder eine Grabengatestruktur.

[0003] Im Stand der Technik besteht das Gate der Grabengatestruktur zum Beispiel aus polykristallinem Silizium. In den letzten Jahren wurden derartige Verfahren vorgeschlagen, die ein Metall mit einem hohen Schmelzpunkt verwenden, um einen Widerstand des Grabengates abzusenken. Zum Beispiel gemäß der Japanischen Patentanmeldung JP-2001-044435 A sind eine polykristalline Siliziumlage (d. h. eine Pufferlage) sowie ein Metall mit einem hohen Schmelzpunkt in einem Graben der Grabengatestruktur angeordnet.

**[0004]** Ein Widerstandselement, das als ein Gatewiderstand bezeichnet wird, kann mit dem Gate verbunden werden. Auch wenn der Gatewiderstand hinsichtlich des Halbleiterchips mit einer herkömmlichen Struktur außen angeordnet ist, wurde in den letzten Jahren vorgeschlagen, den Gatewiderstand im Inneren des Halbleiterchips anzuordnen.

[0005] Zum Beispiel hat die Japanische Patentanmeldung JP-2002-083964 A einen Gatewiderstand (innerer Gatewiderstand) vorgeschlagen, der im Inneren eines Halbleiterchips angeordnet ist. Gemäß dieser Offenlegungsschrift stabilisiert der innere Gatewiderstand, der zum Beispiel aus polykristallinem Silizium besteht, einen Schaltbetrieb der Halbleiterelemente, die parallel angeschlossen sind.

[0006] Zum Beispiel hat die Japanische Patentanmeldung JP-2003-197914 A eine Halbleitervorrichtung offenbart, bei der ein innerer Gatewiderstand, der zum Beispiel aus polykristallinem Silizium besteht, unter einem Gateanschluss angeordnet ist, d. h. in einem freiliegenden Abschnitt einer Verbindungselektrode außerhalb des Gates, wobei dazwischen ein Zwischenlagenisolierfilm ist. Gemäß dieser Offenlegungsschrift sorgt diese Struktur für ei-

ne Halbleitervorrichtung, die eine Fläche eines aktiven Bereiches eines Halbleitersubstrates nicht reduziert, sie hat einen inneren Gatewiderstand mit einer großen Fläche und sie kann eine Stromdichte eines Übergangsstrompulses unterdrücken.

[0007] Die vorstehend genannte Halbleitervorrichtung mit dem äußeren Gatewiderstand leidet an einem Problem einer erhöhten Anzahl der Bauteile. Außerdem ändert sich wahrscheinlich ein Potenzial einer Verbindung zwischen dem Gatewiderstand und dem Halbleiterchip aufgrund von äußeren Störgrößen, und diese Potenzialänderung beeinträchtigt direkt das Gate in dem Halbleiterchip ohne Einwirkung eines Gatewiderstands. Dies führt zu einem Problem, dass die Halbleitervorrichtung wahrscheinlich eine Fehlfunktion hat oder oszilliert.

[0008] Wenn zum Beispiel einige hundert bis zehntausend Gates in einem IGBT mit Strömen versorgt werden, strömt ein hoher Strom durch einen Gatewiderstand. In diesem Fall muß ein Strompfad des Gatewiderstands eine große Querschnittsfläche aufweisen, um die Zuverlässigkeit zu gewährleisten. Bei der Halbleitervorrichtung der japanischen Patentanmeldung JP-2002-083964 A, die vorstehend beschrieben ist, ist es erforderlich, die Breite oder eine Dicke des inneren Gatewiderstands zu vergrößern. Jedoch führt eine Vergrößerung der Dicke zu einem Problem, dass eine lange Zeit zum Ablagern eines Films erforderlich ist, der den inneren Gatewidestand ausbildet, und dass eine Verarbeitung oder Bearbeitung des so abgelagerten Filmes schwierig ist. Außerdem führt eine Vergrößerung der Breite zu einem Problem, dass Flächen des inneren Gatewiderstands und daher der Halbleiterchip vergrößert werden.

[0009] Gemäß dem inneren Gatewiderstand der japanischen Patentanmeldung JP-2003-197914 A, die vorstehend beschrieben ist, kann eine Fläche des Halbleiterchips reduziert werden, da sich der Gateanschluss und der innere Gatewiderstand miteinander überlappen, aber die Fläche kann höchstens nur durch eine Fläche des Gateanschlusses reduziert werden.

[0010] DE 199 60 563 A1 beschreibt eine Halbleiterstruktur mit einem Substrat, einer Mehrzahl darin vorgesehener Gräben und einer Leiterbahn, die derart in die Gräben gefaltet ist, dass ihre Länge innerhalb eines Grabens zumindest die doppelte Grabentiefe beträgt.

**[0011]** DE 103 61 714 A1 beschreibt ein Halbleiterbauelement, bei welchem zwischen einem Gate-Anschluss und einem Source-Anschluss ein Steuerwiderstandselement vorgesehen ist, das einen Ohmschen Widerstand aufweist, der mit steigender Betriebstemperatur monoton fallend ist.

**[0012]** US 5 115 369 A beschreibt einen Leistungstransistor, dessen Steuerelektrode mit einem Polysilizium-JFET verbunden ist. Bei dem Leistungstransistor handelt es sich um einen MOSFET, dessen Steueranschluss mit der Source des JFET verbunden ist, so dass ein Drain-Anschluss des JFET als Eingang fungiert. Mittels des JFET wird ein Widerstand realisiert, der im Normalbetrieb klein ist, jedoch beim Auftreten eines Avalanche-Durchbruchs ansteigt.

**[0013]** JP 2004-281918 A beschreibt eine Halbleitervorrichtung, in der ein Widerstand mit einem stabilen Widerstandswert realisiert ist. Hierzu wird ein Widerstand in einem Graben ausgebildet.

[0014] DE 10 2004 022 455 A1 beschreibt einen IGBT, bei dem in einem Teil eines zwischen den Graben-Steuerelektroden liegenden Bereichs auf der Emitterseite eine Halbleiterregion ausgebildet ist, welche über zwei Dioden mit der Emitterelektrode verbunden ist. Im abgeschalteten Zustand des IGBT sind die Dioden leitend, wodurch Ladungsträger mit hoher Geschwindigkeit aus dem Bauelement abgeleitet werden.

**[0015]** US 2002/0050603 A beschreibt eine Halbleitervorrichtung, in der eine Zenerdiode zwischen einen Kollektor und ein Gate eines Transistors geschaltet ist, wobei die Zenerdiode in das Transistorelement integriert ist und mit einer Glasschicht bedeckt ist.

**[0016]** US 2002/0088991 A1 beschreibt ebenfalls eine Zenerdiode, die eine Einheitszelle in einer Leistungshalbleitervorrichtung umgibt.

**[0017]** DE 101 23 818 B4 beschreibt eine Anordnung mit Schutzfunktion für ein Halbleiterbauelement, bei der ein MOS-Transistor mit seiner Gateeleketrode mit einem floatenden Gebiet elektrisch verbunden ist oder aus dem floatenden Gebiet besteht.

## KURZFASSUNG DER ERFINDUNG

**[0018]** Es ist die Aufgabe der Erfindung, eine Halbleitervorrichtung mit einem Widerstandselement vorzusehen, die eine kleine Anschlussfläche aufweist und einen großen Strom mit hoher Zuverlässigkeit durchlassen kann.

**[0019]** Die Aufgabe wird gelöst durch eine Halbleitervorrichtung nach Anspruch 1, 5, 9, 10, 11, 12 und 17. Weiterbildungen der Erfindung sind in den Unteransprüchen angegeben.

**[0020]** Weitere Merkmale und Vorteile der vorliegenden Erfindung werden aus der folgenden, detaillierten Beschreibung der vorliegenden Erfindung im Zusammenhang mit den beigefügten Zeichnungen ersichtlich.

#### KURZBESCHREIBUNG DER ZEICHNUNGEN

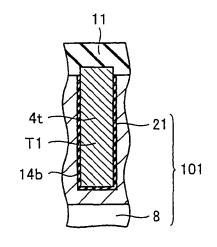

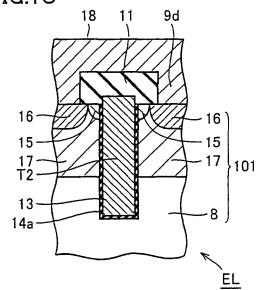

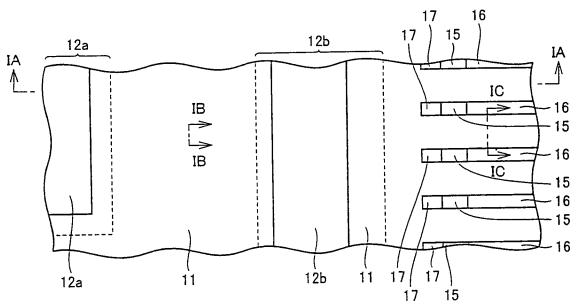

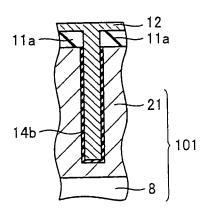

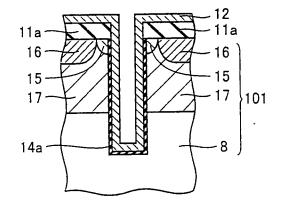

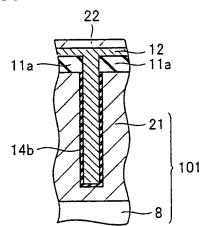

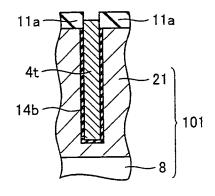

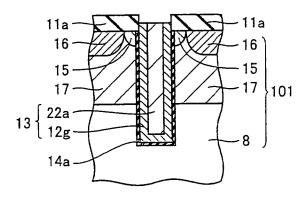

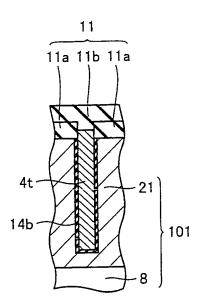

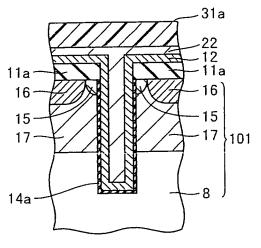

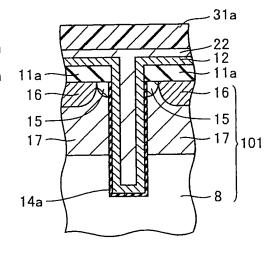

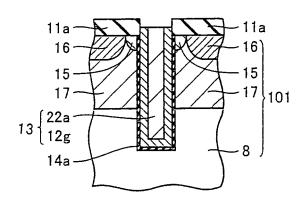

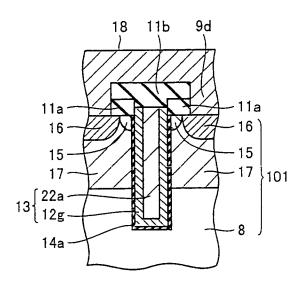

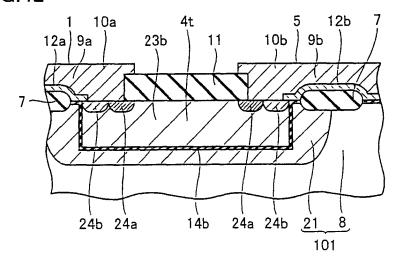

**[0021] Fig.** 1A–**Fig.** 1C zeigen ausschnittartige Schnitte, die schematisch eine Halbleitervorrichtung gemäß einem ersten Erläuterungsbeispiel zeigen.

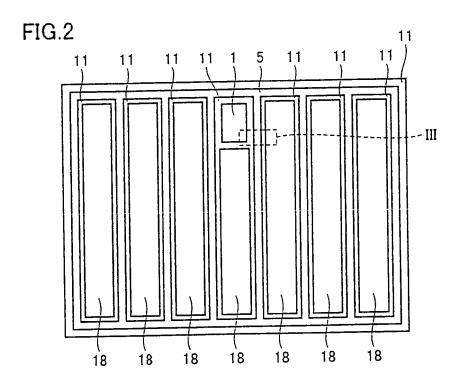

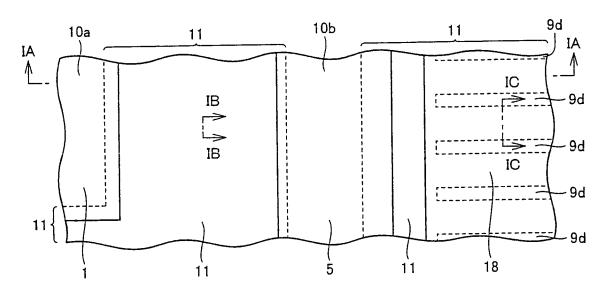

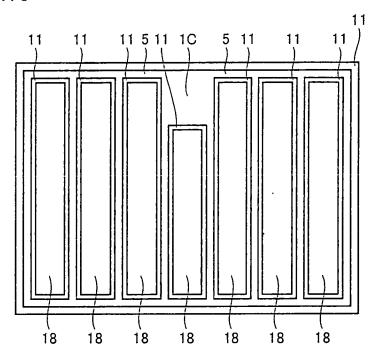

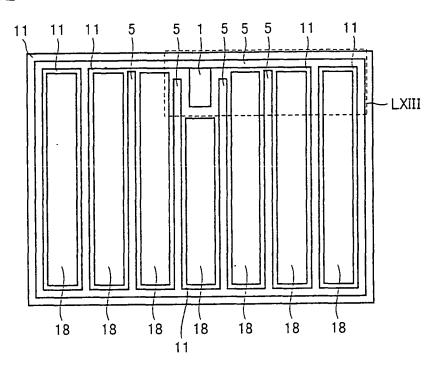

**[0022] Fig.** 2 zeigt eine schematische Draufsicht einer Struktur der Halbleitervorrichtung gemäß des ersten Erläuterungsbeispiels.

**[0023] Fig.** 3 zeigt eine ausschnittartige Draufsicht, die schematisch einen Abschnitt zeigt, der durch III in der **Fig.** 2 angegeben ist.

**[0024] Fig.** 4 entspricht der **Fig.** 3, außer dass ein Gateanschluss, eine Gatehauptzwischenverbindung und ein Emitteranschluss (Emitterelektrode) in der **Fig.** 3 nicht gezeigt sind.

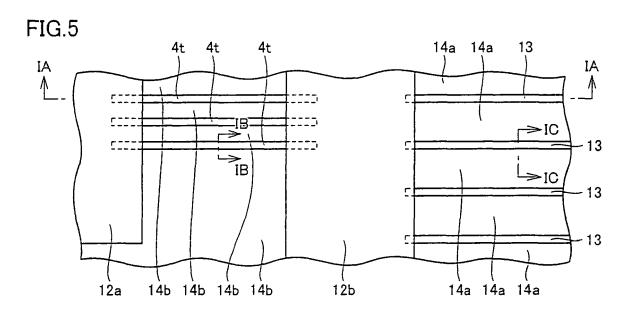

[0025] Fig. 5 entspricht der Fig. 4, außer dass ein Zwischenlagenisolierfilm in der Fig. 4 nicht gezeigt ist

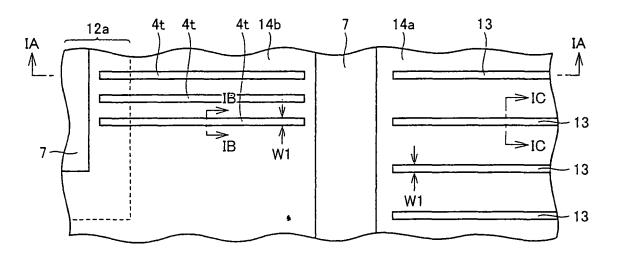

**[0026]** Fig. 6 entspricht der Fig. 5, außer dass polykristalline Siliziumlagen an einer Seite eines Gateanschlusses und einer Seite einer Hauptzwischenverbindung in der Fig. 5 nicht gezeigt sind.

**[0027] Fig.** 7 entspricht der **Fig.** 6, außer dass ein Teil eines Gateoxidfilms und ein Teil eines Isolierfilms in der **Fig.** 6 nicht gezeigt sind.

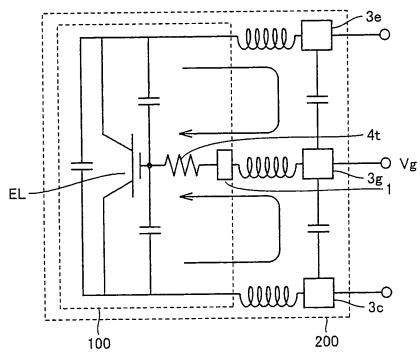

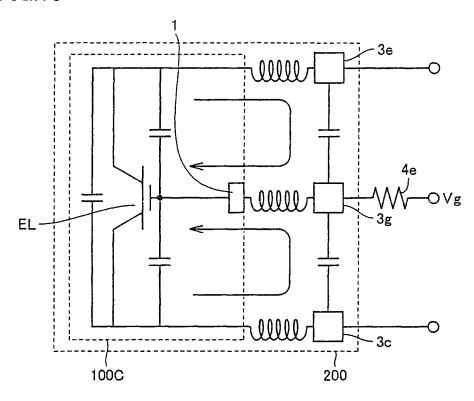

**[0028] Fig.** 8 zeigt schematisch eine Ersatzschaltung in einem Zustand, bei dem die Halbleitervorrichtung des ersten Erläuterungsbeispiels an einer Leiterplatte angeordnet ist.

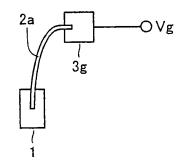

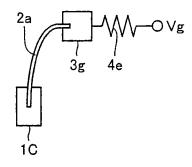

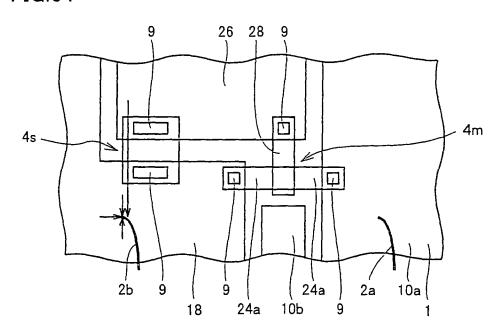

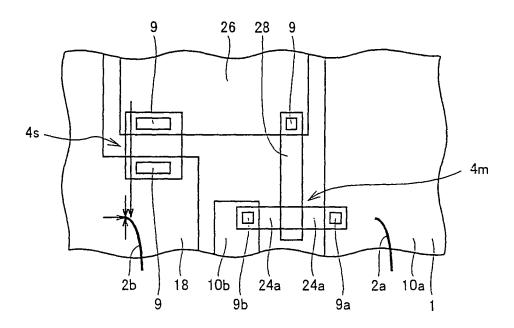

**[0029] Fig.** 9 stellt schematisch einen Verbindungszustand zwischen einem Gateanschluss der Halbleitervorrichtung und einem Anschluss der Leitertafel bei dem ersten Erläuterungsbeispiel dar.

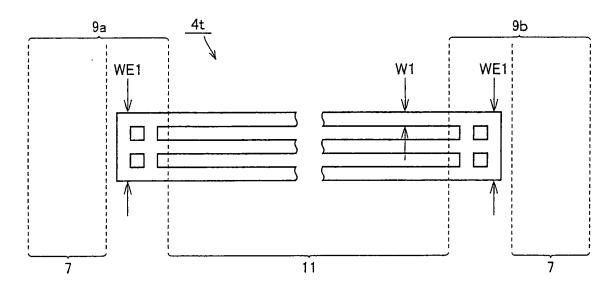

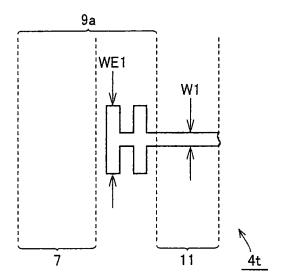

**[0030] Fig.** 10 zeigt eine schematische Draufsicht einer Struktur eines Widerstandselementes in einer Abwandlung der Halbleitervorrichtung des ersten Erläuterungsbeispieles.

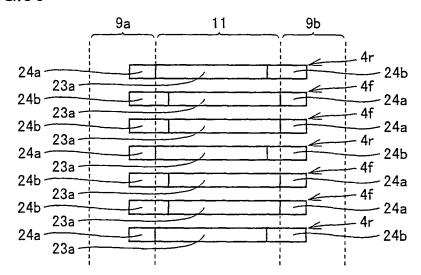

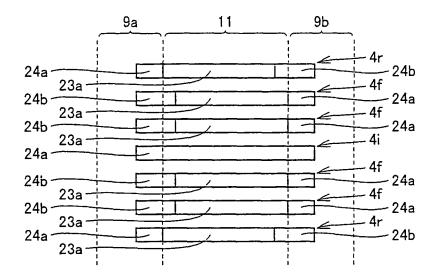

**[0031] Fig.** 11–**Fig.** 15 zeigen ausschnittartige Draufsichten, die schematisch Strukturen von Widerstandselementen in Abwandlungen der Halbleitervorrichtung des ersten Erläuterungsbeispieles zeigen.

**[0032] Fig.** 16 zeigt eine schematische Draufsicht einer Struktur einer Halbleitervorrichtung bei einem ersten Vergleichsbeispiel.

[0033] Fig. 17 stellt schematisch einen Verbindungszustand zwischen einem Gateanschluss der Halbleitervorrichtung und einem Anschluss einer Leiterplatte bei dem ersten Vergleichsbeispiel dar.

**[0034] Fig.** 18 zeigt eine Ersatzschaltung der Halbleitervorrichtung, die an der Leiterplatte bei dem ersten Vergleichsbeispiel angeordnet ist.

**[0035] Fig.** 19 zeigt eine schematische, ausschnittartige Draufsicht einer Halbleitervorrichtung bei einem zweiten Vergleichsbeispiel. Die in der **Fig.** 19 gezeigte Fläche entspricht jener, die in der **Fig.** 5 gezeigt ist. Ein Gateanschluss, eine Gatehauptzwischenverbindung, ein Emitteranschluss und ein Zwischenlagenisolierfilm sind ähnlich wie in der **Fig.** 5 nicht gezeigt.

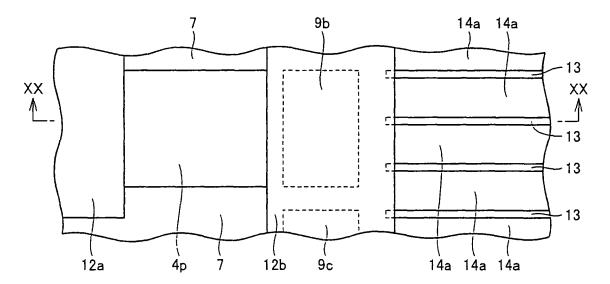

[0036] Fig. 20 zeigt einen schematischen Querschnitt entlang einer Linie XX-XX in der Fig. 19.

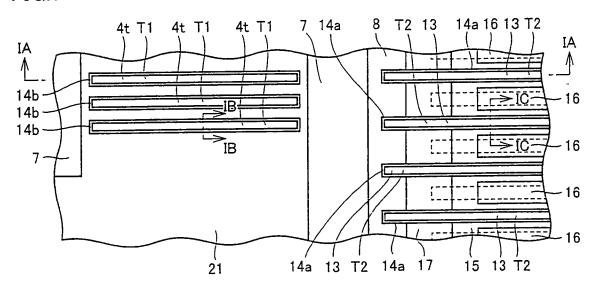

[0037] Fig. 21 zeigt eine schematische, ausschnittartige Draufsicht einer Struktur einer Halbleitervorrichtung gemäß eines zweiten Erläuterungsbeispiels. Die in der Fig. 21 gezeigte Fläche entspricht jener, die in der Fig. 6 gezeigt ist. Ein Gateanschluss, eine Gatehauptzwischenverbindung, ein Emitteranschluss, ein Zwischenlagenisolierfilm und polykristalline Siliziumlagen an einer Seite des Gateanschlusses und an einer Seite der Hauptzwischenverbindung sind, ähnlich wie in der Fig. 6, nicht gezeigt.

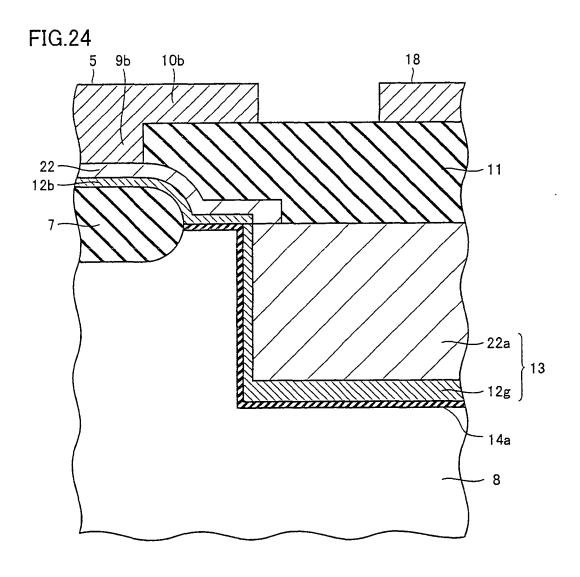

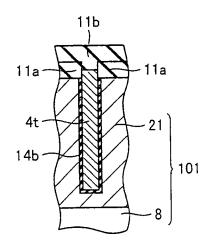

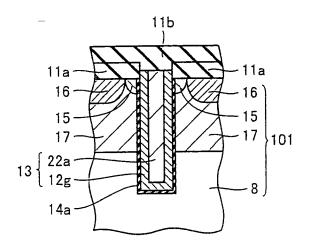

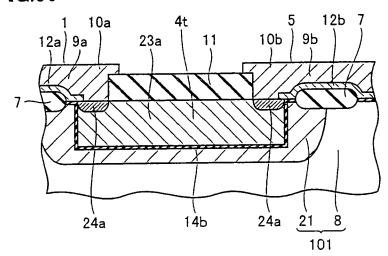

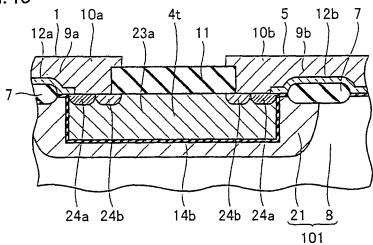

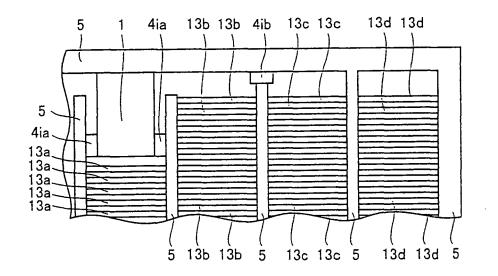

[0038] Fig. 22–Fig. 24 zeigen schematische Querschnitte entlang Linien XXII-XXII, XXIII-XXIII und XXIV-XXIV in der Fig. 21.

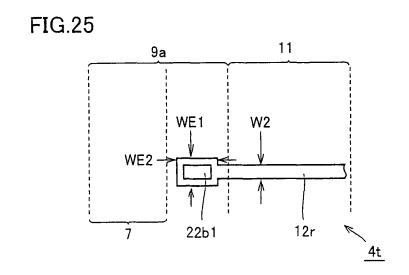

**[0039] Fig.** 25 und **Fig.** 26 zeigen ausschnittartige Draufsichten, die schematisch Strukturen von Widerständen zeigen, die jeweils einen eingebetteten Metallabschnitt aufweisen, bei einer ersten und einer zweiten Abwandlung der Halbleitervorrichtung des zweiten Erläuterungsbeispiels.

[0040] Fig. 27A, Fig. 28A, Fig. 29A, Fig. 30A, Fig. 31A und Fig. 32A zeigen schematische Querschnitte eines ersten bis sechsten Schrittes bei einem Verfahren zum Herstellen der Halbleitervorrichtung gemäß dem zweiten Erläuterungsbeispiel entlang einer Linie XXXIIA-XXXIIA in der Fig. 21.

[0041] Fig. 27B, Fig. 28B, Fig. 29B, Fig. 30B, Fig. 31B und Fig. 32B zeigen schematische Querschnitte des ersten bis sechsten Schrittes bei dem Verfahren zum Herstellen der Halbleitervorrichtung gemäß dem zweiten Erläuterungsbeispiel entlang einer Linie XXXIIB-XXXIIB in der Fig. 21.

[0042] Fig. 33A, Fig. 34A, Fig. 35A, Fig. 36A, Fig. 37A und Fig. 38A zeigen ausschnittartige Querschnitte, die schematisch einen ersten bis sechsten Schritt bei einem Verfahren zum Herstellen einer Halbleitervorrichtung eines dritten Vergleichsbeispiels zeigen, und sie zeigen insbesondere eine Struktur nahe einem ebenen, inneren Gatewider-

stand in einem Bereich entsprechend jenem, der entlang der Linie XX-XX in der **Fig.** 19 verläuft.

[0043] Fig. 33B, Fig. 34B, Fig. 35B, Fig. 36B, Fig. 37B und Fig. 38B zeigen ausschnittartige Querschnitte, die schematisch den ersten bis sechsten Schritt bei dem Verfahren zum Herstellen der Halbleitervorrichtung des dritten Vergleichsbeispiels zeigen, und insbesondere zeigen sie eine Struktur in einem Bereich entsprechend jenem, der entlang der Linie XXXIIB-XXXIIB in der Fig. 21 verläuft.

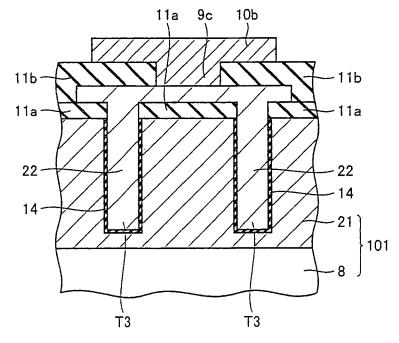

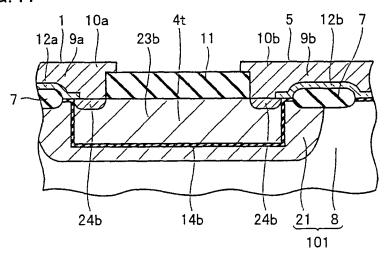

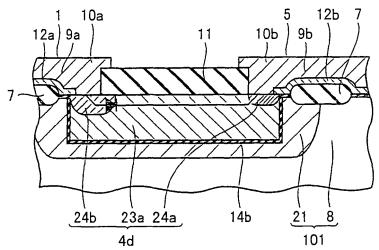

**[0044] Fig.** 39 zeigt einen ausschnittartigen Querschnitt, der schematisch eine Struktur nahe einem Widerstandselement einer Halbleitervorrichtung gemäß einem ersten Ausführungsbeispiel der Erfindung zeigt.

**[0045]** Fig. 40–Fig. 42 zeigen ausschnittartige Querschnitte, die schematisch Strukturen nahe den Widerstandselementen bei den Halbleitervorrichtungen der ersten bis dritten Abwandlung des ersten Ausführungsbeispiels der Erfindung zeigen.

**[0046] Fig.** 43–**Fig.** 45 stellen Betriebe des Widerstandselementes bei der Halbleitervorrichtung gemäß dem ersten Ausführungsbeispiel der Erfindung dar.

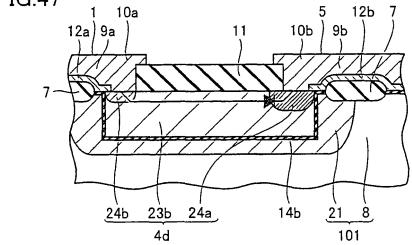

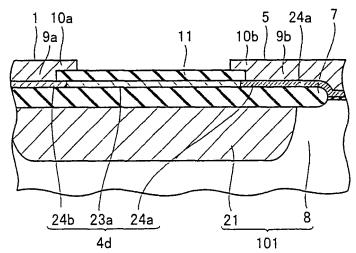

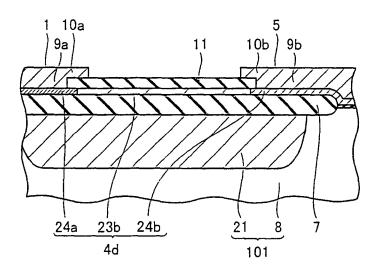

**[0047] Fig.** 46 zeigt einen ausschnittartigen Querschnitt, der schematisch eine Struktur nahe einem Widerstandselement einer Halbleitervorrichtung gemäß einem zweiten Ausführungsbeispiel der Erfindung zeigt.

**[0048] Fig.** 47–**Fig.** 49 zeigen ausschnittartige Querschnitte, die schematisch Strukturen des Widerstandselementes bei der ersten bis dritten Abwandlung der Halbleitervorrichtung des zweiten Ausführungsbeispieles der Erfindung zeigen.

**[0049] Fig.** 50 zeigt eine schematische Draufsicht einer Struktur eines Widerstandselementes einer Halbleitervorrichtung gemäß einem vierten Ausführungsbeispiel der Erfindung.

**[0050]** Fig. 51 zeigt eine schematische Draufsicht einer Struktur eines Widerstandselementes einer Halbleitervorrichtung gemäß einer Abwandlung des vierten Ausführungsbeispiels der Erfindung.

**[0051] Fig.** 52–**Fig.** 55 zeigen ausschnittartige Querschnitte, die schematisch Strukturen nahe Widerstandselementen von Halbleitervorrichtungen gemäß einem siebten bis achten Ausführungsbeispiel der Erfindung zeigen.

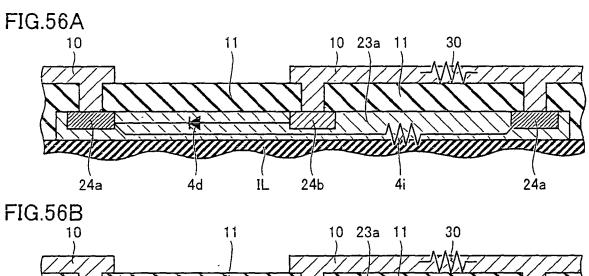

[0052] Fig. 56A zeigt einen ausschnittartigen Querschnitt, der schematisch eine Struktur nahe einem

Widerstandselement einer Halbleitervorrichtung gemäß einem dritten Erläuterungsbeispiel zeigt.

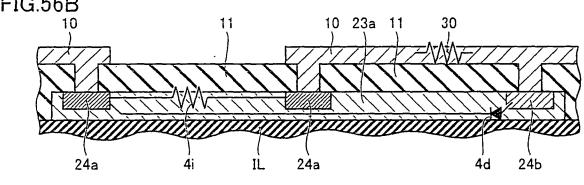

**[0053] Fig.** 56B zeigt einen ausschnittartigen Querschnitt, der schematische eine Struktur nahe einem Widerstandselement einer Halbleitervorrichtung gemäß einer Abwandlung des dritten Erläuterungsbeispieles zeigt.

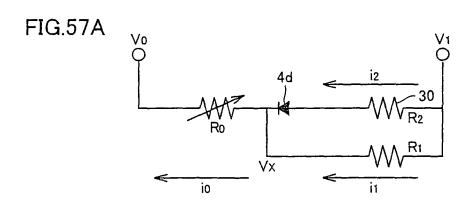

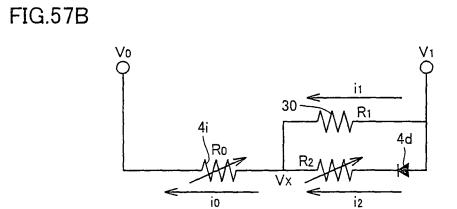

**[0054] Fig.** 57A zeigt eine Ersatzschaltung des Widerstandselementes bei der Halbleitervorrichtung gemäß dem dritten Erläuterungsbeispiel.

**[0055] Fig.** 57B zeigt eine Ersatzschaltung des Widerstandselementes der Halbleitervorrichtung gemäß der Abwandlung des dritten Erläuterungsbeispieles.

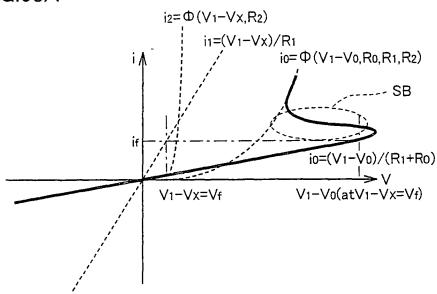

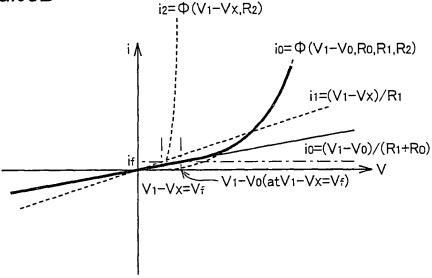

**[0056] Fig.** 58A stellt Spannungs/Strom-Charakteristika dar, die im Falle von ( $R_2 < RR_1 << R_0$ ) durch die Widerstandselemente der Halbleitervorrichtungen gemäß dem dritten Erläuterungsbeispiel und dessen Abwandlung gezeigt werden.

**[0057] Fig.** 58B stellt Spannungs/Strom-Charakteristika dar, die im Falle von  $(R_1 > R_2 >> R_0)$  durch die Widerstandselemente der Halbleitervorrichtungen gemäß dem dritten Erläuterungsbeispiel und dessen Abwandlung gezeigt werden.

**[0058] Fig.** 59 und **Fig.** 60 zeigen ausschnittartige Querschnitte, die schematisch Strukturen nahe Widerstandselementen von Halbleitervorrichtungen gemäß einem vierten Erläuterungsbeispiel sowie einem neunten Ausführungsbeispiel der Erfindung zeigen.

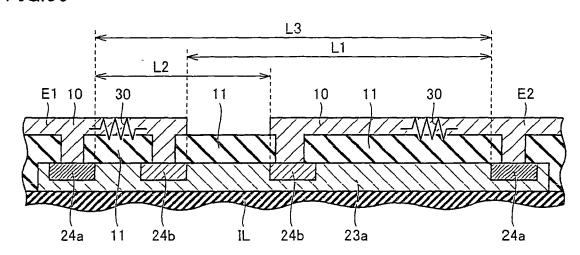

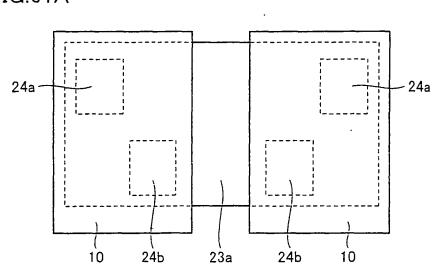

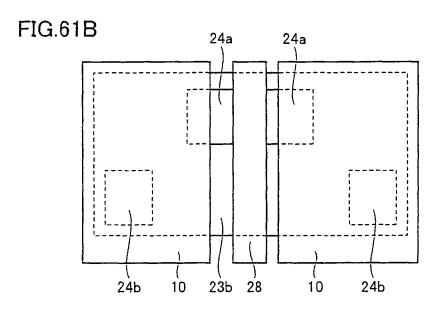

**[0059] Fig.** 61A und **Fig.** 61B zeigen schematische Draufsichten von Strukturen von Widerstandselementen von Halbleitervorrichtungen gemäß Abwandlungen des vierten Erläuterungsbeispiels sowie des neunten Ausführungsbeispieles der Erfindung.

**[0060] Fig.** 62 zeigt eine schematische Draufsicht einer Struktur einer Halbleitervorrichtung gemäß einem fünften Erläuterungsbeispiel.

**[0061] Fig.** 63 zeigt eine ausschnittartige Draufsicht, die schematisch einen Abschnitt zeigt, der durch LXIII in der **Fig.** 62 angegeben ist.

**[0062] Fig.** 64 zeigt eine ausschnittartige Draufsicht, die schematisch ein ebenes Layout nahe einem Widerstandselement einer Halbleitervorrichtung gemäß einem zehnten Ausführungsbeispiel der Erfindung zusammen mit Pfeilen zeigt, die schematisch Stromflußrichtungen angeben.

**[0063] Fig.** 65 zeigt eine ausschnittartige Draufsicht, die schematisch ein ebenes Layout nahe einem Widerstandselement einer Halbleitervorrichtung gemäß

einer Abwandlung des zehnten Ausführungsbeispieles der Erfindung zusammen mit Pfeilen zeigt, die schematisch Stromflußrichtungen angeben.

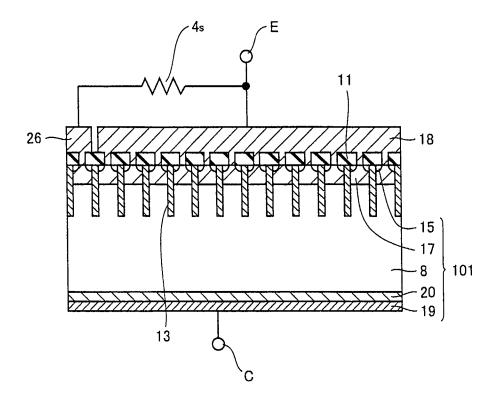

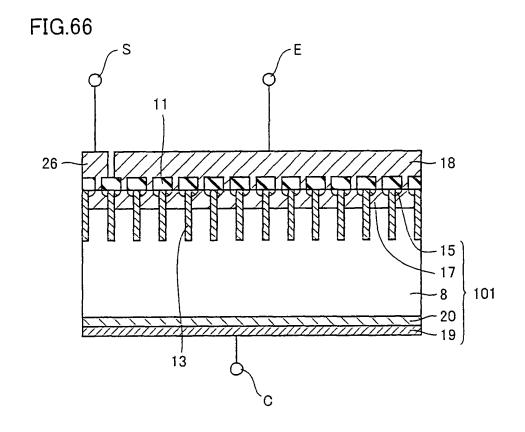

**[0064] Fig.** 66 zeigt einen schematischen Querschnitt einer Struktur einer Fühlerelektrode der Halbleitervorrichtung gemäß dem zehnten Ausführungsbeispiel der Erfindung.

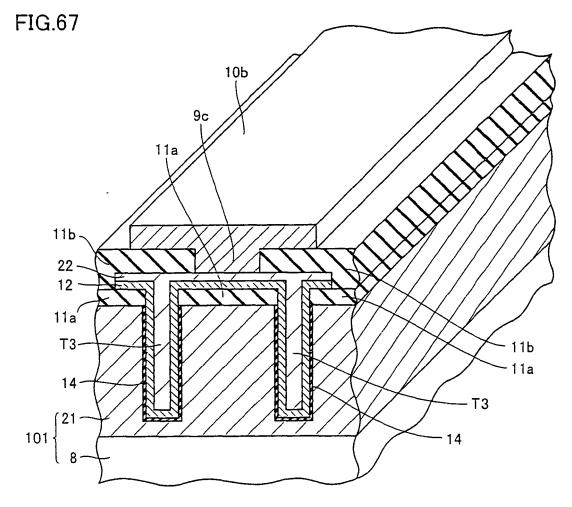

**[0065] Fig.** 67 zeigt schematisch und ausschnittartig eine perspektivische Ansicht eines Schnitts einer Struktur nahe einer Gatehauptzwischenverbindung einer Halbleitervorrichtung gemäß einem elften Ausführungsbeispiel der Erfindung.

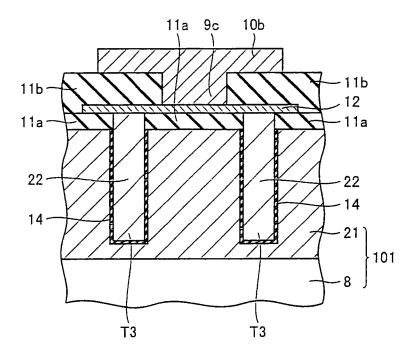

**[0066] Fig.** 68 zeigt einen ausschnittartigen Querschnitt, der schematisch eine Struktur nahe einer Gatehauptzwischenverbindung einer Halbleitervorrichtung gemäß einer ersten Abwandlung des elften Ausführungsbeispieles der Erfindung zeigt.

**[0067] Fig.** 69 zeigt einen ausschnittartigen Querschnitt, der schematisch eine Struktur nahe einer Gatehauptzwischenverbindung einer Halbleitervorrichtung gemäß einer zweiten Abwandlung des elften Ausführungsbeispieles der Erfindung zeigt.

# BESCHREIBUNG DER BEVORZUGTEN AUSFÜHRUNGSBEISPIELE

[0068] Ausführungsbeispiele der Erfindung werden unter Bezugnahme auf die Zeichnungen beschrieben.

[Erstes Erläuterungsbeispiel]

**[0069]** Zunächst wird eine schematische Struktur einer Halbleitervorrichtung eines ersten Erläuterungsbeispieles beschrieben.

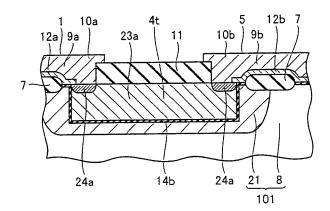

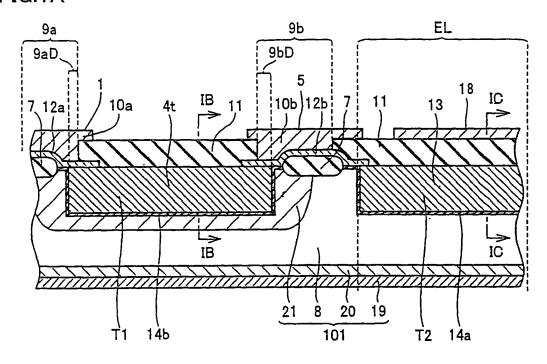

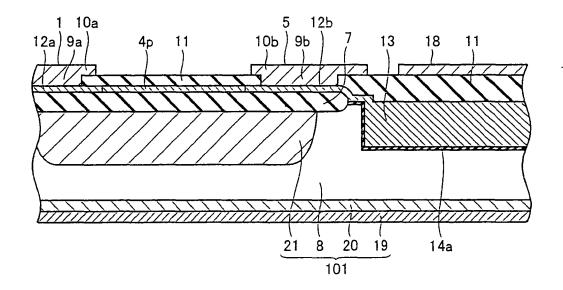

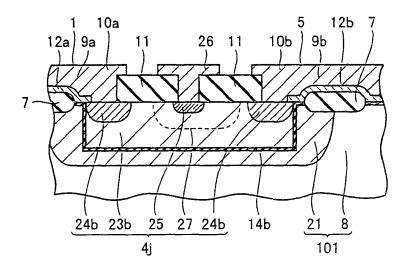

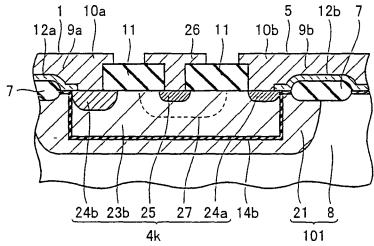

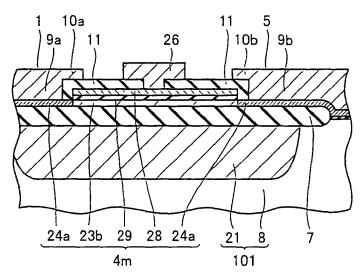

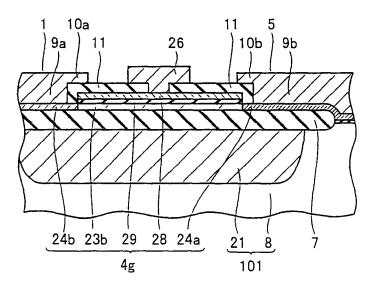

[0070] Unter Bezugnahme auf die Fig. 1A bis Fig. 1C ist ein IGBT-Chip von diesem Erläuterungsbeispiel eine Leistungshalbleitervorrichtung, und er hat ein IGBT-Element EL, das ein Grabengate-Halbleiterelement ist, und einen Innengatewiderstand 4t, der ein Widerstandselement ist.

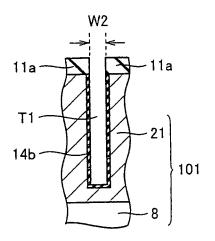

[0071] Unter Bezugnahme auf die Fig. 1A und Fig. 1B ist ein Graben-Innengatewiderstand 4t in einem ersten Graben T1 ausgebildet, der an einem Halbleitersubstrat 101 mit einem dazwischen liegenden Isolierfilm 14b ausgebildet ist. Dadurch ist der Graben-Innengatewiderstand 4t so konfiguriert, dass eine Schnittfläche von seinem Strompfad beim Vergrößern der Tiefe des ersten Grabens T1 vergrößert wird.

[0072] Unter Bezugnahme auf die Fig. 1A und Fig. 1C hat ein IGBT-Element EL einen Kanalbereich, der durch einen Teil des Halbleitersubstrates

**101** ausgebildet ist. Das IGBT-Element EL hat eine große Anzahl an Gateelektroden **13** zum Steuern des Kanalbereiches. Die Gateelektroden **13** haben zum Beispiel eine Anzahl von einigen Hundert bis einigen Zehntausend.

[0073] Unter Bezugnahme auf die Fig. 1A und Fig. 1C und Fig. 2 sind die Gateelektroden 13 der jeweiligen Zellen des IGBT-Elementes EL durch eine Gatehauptzwischenverbindung 5 elektrisch miteinander verbunden. Die Gatehauptzwischenverbindung 5 ist mit einem Randabschnitt eines Gateanschlusses 1 über den Graben-Innengatewiderstand 4t elektrisch verbunden.

[0074] Dadurch ist der IGBT-Chip so konfiguriert, dass er eine Eingabe, die für den Gateanschluss 1 vorgesehen ist, zu jeder Gateelektrode 13 des IGBT-Elementes EL über den Graben-Innengatewiderstand 4t überträgt. Somit ist der Graben-Innengatewiderstand 4t mit der Gateelektrode 13 derart elektrisch verbunden, dass der Graben-Innengatewiderstand 4t einen Widerstand (Gatewiderstand) für einen Strom bildet, der durch die Gateelektrode 13 hindurch strömt. Dieser Gatewiderstand hat hauptsächlich Funktionen zum Verzögern eines Potenzials, das zu der Gateelektrode 13 übertragen wird, und zum Einstellen eines Anstiegs eines Stroms/einer Spannung zur Zeit des Schaltens des IGBT-Elements EL.

[0075] Die Gatehauptzwischenverbindung 5 hat eine polykristalline Siliziumlage 12b, die aus n-leitendem, polykristallinem Silizium besteht, das ein Gatematerial ist, das stark mit Fremdatomen dotiert ist. Die Gatehauptzwischenverbindung 5 hat eine Hauptzwischenverbindungsmetallage 10b zum Reduzieren eines Widerstands der Zwischenverbindung. In einem Kontaktloch 9b an einer Seite der Hauptzwischenverbindung sind die polykristalline Siliziumlage 12b und die Hauptzwischenverbindungsmetallage 10b miteinander in Kontakt, und sie sind elektrisch miteinander verbunden.

**[0076]** Spezifische Strukturen der Halbleitervorrichtung des Erläuterungsbeispiels werden nun beschrieben.

[0077] Unter erneuter Bezugnahme auf die Fig. 1A hat der IGBT-Chip ein Halbleitersubstrat 101 als eine Basis. Der IGBT-Chip hat das IGBT-Element EL einschließlich eines Teils des Halbleitersubstrates 101. Der IGBT-Chip hat den Isolierfilm 14b, den Graben-Innengatewiderstand 4t, einen Feldoxidfilm 7, polykristalline Siliziumlagen 12a und 12b, einen Zwischenlagenisolierfilm 11, eine Gateanschlussmetallage 10a und die Hauptzwischenverbindungsmetallage 10b.

[0078] Der Feldoxidfilm 7 isoliert das Halbleitersubstrat 101 von den polykristallinen Siliziumlagen 12a

und **12b**, und er ist zum Beispiel durch ein LOCOS-Verfahren (Local Oxidation of Silicon) ausgebildet. Die Gateanschlussmetallage **10a** und die Hauptzwischenverbindungsmetallage **10b** bestehen zum Beispiel aus einem leitenden Material mit einem geringen Widerstand, wie zum Beispiel eine Aluminiumlegierung.

[0079] Unter hauptsächlicher Bezugnahme auf die Fig. 1A, Fig. 1B und Fig. 7 hat das Halbleitersubstrat 101 den ersten Graben T1, der eine Innenfläche aufweist, die durch den Isolierfilm 14b abgedeckt ist. Somit deckt der Isolierfilm 14b den Boden und Seitenflächen des ersten Grabens T1 ab. Der Isolierfilm 14b isoliert elektrisch das Halbleitersubstrat 101 von dem Graben-Innengatewiderstand 4t, der in dem ersten Graben T1 angeordnet ist.

[0080] Zum Beispiel hat der erste Graben T1 eine Tiefe (eine Längsgröße in der Fig. 1A) von ungefähr 10 μm und eine Breite (eine seitliche Größe in der Fig. 1B) von ungefähr 1,2 μm, und er ist so konfiguriert, dass sich viele der ersten Gräben T1 parallel mit einer Teilung von 2,5 μm erstrecken, wie dies in der Fig. 7 gezeigt ist. Der Isolierfilm 14b hat eine Filmdicke, die im Vergleich mit den Größen des ersten Grabens T1 klein ist, und sie ist zum Beispiel in einem Bereich von einigen 10 μm bis 200 μm.

[0081] Da keine komplizierte Struktur zwischen benachbarten Graben-Innengatewiderständen 4t vorhanden ist, kann die Teilung der Gräben (erste Gräben T1) für die Graben-Innengatewiderstände 4t kleiner sein als die Teilung der Gräben (zweite Gräben T2) für die Gateelektroden 13. Somit kann die Teilung der ersten Gräben T1 klein sein, und sie ist zum Beispiel ungefähr gleich 2,5 µm.

[0082] Der Graben-Innengatewiderstand 4t besteht aus einem Material, das als ein elektrischer Widerstand verwendet wird, es besteht zum Beispiel aus nleitendem, polykristallinem Silizium, das mit 1 ×  $10^{19}$ / cm³ oder höher stark dotiert ist. Der Graben-Innengatewiderstand 4t hat eine Breite, die zum Beispiel gleich einer Breite W1 (**Fig.** 6) der Gateelektrode 13 ist, und er hat eine Funktion zum Ausüben eines Widerstands für einen Strom, der in einer Längsrichtung (d. h. in der seitlichen Richtung in der **Fig.** 6) strömt. Der Graben-Innengatewiderstand 4t hat eine Tiefe (d. h. eine Größe in der Längsrichtung in den **Fig.** 1A und **Fig.** 1B) zum Beispiel in einem Bereich von 5 µm bis 20 µm.

[0083] Der Graben-Innengatewiderstand 4t hat einen Widerstandswert, der von der Größe des Grabens abhängt, der mit dem Graben-Innengatewiderstand 4t gefüllt ist, und er hängt außerdem von einer Dotierungskonzentration des n-leitenden, polykristallinen Siliziums ab, das den Graben füllt. Dieser Widerstandswert liegt in einem Bereich zum Beispiel

von einigen hunderten Ohm bis einigen Kilo Ohm pro 1 mm Länge des Graben-Innengatewiderstands **4t**.

[0084] Ein Graben-Innengatewiderstand 4t hat eine Wahrscheinlichkeit, dass ein Strom in einem Bereich von einigen zehn bis einigen hunderten Milliampere hindurch tritt. Ein Graben-Innengatewiderstand 4t hat einen Widerstandswert von 1 k $\Omega$  pro 1 mm Länge, und er hat eine Wahrscheinlichkeit, dass ein Strom bis zu 200 mA hindurch tritt. Der Widerstand von 8  $\Omega$ , der den Strom von bis zu 5 A durch läßt, kann dadurch erreicht werden, dass fünfundzwanzig Graben-Innengatewiderstände 4t verbunden werden, die parallel jeweils eine Länge von 200 µm aufweisen.

[0085] Unter Bezugnahme auf die Fig. 1A und Fig. 1B ist der Graben-Innengatewiderstand 4t, der den ersten Graben T1 füllt, mit dem Zwischenlagenisolierfilm 11 abgedeckt, der sich an einer Öffnungsseite des ersten Grabens T1 befindet. Der Zwischenlagenisolierfilm 11 ist mit einem Kontaktloch 9a an der Seite des Gateanschlusses und mit einem Kontaktloch 9b an der Seite der Hauptzwischenverbindung versehen.

[0086] In dem Kontaktloch 9a an der Seite des Gateanschlusses ist die Gateanschlussmetallage 10a mit dem Graben-Innengatewiderstand 4t über die polykristalline Siliziumlage 12a verbunden. In dem Kontaktloch 9b an der Seite der Hauptzwischenverbindung ist die Hauptzwischenverbindungsmetallage 10b mit dem Graben-Innengatewiderstand 4t über die polykristalline Siliziumlage 12b verbunden.

[0087] Unter Bezugnahme auf die Fig. 1A und Fig. 3 hat die Gateanschlussmetallage 10a eine obere Seite mit einer Funktion als ein Gateanschluss 1. Insbesondere ist die obere Seite der Gateanschlussmetallage 10a so konfiguriert, dass sie eine Verbindung zu einer äußeren Zwischenverbindung durch eine Drahtverbindung oder dergleichen ermöglicht. Die Hauptzwischenverbindungsmetallage 10b bildet zusammen mit der polykristallinen Siliziumlage 12b die Gatehauptzwischenverbindung 5.

[0088] Unter Bezugnahme auf die Fig. 1A ist in dem Bereich, in dem das IGBT-Element EL ausgebildet ist, der IGBT-Chip mit dem Halbleitersubstrat 101, einem Gateisolierfilm 14a, der Gateelektrode 13, der polykristallinen Siliziumlage 12b, dem Zwischenlagenisolierfilm 11 und einem Emitteranschluss 18 vorgesehen.

**[0089]** Unter Bezugnahme auf die **Fig.** 2 hat in einem Bereich, in dem der Emitteranschluss **18** ausgebildet ist, das IGBT-Element EL eine Struktur, die zum Beispiel aus einigen hundert bis einigen zehntausend Zellen ausgebildet ist. Jedes IGBT-Element EL hat eine Gateelektrode **13**.

[0090] Unter Bezugnahme auf die Fig. 1A, Fig. 1A und Fig. 7 hat das Halbleitersubstrat 101 einen nleitenden Emitterbereich 15, einen stark dotierten pleitenden Bereich 16, einen p-leitenden Kanalbereich 17, einen leicht dotierten n-leitenden Driftbereich 8, einen n-leitenden Pufferbereich 20 und einen p-leitenden Kollektorbereich 19.

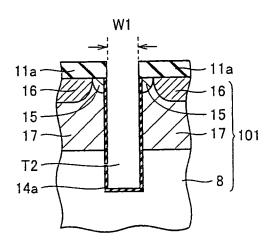

[0091] Das Halbleitersubstrat 101 hat einen zweiten Graben T2 mit einer Innenfläche, die durch den Gateisolierfilm 14a abgedeckt ist. Somit deckt der Gateisolierfilm 14a den Boden und Seitenflächen des zweiten Grabens T2 ab. Der Gateisolierfilm 14a isoliert elektrisch die Gateelektrode 13, die in dem zweiten Graben T2 angeordnet ist, von dem Halbleitersubstrat 101.

[0092] Zum Beispiel hat der zweite Graben T2 eine Tiefe (eine Größe in der Längsrichtung in der Fig. 1A) von ungefähr 10 μm und eine Breite (eine seitliche Größe in der Fig. 1C) von ungefähr 1,2 μm, und er ist so konfiguriert, dass die vielen zweiten Gräben T2 sich parallel mit einer Teilung von 5,0 μm erstrecken, wie dies in der Fig. 7 gezeigt ist. Der Gateisolierfilm 14a hat eine Filmdicke, die verglichen mit den Größen des zweiten Grabens T2 klein ist, und sie ist zum Beispiel in einem Bereich von einigen Mikrometern bis 200 Mikrometern. Die Gateelektrode 13 besteht zum Beispiel aus n-leitendem, polykristallinem Silizium, das mit 1 × 10¹9/cm³ oder mehr stark dotiert ist.

[0093] Unter Bezugnahme auf die Fig. 1A, Fig. 1A und Fig. 5 ist die Gateelektrode 13 mit der polykristallinen Siliziumlage 12b in Kontakt. Dadurch ist die Gateelektrode 13 mit der Gatehauptzwischenverbindung 5 verbunden.

**[0094]** Unter Bezugnahme auf die **Fig.** 1A und **Fig.** 1C ist die Gateelektrode **13**, die den zweiten Graben T2 füllt, mit dem Zwischenlagenisolierfilm **11** an der Öffnungsseite des zweiten Grabens T2 abgedeckt.

[0095] Unter Bezugnahme auf die Fig. 3 und Fig. 4 ist der Zwischenlagenisolierfilm 11 mit einem Emitter-kontaktloch 9d (d. h. ein Kontaktloch für einen Emitter) versehen, durch das der Emitteranschluss (Emitterelektrode) 18 mit dem n-leitenden Emitterbereich 15, dem stark dotierten, p-leitenden Bereich 16 und dem p-leitenden Kanalbereich 17 verbunden ist.

[0096] Bei der vorstehend beschriebenen Struktur, wie sie in der Fig. 1A gezeigt ist, hat das Kontaktloch 9a an der Seite des Gateanschlusses vorzugsweise einen Bereich, der sich mit einer Fläche des Graben-Innengatewiderstands 4t an der Öffnungsseite des ersten Grabens T1 überlappt. Somit hat der Zwischenlagenisolierfilm 11 ein Kontaktloch 9aD an der Seite des Gateanschlusses, das einen Teil des Kontaktloches 9a an der Seite des Gateanschlusses bil-

det und sich an der Öffnungsseite des ersten Grabens T1 des Graben-Innengatewiderstands **4t** befindet.

[0097] Das Kontaktloch 9b an der Seite der Hauptzwischenverbindung hat einen Bereich, der sich mit einer Fläche des Graben-Innengatewiderstands 4t an der Öffnungsseite des ersten Grabens T1 überlappt. Somit hat der Zwischenlagenisolierfilm 11 ein Kontaktloch 9bD an der Seite der Hauptzwischenverbindung, das einen Teil des Kontaktlochs 9b an der Seite der Hauptzwischenverbindung bildet und sich an der Öffnungsseite des ersten Grabens T1 des Graben-Innengatewiderstands 4t befindet.

[0098] Wie dies in den Fig. 1A und Fig. 2 gezeigt ist, isoliert der Zwischenlagenisolierfilm 11 den Gateanschluss 1 von der Gatehauptzwischenverbindung 5, und ein Strompfad zwischen dem Gateanschluss 1 und der Gateelektrode 13 wird im wesentlichen nur durch einen Strompfad gebildet, der sich durch den Graben-Innengatewiderstand 4t erstreckt. Der so gebildete Strompfad hat weder einen Strompfad, der durch eine Störkapazität oder durch eine Störinduktivität verursacht wird, noch einen kleinen Strompfad, der durch einen Isolator fließt.

[0099] Wie dies in den Fig. 1A bis Fig. 1C und Fig. 7 gezeigt ist, hat das Halbleitersubstrat 101 einen p-leitenden Bereich 21, der mit dem Isolierfilm in Kontakt ist und eine Leitfähigkeit aufweist, die entgegengesetzt zu jener des leicht dotierten n-leitenden Driftbereiches 8 des IGBT-Elementes EL ist. Insbesondere ist der p-leitende Bereich 21 mit Fremdatomen dotiert, um eine Leitfähigkeit zu erreichen, die entgegengesetzt zu jener des leicht dotierten n-leitenden Driftbereiches 8 ist, und die Konzentration dieser Fremdatome ist höher als jene der Fremdatome, mit denen der p-leitende Kanalbereich 17 des IGBT-Elementes EL dotiert ist, um die Leitfähigkeit zu erreichen, die entgegengesetzt zu jener des leicht dotierten n-leitenden Driftbereiches 8 ist.

[0100] Das Potenzial des p-leitenden Bereiches 21 wird so gesteuert, dass in dem p-leitenden Bereich 21 keine Inversionslage gebildet werden kann. Für diese Steuerung wird der p-leitende Bereich 21 zum Beispiel mit dem n-leitenden Emitterbereich 15 des IGBT-Elementes EL elektrisch verbunden.

**[0101]** Ein Verfahren zum Verwenden des IGBT-Chips gemäß dem Erläuterungsbeispiel wird nun beschrieben.

[0102] Unter Bezugnahme auf die Fig. 8 und Fig. 9 ist eine Schaltung 100 des IGBT-Chips zum Beispiel in einer Schaltung 200 einer Leiterplatte für den Gebrauch eingebaut. Die Leiterplatte hat einen äußeren Emitteranschluss 3e, einen äußeren Gateanschluss 3g und einen äußeren Kollektoranschluss 3c, die aus

einem leitenden Material mit einem niedrigen Widerstand wie zum Beispiel Gold bestehen.

**[0103]** Der Gateanschluss **1** des IGBT-Chips ist mit dem äußeren Gateanschluss **3g** der Leiterplatte über einen Draht **2a** verbunden, der aus Aluminium oder Gold besteht. Der Emitterbereich **15** (**Fig.** 1C) und p-leitende Kollektorbereich **19** (**Fig.** 1A) des IGBT-Chips sind mit dem äußeren Emitteranschluss **3e** bzw. dem äußeren Kollektoranschluss **3c** elektrisch verbunden. Ein Potenzial  $V_g$  wird auf den äußeren Gateanschluss **3g** extern aufgebracht.

[0104] In der Fig. 8 stellen Symbole von Kapazitäten und Spulen Störkapazitäten und Störinduktivitäten des IGBT-Chips dar. Pfeile in der Fig. 8 stellen Pfade dar, die die Abgaben von dem Kollektor und dem Emitter des IGBT-Elementes EL zu der Gateelektrode über die Störkapazitäten und Störinduktivitäten zurück führen.

**[0105]** Die Halbleitervorrichtung von diesem Erläuterungsbeispiel kann durch ein Verfahren hergestellt werden, das im wesentlichen gleich dem Verfahren für eine Halbleitervorrichtung eines zweiten Erläuterungsbeispieles ist, das später beschrieben wird, außer, dass ein Teil des Verfahrens bei dem ersten Erläuterungsbeispiel vereinfacht ist.

**[0106]** Eine Abwandlung der Struktur des Graben-Innengatewiderstands **4t** bei diesem Erläuterungsbeispiel wird nun beschrieben.

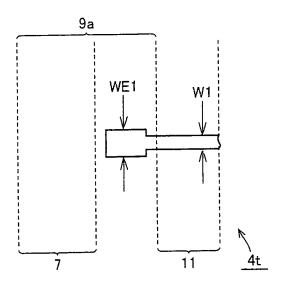

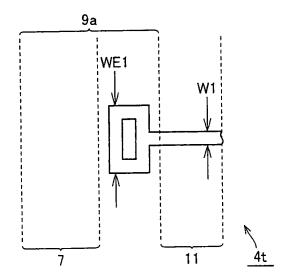

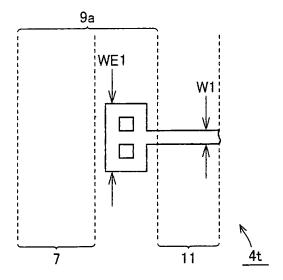

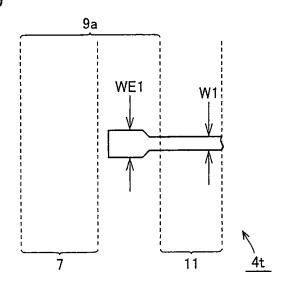

[0107] Unter Bezugnahme auf die Fig. 10 hat der Graben-Innengatewiderstand 4t einen Abschnitt, der gegenüber dem Kontaktloch 9a an der Seite des Gateanschlusses ist, und dieser Abschnitt hat eine Breite WE1, die größer ist als die Breit W1, die gleich einer minimalen Breite eines Abschnittes gegenüber dem Zwischenlagenisolierfilm 11 ist. Außerdem hat der Graben-Innengatewiderstand 4t einen Abschnitt gegenüber dem Kontaktloch 9b an der Seite der Hauptzwischenverbindung, und dieser Abschnitt hat eine Breite WE1, die größer ist als die Breite W1, d. h. die minimale Breite des Abschnittes gegenüber dem Zwischenlagenisolierfilm 11.

[0108] Bei dieser Abwandlung kann der Graben-Innengatewiderstand 4t eine andere Form haben, als sie in der Fig. 10 gezeigt ist, und zum Beispiel kann sie wahlweise Formen gemäß den Fig. 11 bis Fig. 15 haben. Auch wenn die Fig. 11 bis Fig. 15 Strukturen des Graben-Innengatewiderstands 4t nahe einem Abschnitt gegenüber dem Kontaktloch 9a an der Seite des Gateanschlusses zeigen, kann der Abschnitt gegenüber dem Kontaktloch 9b an der Seite der Hauptzwischenverbindung im wesentlichen die gleiche Struktur haben.

[0109] Ein erstes Vergleichsbeispiel wird nun beschrieben.

[0110] Zuerst wird eine Struktur einer Halbleitervorrichtung von diesem Vergleichsbeispiel beschrieben. Unter Bezugnahme auf die Fig. 16 hat ein IGBT-Chip, der die Halbleitervorrichtung von diesem Vergleichsbeispiel ist, einen Gateanschluss 1C und eine Gatehauptzwischenverbindung 5, die miteinander integriert sind. Da der Gateanschluss 1C und die Gatehauptzwischenverbindung 5 miteinander integriert sind, ist zwischen ihnen kein Widerstandselement vorhanden, das als ein Gatewiderstand dient.

**[0111]** Unter Bezugnahme auf die **Fig.** 17 wird ein äußerer Gatewiderstand **4e** als ein Teil oder als eine unabhängige Komponente des IGBT-Chips vorbereitet, und er wird mit dem äußeren Gateanschluss **3g** verbunden. Der äußere Gateanschluss **3g** wird extern mit einem Potenzial  $V_g$  über den äußeren Gatewiderstand **4e** versorgt, um das Potenzial der Gateelektrode zu steuern.

[0112] Unter Bezugnahme auf die Fig. 18 stellen Symbole von Kapazitäten und Spulen Störkapazitäten und Störinduktivitäten in einer Schaltung 100C des IGBT-Chips dar. Pfeile in der Fig. 18 stellen Pfade dar, die die Abgaben von dem Kollektor und dem Emitter des IGBT-Elementes EL zu der Gateelektrode über die Störkapazitäten und Störinduktivitäten zurück führen.

**[0113]** Der äußere Gatewiderstand **4e** ist nicht zwischen der Gateelektrode des IGBT-Elementes EL und dem äußeren Gateanschluss **3g** angeordnet. Somit ist kein äußerer Gatewiderstand **4e** an den Pfaden vorhanden, die die Abgaben von dem Kollektor und dem Emitter de IGBT-Elementes EL zu der Gateelektrode zurück führen.

[0114] Wenn daher das Potenzial des äußeren Gateanschlusses 3g aufgrund von äußeren Störgrößen geändert wird, wird diese Änderung des Potenzials direkt zu der Gateelektrode des IGBT-Elementes EL über die Störinduktivitäten übertragen. Folglich beeinträchtigen die Störgrößen wahrscheinlich die Gateelektrode.

**[0115]** Wenn die vorstehend beschriebene Änderung zu der Gateelektrode des IGBT-Elementes EL zurück kehrt, das als ein Verstärker arbeitet, und zwar über die Pfade, die durch die Pfeile in der Figur angegeben sind, erhöht sich ein Wert Q, der durch die folgende Gleichung dargestellt wird.

$$Q = \sqrt{\frac{C}{L}} \cdot \frac{1}{R}$$

**[0116]** Daher treten wahrscheinlich Schwingungen in einer Gate/Emitter-Spannung  $V_{\rm ge}$ , einer Kollektor/Emitter-Spannung  $V_{\rm ce}$ , einem Kollektorstrom  $I_{\rm c}$  und dergleichen auf. In der vorstehend genannten Formel gibt L eine Störinduktivität an, C gibt eine Störkapazität an und R gibt einen Gatewiderstand an.

[0117] Dann wird ein zweites Vergleichsbeispiel beschrieben.

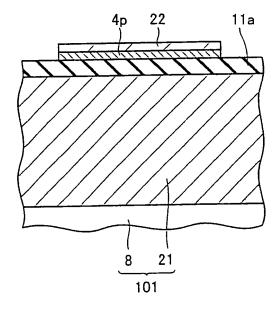

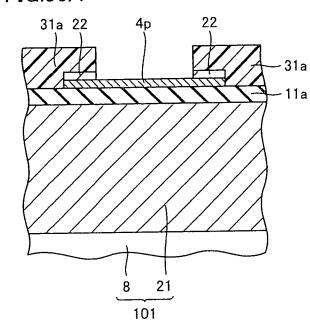

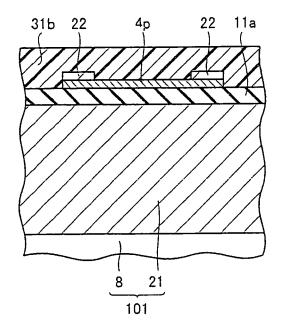

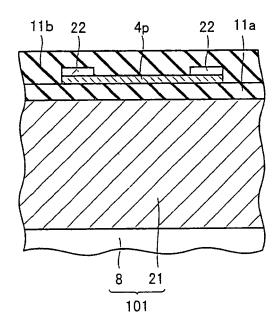

[0118] Unter Bezugnahme auf die Fig. 19 und Fig. 20 hat der IGBT-Chip, der die Halbleitervorrichtung von diesem Vergleichsbeispiel ist, einen ebenen Innengatewiderstand 4p, der sich zwischen dem Gateanschluss 1 und der Gatehauptzwischenverbindung befindet, und er dient als ein Gatewiderstand. Der ebene Innengatewiderstand 4p ist ein Widerstandselement einer ebenen Bauart, die an einem Feldoxidfilm 7 angeordnet ist, und er hat eine Fläche, die parallel zu der Substratfläche des Halbleitersubstrats 101 ist. Der ebene Innengatewiderstand 4p wird dadurch ausgebildet, dass ein polykristalliner Siliziumfilm mit einem Muster ausgebildet wird, der eine Filmdicke von zum Beispiel ungefähr einigen hunderten Nanometern hat.

[0119] Wenn Ströme den einigen hundert bis zehntausend Gateelektroden 13 des IGBT-Elementes EL zugeführt werden, muß der ebene Innengatewiderstand 4p zuverlässig einem großen Strom standhalten. Daher ist die Schnittfläche des Strompfades vergrößert, um einen übermäßigen Anstieg der Stromdichte zu verhindern. Zum Vergrößern der Schnittfläche ist es erforderlich, die Filmdicke (d. h. eine Größe in der Längsrichtung in der Fig. 20) des ebenen Innengatewiderstands 4p zu vergrößern oder die Breite (d. h. eine Größe in der Längsrichtung in der Fig. 19) davon zu vergrößern.

**[0120]** Zum Vergrößern der Filmdicke ist eine lange Prozeßzeit zur Filmbildung erforderlich. Zum Beispiel sind einige Stunden zum Ablagern des polykristallinen Siliziums mit einer Dicke von einigen hunderten Nanometern erforderlich, d. h. der Dicke des ebenen Innengatewiderstands **4p**, die üblicherweise verwendet wird. Zum Vergrößern der Filmdicke auf einige Mikrometer ist die Ablagerungszeit von einigen zehn Stunden erforderlich, und dies erhöht die Herstellungskosten. Wenn der polykristalline Siliziumfilm vergrößert wird, wird es schwierig, eine Fokustiefe bei einem Photogravurprozeß zur Musterbildung und zum Beseitigen von Resten in einem Schritt (d. h. ein Abschnitt mit einem unterschiedlichen Niveau) bei einem Ätzprozeß zu gewährleisten.

**[0121]** Wenn der ebene Innengatewiderstand **4p** eine große Breite hat, nimmt der ebene Innengatewiderstand **4p** eine große Fläche der Substratfläche des Halbleitersubstrat **101** ein, was zu einem Konflikt

mit einer Forderung zur Reduzierung der Größe der Halbleitervorrichtung führt.

[0122] Unter Bezugnahme auf die Fig. 20 hat der Feldoxidfilm 7, der unter dem ebenen Innengatewiderstand 4p angeordnet ist, üblicherweise eine Dicke von ungefähr 1 µm oder mehr. Da der Feldoxidfilm 7 eine niedrige thermische Leitfähigkeit hat, da er ein Oxidfilm ist, wird somit eine Filmdicke mit einer kleinen thermischen Leitfähigkeit unter dem ebenen Innengatewiderstand 4p ausgebildet. Diese Struktur verhindert eine Wärmeabstrahlung von dem ebenen Innengatewiderstand 4p, und eine Temperatur des ebenen Innengatewiderstands 4p wird angehoben, so dass sich der Widerstandswert wahrscheinlich aufgrund einer Temperaturabhängigkeit ändert.

[0123] Gemäß dem Erläuterungsbeispiel ist die Gateelektrode 13 des IGBT-Elementes EL mit dem Graben-Innengatewiderstand 4t elektrische verbunden. Dadurch kann der Graben-Innengatewiderstand 4t als ein Gatewiderstand der Gateelektrode 13 dienen

[0124] Wie dies in den Fig. 1A und Fig. 1B gezeigt ist, ist der Graben-Innengatewiderstand 4t in einem ersten Graben T1 angeordnet. Durch Vergrößern der Tiefe des ersten Grabens T1 ist es daher möglich, die Größe in der Tiefenrichtung des Graben-Innengatewiderstands 4t zu vergrößern. Daher ist es möglich, die Stromdichte des Graben-Innengatewiderstands 4t zu reduzieren, während eine kleine Anschlussfläche (eine Fläche in der Fig. 6) des Graben-Innengatewiderstands 4t an der Substratfläche des Halbleitersubstrats 101 aufrecht erhalten wird, und die Zuverlässigkeit des Graben-Innengatewiderstands 4t kann erhöht werden.

[0125] Wie dies in der Fig. 8 gezeigt ist, ist der Gateanschluss 1 mit der Gateelektrode 13 über den Graben-Innengatewiderstand 4t verbunden. Daher werden die Änderungen des Potenzials, die durch Störgrößen verursacht werden, die auf den Gateanschluss 1 und den äußeren Gateanschluss 3g aufgebracht werden, der mit dem Gateanschluss 1 verbunden ist, durch den Graben-Innengatewiderstand 4t unterdrückt, wenn derartige Potenzialänderungen zu der Gateelektrode 13 übertragen werden.

**[0126]** Vorzugsweise ist ein Strompfad zwischen dem Gateanschluss **1** und der Gateelektrode **13** im wesentlichen nur durch einen Strompfad gebildet, der sich durch den Graben-Innengatewiderstand **4t** hindurch erstreckt. Daher ist kein Strompfad vorhanden, der den Graben-Innengatewiderstand **4t** umgeht, und es ist möglich, ein Absenken des wesentlichen Gatewiderstands und einen Fehler des IGBT-Chips aufgrund eines derartigen umgehenden Strompfades zu verhindern.

[0127] Wie dies in der Fig. 1A gezeigt ist, hat der Zwischenlagenisolierfilm 11 ein Kontaktloch 9aD an der Seite des Gateanschlusses an der Öffnungsseite des ersten Grabens T1 des Graben-Innengatewiderstands 4t. Diese Struktur gewährleistet einen breiten elektrischen Pfad zwischen dem Gateanschluss 1 und dem Graben-Innengatewiderstand 4t, und sie kann eine Verschlechterung der Zuverlässigkeit aufgrund einer Stromkonzentration verhindern.

[0128] Wie dies in der Fig. 1A gezeigt ist, hat der Zwischenlagenisolierfilm 11 ein Kontaktloch 9bD an der Seite der Hauptzwischenverbindung, das sich an der Öffnungsseite des ersten Grabens T1 und an der Öffnungsseite des ersten Grabens T1 des Graben-Innengatewiderstands 4t befindet. Dies gewährleistet einen breiten elektrischen Pfad zwischen der Gatehauptzwischenverbindung 5 und dem Graben-Innengatewiderstand 4t, und es kann eine Verschlechterung der Zuverlässigkeit aufgrund einer Stromkonzentration verhindern.

[0129] Wie dies in den Fig. 1A und Fig. 1C gezeigt ist, kann die Gateelektrode 13 eine Grabengatestruktur haben, da die Gateelektrode 13 in dem zweiten Graben T2 angeordnet ist. Da der zweite Graben T2 gleichzeitig mit dem ersten Graben T1 ausgebildet werden kann, können die Prozeßkosten zum Bilden der Grabengates reduziert werden.

[0130] Wie dies in den Fig. 1A und Fig. 1B gezeigt ist, hat das Halbleitersubstrat 101 einen p-leitenden Bereich 21 mit einer Leitfähigkeit, die entgegengesetzt zu jener des leicht dotierten, n-leitenden Driftbereiches 8 des IGBT-Elementes EL ist. Diese Struktur kann eine Verschlechterung von Durchschlageigenschaften zwischen dem Kollektor und dem Emitter des IGBT-Elementes EL verhindern.

[0131] Vorzugsweise ist der p-leitende Bereich 21 mit Fremdatomen dotiert, um die Leitfähigkeit zu erreichen, die entgegengesetzt zu der Leitfähigkeit des leicht dotierten n-leitenden Driftbereiches 8 ist, und die Konzentration von diesem Fremdatomen ist höher als jene der Fremdatome, mit denen der p-leitende Kanalbereich 17 des IGBT-Elementes EL dotiert ist, um die Leitfähigkeit zu erreichen, die entgegengesetzt zu der Leitfähigkeit des leicht dotierten, n-leitenden Driftbereiches 8 ist. Dadurch kann der p-leitende Kanalbereich 17 zu der n-Leitfähigkeit invertiert werden, ohne dass der p-leitende Bereich 21 zu der n-Leitfähigkeit invertiert wird. Im Gegensatz zu dem zweiten Vergleichsbeispiel, bei dem der Feldoxidfilm 7 mit einer relativ großen Dicke von ungefähr 1 µm bis 2 µm zwischen dem Gatewiderstand und dem pleitenden Bereich 21 vorhanden ist, ist nur der dünne Isolierfilm 14b mit ungefähr einigen zehn Mikrometern bis 200 Mikrometer zwischen dem Gatewiderstand und dem p-leitenden Bereich 21 bei diesem Erläuterungsbeispiel vorhanden, und diese Struktur bewirkt relativ einfach die Umwandlung der Leitfähigkeit des p-leitenden Bereichs **21**. Daher kann die vorstehend beschriebene Festlegung der Konzentrationen der Fremdatome einen größeren Effekt erreichen.

**[0132]** Das Potenzial des p-leitenden Bereichs **21** wird gesteuert, um eine Bildung der Inversionslage in dem p-leitenden Bereich **21** zu verhindern. Für diese Steuerung wird der p-leitende Bereich **21** zum Beispiel mit dem n-leitenden Emitterbereich **15** des IGBT-Elementes EL elektrisch verbunden. Diese Struktur kann eine Verschlechterung von Auswahleigenschaften zwischen dem Kollektor und dem Emitter des IGBT-Elementes EL verhindern.

#### [Zweites Erläuterungsbeispiel]

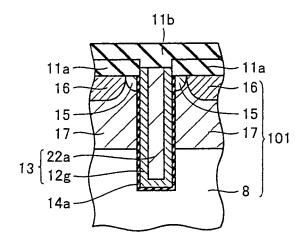

**[0133]** Zuerst wird eine Struktur eines IGBT-Chips beschrieben, der eine Halbleitervorrichtung eines zweiten Erläuterungsbeispieles ist.

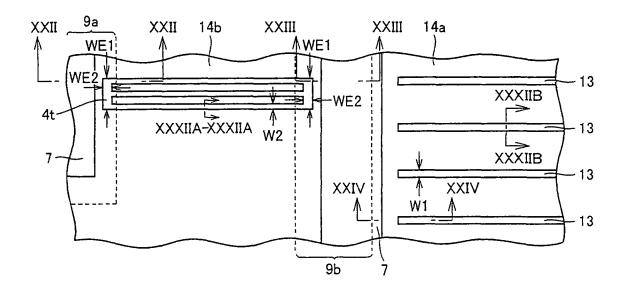

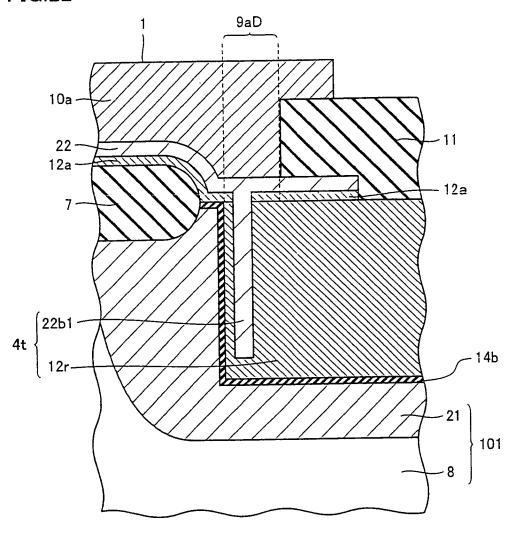

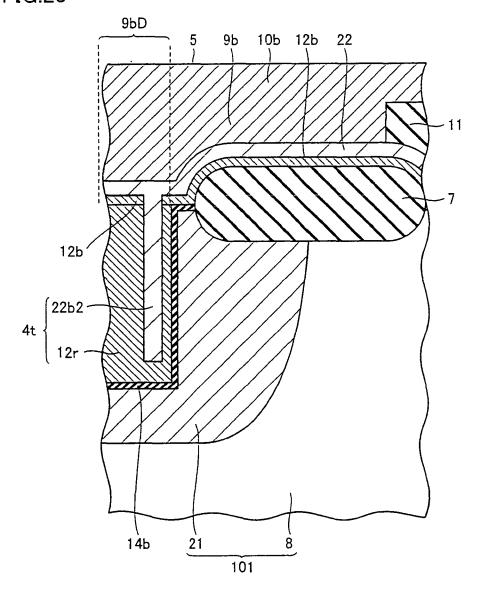

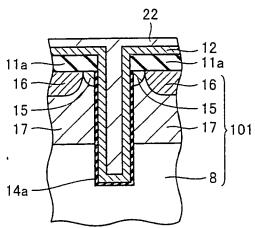

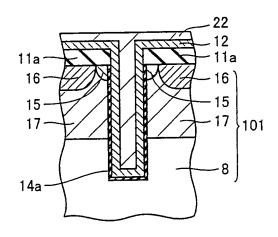

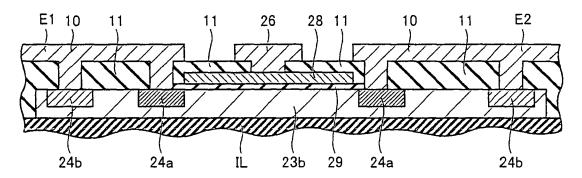

[0134] Unter Bezugnahme auf die Fig. 21 bis Fig. 24 hat der IGBT-Chip von diesem Erläuterungsbeispiel einen Metallabschnitt 22. Der Metallabschnitt 22 hat Metallabschnitte 22b1 und 22b2, die im Inneren des ersten Grabens T1 angeordnet sind, und einen Metallabschnitt 22a, der im Inneren des zweiten Grabens T2 angeordnet ist. Ein Material des Metallabschnitts 22 hat einen kleineren Widerstand als ein Halbleitermaterial wie zum Beispiel stark dotiertes, nleitendes polykristallines Silizium. Das Material der Metallabschnitte 22 ist zum Beispiel ein Metall mit einem hohen Schmelzpunkt wie zum Beispiel Wolfram, Titan, Platin oder Kupfer.

[0135] Unter Bezugnahme auf die Fig. 24 hat die Gateelektrode 13 eine polykristalline Siliziumlage 12g und einen Metallabschnitt 22a, der einen Raum im Inneren der polykristallinen Siliziumlage 12g füllt.

[0136] Unter Bezugnahme auf die Fig. 22 und Fig. 23 hat der Graben-Innengatewiderstand 4t einen eingebetteten Metallabschnitt 22b1 in einem Abschnitt gegenüber dem Kontaktloch 9aD an der Seite des Gateanschlusses. Außerdem hat der Graben-Innengatewiderstand 4t einen eingebetteten Metallabschnitt 22b2 in einem Abschnitt gegenüber dem Kontaktloch 9bD an der Seite der Hauptzwischenverbindung.

[0137] Der Abschnitt des Graben-Innengatewiderstands 4t außer den eingebetteten Metallabschnitten 22b1 und 22b2 ist aus einer polykristallinen Siliziumlage 12r ausgebildet. Die eingebetteten Metallabschnitte 22b1 und 22b2 sind über die polykristalline Siliziumlage 12r elektrisch miteinander verbunden.

**[0138]** Hauptsächlich unter Bezugnahme auf die **Fig.** 21 befindet sich der Zwischenlagenisolierfilm **11** (**Fig.** 23 und **Fig.** 24), der an dem Graben-Innengate-

widerstand **4t** angeordnet ist, zwischen dem Kontaktloch **9a** an der Seite des Gateanschlusses und dem Kontaktloch **9b** an der Seite der Hauptzwischenverbindung, was durch gestrichelte Linien dargestellt ist. Der Abschnitt des Graben-Innengatewiderstands **4t** gegenüber dem Zwischenlagenisolierfilm **11** hat eine minimale Breite W2. Die **Fig.** 21 zeigt anhand eines Beispiels eine Struktur, bei der der Abschnitt des Graben-Innengatewiderstands **4t** gegenüber dem Zwischenlagenisolierfilm **11** eine konstante Breite W2 hat.

[0139] Der Graben-Innengatewiderstand 4t hat einen Abschnitt, der dem Kontaktloch 9a an der Seite des Gateanschlusses gegenüber liegt, und dieser Abschnitt hat eine Breite WE1, die größer ist als die Breite W2. Dieser Abschnitt mit der großen Breite WE1 hat eine Länge WE2, die größer ist als die Breite W2.

**[0140]** Unter Bezugnahme auf die **Fig.** 22 befindet sich der Abschnitt mit der Breite W2 unter dem Zwischenlagenisolierfilm **11**, und er ist aus der polykristallinen Siliziumlage **12r** ausgebildet. Der Abschnitt mit der Breite WE1 beinhaltet den Metallabschnitt **22b1** mit einem geringeren Widerstand als die polykristalline Siliziumlage **12r**.

**[0141]** Der Graben-Innengatewiderstand **4t** hat einen Abschnitt, der dem Kontaktloch **9b** an der Seite der Hauptzwischenverbindung gegenüber liegt, und dieser Abschnitt hat eine Breite WE1, die größer ist als die Breit W2. Dieser Abschnitt mit der großen Breite WE1 hat eine Länge WE2, die größer ist als die Breite W2.

**[0142]** Unter Bezugnahme auf die **Fig.** 23 hat der Abschnitt mit der Breite WE1 den Metallabschnitt **22b2**, der einen geringeren Widerstand als die polykristalline Siliziumlage **12r** hat.

[0143] Unter Bezugnahme auf die Fig. 21 hat die Gateelektrode 13 die maximale Breite (d. h. die Größe in der Längsrichtung in der Fig. 21), die gleich der Breite W1 ist. Diese Breite W1 ist größer als die Breite W2. Die Fig. 21 zeigt anhand eines Beispiels eine Struktur, bei der die Gateelektrode 13 eine konstante Breite W1 hat.

**[0144]** Unter Bezugnahme auf die **Fig.** 24 hat der Abschnitt der Gateelektrode **13** mit der Breite W1 den Metallabschnitt **22a** mit einem geringeren Widerstand als die polykristalline Siliziumlage **12g**.

**[0145]** Strukturen außer den vorstehend beschriebenen sind im wesentlichen gleich wie bei dem ersten Erläuterungsbeispiel. Daher tragen die gleichen oder entsprechenden Elemente die gleichen Bezugszeichen, und deren Beschreibung wird nicht wiederholt.

**[0146]** Eine Abwandlung der Struktur des Graben-Innengatewiderstands **4t** gemäß diesem Erläuterungsbeispiel wird nun beschrieben.

[0147] Die Fig. 25 und Fig. 26 zeigen ausschnittartige Draufsichten, die schematisch eine erste und eine zweite Abwandlung der Halbleitervorrichtung des zweiten Erläuterungsbeispieles zeigen, und insbesondere zeigen sie Strukturen der Widerstandselemente mit den darin eingebetteten Metallabschnitten. Gestrichelte Linien in den Fig. 25 und Fig. 26 stellen ungefähre Positionsbeziehungen des Widerstandselementes hinsichtlich des Feldoxidfilms, des Kontaktloches an der Seite des Gateanschlusses und des Zwischenlagenisolierfilms dar.

[0148] Unter Bezugnahme auf die Fig. 25 hat der Graben-Innengatewiderstand 4t bei der ersten Abwandlung einen Abschnitt, der gegenüber dem Kontaktloch 9a an der Seite des Gateanschlusses liegt, und dieser Abschnitt hat eine Breite WE1, die größer ist als die Breite W2. Der Abschnitt mit der Breite WE1 hat einen Abschnitt mit einer Länge WE2, die größer ist als die Breite W2. Der Abschnitt mit der Breite WE1 des Graben-Innengatewiderstands 4t hat einen eingebetteten Metallabschnitt 22b1.

[0149] Unter Bezugnahme auf die Fig. 26 hat der Graben-Innengatewiderstand 4t bei der zweiten Abwandlung viele Abschnitte, die dem Kontaktloch 9a an der Seite des Gateanschlusses gegenüber liegen, und die jeweils eine Breite WE1 haben, die größer ist als die Breite W2. Jeder Abschnitt mit der Breite WE1 hat einen Abschnitt mit einer Länge WE2, die größer ist als die Breite W2. Jeder Abschnitt mit der Breite WE1 des Graben-Innengatewiderstands 4t hat einen eingebetteten Metallabschnitt 22b1.

**[0150]** Die erste und die zweite Abwandlung wurden im Zusammenhang mit den Strukturen beschrieben, bei denen ein Teil des Metallabschnitts **22** in dem Abschnitt eingebettet ist, der dem Kontaktloch **9a** an der Seite des Gateanschlusses gegenüber liegt. Der Abschnitt gegenüber dem Kontaktloch **9b** an der Seite der Hauptzwischenverbindung kann im wesentlichen die gleiche Struktur haben, wie sie vorstehend beschrieben ist.

**[0151]** Ein Verfahren zum Herstellen der Halbleitervorrichtung von diesem Erläuterungsbeispiel wird nun beschrieben.

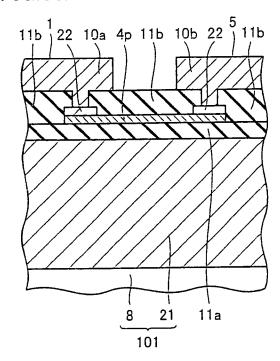

**[0152]** Unter Bezugnahme auf die **Fig.** 27A und **Fig.** 27B wird ein Zwischenlagenisolierfilm **11a**, der aus einem Siliziumoxidfilm oder dergleichen besteht, an dem Halbleitersubstrat **101** abgelagert. Der Zwischenlagenisolierfilm **11a** wird einen Teil des Zwischenlagenisolierfilms **11** bilden.

**[0153]** Der Zwischenlagenisolierfilm **11a** ist als ein Muster durch das Photogravurverfahren ausgebildet. Der gemusterte Zwischenlagenisolierfilm **11a** wird als eine Maske verwendet, und ein Ätzen wird an dem Halbleitersubstrat **101** bewirkt, um den ersten und den zweiten Graben T1 und T2 auszubilden. Die Zwischenlagenisolierfilme **14b** und **14a** werden durch Oxidation, Ablagerung und dergleichen an den inneren Flächen des ersten bzw. zweiten Grabens T1 und T2 ausgebildet.

**[0154]** Dadurch wird der erste Graben T1 mit der Breite W2 ausgebildet, der durch den Isolierfilm **14b** abgedeckt ist. Außerdem wird der zweite Graben T2 mit der Breite W1 ausgebildet, der durch den Gateisolierfilm **14a** abgedeckt ist.

[0155] Hauptsächlich unter Bezugnahme auf die Fig. 28A und Fig. 28B wird eine polykristalline Siliziumlage 12, die stark mit Fremdatomen dotiert ist, an dem Halbleitersubstrat 101 abgelagert. Die abgelagerte polykristalline Siliziumlage 12 füllt vollständig einen Abschnitt mit der Breite W2 (Fig. 27A) des ersten Grabens T1. Der Abschnitt mit der Breite WE1 des ersten Grabens T1 (d. h. ein Abschnitt gegenüber dem Kontaktloch 9aD an der Seite des Gateanschlusses in der Fig. 22) wird nur teilweise gefüllt. Wie dies in der Fig. 28B gezeigt ist, wird der zweite Graben T2 nur teilweise gefüllt.

**[0156]** Unter Bezugnahme auf die **Fig.** 29A und **Fig.** 29B wird der Metallabschnitt **22**, der aus einem Metall mit einem hohen Schmelzpunkt oder dergleichen besteht, an der polykristallinen Siliziumlage **12** an dem Halbleitersubstrat **101** abgelagert. Dies füllt vollständig einen partiellen Raum, der in dem Abschnitt mit der Breite WE1 des ersten Grabens T1 verbleibt (d. h. in dem Abschnitt gegenüber dem Kontaktloch **9aD** an der Seite des Gateanschlusses in der **Fig.** 22).

[0157] Außerdem wird der zweite Graben T2 vollständig gefüllt, wie dies in der Fig. 29B gezeigt ist.

[0158] Dann werden der Metallabschnitt 22 und die polykristalline Siliziumlage 12 nacheinander zurück geätzt.

**[0159]** Unter Bezugnahme auf die **Fig.** 30A und **Fig.** 30B legt die vorstehend beschriebene Rückätzung den Zwischenlagenisolierfilm **11a** frei.

**[0160]** Unter Bezugnahme auf die **Fig.** 31A und **Fig.** 31B wird ein Zwischenlagenisolierfilm **11b** an dem Halbleitersubstrat **101** ausgebildet. Zum Beispiel wird bei einem Verfahren für diese Ausbildung ein BPSG-Film (Boron-Phospho-Silicate-Glass) abgelagert, und er wird einer Wärmebehandlung ausgesetzt, um die Oberfläche des Isolierfilms abzuflachen.

Der Zwischenlagenisolierfilm **11b** wird einen Teil des Zwischenlagenisolierfilms **11** bilden.

**[0161]** Unter Bezugnahme auf die **Fig.** 32A und **Fig.** 32B werden die Zwischenlagenisolierfilme **11a** und **11b** wahlweise beseitigt, um das Emitterkontaktloch **9d**, das Kontaktloch **9a** an der Seite des Gateanschlusses (**Fig.** 21) und das Kontaktloch **9b** an der Seite der Hauptzwischenverbindung (**Fig.** 21) auszuhilden

[0162] Dann wird ein Metallfilm, der aus einem Elektrodenmaterial wie zum Beispiel Aluminium oder eine Zusammensetzung davon besteht, abgelagert und als Muster ausgebildet, um den Emitteranschluss 18, die Gateanschlussmetallage 10a (Fig. 22) und die Hauptzwischenverbindungsmetallage 10b (Fig. 23 und Fig. 24) auszubilden.

**[0163]** Durch die vorstehend beschriebene Verarbeitung wird der IGBT-Chip ausgebildet, der die Halbleitervorrichtung des Erläuterungsbeispieles ist.

**[0164]** Der Schritt zum Ausbilden des n-leitenden Emitterbereiches **15**, des stark dotierten, p-leitenden Bereiches **16**, des p-leitenden Kanalbereiches **17** und dergleichen an dem Halbleitersubstrat **101** kann entweder vor oder nach dem Schritt zum Ausbilden des ersten und des zweiten Grabens T1 und T2 ausgeführt werden.

**[0165]** Dann wird ein Verfahren zum Herstellen der Halbleitervorrichtung des dritten Vergleichsbeispiels beschrieben. Die Struktur von diesem Vergleichsbeispiel unterscheidet sich von dem zweiten Vergleichsbeispiel darin, dass der Metallabschnitt **22** hinzugefügt wird.

[0166] Unter Bezugnahme auf die Fig. 33A und Fig. 33B werden Schritte durchgeführt, die ähnlich den Schritten zum Ausbilden der Strukturen in den Fig. 29A und Fig. 29B sind, aber der erste Graben T1 wird im Gegensatz zu diesem Erläuterungsbeispiel nicht ausgebildet. Wie dies in der Fig. 33A gezeigt ist, wird folglich ein ebener Innengatewiderstand 4p entlang einer ebenen Substratfläche des Halbleitersubstrats 101 anstelle des Graben-Innengatewiderstands 4t von diesem Erläuterungsbeispiel ausgebildet.

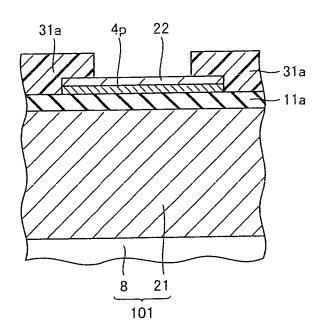

[0167] Unter Bezugnahme auf die Fig. 34A und Fig. 34B wird ein Photolack 31a auf das Halbleitersubstrat 101 aufgebracht. Wie dies in der Fig. 34A gezeigt ist, wird der Photolack 31a durch das Photogravurverfahren gemustert. Dadurch wird der Metallabschnitt 22 teilweise an dem ebenen Innengatewiderstand 4p freigelegt.

[0168] Unter Bezugnahme auf die Fig. 35A und Fig. 35B wird ein Ätzen an einem Abschnitt des Me-

tallabschnitts **22** bewirkt, der nicht durch den Photolack **31a** abgedeckt ist. Dies teilt den Metallabschnitt **22** in viele Bereiche, wie dies in der **Fig.** 35A gezeigt ist. Danach wird der Photolack **31a** beseitigt.

[0169] Hauptsächlich unter Bezugnahme auf die Fig. 36A und Fig. 36B wird der Photolack 31b auf das Halbleitersubstrat 101 aufgebracht. Der Photolack 31b wird durch das Photogravurverfahren so gemustert, dass der Photolack 31b einen Bereich abdeckt, in dem der ebene Innengatewiderstand 4p ausgebildet wird, und er legt einen Abschnitt nahe der Gateelektrode 13 frei. Ein Rückätzen wird nachfolgend an dem Metallabschnitt 22 und der polykristallinen Siliziumlage 12 (Fig. 35B) bewirkt, um den Zwischenlagenisolierfilm 11a in jenem Bereich freizulegen, der durch den Photolack 31b nicht maskiert ist. Danach wird der Photolack 31b beseitigt.

[0170] Unter Bezugnahme auf die Fig. 37A und Fig. 37B wird der Zwischenlagenisolierfilm 11b an dem Halbleitersubstrat 101 ausgebildet. Zum Beispiel wird bei einem Verfahren zu dieser Ausbildung ein BPSG-Film (Boron-Phospho-Silicate-Glass) abgelagert und einer Wärmebehandlung ausgesetzt, um die Oberfläche des Isolierfilms abzuflachen.

[0171] Unter Bezugnahme auf die Fig. 38A und Fig. 38B werden wahlweise die Zwischenlagenisolierfilme 11a und 11b geätzt. Dadurch werden Kontaktlöcher wie zum Beispiel das Emitterkontaktloch 9d ausgebildet. Dann werden der Emitteranschluss 18, die Gateanschlussmetallage 10a und die Hauptzwischenverbindungsmetallage 10b ausgebildet.

[0172] Durch die vorstehend genannten Schritte wird die Halbleitervorrichtung von diesem Vergleichsbeispiel ausgebildet. Das Verfahren zum Herstellen der Halbleitervorrichtung von diesem Vergleichsbeispiel erfordert die Schritte, die in den Fig. 34A und Fig. 34B sowie in den Fig. 35A und Fig. 35B gezeigt sind, um den Metallabschnitt 22 zu ätzen, der mit dem Photolack 31a maskiert ist, und somit erfordert es komplizierte Schritte.

**[0173]** Des weiteren ändert sich bei dem Ätzprozeß zum Beseitigen des Metallabschnitts **22** die Filmdicke des ebenen Innengatewiderstands **4p** aufgrund von Änderungen beim Überätzen. Dies führt zu Änderungen des Widerstandswerts des ebenen Innengatewiderstands **4p**, der als der Gatewiderstand dient.

[0174] Bei diesem Erläuterungsbeispiel hat der Abschnitt des Graben-Innengatewiderstands 4t mit der Breite WE1 (Fig. 21) den Metallabschnitt 22b1 in der Position, die dem Kontaktloch 9aD an der Seite des Gateanschlusses gegenüber liegt, und zwar zusätzlich zu der polykristallinen Siliziumlage 12r, wie dies in der Fig. 22 gezeigt ist. Dieser Metallabschnitt 22b1 hat einen geringeren Widerstand als die polykristalli-

ne Siliziumlage **12r**. Diese Struktur schwächt eine örtliche Konzentration des Stroms zwischen dem Gateanschluss **1** und dem Graben-Innengatewiderstand **4t** ab und erhöht die Zuverlässigkeit des IBGT-Chips.

[0175] Der Abschnitt des Graben-Innengatewiderstands 4t mit der Breite WE1 (Fig. 21) hat den Metallabschnitt 22b2 in der Position gegenüber dem Kontaktloch 9bD an der Seite der Hauptzwischenverbindung zusätzlich zu der polykristallinen Siliziumlage 12r, wie dies in der Fig. 23 gezeigt ist. Dieser Metallabschnitt 22b2 hat einen geringeren Widerstand als die polykristalline Siliziumlage 12r. Diese Struktur schwächt eine örtliche Konzentration des Stroms zwischen der Gatehauptzwischenverbindung 5 und dem Graben-Innengatewiderstand 4t ab und erhöht die Zuverlässigkeit des IGBT-Chips.

[0176] Wie dies in der Fig. 21 gezeigt ist, hat die Gateelektrode 13 eine Breite W1, die größer ist als die Breite W2 des Graben-Innengatewiderstands 4t. Wie dies in den Fig. 27A und Fig. 27B gezeigt ist, ist somit eine Breite W1 des Grabens zum Ausbilden der Gateelektrode 13 größer als die Breite W2 des Grabens zum Ausbilden des Graben-Innengatewiderstands 4t. Daher können derartige Zustände gleichzeitig erreicht werden, dass der Graben mit der Breite W2 vollständig durch die polykristalline Siliziumlage 12 gefüllt ist und dass der Abschnitt mit der Breite W1 nicht vollständig gefüllt ist. Wie dies in der Fig. 30 gezeigt ist, kann daher der Metallabschnitt 22a in jenem Abschnitt angeordnet sein, der nicht mit der polykristallinen Siliziumlage gefüllt ist.

**[0177]** Wie dies vorstehend beschrieben ist, ist der Graben mit der Breite W2 vollständig mit der polykristallinen Siliziumlage **12** mit einem relativ hohen Widerstand gefüllt, so dass der Graben-Innengatewiderstand **4t** mit einem ausreichend hohen Widerstandswert erreicht werden kann.

[0178] Des weiteren hat die Gateelektrode 13 den Metallabschnitt 22a mit einem geringeren Widerstand als die polykristalline Siliziumlage 12, so dass der elektrische Widerstand der Gateelektrode 13 reduziert werden kann. Dadurch können die Änderungen der Übertragungsverzögerung der Gatepotentiale in den Gateelektroden reduziert werden. Dies reduziert eine Zeit, in der ein Ein-Bereich und ein Aus-Bereich gleichzeitig bei dem Schaltbetrieb des IGBT-Elementes EL vorhanden sind. Daher ist es möglich, die Zeit zu verkürzen, in der der Strom, der zwischen dem Kollektor und dem Emitter des IGBT-Elementes EL strömt, an einem Teil der Ein-Bereiche konzentriert wird. Dementsprechend kann eine örtliche Erwärmung in einem Teil der Ein-Bereiche unterdrückt werden, so dass der IGBT-Chip eine verbesserte Zuverlässigkeit haben kann.

[Erstes Ausführungsbeispiel]

**[0179]** Zuerst wird eine Struktur eines IGBT-Chips beschrieben, der eine Halbleitervorrichtung eines ersten Ausführungsbeispieles ist.

[0180] Unter Bezugnahme auf die Fig. 39 hat der Graben-Innengatewiderstand 4t, der ein Widerstandselement der Halbleitervorrichtung von diesem Ausführungsbeispiel ist, als ein Hauptelement eine n-leitende, leicht dotierte polykristalline Siliziumlage 23a. Der Graben-Innengatewiderstand 4t hat eine n-leitende, stark dotierte polykristalline Siliziumlage 24a, die sich in Abschnitten befindet, die mit dem Kontaktloch 9a an der Seite des Gateanschlusses und dem Kontaktloch 9b an der Seite der Hauptzwischenverbindung in Kontakt sind.

[0181] Die Halbleitervorrichtung von diesem Ausführungsbeispiel unterscheidet sich von dem ersten und dem zweiten Erläuterungsbeispiel darin, dass ein Hauptabschnitt der eingebetteten Substanz des Graben-Innengatewiderstands 4t die polykristallinen Siliziumlagen mit einer Konzentration sind, die kleiner ist als bei dem ersten und dem zweiten Erläuterungsbeispiel, und dass die Potenzialdifferenz zwischen dem Graben-Innengatewiderstand 4t und dem p-leitenden Bereich 21, der mit ihm in Kontakt ist, so eingestellt werden kann, dass die n-leitende leicht dotierte polykristalline Siliziumlage 23a zumindest zwei Zustände von einem Akkumulationszustand, einem Sperrzustand und einem Inversionszustand erreichen kann.

**[0182]** Strukturen außer den vorstehend beschriebenen sind im wesentlichen gleich wie bei dem ersten Erläuterungsbeispiel, das bereits beschrieben wurde. Daher tragen die gleichen oder entsprechenden Elemente die gleichen Bezugszeichen, und deren Beschreibung wird nicht wiederholt.

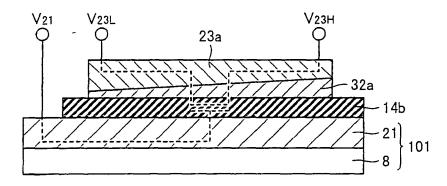

**[0183]** Ein Betrieb des Widerstandselements bei der Halbleitervorrichtung von diesem Ausführungsbeispiel wird nun beschrieben. Unter Bezugnahme auf die **Fig.** 43 und **Fig.** 45 geben  $V_{23H}$  und  $V_{23L}$  Potenziale an den entgegengesetzten Enden des Strompfads der n-leitenden, leicht dotierten polykristallinen Siliziumlage **23a** an.  $V_{21}$  gibt das Potenzial an der Seite des Isolierfilms **14b** des Halbleitersubstrats **101** an, und es gibt das Potenzial des p-leitenden Bereiches **21** an, wenn der p-leitende Bereich **21** bei dem Halbleitersubstrat **101** verwendet wird.

**[0184]** Unter Bezugnahme auf die **Fig.** 43, wenn  $V_{21}$  ( $V_{21} > V_{23L} >> V_{23H}$ ) erfüllt, ist die n-leitende, leicht dotierte polykristalline Siliziumlage **23a** in dem Akkumulationszustand. Somit wird eine Akkumulationslage **32a** durch Elektronen an der Fläche an der Seite des Isolierfilms **14b** der n-leitenden, leicht dotierten polykristallinen Siliziumlage **23a** ausgebildet. In diesem Fall werden Elektronen, d. h. Träger über die

gesamte n-leitende, leicht dotierte polykristalline Siliziumlage **23a** so verteilt, dass die gesamte n-leitende, leicht dotierte polykristalline Siliziumlage **23a** den Strompfad in dem Graben-Innengatewiderstand **4t** bilden kann.

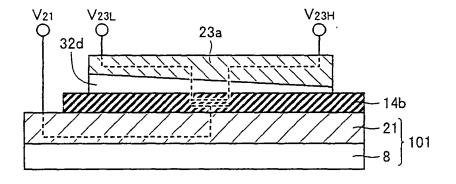

[0185] Unter Bezugnahme auf die Fig. 44, wenn  $V_{21}$  (0 >  $(V_{21} - V_{23L})$  >  $(V_{th}$  mit  $V_{23L})$ ) gilt, erreicht die n-leitende, leicht dotierte polykristalline Siliziumlage 23a den Sperrzustand. Somit wird eine Sperrlage 32d an der Fläche an der Seite des Isolierfilms 14b der n-leitenden, leicht dotierte polykristalline Siliziumlage 23a ausgebildet. In diesem Fall bildet die Sperrlage 32d keinen Strompfad in dem Graben-Innengatewiderstand 4t, so dass der Widerstandswert des Graben-Innengatewiderstands 4t erhöht wird. In der vorstehend genannten Formel gibt  $V_{th}$  ein Potenzial an, das einen Schwellwert erreicht, der bestimmt, ob die n-leitende, leicht dotierte polykristalline Siliziumlage 23a den Strom durchlassen kann oder nicht.

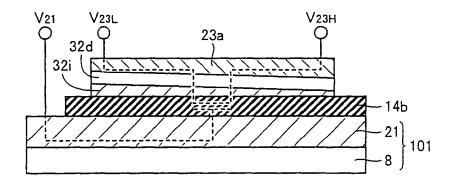

[0186] Unter Bezugnahme auf die Fig. 45, wenn  $V_{21}$  (0 > ( $V_{th}$  mit  $V_{23H}$ ) > ( $_{V21}$  –  $V_{23H}$ )) gilt, erreicht die n-leitende, leicht dotierte polykristalline Siliziumlage 23a den Inversionszustand. Insbesondere sind die Sperrlage 32d und eine Inversionslage 32i an der Fläche an der Seite des Isolierfilms 14b der n-leitenden, leicht dotierte polykristalline Siliziumlage 23a ausgebildet. In diesem Fall bildet die Sperrlage 32d keinen Strompfad in dem Graben-Innengatewiderstand 4t. Außerdem isoliert die Sperrlage 32d die Inversionslage 32i von dem Strompfad des Graben-Innengatewiderstands 4t. Daher wird der Widerstandswert des Graben-Innengatewiderstands 4t weiter erhöht.

[0187] Unter Bezugnahme auf die Fig. 40 unterscheidet sich der Graben-Innengatewiderstand 4t, der ein Widerstandselement einer Halbleitervorrichtung einer ersten Abwandlung von dem Ausführungsbeispiel ist, von diesem Ausführungsbeispiel darin, dass die Struktur der ersten Abwandlung des weiteren eine p-leitende, stark dotierte polykristalline Siliziumlage 24b aufweist, die an Abschnitten angeordnet ist, die mit dem Kontaktloch 9a an der Seite des Gateanschlusses und dem Kontaktloch 9b an der Seite der Hauptzwischenverbindung in Kontakt sind.

[0188] Unter Bezugnahme auf die Fig. 41 hat der Graben-Innengatewiderstand 4t, der ein Widerstandselement einer Halbleitervorrichtung einer zweiten Abwandlung des Ausführungsbeispieles ist, als einen Hauptabschnitt eine p-leitende, leicht dotierte polykristalline Siliziumlage 23b, die ein Halbleiterbereich ist. Der Graben-Innengatewiderstand 4t hat die p-leitende, stark dotierte polykristalline Siliziumlage 23b, die an Abschnitten angeordnet ist, die mit dem Kontaktloch 9a an der Seite des Gateanschlusses und dem Kontaktloch 9b an der Seite der Hauptzwischenverbindung in Kontakt sind.

[0189] Unter Bezugnahme auf die Fig. 42 unterscheidet sich der Graben-Innengatewiderstand 4t, der ein Widerstandselement einer Halbleitervorrichtung einer dritten Abwandlung des Ausführungsbeispieles ist, von der zweiten Abwandlung von diesem Ausführungsbeispiel darin, dass die Struktur der dritten Abwandlung des weiteren eine n-leitende, stark dotierte polykristalline Siliziumlage 24a aufweist, die an Abschnitten angeordnet ist, die mit dem Kontaktloch 9a an der Seite des Gateanschlusses und dem Kontaktloch 9b an der Seite der Hauptzwischenverbindung in Kontakt sind.

[0190] Wenn der Gatewiderstand in dem Sperrzustand zum Zwecke einer Erreichung einer gewünschten Gateverzögerung sehr hoch ist, kann die Struktur zusammen mit dem Graben-Innengatewiderstand 4t des ersten Erläuterungsbeispieles und/oder dem Graben-Innengatewiderstand 4t (Fig. 22 und Fig. 23) des zweiten Erläuterungsbeispieles verwendet werden

[0191] Wenn die Gateelektrode 13 durch Schritte ausgebildet wird, die sich von jenen des Graben-Innengatewiderstands 4t unterscheiden, kann das Dotieren des polykristallinen Siliziums mit unterschiedlicher Konzentration in jeweils unterschiedlichen Schritten durchgeführt werden. Dadurch können die Dotierungskonzentrationen der Gateelektrode 13 und der Gatehauptzwischenverbindung 5 erhöht werden, um die Widerstände abzusenken, so dass die Verzögerung und der Verlust in dem IGBT-Chip reduziert werden können.

[0192] Bei diesem Ausführungsbeispiel erzeugt die Potenzialdifferenz zwischen dem p-leitenden Bereich 21 und dem Graben-Innengatewiderstand 4t die Sperrlage an der n-leitenden, leicht dotierten polykristallinen Siliziumlage 23a des Graben-Innengatewiderstands 4t, so dass der Widerstandswert des Graben-Innengatewiderstands 4t eingestellt werden kann.

[0193] Da die n-leitende, stark dotierte polykristalline Siliziumlage 24a an dem Abschnitt ausgebildet wird, der mit dem Graben-Innengatewiderstand 4t in Kontakt ist, erhöht sich der Gatewiderstand im Laufe der Zeit eines Ausschaltvorgangs des IGBT-Elements EL. Dadurch kann die Überspannung des IGBT-Elements EL klein sein.

[0194] Bei der ersten und der dritten Abwandlung von diesem Ausführungsbeispiel ist der Graben-Innengatewiderstand 4t jeweils an dem elektrischen Kontaktabschnitt mit der n-leitenden, stark dotierten polykristallinen Siliziumlage 24a und der p-leitenden, stark dotierten polykristallinen Siliziumlage 24b vorgesehen. Dadurch verringert sich der Gatewiderstand in dem Akkumulationszustand, und insbeson-

dere ist die Verzögerungszeit stabil, wenn das Potenzial ( $V_q < 0 V$ ) aufgebracht wird.

[Zweites Ausführungsbeispiel]

**[0195]** Zuerst wird eine Struktur eines Widerstandselements einer Halbleitervorrichtung von diesem Ausführungsbeispiel beschrieben.

[0196] Unter Bezugnahme auf die Fig. 46 hat der IGBT-Chip von diesem Ausführungsbeispiel einen Dioden-Innengatewiderstand 4d als ein Widerstandselement. Der Dioden-Innengatewiderstand 4d hat eine p-leitende, stark dotierte polykristalline Silizumlage 24b, eine n-leitende, leicht dotierte polykristalline Siliziumlage 23a und eine n-leitende, stark leicht dotierte polykristalline Siliziumlage 24a. Die n-leitende, leicht dotierte polykristalline Siliziumlage 23a ist mit dem Gateanschluss 1 und der Gatehauptzwischenverbindung 5 über die p- und n-leitende, stark dotierte polykristalline Siliziumlage 24b und 24a jeweils elektrisch verbunden.

[0197] Gemäß der vorstehend beschriebenen Struktur hat der Dioden-Innengatewiderstand 4d von diesem Ausführungsbeispiel eine Diode (die durch ein Diodensymbol in der Figur dargestellt ist), die eine pn-Sperrfläche an der Grenzfläche zwischen der pleitenden, stark dotierten polykristallinen Siliziumlage 24b und der n-leitenden, leicht dotierten polykristallinen Siliziumlage 23a aufweist.

[0198] Bei diesem Ausführungsbeispiel ist ein Auswahlbereich der Konzentration der Fremdatome der n-leitenden, leicht dotierten polykristallinen Siliziumlage 23a breiter als bei dem ersten Ausführungsbeispiel. Die Konzentration der Fremdatome der n-leitenden, leicht dotierten polykristallinen Siliziumlage 23a bei dem ersten Ausführungsbeispiel ist so eingestellt, dass zumindest zwei von dem Inversionszustand, dem Akkumulationszustand und dem Sperrzustand erreicht werden, aber diese Beschränkung wird diesem Ausführungsbeispiel nicht auferlegt.

**[0199]** Strukturen außer die vorstehend beschriebenen sind im wesentlichen gleich wie bei dem ersten Ausführungsbeispiel, das bereits beschrieben wurde. Daher tragen die gleichen oder entsprechenden Elemente die gleichen Bezugszeichen, und deren Beschreibung wird nicht wiederholt.

**[0200]** Ein Betrieb des Widerstandselements bei der Halbleitervorrichtung von diesem Ausführungsbeispiel wird nun beschrieben. Bei einer Anfangsstufe und einer letzten Stufe des Schaltvorgangs des IGBT-Elements EL (in der **Fig.** 46 nicht gezeigt) ist die Potenzialdifferenz zwischen den entgegengesetzten Enden des Dioden-Innengatewiderstands **4d** klein, der Gatewiderstand der Gateelektrode **13** ist (in der **Fig.** 46 nicht gezeigt). Die Diode zeigt einen ho-

hen Widerstand, wenn eine Potenzialdifferenz zwischen einer Anode und einer Kathode klein ist. In umgekehrter Weise erreicht die Diode einen kleinen Widerstand, wenn die Potenzialdifferenz zwischen den entgegengesetzten Enden groß ist. Daher hat der Dioden-Innengatewiderstand 4d hohe Widerstandswerte während einer Anfangsstufe und einer letzten Stufe des Schaltvorgangs, wenn dies mit einer mittleren Stufe verglichen wird.

**[0201]** Abwandlungen der Halbleitervorrichtung des Ausführungsbeispiels werden nun beschrieben.

**[0202]** Unter Bezugnahme auf die **Fig.** 47 hat der Dioden-Innengatewiderstand **4d** bei einer ersten Abwandlung des Ausführungsbeispiels eine Diode (durch ein Diodensymbol in der Figur dargestellt), die eine pn-Sperrfläche an einer Grenzfläche zwischen der p-leitenden, leicht dotierten polykristallinen Siliziumlage **23b** und der n-leitenden, stark dotierten polykristallinen Siliziumlage **24a** aufweist.

**[0203]** Unter Bezugnahme auf die **Fig.** 48 unterscheidet sich eine zweite Abwandlung des Ausführungsbeispiels von dem Ausführungsbeispiel darin, dass der Dioden-Innengatewiderstand **4d** nicht im Inneren des Grabens des Halbleitersubstrats **101** angeordnet ist, aber er ist an dem Feldoxidfilm **7** ausgebildet.

**[0204]** Unter Bezugnahme auf die **Fig.** 49 ist bei einer dritten Abwandlung des Ausführungsbeispiels die Art die Leitfähigkeit der Diode entgegengesetzt zu jener der zweiten Abwandlung.

[0205] Bei diesem Ausführungsbeispiel hat der Dioden-Innengatewiderstand 4d hohe Widerstandswerte während der Anfangsstufe und der letzten Stufe des Schaltvorgangs des IGBT-Elements EL, wenn dies mit der mittleren Stufe verglichen wird. Daher wird eine Erzeugung einer Überspannung unterdrückt. Dies sorgt für einen kleinen Verlust des IGBT-Chips.