# (19) 国家知识产权局

# (12) 发明专利

(10) 授权公告号 CN 116521466 B (45) 授权公告日 2023. 09. 15

- (21)申请号 202310804435.0

- (22) 申请日 2023.07.03

- (65) 同一申请的已公布的文献号 申请公布号 CN 116521466 A

- (43) 申请公布日 2023.08.01

- (73)专利权人 武汉芯必达微电子有限公司 地址 430000 湖北省武汉市东湖高新区华 翔中心A2栋16楼

- (72)发明人 蒋晓伟

- (74) 专利代理机构 南京纵横知识产权代理有限 公司 32224

专利代理师 徐瑛

(51) Int.CI. **G06F** 11/22 (2006.01)

#### (56) 对比文件

- CN 107271884 A,2017.10.20

- CN 103839592 A,2014.06.04

- CN 103617810 A,2014.03.05

- CN 106802870 A,2017.06.06

- CN 103310850 A,2013.09.18

- CN 107301880 A,2017.10.27

- CN 116243147 A, 2023.06.09

- CN 115691632 A, 2023.02.03

- CN 103903651 A,2014.07.02

- CN 109801666 A, 2019.05.24

- CN 107068196 A, 2017.08.18

- CN 111354412 A, 2020.06.30

- CN 101458971 A, 2009.06.17

- CN 108062267 A,2018.05.22

- CN 112199308 A,2021.01.08

- US 2006031726 A1,2006.02.09

- US 2013151914 A1,2013.06.13

- US 2004049724 A1,2004.03.11

- US 2019244670 A1,2019.08.08

杨丽婷.嵌入式Flash存储器内建自测试电 路设计.《中国优秀硕士学位论文全文数据库》 .2020,全文.

任栋梁.嵌入式闪存测试技术研究.《中国优 秀硕士学位论文全文数据库》.2012,全文.

### 审查员 田翌

权利要求书2页 说明书8页 附图4页

#### (54) 发明名称

一种嵌入式Flash内建自测试的电路与方法 (57) 摘要

本发明公开提供一种嵌入式Flash内建自测 试的电路与方法,包括内建自测试接口BIST Interface和至少一个内建自测试控制器BIST Controller,其中,内建自测试接口BIST Interface包括:总线接口,命令寄存器CMD,模式 寄存器Pattern,数据寄存器Data和状态寄存器 Status:内建自测试控制器BIST Controller包 m 括:模式生成单元Pattern Generate,命令接口 99 单元和主状态机单元。本发明针对计算控制芯 片、SoC芯片的嵌入式Flash测试,提供了易于IP 化、易于系统集成的内建自测试电路结构,同时 云 提供了可在生产阶段和产品阶段嵌入式Flash的 测试方法,解决了eFlash BIST不易IP化、不易扩

展与集成:灵活性、效率与复杂度较难平衡:以及 用途单一,无法为产品级功能应用的问题。

1.一种嵌入式Flash內建自测试的电路,其特征在于,包括內建自测试接口BIST Interface和至少一个內建自测试控制器BIST Controller,其中,

所述內建自测试接口BIST Interface包括:总线接口,用于提供访问接口;命令寄存器 CMD,用于向至少一个所述內建自测试控制器BIST Controller下达不同测试命令;模式寄存器Pattern,用于配置命令执行的类型或参数;数据寄存器Data,用于对嵌入式闪存宏eFlash Macro内部的单个嵌入式闪存eFlash字或单个寄存器进行写或读操作;状态寄存器 Status,用于获取至少一个所述内建自测试控制器BIST Controller的命令执行状态和操作结果;

所述內建自测试控制器BIST Controller包括:模式生成单元Pattern Generate,用于不同模版算法的数据生成;模式检验单元Pattern Check,用于不同模版算法的数据检验;命令接口单元,用于向嵌入式闪存接口eFlash IF发起不同类型的命令请求;主状态机单元,用于解析內建自测试接口BIST Interface发起的命令与配置的模式,并根据这些信息,调用和管理模版算法逻辑和命令接口逻辑,进而硬件执行对嵌入式闪存宏eFlash Macro的测试操作,并由状态寄存器Status记录嵌入式闪存接口eFlash IF反馈的测试状态与结果;嵌入式闪存接口eFlash IF是嵌入式闪存宏eFlash Macro的基础操作的接口,控制嵌入式闪存宏eFlash Macro的所有I/O,根据嵌入式闪存宏eFlash Macro的规范产生操作时序,根据用户模式和测试模式的需要,开放相应的命令请求接口,即内建自测试控制器BIST Controller和用户控制器User Controller共用嵌入式闪存接口eFlash IF对嵌入式闪存宏eFlash Macro进行操作。

- 2.根据权利要求1所述一种嵌入式Flash内建自测试的电路,其特征在于,所述嵌入式闪存接口eFlash IF为嵌入式闪存宏eFlash Macro的基础操作接口,用于控制嵌入式闪存宏eFlash Macro的规范产生用户模式或测试模式的操作时序。

- 3.根据权利要求2所述一种嵌入式Flash内建自测试的电路,其特征在于,所述电路还包括嵌入式闪存用户模块eFlash User,包括用户控制器User Controller与用户接口User Interface,用于提供用户模式下对嵌入式闪存宏eFlash Macro进行编程或擦除的控制接口。

- 4.根据权利要求3所述一种嵌入式Flash内建自测试的电路,其特征在于,所述用户控制器User Controller与内建自测试控制器BIST Controller均通过所述嵌入式闪存接口eFlash IF对嵌入式闪存宏eFlash Macro进行操作。

- 5.根据权利要求1所述一种嵌入式Flash内建自测试的电路,其特征在于,所述电路还包括总线转换模块ATE2BUS,用于实现自动测试仪ATE总线对系统总线的转换,提供自动测试仪ATE对内建自测试接口BIST Interface中寄存器的访问。

- 6.根据权利要求1所述一种嵌入式Flash内建自测试的电路,其特征在于,所述电路还包括接入控制模块Access Control,用于配置访问权限控制。

- 7.一种嵌入式Flash内建自测试方法,应用权利要求1-6中任一项所述的电路实现,其特征在于,应用于生产测试阶段,所述方法包括:

连接自动测试仪ATE与被测裸芯片:

自动测试仪ATE通过总线转换模块ATE2BUS对内建自测试接口BIST Interface的寄存

### 器配置;

配置完成后,触发内建自测试控制器BIST Controller向嵌入式闪存接口eFlash IF发起与配置内容相应的操作请求,其中,操作过程控制由内建自测试控制器BIST Controller 硬件实现,操作时序控制由嵌入式闪存接口eFlash IF实现;

嵌入式闪存接口eFlash IF将操作完成的结果反馈至内建自测试接口BIST Interface 的寄存器,由自动测试仪ATE访问获取。

- 8.根据权利要求7所述一种嵌入式Flash内建自测试方法,其特征在于,根据嵌入式闪存eFlash的规格与工艺特性,设计用于嵌入式闪存宏eFlash Macro测试的测试用例与测试数量。

- 9.一种嵌入式Flash内建自测试方法,应用权利要求1-6中任一项所述的电路实现,其特征在于,应用于产品测试阶段,所述方法包括:

中央处理单元CPU运行测试用例程序,通过总线对内建自测试接口BIST Interface的 寄存器进行配置;

配置完成后,触发内建自测试控制器BIST Controller向嵌入式闪存接口Flash IF发起与配置内容相应的操作请求,其中,操作过程控制由内建自测试控制器BIST Controller硬件实现,操作时序控制由嵌入式闪存接口eFlash IF实现;

嵌入式闪存接口eFlash IF将操作完成的结果反馈至内建自测试接口BIST Interface 的寄存器,由CPU读取。

10.根据权利要求9所述一种嵌入式Flash内建自测试方法,其特征在于,根据待测试产品的规格与功能,设计用于嵌入式闪存宏eFlash Macro测试的测试用例与测试数量。

# 一种嵌入式Flash内建自测试的电路与方法

### 技术领域

[0001] 本发明属于计算控制芯片、SoC集成电路领域,尤其涉及嵌入式Flash(eFlash)的可测试性设计方向,更具体地,涉及一种应用于片上嵌入式Flash的内建自测试的电路结构与测试方法。

## 背景技术

[0002] 随着集成电路工艺的发展与进步,嵌入式Flash已经成为计算控制芯片、SoC产品领域必不可少的部分。嵌入式Flash的容量也朝着越来越大的方向发展,在此趋势下存储器模块对整个SoC芯片的面积占比将越来越大,这也意味着嵌入式Flash区域可能将分布到更多的故障或缺陷,因此,为提高嵌入式Flash的良率,针对嵌入式Flash的测试变得越来越重要。

[0003] 论文《一种嵌入式Flash存储器的内建自测试电路的设计》(郭巍巍,复旦大学,2014)介绍了当今嵌入式Flash存储器的故障类型与测试方法:对于故障类型,主要可分为硬故障与软故障,典型的硬故障有译码器故障、存储器I/0漏电、存储单元损坏等,典型的软故障有存储单元固定(stuck)故障、存取速度慢、读/写干扰故障等。因此,嵌入式Flash的测试需要对上述故障类型进行有效且高效的检测。

[0004] 对于嵌入式Flash存储器的测试方法主要有三种:

[0005] 1、直接存取测试

[0006] 利用自动测试仪(ATE)对嵌入式Flash直接访问,此方法缺点在于需将大量嵌入式Flash I/0引出,且长时间占用ATE,导致过高的测试成本;

[0007] 2、利用嵌入式微处理器间接测试

[0008] 利用微处理器对嵌入式Flash进行读写操作,测试向量为微处理器运行的程序代码,此方法缺点在于一方面依赖微处理架构与指令,没有很好的可移植性,另一方面对可运行的测试用例的类型和数量有所限制,如无法执行对嵌入式Flash内部高压的修调(Trim)操作等:

[0009] 3、存储器内建自测试(BIST)

[0010] 利用额外增加的测试功能电路,包括测试状态机、地址发生器、数据发生器、比较器等逻辑,在ATE的控制下,BIST自动完成对嵌入式Flash的特定操作,并反馈执行结果。

[0011] 目前,內建自测试(BIST,Built-In Self-Test)是大规模存储器最通用的方法,相较其他两种方法,具有相对成本低、效率高、覆盖率高、测试灵活的优势。当前,针对计算控制芯片、SoC领域嵌入式Flash內建自测试的电路结构与测试方法存在以下缺点:

[0012] 1、eFlash BIST不易IP化、不易扩展与集成

[0013] 例如,针对一个Block eFlash Macro的BIST电路无法复用至多个Block eFlash Macro的测试;

[0014] 2、eFlash BIST的灵活性、效率与复杂度较难平衡

[0015] 例如,存在方案将eFlash BIST测试用例固化,包含测试模式与测试个数均固定,

此方法虽一定程度保证了效率,但将具有较大的逻辑复杂度,降低了针对性测试序列排布的灵活性和用于定位调试的灵活性;

[0016] 3、eFlash BIST用途单一,无法为产品级功能应用

[0017] 当前的eFlash BIST方案均用于工厂阶段的CP测试,暂无eFlash BIST复用于芯片导入、产品开发阶段的eFlash关键功能自检的方案,虽然可以使用eFlash用户模式接口对一部分eFlash功能进行自检,但是对于涉及特殊模式操作的测试用例,如Margin Read、读参考电压测试等,用户模式接口无法覆盖,同时,对于大区域范围的操作的测试用例,用户模式接口测试方式也相当耗时。

# 发明内容

[0018] 为克服上述现有技术的不足,本发明提供一种嵌入式Flash内建自测试的电路与方法,用以解决上述至少一个技术问题。

[0019] 根据本发明说明书的一方面,提供一种嵌入式Flash内建自测试的电路,包括内建自测试接口BIST Interface和至少一个内建自测试控制器BIST Controller,其中,

[0020] 所述內建自测试接口BIST Interface包括:总线接口,用于提供访问接口;命令寄存器CMD,用于向至少一个所述內建自测试控制器BIST Controller下达不同测试命令;模式寄存器Pattern,用于配置命令执行的类型或参数;数据寄存器Data,用于对嵌入式闪存宏eFlash Macro内部的单个嵌入式闪存eFlash字或单个寄存器进行写或读操作;状态寄存器Status,用于获取至少一个所述內建自测试控制器BIST Controller的命令执行状态和操作结果;

[0021] 所述內建自测试控制器BIST Controller包括:模式生成单元Pattern Generate,用于不同模版算法的数据生成;模式检验单元Pattern Check,用于不同模版算法的数据检验;命令接口单元,用于向嵌入式闪存接口eFlash IF发起不同类型的命令请求;主状态机单元,用于解析內建自测试接口BIST Interface发起的命令与配置的模式,并根据这些信息,调用和管理模版算法逻辑和命令接口逻辑,进而硬件执行对嵌入式闪存宏eFlash Macro的测试操作,并由状态寄存器Status记录嵌入式闪存接口eFlash IF反馈的测试状态与结果。

[0022] 上述技术方案针对计算控制芯片、SoC芯片的嵌入式Flash测试,提供了一种易于 IP化、易于系统集成的内建自测试电路结构,可用于生产阶段和产品阶段的eFlash测试,且 实现了灵活性、效率与复杂度的平衡。

[0023] 作为进一步的技术方案,所述嵌入式闪存接口eFlash IF为嵌入式闪存宏eFlash Macro的基础操作接口,用于控制嵌入式闪存宏eFlash Macro的所有I/0,根据嵌入式闪存宏eFlash Macro的规范产生使用模式或测试模式的操作时序。

[0024] 作为进一步的技术方案,所述电路还包括嵌入式闪存用户模块eFlash User,包括用户控制器User Controller与用户接口User Interface,用于提供用户模式下对嵌入式闪存宏eFlash Macro进行编程或擦除的控制接口。

[0025] 作为进一步的技术方案,所述用户控制器User Controller与内建自测试控制器 BIST Controller均通过所述嵌入式闪存接口eFlash IF对嵌入式闪存宏eFlash Macro进行操作。

[0026] 作为进一步的技术方案,所述电路还包括总线转换模块ATE2BUS,用于实现自动测试仪ATE总线对系统总线的转换,提供自动测试仪ATE对内建自测试接口BIST Interface中寄存器的访问。

[0027] 作为进一步的技术方案,所述电路还包括接入控制模块Access Control,用于配置访问权限控制。

[0028] 根据本发明说明书的一方面,提供一种嵌入式Flash内建自测试方法,应用所述的电路实现,应用于生产测试阶段,所述方法包括:

[0029] 连接自动测试仪ATE与被测裸芯片;

[0030] 自动测试仪ATE通过总线转换模块ATE2BUS对内建自测试接口BIST Interface的 寄存器配置;

[0031] 配置完成后,触发内建自测试控制器BIST Controller向嵌入式闪存接口eFlash IF发起与配置内容相应的操作请求,其中,操作过程控制由内建自测试控制器BIST Controller硬件实现,操作时序控制由嵌入式闪存接口eFlash IF实现;

[0032] 嵌入式闪存接口eFlash IF将操作完成的结果反馈至内建自测试接口BIST Interface的寄存器,由自动测试仪ATE访问获取。

[0033] 作为进一步的技术方案,根据嵌入式闪存eFlash的规格与工艺特性,设计用于嵌入式闪存宏eFlash Macro测试的测试用例与测试数量。

[0034] 根据本发明说明书的一方面,提供一种嵌入式Flash内建自测试方法,应用所述的电路实现,应用于产品测试阶段,所述方法包括:

[0035] 中央处理单元CPU运行测试用例程序,通过总线对内建自测试接口BIST Interface的寄存器进行配置:

[0036] 配置完成后,触发内建自测试控制器BIST Controller向嵌入式闪存接口Flash IF发起与配置内容相应的操作请求,其中,操作过程控制由内建自测试控制器BIST Controller硬件实现,操作时序控制由嵌入式闪存接口eFlash IF实现;

[0037] 嵌入式闪存接口eFlash IF将操作完成的结果反馈至内建自测试接口BIST Interface的寄存器,由CPU读取。

[0038] 作为进一步的技术方案,根据待测试产品的规格与功能,设计用于嵌入式闪存宏eFlash Macro测试的测试用例与测试数量。

[0039] 与现有技术相比,本发明的有益效果在于:

[0040] 1、本发明提供的eFlash BIST框架,易于IP化、可用于多eFlash Macro测试的扩展;

[0041] 2、本发明提供的eFlash BIST功能,兼顾了测试流程的灵活性与效率,同时降低了逻辑冗余;

[0042] 3、本发明提供的eFlash BIST 计算控制芯片、SoC集成方案,可实现生产阶段灵活、高效的CP测试与调试分析;

[0043] 4、本发明提供的eFlash BIST 计算控制芯片、SoC集成方案测试方法与流程,增强了eFlash BIST逻辑的用途支持产品阶段eFlash的更丰富、更高效的功能自检。

# 附图说明

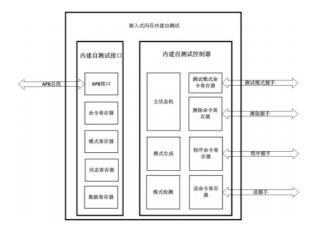

[0044] 图1为根据本发明实施例的嵌入式Flash内建自测试电路的功能模块示意图。

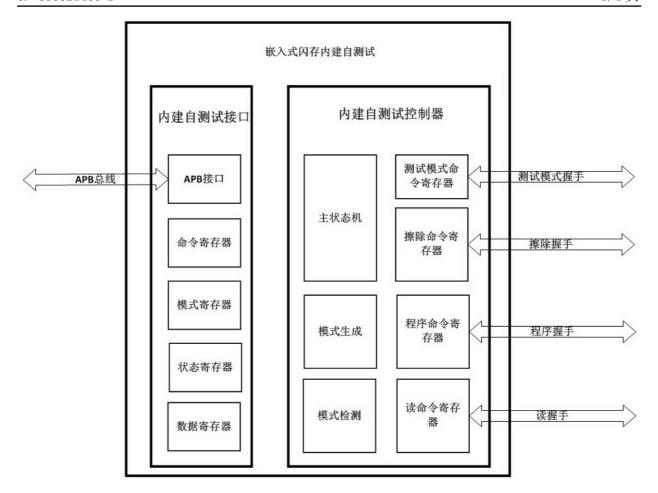

[0045] 图2为根据本发明实施例的eFlash IF与eFlash Macro示意图。

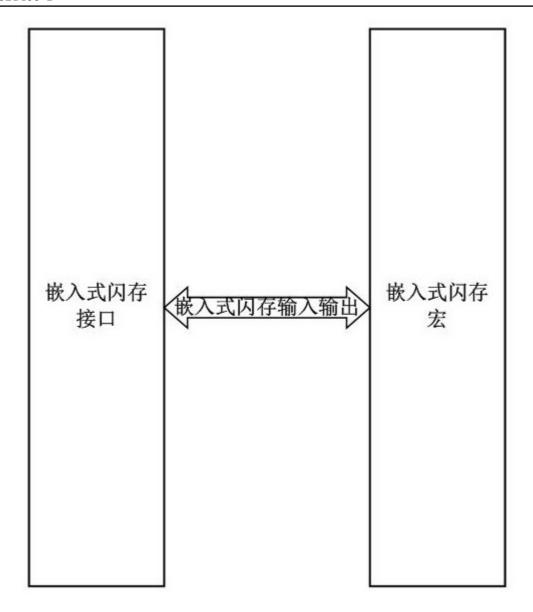

[0046] 图3为根据本发明实施例的计算控制芯片系统架构示意图。

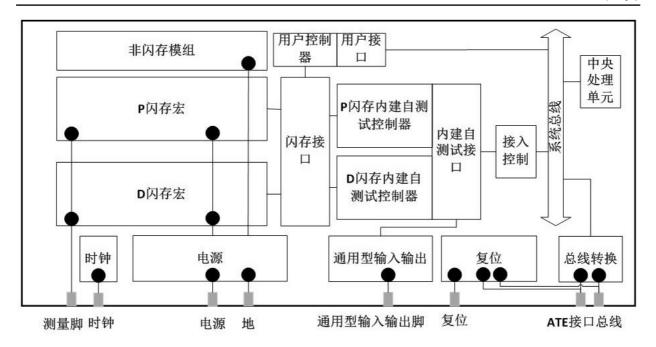

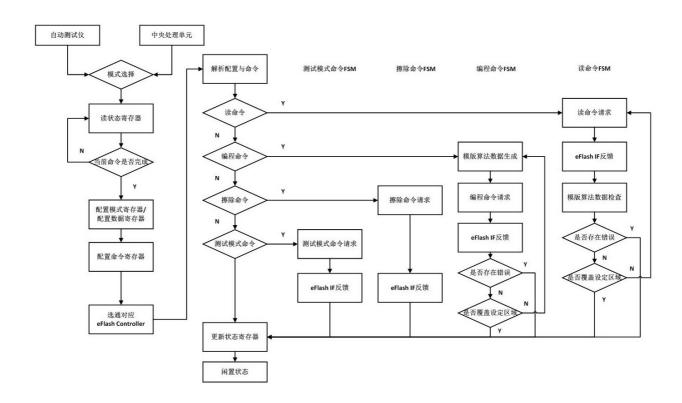

[0047] 图4为根据本发明实施例的ATE模式/CPU模式eFlash BIST命令执行流程图。

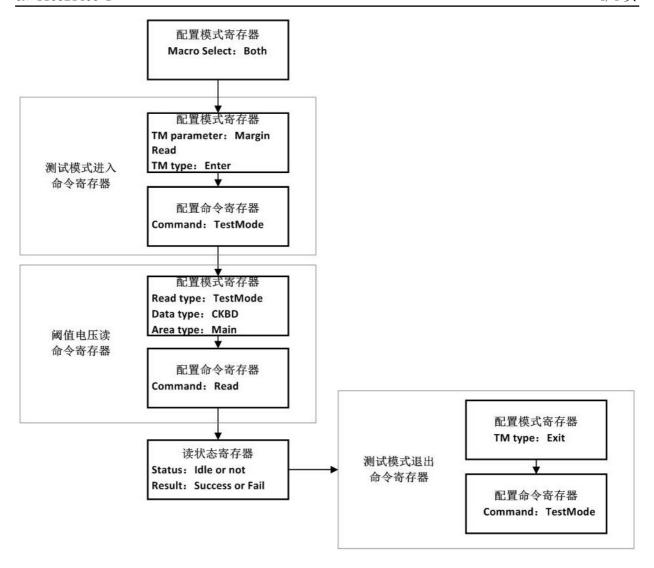

[0048] 图5为根据本发明实施例的对典型测试用例实施的配置流程示意图。

## 具体实施方式

[0049] 以下将结合附图对本发明各实施例的技术方案进行清楚、完整的描述,显然,所描述的实施例仅仅是本发明的一部分实施例,而不是全部的实施例。基于本发明的实施例,本领域普通技术人员在没有做出创造性劳动的前提下所得到的所有其它实施例,都属于本发明所保护的范围。

[0050] 本发明针对计算控制芯片、SoC芯片的嵌入式Flash(以下简称eFlash)测试,提供了一种易于IP化、易于系统集成的内建自测试电路结构,同时提供了可在生产阶段和产品阶段eFlash的测试方法。

[0051] 本发明提供的內建自测试电路结构包括两个层面:eFlash BIST模块层面和 eFlash BIST相关的系统层面。

[0052] 如图1所示,eFlash BIST模块由两个子模块构成:内建自测试接口BIST Interface(以下简称BIST Interface)与内建自测试控制器BIST Controller(以下简称BIST Controller)。

[0053] BIST Interface主要由APB总线接口和多个寄存器组成,功能是为以下寄存器资源提供APB访问接口,从而有利于系统集成。这里并不仅限于APB总线,可以是其他协议的系统总线。

[0054] 命令寄存器CMD,用于向BIST Controller下达不同测试目的命令,如程序 Program、读Read、擦除Erase命令等。

[0055] 模式寄存器Pattern,用于配置命令执行的类型或参数,如模版算法类型、操作区域、操作时序参数等。

[0056] 数据寄存器Data,用于对嵌入式闪存宏eFlash Macro(以下简称eFlash Macro)内部的单个eFlash字或单个寄存器进行写或读操作。

[0057] 状态寄存器Status,用于获取BIST Controller命令执行状态和操作结果等。

[0058] BIST Controller主要由三大部分逻辑组成:模版算法逻辑、命令接口逻辑和主状态机逻辑。

[0059] 进一步地,模版算法逻辑包括Pattern Generate和Pattern Check,用于不同模版算法的数据生成与检验,数据的生成与检验将根据模版算法的规律,为Flash Macro对应地址生成模版数据,用于向eFlash Macro中编程和从eFlash Macro中读取后比对。模版算法类型包括全零(Full 0)、全一(Full 1)、棋盘格(CKBD)、反棋盘格(ICKBD)、对角线(DIAG)、首行首列零(1R1C)。

[0060] 进一步地,命令接口逻辑包括TestMode CMD、Erase CMD、Program CMD和Read CMD,用于向eFlash IF发起不同类型的命令请求,上述命令接口逻辑通过握手方式向

eFlash IF发起对应类型的操作请求,同时eFlash IF反馈命令执行状态与结果。

[0061] 进一步地,主状态机逻辑包括Main FSM,BIST Controller的主状态机,用于解析 BIST Interface发起的命令与配置的模式,并根据这些信息,调用和管理模版算法逻辑和命令接口逻辑,进而硬件执行对eFlash Macro的测试操作,并由状态寄存器记录eFlash IF 反馈的测试状态与结果。

[0062] 在一些实施方式中,BIST Interface与BIST Controller之间可以一对多例化。例如,对于2个eFlash Macro的计算控制芯片系统,eFlash BIST模块可以由一个BIST Interface和两个BIST Controller构成,这样仅需要修改一小部分逻辑,便可实现对两个eFlash Macro的独立、同步测试,利于简化ATE的操作步骤,降低测试时间。

[0063] 嵌入式闪存接口eFlash IF(以下简称eFlash IF)是eFlash Macro的基础操作的接口,控制eFlash Macro的所有I/0,根据eFlash Macro的规范产生操作时序,根据用户模式和测试模式的需要,开放相应的命令请求接口,即BIST Controller和User Controller共用eFlash IF对eFlash Macro进行操作;区别在于,BIST Controller相较User Controller具有更多类型的操作命令接口与更多可配的操作参数。相对于已有方案中eFlash BIST需要单独对eFlash Macro的时序控制逻辑而言,本发明将用户模式和测试模式的操作时序逻辑统一实现于eFlash IF,优点在于一方面降低了eFlash BIST的复杂度,易于将eFlash BIST IP化,另一方面用户模式和测试模式的时序操作大部分融合、复用,减少了逻辑冗余。

[0064] eFlash Macro即eFlash IP,内部主要是由浮栅结构构成的存储阵列以及对围绕存储阵列的控制逻辑与接口逻辑,是eFlash BIST执行操作、测试的最终对象。

[0065] eFlash BIST相关的系统层面主要是为实现具体功能所涉及的除eFlash BIST模块外的其他模块,以及它们与eFlash BIST模块之间的联系,主要模块有:

[0066] 1、ATE2BUS模块,实现ATE总线对系统总线的转换,提供ATE对BIST Interface模块 寄存器的访问:

[0067] 2、eFlash User模块,包括User Controller与User Interface,提供用户模式下对eFlash Macro进行编程或擦除的控制接口;

[0068] 3、eFlash IF模块,eFlash Macro的基础操作的接口,控制eFlash Macro的所有I/0,根据eFlash Macro的规范产生操作时序,操作时序包括使用模式时序与测试模式时序;

[0069] 4、Access Control模块,可配置访问权限控制,在不同阶段保护eFlash内容不被故意或意外改变;

[0070] 5、Clock、Power、Reset模块,提供生产模式和用户模式下的时钟、电源、复位信号。

[0071] 在模块间关联上,eFlash User模块和eFlash BIST模块的寄存器部分均可通过总线访问与控制,并且均具有向eFlash IF发起操作请求的功能;区别在于eFlash BIST模块是针对eFlash的故障、性能测试,需要具有更丰富、更高效、更灵活的操作模式,如高压修调(HV Trim)、棋盘格算法编程与验证、Margin Read等,而这些是不需要且不应该在正常使用阶段开放给用户的。

[0072] 本发明提供的可在生产阶段和产品阶段对eFlash进行测试的方法是利用上述eFlash BIST电路结构,所匹配的使用方法与流程,包括以下两个方面:

[0073] 1、生产阶段测试方法

[0074] 生产阶段对eFlash的测试,也称Wafer Sort或CP测试,是在晶元封装前对eFlash的测试,这是本发明的主要应用场景。

[0075] 生产阶段测试需要ATE设备,由ATE通过探针卡与被测裸Die连接,ATE通过ATE2BUS 模块对BIST Interface的寄存器配置,触发BIST Controller向eFlash IF发起相应的操作请求,操作过程控制由BIST Controller硬件实现,操作时序控制由eFlash IF实现,eFlash IF将操作完成与结果将反馈至BIST Interface的寄存器,可由ATE访问获取,在ATE上位机的控制下完成测试流程。

[0076] ATE上位机可根据eFlash规格与工艺特性,灵活且有针对性地设计测试用例与测试数量对eFlash Macro进行测试。

[0077] 2、产品阶段测试方法

[0078] 随着eFlash对计算控制芯片、SoC领域产品越来越重要,在利用计算控制芯片、SoC 芯片进行产品开发阶段,也越来越重视对eFlash基本功能的测试与验证,例如,eFlash阵列 完整性检查、eFlash地址编解码逻辑检查、阈值电压读操作(Margin Read)、eFlash读参考 电压检查(Read reference voltage)等,这是本发明创新的应用场景。

[0079] 产品阶段测试需要利用计算控制芯片、SoC内置的微处理器(CPU)和额外的存储资源,额外的存储资源可以是片上SRAM,存储所需的测试用例程序,CPU运行测试用例程序,通过总线对BIST Interface的寄存器配置,触发BIST Controller向Flash IF发起相应的操作请求,操作过程控制由BIST Controller硬件实现,操作时序控制由eFlash IF实现,eFlash IF将操作完成与结果反馈至BIST Interface的寄存器,可由CPU读取,在测试程序的控制下完成整个测试流程。

[0080] CPU运行的测试程序可根据产品规格与重点功能,灵活且有针对性地设计测试用例与测试数量对eFlash Macro进行测试。此方法复用了eFlash BIST模块逻辑,为产品开发阶段提供了对eFlash基础功能自检的高效测试方法。

[0081] eFlash BIST命令是测试的基础单元,根据测试用例的要求,可由单个或多个BIST命令组合实现一个完整的测试用例,多个测试用例组合实现整体的生产阶段的CP测试或产品阶段的自检测试。

[0082] 作为一种实施方式,对单个命令的执行流程如图4所示。

[0083] 首先,根据当前芯片阶段选择测试模式,即借助ATE实现的CP测试或借助嵌入式CPU实现的自检测试,两者可等效称为主机,下称主机。由主机通过总线读取eFlash BIST状态寄存器,判断当前是否正在执行命令,主机应等待BIST Controller闲置后发起新的操作;如果上一个命令已完成,则开始发起新的命令流程,主机首先根据需要,配置模式寄存器与数据寄存器,然后配置命令寄存器,eFlash BIST模块内部逻辑将根据模式寄存器中Macro选择配置,选通对应的BIST Controller,例如,如果选通PFlash与DFlash,则对应的PFlash BIST Controller与DFlash BIST Controller将一起解析配置与命令,独立、并行执行操作;

[0084] 然后,选通的eFlash BIST Controller的主状态机将开始运行,根据解析的配置信息和命令信息跳转至如下子状态机:

[0085] 读命令子状态机,根据配置信息,从起始地址开始,以Word为单位向eFlash IF发起读请求,eFlash IF反馈完成信号后,模版算法数据检查模块对eFlash反馈的数据信号进

行比对,如果数据不一致,则可跳出读命令子状态机,更新命令状态为完成,命令结果为 Fail,也可将错误数据地址缓存至状态寄存器用于定位分析;如果数据一致,则判断读取范 围是否已覆盖设定范围,如果没有覆盖,则继续发起读请求,进行数据检查,直到全部覆盖, 跳出读命令子状态机,并更新命令状态为完成,命令结果为Success。

[0086] 编程命令子状态机,根据配置信息,从起始地址开始,由模版算法逻辑生成地址相关的数据,子状态机以Word或Row为单位向eFlash IF发起编程命令请求,eFlash IF反馈完成信号,同时eFlash IF反馈编程是否成功,如果不成功,则跳出编程命令子状态机,更新命令状态为完成,命令结果为Fail,也可将错误数据地址缓存至状态寄存器用于定位分析;如果编程成功,则判断编程范围是否已覆盖设定的范围,如果没有覆盖,则继续发起编程请求,直到全部覆盖,跳出编程子状态机,并更新命令状态为完成,命令结果为Success。

[0087] 擦除命令子状态机,根据配置信息,发起相应类型的擦除命令请求,如块擦除或整片擦除,eFlash IF反馈完成信号,同时eFlash IF反馈擦除是否成功,如果失败,更新命令状态为完成,命令结果为Fail,如果成功,则更新命令状态为完成,命令结果为Success。

[0088] 测试模式命令子状态机,测试模式是eFlash Macro所定义的模式配置机制,包括测试模式进入与测试模式退出,测试模式的进入和退出分别为一段特殊时序,进入相应的测试模式后,便可以在测试模式所具有的条件下对eFlash Macro进行特殊模式操作;子状态机根据配置信息,向eFlash IF发起测试模式进入或测试模式退出,eFlash IF反馈完成信号,同时eFlash IF反馈测试模式进入或退出是否成功,如果失败,更新命令状态为完成,命令结果为Fail,如果成功,则更新命令状态为完成,命令结果为Success。

[0089] 最后,在子状态机完成状态寄存器的更新后,主状态机与子状态机进入闲置状态。

[0090] 作为一种实施方式,对典型测试用例实施的配置流程如图5所示。

[0091] 以图5 的Margin Read CKBD测试用例,分析具体的配置流程,Margin Read是一个常见的eFlash测试用例,意义是在一定电压偏置下检验读操作是否正常,eFlash Macro具有Margin Read测试模式,配置流程如下:

[0092] 首先,配置模式寄存器选通两个eFlash Macro,这样,两个BIST Controller将接收同一命令与配置,并且同时执行测试;

[0093] 其次,进行 TestMode Enter命令配置,包括配置模式寄存器中TestMode参数为 Margin Read,TestMode类型为Enter,然后配置命令寄存器为TestMode,按照eFlash BIST 命令执行流程执行测试模式命令操作;

[0094] 然后,进行Margin Read命令配置,包括配置模式寄存器中Read类型为TestMode模式,这将告诉eFlash IF使用测试模式的时序参数,配置模版数据类型为CKBD,配置读区域为Main Array,然后配置命令寄存器为Read,按照eFlash BIST命令执行流程执行读命令操作;

[0095] 对存储主区Main Array的读检验操作将持续微妙或毫秒级别,此时,主机可通过循环读状态寄存器的方式判断操作是否完成、操作是否成功,对于本示例,需分别读取两个eFlash BIST独立的状态位,来判断操作是否完成;

[0096] 最后,在操作完成后,为进行后续其他测试,需退出TestMode,进行 TestMode Exit命令配置,包括配置模式寄存器中TestMode类型为Exit,然后配置命令寄存器为 TestMode,按照eFlash BIST命令执行流程执行测试模式命令操作;

[0097] 至此,一个完整的测试用例执行完成,类似的,可以根据测试需要,由主机排列与组合测试序列,以达到全面、可靠的测试目的。

[0098] 本发明的电路结构中,内建自测试接口BIST Interface配置有总线接口,便于系统集成,同时内建自测试接口BIST Interface可对应多个内建自测试控制器BIST Controller,可实现一次命令配置,对多个嵌入式闪存eFlash执行独立、并行测试,有利于降低逻辑面积、减少自动测试仪ATE操作次数与测试时间。

[0099] 本发明在eFlash的内建自测试部分不包含对嵌入式闪存宏eFlash Macro直接操作的逻辑,由嵌入式闪存接口eFlash IF统一实现用户模式和测试模式的时序控制,内建自测试控制器BIST Contoller与用户控制器User Controller均使用嵌入式闪存接口eFlash IF通过握手方式发起操作请求,有利于减少冗余逻辑面积,易于eFlash BIST IP化。

[0100] 本发明基于eFlash BIST模块实施的系统架构与测试方法,eFlash BIST模块可接入系统总线,由ATE、CPU分别控制,对应提供了生产阶段CP测试方法与产品阶段功能测试方法,复用了eFlash BIST功能逻辑,提供了灵活、高效的自检功能。

[0101] 在本说明书的描述中,参考术语"一个实施方式"、"某些实施方式"、"示意性实施方式"、"示例"、"具体示例"、或"一些示例"等的描述意指结合所述实施方式或示例描述的具体特征、结构、材料或者特点包含于本发明的至少一个实施方式或示例中。在本说明书中,对上述术语的示意性表述不一定指的是相同的实施方式或示例。而且,描述的具体特征、结构、材料或者特点可以在任何的一个或多个实施方式或示例中以合适的方式结合。

[0102] 最后应说明的是:以上实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明实施例技术方案。

图 1

图 2

图 3

图 4

图 5