#### (19) **日本国特許庁(JP)**

## (12) 特許公報(B2)

(11)特許番号

特許第4928754号 (P4928754)

(45) 発行日 平成24年5月9日(2012.5.9)

(24) 登録日 平成24年2月17日 (2012.2.17)

| (51) Int.Cl. | FI                           |                     |

|--------------|------------------------------|---------------------|

| HO1L 29/78   | <b>(2006.01)</b> HO1L        | 29/78 6 5 2 F       |

| HO1L 29/739  | <b>) (2006.01)</b> HO1L      | 29/78 6 5 2 B       |

|              | HO1L                         | 29/78 6 5 2 M       |

|              | HO1L                         | 29/78 6 5 3 A       |

|              | HO1L                         | 29/78 6 5 5 A       |

|              |                              | 講求項の数 5 (全 12 頁)    |

| (21) 出願番号    | 特願2005-210162 (P2005-210162) | (73) 特許権者 000003078 |

| (22) 出願日     | 平成17年7月20日 (2005.7.20)       | 株式会社東芝              |

| (65) 公開番号    | 特開2007-27561 (P2007-27561A)  | 東京都港区芝浦一丁目1番1号      |

| (43) 公開日     | 平成19年2月1日 (2007.2.1)         | (74)代理人 110001092   |

| 審査請求日        | 平成20年6月9日(2008.6.9)          | 特許業務法人サクラ国際特許事務所    |

||(74)代理人 100077849 弁理士 須山 佐一

(72) 発明者 杉山 公一

神奈川県川崎市幸区小向東芝町1番地 株 式会社東芝 マイクロエレクトロニクスセ

ンター内

(72) 発明者 山口 正一

神奈川県川崎市幸区小向東芝町1番地 株 式会社東芝 マイクロエレクトロニクスセ

ンター内

最終頁に続く

## (54) 【発明の名称】電力用半導体装置

#### (57)【特許請求の範囲】

### 【請求項1】

半導体装置としてのバーティカルな方向である第1の方向に直交する第2の方向に延長 する形状のゲート電極と、

前記ゲート電極を取り囲むゲート絶縁膜と、

前記ゲート絶縁膜の一部を介して前記ゲート電極に対向位置するn型ソース層と、

前記n型ソース層に隣接し、かつ前記ゲート絶縁膜の別の一部を介して前記ゲート電極 に対向位置するp型ベース層と、

前記p型ベース層に隣接しかつ前記n型ソース層に接することなく、前記ゲート絶縁膜 のさらに別の一部を介して前記ゲート電極に対向位置するn型ベース層と、

前記第2の方向に直交したラテラル方向である第3の方向に延びるストライプ状の突出 面領域を前記n型ソース層および前記p型ベース層に接するため有するひとつの電極領域 لے

を具備することを特徴とする電力用半導体装置。

#### 【請求項2】

前記ゲート電極が、トレンチゲート構造であることを特徴とする請求項1記載の電力用 半導体装置。

#### 【請求項3】

前記n型ソース層が、前記第2の方向に平行に延長形成されていることを特徴とする請 求項1記載の電力用半導体装置。

#### 【請求項4】

前記n型ソース層が、比較的n型濃度の低い領域と比較的n型濃度の高い領域とからなり、該比較的n型濃度の低い領域が前記電極領域に接し、該比較的n型濃度の高い領域は前記電極領域に接していないことを特徴とする請求項1記載の電力用半導体装置。

## 【請求項5】

前記 n 型ソース層が、前記<u>第2の</u>方向に対して45度以下の角度をもって<u>ラテラル方向</u>に延長形成されていることを特徴とする請求項1記載の電力用半導体装置。

#### 【発明の詳細な説明】

#### 【技術分野】

[0001]

本発明は、電流のスイッチングを行う電力用半導体装置に係り、特に、絶縁ゲート型構造の電力用半導体装置に関する。

#### 【背景技術】

## [0002]

電流スイッチングを行う電力用半導体装置は、一般に、損失低減などのためオン状態における発生電圧(オン電圧)が十分に小さいことが求められる。この目的のため、IGBT(insulated gate bipolar transistor)やMOSFETなどの絶縁ゲートを有する電力用半導体装置では、ゲート電極ピッチを密に形成してチャネル密度を高くする手法を採用することができる。

## [0003]

ゲート電極ピッチを密に形成するには、一般に、マスク合わせ精度を高くする必要がある。特に、スイッチングされる電流の経路である半導体領域とその電極領域とのコンタクト面おける必要な位置合わせ精度は、ゲート電極形成ピッチの狭小化に伴い増大する。このためプロセス的な困難性が大きくなる。このようなプロセス的な困難性を増大させずにゲート電極形成ピッチを密にするには、ゲート電極のみすべて取り囲むように絶縁膜を先に形成してから半導体領域の面を電極領域とのコンタクト面とすることが考えられる。これによればゲート電極との接触を避けるように容易に電極領域を形成でき、半導体領域との電極領域とのコンタクト面の形成における必要な合わせ精度を原理的に不要にすることができる。

## [0004]

しかしながら、いずれにしてもチャネル密度を高くすると、負荷短絡時に過大な電流が流れ、例えば保護回路を設けてもこれが作動する前に破壊してしまうというような半導体装置としての不具合が発生しやすくなる。なお、本願で提供しようとする半導体装置とは構造や製造方法が異なるが、参考となる半導体装置には下記特許文献1に開示のものがある。

【特許文献 1 】特開 2 0 0 1 - 1 5 7 4 3 号公報

## 【発明の開示】

【発明が解決しようとする課題】

### [0005]

本発明は、オン電圧を十分に低減しかつ十分な短絡耐量を確保することが可能な電力用 40 半導体装置を提供することを目的とする。

#### 【課題を解決するための手段】

### [0006]

本発明の一態様に係る電力用半導体装置は、半導体装置としてのバーティカルな方向である第1の方向に直交する第2の方向に延長する形状のゲート電極と、前記ゲート電極を取り囲むゲート絶縁膜と、前記ゲート絶縁膜の一部を介して前記ゲート電極に対向位置するn型ソース層と、前記n型ソース層に隣接し、かつ前記ゲート絶縁膜の別の一部を介して前記ゲート電極に対向位置するp型ベース層と、前記p型ベース層に隣接しかつ前記n型ソース層に接することなく、前記ゲート絶縁膜のさらに別の一部を介して前記ゲート電極に対向位置するn型ベース層と、前記第2の方向に直交したラテラル方向である第3の

10

20

30

方向に延びるストライプ状の突出面領域を前記 n 型ソース層および前記 p 型ベース層に接するため有するひとつの電極領域とを具備する。

#### 【発明の効果】

#### [0007]

本発明によれば、オン電圧を十分に低減しかつ十分な短絡耐量を確保することが可能な電力用半導体装置を提供することができる。

【発明を実施するための最良の形態】

### [0008]

本発明の一態様に係る半導体装置によれば、スイッチングすべき電流が流れる半導体領域たるn型ソース層およびp型ベース層へのコンタクトを行う電極領域が、ゲート電極が延長する方向と直交する方向に延びる複数の横平面でこれらのn型ソース層およびp型ベース層に接触する。すなわち、ゲート電極の配置との合わせ精度を問題とする必要のないコンタクト領域の方向設定であり、チャネル密度が密であってもコンタクト領域形成のためのプロセス的な困難性が増大しない。さらに、n型ソース層のソース領域としての機能が、過大な電流が流れるとその一部で喪失する。これは、ゲート電極が延長する方向と直交する方向の延びる横平面が複数であるため接触面がストライプ状となり、これにより電極領域と直接接触しないソース領域へは微小な抵抗が生じるからである。したがって、過大な電流が流れようとするとチャネル密度が減少し破壊を防止する。

#### [0009]

なお、ここで「横平面」は、半導体装置としての横方向(ラテラル方向)の平面を言い 、縦方向(バーティカル方向)の平面ではないことを意味する。

#### [ 0 0 1 0 ]

本発明の実施態様として、前記ゲート電極は、トレンチゲート構造である、とすることができる。ゲート電極形成ピッチを密にするための有力な構造である。

#### [0011]

また、実施態様として、前記トレンチゲート構造を有する前記ゲート電極が、<u>前記第2</u>の方向に平行に複数形成され、該複数のゲート電極それぞれが含まれるトレンチゲート構造の部分同士の間隔が 1  $\mu$  m以下である、とすることができる。トレンチゲート構造同士の間隔を 1  $\mu$  m以下としてチャネル密度を増加させるものである。電極形成の位置合わせ精度が不要のため、このような微小なトレンチゲート構造同士の間隔を有する場合に向いている。

## [0012]

また、実施態様として、前記 n 型ソース層は、前記<u>第2の</u>方向に平行に延長形成されている、とすることができる。チャネル密度を密にするための有力な構造である。

#### [0013]

また、実施態様として、前記 p 型ベース層が、比較的 p 型濃度の低い領域と比較的 p 型濃度の高い領域とからなり、該比較的 p 型濃度の高い領域が前記電極領域に接し、該比較的 p 型濃度の低い領域は前記電極領域に接していない、とすることができる。比較的 p 型濃度の高い領域と電極領域とを接することによりオーミック接合を確実化するものである

## [0014]

また、実施態様として、前記n型ソース層が、前記ゲート電極あたりふたつ存在する、とすることができる。例えば、ゲート電極用のトレンチを形成するためのマスクを利用してイオン注入を行えばこのような態様になる。製造プロセスとしての便宜が得られる。

## [0015]

また、実施態様として、前記n型ソース層が、前記ゲート電極あたりひとつ存在する、とすることもできる。例えばn型ソース層を形成するためのみのマスクを利用してイオン注入を行えばこのような態様になる。ゲート電極形成ピッチを小さくすれば、このような態様でもチャネル密度を大きくすることができる。

## [0016]

10

20

30

10

20

30

40

50

また、実施態様として、前記n型ソース層が、比較的n型濃度の低い領域と比較的n型濃度の高い領域とからなり、該比較的n型濃度の低い領域が前記電極領域に接し、該比較的n型濃度の高い領域は前記電極領域に接していない、とすることができる。比較的n型濃度の低い領域が電極領域に接することで、電極からソース領域へ微小な抵抗を形成する。これにより、過大な電流が流れようとしたときにソース領域としての機能をなくさせ、半導体装置として破壊することを一層防止できる。

#### [0017]

また、実施態様として、前記 n 型ソース層が、前記<u>第2の</u>方向に対して45度以下の角度をもって<u>ラテラル方向に</u>延長形成されている、としてもよい。このように n 型ソース層がゲート電極の方向に対して傾いて形成されていても、コンタクト領域設定のためのプロセス的な困難性が増大しない。また、過大な電流が流れようとするとソース領域として機能が不全となり破壊を防止する。なお、45度を超えるとコンタクト領域設定のための必要な位置合わせ精度は徐々に増加する。ゲート電極が延長する方向での位置合わせ余裕が小さくなるからである。

#### [0018]

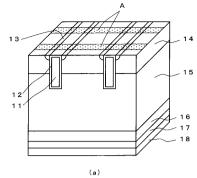

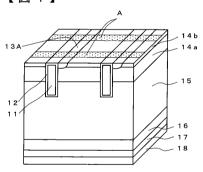

以上を踏まえ、以下では本発明の実施形態を図面を参照しながら説明する。図1は、本発明の一実施形態に係る電力用半導体装置(IGBT)の構造を模式的に示す仮想切断斜視図である。図1(b)がエミッタ電極20を含めた全体の図示であり、図1(a)は、特徴を示すため、図1(b)において、p型ベース層14の上面の高さで切断しその上面を示した仮想図である。両図中に示した前側の切断面パターンは、不図示の左右方向には繰り返し形成されている。また、不図示の前後方向には同一パターンである。

#### [0019]

このIGBTは、図示するように、ゲート電極11、ゲート絶縁膜12、n型ソース層 13、p型ベース層14、n型ベース層15、n型バッファ層16、p型エミッタ層17 、コレクタ電極18、絶縁膜19、エミッタ電極20を有する。図1(a)におけるドットパターンAの領域は、エミッタ電極20の下面であって、半導体領域であるn型ソース層13およびp型ベース層14まで達した領域面を示している。

#### [0020]

ゲート電極11は、複数のトレンチそれぞれの中に埋め込み形成され、これによりそれぞれ縦方向に長い矩形上の断面を有しその断面に直交する方向に延長する形状になっている。延長の端部では互いに電気的に導通されひとつのゲート端子Gを構成する。また、ゲート電極11は、ゲート絶縁膜12に取り囲まれ、ゲート絶縁膜11を介して上部でn型ソース層13と、それより下でp型ベース層14と、さらにそれより下でn型ベース層15とそれぞれ対向している。ゲート絶縁膜12を介してゲート電極11と対向するp型ベース層14の領域にはチャネルが形成される。なお、ゲート電極11の断面形状は、図示するような長矩形状ではなく、下側で丸みを帯びさせるなどして電界緩和を図るのがより実際的である。「縦方向」は、半導体装置としての縦方向(バーティカル方向)である。【0021】

n型ベース層15の下側には、n型バッファ層16、p型エミッタ層17、コレクタ電極18がそれぞれ積層的に位置している。コレクタ電極18は、コレクタ端子Cとして機能する。n型ベース層15の上側には、p型ベース層14が積層的に位置し、p型ベース層14の上面側にはトレンチ両側の領域に選択的にn型ソース層13が形成されている。n型ソース層13は、ゲート電極11ひとつあたりふたつあることになり、そのそれぞれはゲート電極11が延長する方向と平行に形成されている。これによりチャネル密度を向上しチャネルでの電圧降下Vchを減少させてオン抵抗を低減できる。n型ソース層13それぞれは、大電流で抵抗が顕在化するようにある程度細く形成するのが好ましい。

#### [0022]

絶縁膜19は、少なくとも、ゲート電極11の上面を覆い、かつ領域Aを除く半導体領域を覆うように選択的に形成されている。エミッタ電極20は、領域A内でn型ソース層13およびp型ベース層14に接触するように絶縁膜19上を含めて全面に形成されてい

10

20

30

40

50

る。エミッタ電極 2 0 は、エミッタ端子 E として機能する。領域 A は、ゲート電極 1 1 が延長する方向に直交する方向に延びる複数の横平面であり、複数であることからストライプ状になっている。

#### [0023]

このIGBTのトランジスタとしての動作は以下のようである。コレクタ電極18が正、エミッタ電極20が負の各電圧とされ、エミッタ電極20に対してゲート電極11に正の電圧が印加されると、n型ソース層13に連なりゲート絶縁膜12に対向するp型ベース層14の領域にチャネルが形成される。するとこのチャネルを介してn型ソース層13からn型ベース層15に電子が注入され、これに対応してp型エミッタ層17からはn型バッファ層16を介してn型ベース層15にホールが注入される。これらによりp型エミッタ層17、n型ベース層15+n型バッファ層16、p型ベース層14からなるpnpトランジスタがオンし、IGBTとしてオン状態となる。エミッタ電極20とゲート電極11との間に正電圧が印加されなくなるとチャネルが消失して上記トランジスタがオフし、IGBTとしてオフ状態となる。

#### [0024]

図1(a)、同(b)に示す構造は、寸法的には、例えば、ゲート絶縁膜12を含めたゲート電極11(ゲート絶縁膜12を含めたゲート電極11の部分を以下「トレンチゲート構造部分」ともいう。)の幅を0.5μmから2μm程度、トレンチゲート構造部分同士の間隔(内法)を1μm程度以下とすることができる。このような微小な間隔であっても、エミッタ電極20が半導体領域であるn型ソース層13およびp型ベース層14と接触する領域は、図示の領域Aとされており、すなわち、トレンチゲート構造部分同士の間隔の延びる方向と直交しており、接触領域の設定に位置合わせの困難性は生じない。

## [0025]

また、領域 A での接触のため、エミッタ電極 2 0 が n 型ソース層 1 3 の上面すべてには接触せず、負荷短絡のような場合には、エミッタ電極 2 0 に接していない n 型ソース層 1 3 の部分が抵抗として顕在化しその部分に連なるチャネルが消失する。よって、チャネル密度が減じて過大電流が抑制され破壊を防止できる。なお、領域 A それぞれの幅は例えば 1 μ m 以上、それらの間隔(内法)は例えば 1 μ m ないし 1 0 μ m とすることができる。以上の電極位置合わせおよび破壊防止の点は比較参照例と対比して再度説明する。

## [0026]

他の部分の寸法については、図1(a)におけるゲート絶縁膜12が下側でn型ベース層15に接する深さは、例えば2μmないし6μm、同図のp型ベース層14の達する深さは、例えば1μmないし3μmとすることができる。また、ゲート絶縁膜12の厚さを、ゲート電極11の側方および下方でともに例えば100nm程度、図1(a)におけるゲート電極11上面の絶縁膜19の厚さ(図1(b)においてではない)を例えば0.2μm程度とすることができる。p型ベース層14およびn型ソース層13上での絶縁層19の厚さは、例えば0.5μmないし1μmとすることができる。

## [0027]

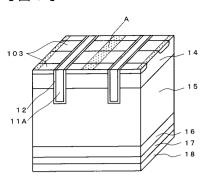

図8は、比較参照例としての電力用半導体装置(IGBT)の構造を模式的に示す仮想切断斜視図である。図としての見方は図1(a)と同じである。また、図1に示したものと同一相当の部位には同一符号を付してある。この比較参照例では、n型ソース層103をゲート電極11Aの延長する方向と直交する方向に形成して、それら間の位置合わせ精度を要しないようにしている。しかし、不図示のエミッタ電極が接触する領域Aをゲート電極11Aの延長する方向と同一方向にストライプ状とする必要があり、ゲート電極11A間の間隔が狭い場合には、ゲート電極11Aを形成するためのトレンチと領域Aとの位置合わせが難しい。また、チャネル密度が図1に示したものに比較して小さい。

#### [0028]

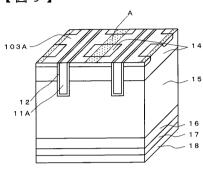

図9は、別の比較参照例としての電力用半導体装置(IGBT)の構造を模式的に示す 仮想切断斜視図である。図としての見方は図1(a)と同じである。また、図1に示した ものと同一相当の部位には同一符号を付してある。この比較参照例は、n型ソース層10

10

20

30

40

50

3 A がゲート電極 1 1 A を挟むようにも形成され全体として梯子状に形成されているので、図 8 に示したものに比べてチャネル密度が向上している。しかしながら、この場合には、図示左右方向に、 n 型ソース層 1 0 3 A とゲート電極 1 1 A を形成するためのトレンチとの位置合わせも必要になりさらにプロセス的な困難性が増加する。

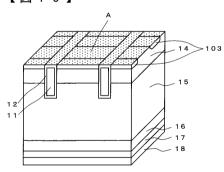

## [0029]

図10は、さらに別の比較参照例としての電力用半導体装置(IGBT)の構造を模式的に示す仮想切断斜視図である。図としての見方は図1(a)と同じである。また、図1、図8に示したものと同一相当の部位には同一符号を付してある。この比較参照例は、図8と見比べてわかるように、ゲート電極11上のみにあらかじめ絶縁膜を形成しておくものであり、n型ソース層103については図8に示したものと同様である。この場合には、不図示のエミッタ電極が接触する領域Aを図示するように全面として、ゲート電極11が埋め込まれるトレンチとの電極接触の位置合わせが不要になる。しかしながら、n型ソース層103の上面すべてにエミッタ電極が接触しているので、負荷短絡時などの大電流が流れる場合にn型ソース層103の抵抗が顕在化しにくく、破壊しやすい。

#### [0030]

以上述べた比較参照例との対比により、図1に示した実施形態の利点はより明確である

## [0031]

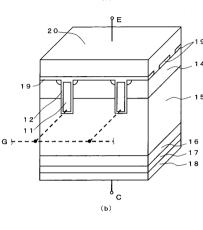

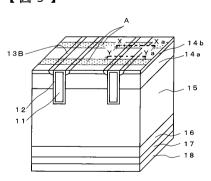

次に、本発明の別の実施形態に係る電力用半導体装置(IGBT)について図2を参照して説明する。図2は、本発明の別の実施形態に係る電力用半導体装置(IGBT)の構造を模式的に示す仮想切断斜視図である。図2において、図1中に示した部位と同一のものには同一の符号を付してある。その部分については説明を省略する。なお、図2は、図1(a)に対応する図示であり、図1(b)に対応する図示は自明なので省略する。

#### [0032]

この実施形態は、 p型ベース層 1 4 を、 p型濃度の比較的低い p型ベース層 1 4 a と p型濃度の比較的高い p型ベース層 1 4 b ( = p型コンタクト層) とからなるようにしている。 p型ベース層 1 4 b は p型ベース層 1 4 a の上面側に形成されており、不図示のエミッタ電極との領域 A での接触はもっぱら p型濃度の比較的高い p型ベース層 1 4 b の側が行うようになっている。このようにすることで、エミッタ電極と p型ベース層 2 b の厚みの分だけ p型ベース層全体としての抵抗を小さくさせている。 p型ベース層 1 4 b の厚みは例えば 0 . 3 p m 程度にすることができる。この実施形態は、 p型濃度の比較的低い p型ベース層 1 4 a の不純物濃度を制御することで、しきい値電圧をある程度変えることもできる。

#### [0033]

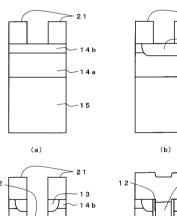

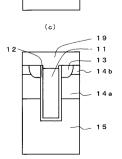

次に、図2に示したIGBTにおけるn型ソース層13およびその周辺の形成過程を図3を参照して説明する。図3は、図2に示したIGBTにおけるn型ソース層13およびその周辺の形成過程を模式的に示す工程図であるが、図1に示した実施形態でもほぼ同様である。図3において、図1、図2に対応する部位には同一符号を付してある。図1、図2に示した実施形態は、ゲート電極11を形成するためのトレンチとn型ソース層13との形成位置合わせが一見難しいように見えるが、以下のようにしてこの困難さを回避できる。

### [0034]

まず、図3(a)に示すように、n型ベース層15上にp型濃度の比較的低いp型ベース層14aとp型濃度の比較的高いp型ベース層14bとを積層的に形成する。これは、例えば、n型ベース層15にp型不純物となる例えばボロンのイオン注入・拡散を行ってp型ベース層14aを形成後、さらに、例えばボロンのイオン注入を加速エネルギ、ドーズ量を変えて行いp型ベース層14bを形成すればよい。なお図1に示した実施形態の場合はp型ベース層14として単一に形成する。p型ベース層14a、14bが形成されたら、ゲート電極11のためのトレンチを加工形成するため、所定のパターンを有する例え

ば酸化膜からなるマスク21を上面に設ける(図3(a))。

## [0035]

次に、このマスク21を利用してn型不純物となる例えばリンのイオン注入を、p型ベース層14bに向けてかつその注入深さがp型ベース層14a中に達するように行う。このときやや斜め方向からイオン注入を行うか、または垂直にイオン注入後熱拡散させるか、あるいはその両者を行うことで、図3(b)に示すように、マスク21の下側にも広がってn型ソース層13を形成させる。

### [0036]

次に、図3(c)に示すように、引き続きマスク21を利用して、n型ソース層13およびp型ベース層14aを貫通しn型ベース層15中に達するトレンチ22を、例えばRIE(reactive ion etching)法で形成する。そして、図3(d)に示すように、トレンチ22の側壁および底面を例えば熱酸化させてゲート絶縁膜12を形成する。

#### [0037]

そのあとマスク21を除去しゲート酸化膜12が形成されたトレンチ内を含めて例えば多結晶シリコンを例えばCVD(chemical vapor deposition)法で堆積させ、さらに堆積させた多結晶シリコンをエッチバックしトレンチ内のみに多少落ち込ませて残しゲート電極11とする(図3(d))。続いて絶縁膜19を全面に堆積させる(同)。このときトレンチ22の幅の設定によっては(特にそれが広い場合)、図3(d)に示すように、堆積させた絶縁膜19の上面に段差が形成され、このまま領域Aを露出するため絶縁膜19のエッチングを行うとゲート電極11が露出する恐れがある。

#### [0038]

そこで、絶縁膜19を全面に堆積させたら、図3(e)に示すように、絶縁膜19の上面側を例えばCMP(chemical mechanical polishing)法で平坦化し、その後領域Aを露出するために絶縁膜19の選択的エッチングを行う。これにより、ゲート電極11の露出を避けて絶縁膜19の最終的なパターン形成が終了する。このあとエミッタ電極20(図1(b)参照)が形成されるが、そのときゲート電極11とエミッタ電極20とのショート不良を効果的に防止できる。

#### [0039]

図3に示した工程によれば、n型ソース層13の形成にゲート電極11用のトレンチ22を形成するためのマスク21が利用されるので、それら間の位置合わせ精度の問題は生じない。また、ゲート電極11の幅を広く(例えばトレンチゲート構造部分の間隔より広く)形成する場合に想起される、ゲート電極11とエミッタ電極20とのショート不良の問題にも対処がされている。

#### [0040]

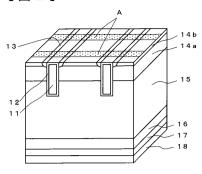

次に、本発明のさらに別の実施形態について図4を参照して説明する。図4は、本発明のさらに別の実施形態に係る電力用半導体装置(IGBT)の構造を模式的に示す仮想切断斜視図である。図4において、すでに説明した部位と同一の部位には同一符号を付してあり、その部分の説明は省略する。なお、図4は、図1(a)に対応する図示であり、図1(b)に対応する図示は自明なので省略する。

## [0041]

この実施形態は、 n型ソース層 1 3 Aがゲート電極 1 1 の片側のみに形成されており、つまりゲート電極 1 1 ひとつあたり n型ソース層 1 3 Aがひとつ存在するようになっている。このような構造の違いはあるが、エミッタ電極 2 0 (図 1 ( b )参照)が半導体領域である n型ソース層 1 3 A および p型ベース層 1 4 b と接触する領域は、図示の領域 A とされ、トレンチゲート構造部分間の延びる方向と直交しているので、接触領域の設定に位置合わせの困難性は生じない。また、領域 A での接触のため、エミッタ電極 2 0 が n型ソース層 1 3 A の上面すべてには接触せず、負荷短絡のような場合には、エミッタ電極 2 0 に接していない n型ソース層 1 3 A の部分が抵抗として顕在化しその部分に連なるチャネルが消失する。よって、チャネル密度が減じて過大電流が抑制され破壊を防止できる。

## [0042]

50

10

20

30

この実施形態は、 n 型ソース層 1 3 A を例えばマスクを用いてイオン注入で形成するとき、マスク位置精度(ゲート電極 1 1 との位置合わせ精度)をあまり求めないようにできる。これは、図 4 の図示左右方向における n 型ソース層 1 3 A の形成幅の違いは、実際上、動作の違いにあまり影響を与えないからである。これにより、 n 型ソース層を形成するためのマスクの位置は、ゲート電極 1 1 を形成するトレンチの位置に一部が重なる程度の精度があればよい。

#### [0043]

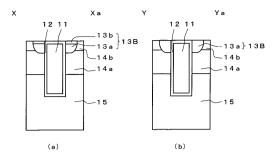

次に、本発明のさらに別の実施形態について図5、図6を参照して説明する。図5は、本発明のさらに別の実施形態に係る電力用半導体装置(IGBT)の構造を模式的に示す仮想切断斜視図である。図6は、図5中に示すX-Xa位置およびY-Ya位置における矢視方向の模式的な断面図である。図5、図6において、すでに説明した部位と同一の部位には同一符号を付してあり、その部分の説明は省略する。なお、図5は、図1(a)に対応する図示であり、図1(b)に対応する図示は自明なので省略する。

## [0044]

この実施形態は、エミッタ電極と接触する領域Aにおけるn型ソース層13Bの構造に特徴があり、図6(a)に示すように、領域Aに接触する上面は比較的n型不純物濃度の低いn型ソース層13bの領域とされており、それ以外は図6(a)、同(b)に示すように比較的n型不純物濃度の高いn型ソース層13aとなっている。n型ソース層13bの形成には、例えば、絶縁膜19(図1(b)、図3(e)参照)をエッチングで形成後に、領域Aに少量のp型不純物(例えばボロン)をイオン注入すればよい。

#### [0045]

この実施形態のIGBTは、例えば負荷短絡で過大な電流が流れようとすると、n型ソース層13bが抵抗領域として顕著になり、n型ソース層13aの電位が上がる。よってこのときのIGBTはソース層としての機能が不全となりオン状態が持続しなくなる。すなわち、短絡耐量をさらに増加させることができる。

#### [0046]

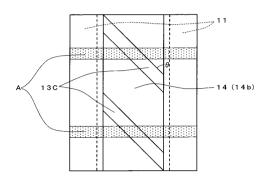

次に、本発明のさらに別の実施形態について図7を参照して説明する。図7は、本発明のさらに別の実施形態に係る電力用半導体装置(IGBT)の構造を模式的に示す半導体領域の上面図である。図7において、すでに説明した部位と同一の部位には同一符号を付してあり、その部分の説明は省略する。図7は、図1(a)における上面に対応した図示である。

## [0047]

この実施形態は、 n型ソース層 1 3 Cを、ゲート電極 1 1 が延長する方向に対して角度を持たせて形成したものである。このような斜角で n型ソース層 1 3 Cを形成することでゲート電極 1 1 の位置に対する n型ソース層 1 3 Cの位置合わせは必要なくなる。また、エミッタ電極 2 0 (図 1 (b)参照)が接触する領域 A の形成方向が上記各実施形態と同じくゲート電極 1 1 が延長する方向と直交しているので、領域 A とゲート電極 1 1 との位置合わせ精度も必要ない。

### [0048]

領域 A と n 型ソース層 1 3 C との位置合わせには多少考慮が必要であるが、例えば角度を 4 5 度以下とすれば、領域 A の図示上下方向の設定余裕が大きくなり好ましい。角度 を 4 5 度よりかなり小さく設定して、ゲート電極 1 1 同士間に挟まれるひとつの n 型ソース層 1 3 C あたり複数の領域 A が設けられるようにしてもよい。

## [0049]

この実施形態のIGBTでも短絡耐量の改善は実現されている。領域Aとn型ソース層13Cとが重なる領域から、ゲート電極11に対向のp型チャネル領域14に形成されるチャネルまでの間に、ある程度の長さのn型ソース層13Cが介在する構造だからである。また、n型ソース層13Cの間を詰めてこれらを多数形成することでチャネルの密度を増加させることも可能でありオン電圧の低減も実現可能である。

## 【図面の簡単な説明】

10

20

30

## [0050]

- 【図1】本発明の一実施形態に係る電力用半導体装置(IGBT)の構造を模式的に示す 仮想切断斜視図。

- 【図2】本発明の別の実施形態に係る電力用半導体装置(IGBT)の構造を模式的に示す仮想切断斜視図。

- 【図3】図2に示したIGBTにおけるn型ソース層13およびその周辺の形成過程を模式的に示す工程図。

- 【図4】本発明のさらに別の実施形態に係る電力用半導体装置(IGBT)の構造を模式的に示す仮想切断斜視図。

- 【図5】本発明のさらに別の実施形態に係る電力用半導体装置(IGBT)の構造を模式的に示す仮想切断斜視図。

- 【 図 6 】図 5 中に示すX-Xa位置およびY-Ya位置における矢視方向の模式的な断面 図。

- 【図7】本発明のさらに別の実施形態に係る電力用半導体装置(IGBT)の構造を模式的に示す半導体領域の上面図。

- 【図8】比較参照例としての電力用半導体装置(IGBT)の構造を模式的に示す仮想切断斜視図。

- 【図9】別の比較参照例としての電力用半導体装置(IGBT)の構造を模式的に示す仮想切断斜視図。

- 【図10】さらに別の比較参照例としての電力用半導体装置(IGBT)の構造を模式的に示す仮想切断斜視図。

#### 【符号の説明】

#### [0051]

1 1 … ゲート電極、 1 2 … ゲート絶縁膜、 1 3 , 1 3 A , 1 3 B , 1 3 C … n型ソース層、 1 3 a … n型ソース層(n型濃度高)、 1 3 b … n型ソース層(n型濃度低)、 1 4 m p型ベース層、 1 4 a … p型ベース層(p型濃度低)、 1 4 b … p型ベース層(p型濃度高:p型コンタクト層)、 1 5 … n型ベース層、 1 6 … n型バッファ層、 1 7 … p型エミッタ層、 1 8 … コレクタ電極、 1 9 … 絶縁膜、 2 0 … エミッタ電極、 2 1 … ゲート電極用トレンチを形成するためのマスク、 2 2 … ゲート電極用のトレンチ、 A … エミッタ電極と半導体領域とのコンタクト面。

30

10

【図1】

【図2】

【図3】

-15

(d)

(e)

【図4】

【図5】

# 【図6】

# 【図7】

# 【図8】

【図9】

【図10】

## フロントページの続き

## 審査官 安田 雅彦

(56)参考文献 特開2007-005492(JP,A)

特開平03-064931(JP,A)

特開2004-165691(JP,A)

特開平08-316479(JP,A)

特開2001-015743(JP,A)

## (58)調査した分野(Int.CI., DB名)

H01L 29/78

H01L 21/336

H01L 29/739

H01L 21/331