### (19) **日本国特許庁(JP)**

GO6F 12/00

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2011-175666 (P2011-175666A)

(43) 公開日 平成23年9月8日(2011.9.8)

(51) Int. Cl. GO6F 12/02 (2006, 01) FIGO6F 12/02 530C GO6F 12/00 591

テーマコード (参考) 5B060

GO6F 12/00 597U

> 審査請求 有 請求項の数 10 OL (全 12 頁)

(21) 出願番号 特願2011-97418 (P2011-97418) (22) 出願日 平成23年4月25日 (2011.4.25) (62) 分割の表示 特願2011-4482 (P2011-4482)

(2006, 01)

の分割

原出願日 平成23年1月13日 (2011.1.13) (31) 優先権主張番号 特願2010-19547 (P2010-19547)

(32) 優先日 平成22年1月29日 (2010.1.29)

(33) 優先権主張国 日本国(JP) (71) 出願人 000003078 株式会社東芝

東京都港区芝浦一丁目1番1号

(74)代理人 100108855

弁理士 蔵田 昌俊

(74)代理人 100159651

弁理士 高倉 成男

(74)代理人 100091351

弁理士 河野 哲

(74)代理人 100088683

弁理士 中村 誠

(74)代理人 100109830

弁理士 福原 淑弘

(74)代理人 100075672

弁理士 峰 隆司

最終頁に続く

# (54) 【発明の名称】半導体記憶装置及び半導体記憶装置の制御方法

# (57)【要約】

CPUからの1コマンドでコンパクション動 作が実行される半導体記憶装置。

【課題を解決するための手段】 半導体記憶装置は、不 揮発性メモリのコマンドをキューイングするキューイン グバッファ(26)と、不揮発性メモリのリードコマン ドを発行するリード手段(#102)と、リード手段に より前記不揮発性メモリから読み出されたデータをユー ザデータと管理データとに分離する分離手段(#104 )と、不揮発性メモリのライトアドレスを管理するライ トポインタ情報により示されるアドレスを分離手段によ り得られた管理データに対して加えてライトコマンドを 発行し、キューイングバッファへ自動的にキューイング するライトコマンド発行手段(#110)と、ライトコ マンド発行手段により発行されたライトコマンドを不揮 発性メモリに与え、データを不揮発性メモリに書き込む ライト手段(#114)とを具備する。

# 【選択図】図4

#### 【特許請求の範囲】

### 【請求項1】

不揮発性メモリからデータを読み出すリード手段と、

前記リード手段により読み出されたデータをユーザデータと管理データとに分離する分離手段と、

前記不揮発性メモリのライトアドレスを管理するライトポインタ情報により示されるアドレスを前記分離手段により分離された管理データに対して加えてライトコマンドを発行し、前記分離手段により分離されたデータを前記不揮発性メモリに書き込むライト手段と

を具備する半導体記憶装置。

# 【請求項2】

前記ライト手段による書き込み処理の開始する際に、前記リード手段により読み出されたデータが有効か無効かを判定する判定手段をさらに具備し、

前記ライト手段は、前記判定手段により無効であると判定されると、無効なデータを前記不揮発性メモリに書き込む請求項1記載の半導体記憶装置。

#### 【請求項3】

前記ライト手段による書き込み処理の開始する際に、前記リード手段により読み出されたデータが有効か無効かを判定する判定手段をさらに具備し、

前記ライト手段は、前記判定手段により無効であると判定されると、書き込み処理を中止する請求項1記載の半導体記憶装置。

#### 【請求項4】

前記ライト手段による書き込み処理後、正引きテーブルを更新する手段をさらに具備する請求項1記載の半導体記憶装置。

#### 【請求項5】

前記不揮発性メモリは所定のバイト毎に1ページを構成し、所定のページが1ブロックを構成し、ページ単位でアクセスされ、データは全てのページが無効であるフリーブロックの先頭ページから書き込まれ、前記ライトポインタ情報は1ページの書き込みに応じてインクリメントされる請求項1記載の半導体記憶装置。

### 【請求項6】

不揮発性メモリを含む半導体記憶装置の制御方法であって、

前記不揮発性メモリからデータを読み出すことと、

前記不揮発性メモリから読み出されたデータをユーザデータと管理データとに分離する ことと

前記不揮発性メモリのライトアドレスを管理するライトポインタ情報により示されるアドレスを前記分離することにより分離された管理データに対して加えてライトコマンドを発行することと、

前記ライトコマンドを前記不揮発性メモリに与え、前記分離されたデータを前記不揮発性メモリに書き込むことと、

を具備する制御方法。

#### 【請求項7】

前記書き込み処理の開始の際に、前記不揮発性メモリから読み出されたデータが有効か無効かを判定することをさらに具備し、

前記書き込むことは、前記不揮発性メモリから読み出されたデータが無効であることを判定すると、無効なデータを前記不揮発性メモリに書き込む請求項6記載の制御方法。

#### 【請求項8】

前記書き込み処理の開始の際に、前記不揮発性メモリから読み出されたデータが有効か 無効かを判定することをさらに具備し、

前記不揮発性メモリから読み出されたデータが無効であることを判定すると、前記書き込むことは中止される請求項6記載の制御方法。

### 【請求項9】

10

20

30

40

50

20

30

40

50

前記書き込み処理後、正引きテーブルを更新することをさらに具備する請求項6記載の制御方法。

# 【請求項10】

前記書き込み処理後、前記不揮発性メモリのページ毎のデータの有効、無効を示すデータを示す有効ページ管理テーブルを更新することをさらに具備する請求項6記載の制御方法。

【発明の詳細な説明】

# 【技術分野】

# [0001]

本発明はNAND型フラッシュメモリ等の不揮発性メモリを含む半導体記憶装置及び半導体記憶装置の制御方法に関する。

# 【背景技術】

# [0002]

一般に不揮発性メモリ、例えばフラッシュメモリはデータの書き込みの際に上書きができないので、データの書き込みや削除を繰り返すと、分断された不要な領域が削除されずに残る。この不要な領域を消去し、使用している領域を連続した領域に纏める処理はコンパクションと呼ばれる。従来の半導体記憶装置のコンパクション処理は例えば特許文献1に記載されている。

### [0003]

特許文献 1 記載の記憶装置は、内部において、3 2 ビットのメモリバスに 1 6 ビットの入出力を持つ 2 チップの 8 ギガビットの N A N D 型フラッシュメモリが並列に接続される。2 つのチップは読み出しや書き込みにおいて同時並列にアクセスされる。すなわち、メモリバスは 1 6 ビットバスを 2 チャンネル備えた構成となっている。各フラッシュメモリは書き込みや読み出しのアクセスを例えば 4 キロバイトのページ単位で行う。従って、実ページサイズとしては 8 キロバイトが一括アクセスされることになる。

#### [0004]

記憶装置に内蔵されたRAMには、プログラムを実行するためのコードエリアやワーキングエリアが設けられており、さらにページ単位の仮想アドレスを管理するアドレス変換テーブル、正常な空きブロックを検索する検索テーブル、各ブロックの無効ページ数を管理するカウンタテーブル、ライトポインタ、無効ページ総数のカウンタ、未使用ページカウンタ等が構築されている。

#### [00005]

データの更新(書き込み)動作は追記型書き込みが行われる。追記型書き込みが行われると、更新前のデータが格納されている物理ページアドレス、例えば" 0 × 0 0 6 0 B 0 "に相当するページ領域はアドレス変換テーブルの物理アドレスフィールドから削除され、外からアクセスできなくなる。即ち、無効化される。

#### [0006]

しかし、それらにはデータが書き込まれており、そのままでは空き領域として使用することもできない。このような書き込みを何度も繰り返すと、多くの無効ページ領域が発生する。それらは再度空き領域として使用できるよう、消去して回復させる必要がある(コンパクションに相当)。また、その場合、消去ブロック" 0 × 0 0 6 0 "に残された他の有効データは退避させる必要がある。

# [0007]

この回復処理は、例えばまず対象ブロック内の有効データを、更新の際と同様に一旦ページバッファに読み出してから、他のブロックの空き領域に追記で書き込んでいき、それによって実質的な退避を行えばよい。すなわち、有効ページを仮更新することで、その元領域を全て無効化する。その後、対象ブロックを消去することによって、回復処理が実施される。

#### [0008]

この回復処理は記憶装置の待機時やシステムのアイドル時に自動的に実施することがで

きる。しかし、多くの未使用領域が残っており僅かな無効ページしか存在しない状態で無理に回復処理を実行しても、殆ど効果は得られない。一方、いつまでも回復処理をせぬまま放置すると、未使用領域が不足し、アクセスレイテンシィとなる。そのため、本当に回復処理を実行すべきか否かを判定し、かつ回復処理の対象ブロックを選定する機能がシステムのどこかに必要になる。

[0009]

そこで、上記回復処理と、それを実行するか否かの判定、及び回復対象ブロックの選択をひとまとまりの作業グループとみなして回復シーケンスとし、記憶装置に実装しておく。そして、ホストシステムからの回復処理実行コマンドに応じて、あるいは記憶装置が待機状態に入った際に自動的に回復シーケンスを実行する。

10

【先行技術文献】

【特許文献】

[ 0 0 1 0 ]

【 特 許 文 献 1 】 特 開 2 0 0 8 - 1 4 6 2 5 3 号 公 報 ( 段 落 0 0 5 0 、 0 0 5 1 、 0 0 6 6 、 0 0 6 7 、 0 0 7 2 - 0 0 7 5 )

【発明の概要】

【発明が解決しようとする課題】

[ 0 0 1 1 ]

このように特許文献 1 記載の装置は、回復処理と、それを実行するか否かの判定、及び回復対象ブロックの選択をひとまとまりの回復シーケンスとして記憶装置に実装しておき、システムからの回復処理実行コマンドに応じて回復シーケンスを実行するようにしている。フラッシュメモリにおける無効ページの回復作業によってフラッシュメモリの使用効率を向上させることができる。

20

[0012]

しかしながら、この装置では回復シーケンスはCPUのソフトウェアとして実行されている為、1つの回復シーケンスを実行するにもCPUは複数の処理を行う必要がある。回復処理の実行中にソフトウェアの介入が複数はいることによりCPUの処理性能が劣化し、システム全体でのパフォーマンス低下が生じるという課題がある。

【課題を解決するための手段】

[0013]

本発明の一態様による半導体記憶装置は、

不揮発性メモリからデータを読み出すリード手段と、

前記リード手段により読み出されたデータをユーザデータと管理データとに分離する分離手段と、

前記不揮発性メモリのライトアドレスを管理するライトポインタ情報により示されるアドレスを前記分離手段により分離された管理データに対して加えてライトコマンドを発行し、前記分離手段により分離されたデータを前記不揮発性メモリに書き込むライト手段と、を具備する。

【発明の効果】

[0014]

40

50

30

本発明の一態様によれば、CPUからの1コマンドでコンパクション動作が実行されるので、CPUの処理負荷の低減が可能になるとともに、途中でソフトウェア処理が介入せず、システム全体の処理能力が高くなる。

【図面の簡単な説明】

[ 0 0 1 5 ]

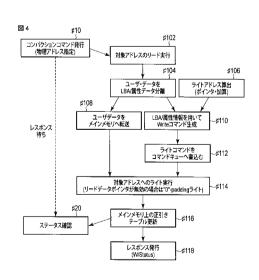

【図1】本発明の実施の形態に係るフラッシュメモリコントローラおよびその周辺システムでの位置づけを示すブロック図。

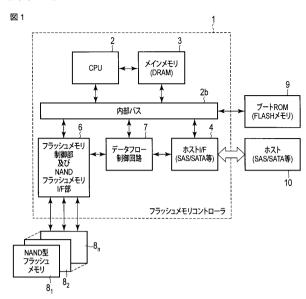

【図2】フラッシュメモリコントローラ内のフラッシュメモリ制御部、データフロー制御 回路の詳細なブロック図である。

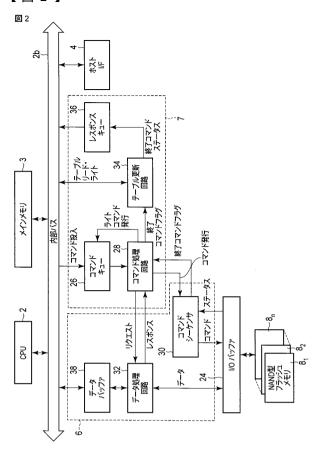

【図3】コンパクション動作時のNANDフラッシュメモリコントローラのデータの流れ

を示す図。

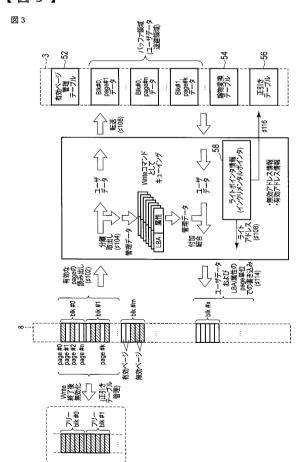

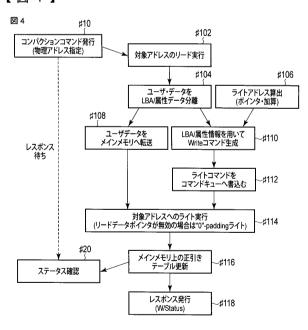

【 図 4 】 N A N D フラッシュメモリコントローラのコンパクション動作を示すフローチャート。

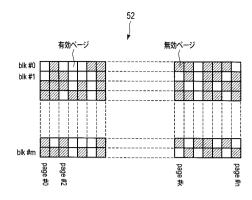

【図5】メインメモリに設けられる有効ページ管理テーブルを示す図。

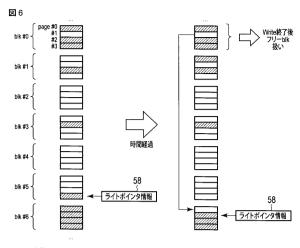

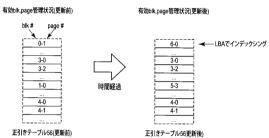

【図6】NANDフラッシュメモリコントローラのコンパクション動作に関する追記ポインタの動作と正引きテーブルの更新を示す図。

【発明を実施するための形態】

[0016]

以下、図面を参照して本発明の実施の形態について詳細に説明する。

[0017]

図 1 は一実施形態の構成を示すブロック図である。本実施形態は複数の不揮発性メモリ、例えば N A N D 型フラッシュメモリ 8  $_1$  、 8  $_2$  、 ... 8  $_n$  を含む。 N A N D 型フラッシュメモリ 8  $_1$  、 8  $_2$  、 ... 8  $_n$  を含む。 N A N D 型フラッシュメモリ 8  $_1$  、 8  $_2$  、 ... 8  $_n$  の各々は例えば 2 ~ 1 6 個のメモリチップからなる。 N A N D 型フラッシュメモリ 8  $_1$  、 8  $_2$  、 ... 8  $_n$  はフラッシュメモリコントローラ 1 に接続される。フラッシュメモリコントローラ 1 は内部バス 2 bに接続された 1 C P U 1 と、メインメモリ 1 と、フラッシュメモリ制御部及び 1 A 1 D フラッシュメモリ 1 / 1 F 1 6 と、データフロー制御回路 1 と、ホスト 1 / 1 F 1 4 とを具備する。

[0018]

フラッシュメモリ制御部及びNANDフラッシュメモリI/F部6はNAND型フラッシュメモリ8 $_1$ 、8 $_2$ 、…8 $_n$ に接続され、NAND型フラッシュメモリ8 $_1$ 、8 $_2$ 、…8 $_n$ へのアクセスを制御する。具体的には、フラッシュメモリ制御部及びNANDフラッシュメモリI/F部6はNAND型フラッシュメモリ8 $_1$ 、8 $_2$ 、…8 $_n$ に対してアドレスやデータ制御を行う。フラッシュメモリ制御部及びNANDフラッシュメモリI/F部6はCPU2からのコマンドを受理し、NAND型フラッシュメモリ8 $_1$ 、8 $_2$ 、…8 $_n$ とメインメモリ3間のデータ転送を実施する。フラッシュメモリ制御部及びNANDフラッシュメモリI/F部6は内部で論理プロックアドレス(Logical Block Address: LBA)情報や各種属性(フラグ)情報を保持する。

[0019]

ホストI/F4はプロトコルSASやSATAによりホストシステム10に接続され、データフロー制御回路7を介して、ホスト・NAND型フラッシュメモリ間でやりとりされるデータのフロー制御を行う。ホストI/F4はホストシステム10からはLBAでアクセスされる。メインメモリ3は例えばDRAMが使用され、退避データや正引きテーブル、論物変換テーブルを格納する。

[0020]

フラッシュメモリコントローラ 1 の内部バス 2 bには外付けのブート R O M 9 も接続される。ブート R O M 9 は一例としてフラッシュメモリが使用され、ファームウェアを含む。ファームウェアは C P U 2 を使用し、フラッシュメモリ制御部及び N A N D フラッシュメモリエ / F 部 6 内部への I / O コマンドアクセスにより N A N D型フラッシュメモリ 8 1、82、…8nへのリードコマンド、ライトコマンドの発行を行う。ファームウェアは R O M 9 にプログラムされた内容が、システム電源起動時に、 C P U 2 内部の一時記憶部もしくはメインメモリ 3 に転送されて動作するものとする。

[0021]

図2はフラッシュメモリ制御部及びNANDフラッシュメモリI/F部6、データフロー制御回路7の詳細なブロック図である。フラッシュメモリ制御部及びNANDフラッシュメモリI/F部6はI/Oバッファ24を介してNAND型フラッシュメモリ8ヘアクセスする。内部バス2bからのライトデータはデータバッファ38、データ処理回路32を介してI/Oバッファ24に供給され、I/Oバッファ24からのリードデータはデータ処理回路32、データバッファ38を介して内部バス2bに供給される。

[0022]

10

20

30

40

50

20

30

40

50

CPU2からのリードコマンド、ライトコマンドは内部バス2 bを介してコマンドキュー26に書き込まれる(コマンド投入)。ここでのコマンドフォーマットはフラッシュメモリ制御部及びNANDフラッシュメモリI/F部6が処理しやすいフォーマットであればよく、ハードウェア実装に依存している。本特許の要ではないためここでは特に言及しないコマンドキュー26にコマンドが投入されると、コマンド処理回路28はエントリされたコマンドをコマンドキュー26から取り出し、コマンドシーケンサ30にコマンドを発行して起動をかける。

### [0023]

CPU2からコンパクションコマンドが発行されると、コマンドキュー26にはリードコマンドとして投入される。コマンド処理回路28はコマンドキュー26からリードコマンドを取り出して、コマンドシーケンサ30にコマンド発行をして起動をかけ、その後、エ/Oバッファ24を介して、NANDフラッシュメモリ8の該当ブロックからデータをリードする。NANDフラッシュメモリ8内の各ブロックの各ページのデータが有効であるか無効であるかはメインメモリ3内の有効ページ管理テーブル(後述)により管理されており、CPU2は有効なデータを含むページに対してのみリードアドレスを与え、有効なデータのみリードする。

#### [0024]

コマンドシーケンサ30は複数のNAND型フラッシュメモリからいずれかの選択と、NAND型フラッシュメモリ8へのアクセスコマンド発行を行う。コマンに対してメインのはNAND型フラッシュメモリ8のアクセスの際、データ処理回路32に対してメるので、データ処理回路32に対してが完了すると、伴わなンサ30に終了ないで、カーケンサ30に終了するとコマンドシーケンサ30に終了コマンド処理回路32はデータをはアーブル更新回路34に対して終了コマンドを送付する。コマンド処理回路32はNAND型フラッとに対して終了コマンドを送付する。この時、データ処理回路32はNAND型フラッとに対して終了コマンドを送付する。この時、データとしBA情報、その他後続めるによりにではです。属性データとに分離し、LBA/属性データをコマンド処理回路28に終了レルのよの手に変す。属性データの一例としては、データにエラー訂正符号化(ECC)によるデータのチェックを行うか否かを示す情報やデータ長、暗号の有無などがある。

#### [0025]

コマンドキュー 2 6 内の全てのリードコマンド終了後に、コマンドキュー 2 6 内のライト処理 (後続のライト処理と称する) へ移る。この詳細は図3を参照して後述する。コマンド処理回路 2 8 はコマンドキュー 2 6 内のライトコマンドを取り出して、コマンドシーケンサ3 0 にコマンド発行をして起動をかける。その後、コマンド処理回路 2 8 は I / O バッファ 2 4 を介して N A N D フラッシュメモリ 8 へのデータのライトを行う。この時、コマンドシーケンサ3 0 は、データ処理回路 3 2 に対してメインメモリ 3 からのデータ転送要求を実施し、LBA / 属性データ、ライトアドレスを用いて、データライト処理を行う。ライトアドレスはフラッシュメモリコントローラ 1 内で生成する。具体的には、ホスト1 0 から供給されたLBAに基づいて後述の論物変換テーブルから物理アドレスが計算される。ここでは、ライトアドレスは追記型アルゴリズムに従い生成される。追記型アルゴリズムは、1 回のライト時に順次ポインタを順次進める制御をするため、ライトアドレスは容易に生成できる。

# [0026]

データ処理回路 3 2 はデータ転送が完了すると、コマンドシーケンサ 3 0 に終了レスポンスを返す。その後、コマンド処理回路 2 8 は終了通知と正引きテーブル更新に必要な情報をテーブル更新回路 3 4 は終了したコマンドに係るメインメモリ 3 上のテーブル更新を実施するモジュールであり、ライト終了時の有効ページ管理ビットマップテーブルの更新処理及び、その他の管理テーブルの更新処理を実施する。更新処理の詳細は後述する。テーブル更新回路 3

20

30

40

50

4 はすべての処理を終了後、レスポンスキュー36に終了コマンドとステータスを送信してハードウェアとしてのコマンド処理が完了する。CPU2はレスポンスキュー36をリードすることによってコマンド実行結果を確認することができる。

### [0027]

図 3 はこのように構成されたフラッシュメモリコントローラ 1 (特に、フラッシュメモリ制御部及び N A N D フラッシュメモリ I / F 部 6 とデータフロー制御回路 7 )によるコンパクション動作の際のデータの流れの概要を示す図であり、図 4 は図 3 の動作を実現するためのフラッシュメモリコントローラ 1 のフローチャートである。図 4 は左側の 2 つのブロック (ブロック # 1 0 2 ~ # 1 1 8 ) がフラッシュメモリコントローラ 1 (ハードウェア)の処理である。

#### [0028]

NAND型フラッシュメモリ8  $_1$ 、8  $_2$ 、…8  $_n$  は所定のバイト、例えば2112バイト毎に1ページを構成し、所定のページ、例えば64ページが1ブロックを構成する。6 方のなページと無効なページが混在する。有効なページとは、当該ページに書き込まれたデータが存在し、そのデータは有効であることを示している。無効なページとは、当該ページ内に何も書き込まれていないか、もしくは当該ページ内に何も書き込まれていないか、もしくは当該ページ内に回れる。このNAND型フラッシュメモリ8、8  $_2$ 、…8  $_n$  の各ページが有効(Valid)か無効(Invalid)かを示すための有効ページ管理テーブル52がメインメモリ3内に設けられる。このテーブルである。NAND型フラッシュメモリ8、8  $_2$ 、…8  $_n$  への書き込みが正常に終了し、コマンドステータスをCPUに返す前に、有効ページ管理テーブル52の有効/無効状態が更新される。メインメモリ3には論理アドレスと物理アドレスの変換のための論物テーブル54、論理アドレスの順に有効ブロックの物理アドレスを並べた正引きテーブル56が設けられる。

#### [0029]

先ず、CPU2からNAND型フラッシュメモリ8の物理アドレスを指定してコンパクションコマンドを発行する(図4のブロック#10)。この後、CPU10はコンパクション処理が終了するまで、待機状態となる。実際の実施例として、コンパクション処理中にホストからのデータアクセス(ユーザーデータリードまたはライト)が発生することが想定されるため、コンパクションの処理は割り込みによる検知を行っている。また、コンパクション処理の最中にコンパクション対象領域のデータが無効になるケースも存在し、その場合の処理を考慮している。

# [0030]

メモリコントローラ 1 は N A N D 型フラッシュメモリ 8 の指定された物理アドレスのブロックの有効ページからデータを読み出す(ブロック # 1 0 2 )。 読み出されたデータはデータ処理回路 3 2 によりユーザデータと管理データ(LBA/属性データ)とに分離される(ブロック # 1 0 4 )。 ユーザデータはメインメモリ 3 のユーザデータ領域に転送される(ブロック # 1 0 8 )。

#### [0031]

一方、追記ポインタ 5 8 (図 2 のコマンドシーケンサ 3 0 に含まれる)によりライトアドレスが算出される(ブロック # 1 0 6)。コマンド処理回路 2 8 はライトアドレスと L B A / 属性データとからライトコマンドを生成し(ブロック # 1 1 0 )、ライトコマンドをコマンドキュー 2 6 に投入する(ブロック # 1 1 2 )。

#### [0032]

コマンドキュー 2 6 から読み出されたライトコマンドにより、メインメモリ 3 から転送されたユーザデータが N A N D型フラッシュメモリ 8 の指定されたアドレスにライトされる(ブロック # 1 1 4 )。ブロック # 1 1 4 のように、ブロック # 1 0 2 で実行したリードコマンドに後続してコマンドキュー 2 6 に配置されているライトコマンドの実行(後続のライト)時には、読み出したリードデータが、ライトを行う直前の時点で有効か無効か

20

30

40

50

を再度判断する必要がある。これは、リード時は有効であったデータがコンパクション処理中に無効に変化する可能性があり、それに対応するためである。例えば、ホスト10によりユーザデータを上書きした場合は、NANDフラッシュメモリ8上では以前にユーザデータが書かれていた物理アドレスとは別の物理アドレスにデータが書き込みされ、以前にユーザデータが書かれていたNANDフラッシュメモリ8の物理アドレスにそれまでに存在していたデータ(リードデータ)は無効となる。このため、読み出したリードデータが無効になっている時は、無効なデータ(オール " 0 ")が書き込まれる(" 0 " パディング)。これは、今回の書き込みは無効であるので、書き込み動作自体を中止しても良いが、コマンドキュー26からライトコマンドが取り出された後に中止するのはハードウェア的に困難な場合があるので、書き込むデータを意味の無いものにして実質的に書き込みを中止し、ハードウェアの処理を簡単にするためである。

[0033]

ブロック # 1 1 6 でテーブル更新回路 3 4 はメインメモリ 3 内の正引きテーブル 5 6 を更新する。その後、ブロック # 1 1 8 でテーブル更新回路 3 4 はレスポンスキュー 3 6 に終了コマンドとステータスを送信してハードウェアとしてのコマンド処理が完了する。

[0034]

CPU2はレスポンスキュー36をリードすることによってコマンド実行ステータスを確認する(ブロック#20)。

[0035]

図6は追記ポインタ58の動作と正引きテーブル56の更新の様子を示す図である。ある時刻において、NANDフラッシュメモリ8の有効/無効ページの状態と正引きテーブル56の状態は図6の左側の状態(更新前)であるとする。追記ポインタ58の指す位置はブロック#5のページ#3とする。この状態において、コンパクション対象としてブロック#0が選ばれたとする。コンパクション対象は有効ページ管理テーブル52の情報に基づいて、有効ページを含み最も数が小さいブロックが選ばれる。有効ページ管理テーブル52は2次元のビットマップ状に配置されているので、コンパクション対象候補のブロックの列挙を容易に行える。ブロック#0の有効ページはページ#1のみである。

[0036]

コンパクションのためには、最初にフリーブロック(全てのページが無効)#6を取得して、そのブロックの先頭ページから順番に有効ページのデータをコピーする。ブロック#6のページ#0にコピーした状態を図6の右側に示す。次に、コピーしたデータ(ブロック#0のページ#1)のLBAの位置がコピー先の位置(ブロック#6のページ#0)を示すように正引きテーブル56を更新する。で、有効ページがなくなったブロック#0をフリーブロック扱いにするために有効ページででで、ブロック#0のページ#1を無効化)する。ブロック#0のページ#1のデータをブロック#6のページ#1を無効化)する。ブロック#0のページ#1のデータをブロック#6のページ#0にことにより、追記ポインタ58はブロック#6のページ#0に、ブロック#5のページ#3が無効から有効に変わったのは、コンパクション処理と平行して動作したユーザーWrite処理によるものである。本特許の本質でない為、詳細は割愛するが、追記ポインタの1加算、それまで追記ポインタが指していた位置へのデータ書き込み、正引きテーブルの更新(blk#5-page#3)された様子も示されている。図では、かつLBA重複があったため、そのLBA(blk#1-page#0)が無効にされた様子も示されている。

[0037]

以上説明したように、第1の実施の形態によれば、NANDフラッシュメモリ8のコンパクション処理を行う場合、CPU2は物理ブロックアドレスを指定してコンパクションコマンドを発生するだけでよい。フラッシュメモリコントローラ1はこのコマンドを受けると、当該ブロックから有効ページのデータをリードし、リードデータから分離した管理データ(LBA/属性データ)に対して追記ポインタにより発生したライトアドレスを追加してライトコマンドを発生する。このライトコマンドに対してメインメモリからのユーザデータを付加・結合してNANDフラッシュメモリ8の指定アドレスへページ単位で書

20

30

き込む。書き込み後、データがリードされたブロックが無効化され、正引きテーブルが更新される。これにより、CPU2からの1コマンドでコンパクション動作(リード処理、後続のライト処理、正引きテーブルの更新処理)を行うことができCPU処理負荷の低減が可能となるとともに、途中でソフトウェ処理が入らないため、システム全体の処理能力が速くなる。

## [0038]

書き込みの直前にリードデータが無効となっているか否かを確認し、無効となっているときは、書き込みを中止する、あるいは無効なデータを書き込むことにより、コンパクションの最中にリードデータが無効になった場合にも対処できる。

### [0039]

なお、この発明は、上記実施形態そのままに限定されるものではなく、実施段階ではその要旨を逸脱しない範囲で構成要素を変形して具体化できる。また、上記実施形態に開示されている複数の構成要素の適宜な組み合せにより種々の発明を形成できる。例えば、実施形態に示される全構成要素から幾つかの構成要素を削除してもよい。更に、異なる実施形態に亘る構成要素を適宜組み合せてもよい。例えば、本発明はホスト10により制御される半導体ドライブ(Solid State Drive: SSD)を例に説明したが、これに限らず、シリコンオーディオ機器、メモリメディアカードなどに適用することもできる。

#### [0040]

また、本発明は、コンピュータに所定の手段を実行させるため、コンピュータを所定の手段として機能させるため、コンピュータに所定の機能を実現させるため、あるいはプログラムを記録したコンピュータ読取り可能な記録媒体としても実施することもできる。

#### [0041]

また、コンパクションに限らず、不揮発性メモリの特性である一定期間毎のデータ移動 (定期リフレッシュ)への応用や、RMW(リード・モディファイ・ライト)への応用も可能 である。

#### 【符号の説明】

# [0042]

1 ... フラッシュメモリコントローラ、2 ... C P U、3 ... メインメモリ、4 ... ホストI / F、6 ... フラッシュメモリ制御部及びN A N D フラッシュメモリI / F部、7 ... データフロー制御回路、8 ... N A N D 型フラッシュメモリ、9 ... ブート R O M、2 6 ... コマンドキュー、2 8 ... コマンド処理回路、3 0 ... コマンドシーケンサ、3 2 ... データ処理回路、3 4 ... テーブル更新回路。

# 【図1】

# 【図2】

# 【図3】

# 【図4】

# 【図5】

図 5

# 【図6】

# フロントページの続き

(74)代理人 100095441

弁理士 白根 俊郎

(74)代理人 100084618

弁理士 村松 貞男

(74)代理人 100103034

弁理士 野河 信久

(74)代理人 100119976

弁理士 幸長 保次郎

(74)代理人 100153051

弁理士 河野 直樹

(74)代理人 100140176

弁理士 砂川 克

(74)代理人 100158805

弁理士 井関 守三

(74)代理人 100124394

弁理士 佐藤 立志

(74)代理人 100112807

弁理士 岡田 貴志

(74)代理人 100111073

弁理士 堀内 美保子

(74)代理人 100134290

弁理士 竹内 将訓

(72)発明者 松山 元彦

東京都港区芝浦一丁目 1番 1号 株式会社東芝内

(72)発明者 福田 徹

東京都港区芝浦一丁目1番1号 株式会社東芝内

(72)発明者 茂呂 祐行

東京都港区芝浦一丁目1番1号 株式会社東芝内

F ターム(参考) 5B060 AA10 AA14 AA15