## (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2008-147355 (P2008-147355A)

(43) 公開日 平成20年6月26日 (2008.6.26)

| (51) Int.Cl. | FI                           |           |                       | テーマコード (参考)       |  |  |  |  |  |  |  |  |

|--------------|------------------------------|-----------|-----------------------|-------------------|--|--|--|--|--|--|--|--|

| HO1L 29/78   | (2006.01) HO1L               | 29/78 3   | 0 1 G                 | 4 M 1 O 4         |  |  |  |  |  |  |  |  |

| HO1L 21/28   | <b>(2006.01)</b> HO1L        | 21/28 3   | O 1 S                 | 5 F 1 4 O         |  |  |  |  |  |  |  |  |

| HO1L 29/423  | <b>(2006.01)</b> HO1L        | 29/58     | G                     |                   |  |  |  |  |  |  |  |  |

| HO1L 29/49   | <b>(2006.01)</b> HO1L        | 29/44     | S                     |                   |  |  |  |  |  |  |  |  |

| HO1L 29/41   | (2006. 01)                   |           |                       |                   |  |  |  |  |  |  |  |  |

|              |                              | 審査請求 オ    | 院請求 請求項の              | 数 22 O L (全 19 頁) |  |  |  |  |  |  |  |  |

| (21) 出願番号    | 特願2006-331909 (P2006-331909) | (71) 出願人  | 000005821             |                   |  |  |  |  |  |  |  |  |

| (22) 出願日     | 平成18年12月8日 (2006.12.8)       | :         | 松下電器産業株               | 式会社               |  |  |  |  |  |  |  |  |

|              |                              |           | 大阪府門真市大学              | 字門真1006番地         |  |  |  |  |  |  |  |  |

|              |                              | (74)代理人   | 100077931             |                   |  |  |  |  |  |  |  |  |

|              |                              |           | 弁理士 前田                | <i>I</i> I        |  |  |  |  |  |  |  |  |

|              |                              | ` /       | 100110939             |                   |  |  |  |  |  |  |  |  |

|              |                              |           | 弁理士 竹内 5              | <del>E</del>      |  |  |  |  |  |  |  |  |

|              |                              | 1 ( ) ( ) | 100110940             | <del>-</del> -    |  |  |  |  |  |  |  |  |

|              |                              |           |                       | 高久                |  |  |  |  |  |  |  |  |

|              |                              | 1 \ /     | 100113262             | <del></del>       |  |  |  |  |  |  |  |  |

|              |                              | 1         |                       | 佑二                |  |  |  |  |  |  |  |  |

|              |                              | 1 \ /     | 100115059             | <b>六</b>          |  |  |  |  |  |  |  |  |

|              |                              | 1         | 弁理士 今江 〕<br>100115691 | 克実                |  |  |  |  |  |  |  |  |

|              |                              | 1 ` '     |                       | <b>举</b> 由        |  |  |  |  |  |  |  |  |

|              |                              |           | 弁理士 藤田 第              | 篤史<br>最終頁に続く      |  |  |  |  |  |  |  |  |

|              |                              |           |                       |                   |  |  |  |  |  |  |  |  |

## (54) 【発明の名称】半導体装置および半導体装置の製造方法

## (57)【要約】

【課題】均一なシリサイド層を有し、低抵抗化されたゲート電極を備えた半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板101内に形成された低濃度ソース・ドレイン領域106および高濃度ソース・ドレイン領域106的よび高濃度ソース・ドレイン領域106の間に位置する領域の上に形成されたゲート絶縁膜102と、ゲート絶縁膜102上に形成され、金属シリサイドからなるゲート電極103とを備えている。ゲート電極103の上部におけるゲート長は、ゲート電極の他の部分におけるゲート長よりも大きくなっている。

## 【選択図】図1

#### 【特許請求の範囲】

### 【請求項1】

半導体基板と、

前記半導体基板内に形成されたソース領域およびドレイン領域と、

前記半導体基板のうち平面的に見て前記ソース領域と前記ドレイン領域の間に位置する領域の上に形成されたゲート絶縁膜と、

前記ゲート絶縁膜上に形成され、金属シリサイドからなるゲート電極とを備えており、 前記ゲート電極の上部におけるゲート長が前記ゲート電極の他の部分におけるゲート長 よりも大きい半導体装置。

#### 【請求項2】

前記ゲート電極は、上部が逆テーパー形状である請求項1に記載の半導体装置。

#### 【請求項3】

前記半導体基板上で且つ前記ゲート電極の側方に形成された層間絶縁膜と、

前記ゲート電極の側面と前記層間絶縁膜との間に形成された第1のサイドウォール膜とをさらに備えている請求項1または2に記載の半導体装置。

#### 【請求項4】

前記第1のサイドウォール膜と前記ゲート電極の下部の側面との間から前記半導体基板と前記第1のサイドウォール膜との間にわたって形成された第2のサイドウォール膜をさらに備えている請求項3に記載の半導体装置。

#### 【請求項5】

前記金属シリサイドは、チタンシリサイド、コバルトシリサイド、ニッケルシリサイド、タングステンシリサイド、タンタルシリサイド、ハフニウムシリサイド、ジルコニウムシリサイド、モリブデンシリサイド、および白金シリサイドのうちいずれか1つを少なくとも含んでいる請求項1~4のうちいずれか1つに記載の半導体装置。

#### 【請求項6】

半導体基板上のゲート電極形成領域に、下から順に積層されたゲート絶縁膜、ゲート電極形成膜、および第1の絶縁膜を形成する工程(a)と、

前記第1の絶縁膜をマスクとして前記半導体基板内にイオン注入することにより、ソース領域およびドレイン領域を形成する工程(b)と、

前記半導体基板の全面に第2の絶縁膜を堆積させた後、前記第1の絶縁膜の上面が露出するまで前記第2の絶縁膜を除去する工程(c)と、

前記第1の絶縁膜を除去して、前記ゲート電極形成膜に達する開口部を形成する工程(d)と、

前記第2の絶縁膜のうち前記開口部に面する部分の上部を除去することにより、上面のゲート長方向の幅が他の部分のゲート長方向の幅よりも大きい逆テーパー形状に前記開口部を加工する工程(e)と、

前記半導体基板の全面に金属膜を堆積させ、前記開口部に前記金属膜を埋め込む工程(f)と、

前記半導体基板を加熱して前記金属膜と前記ゲート電極形成膜を反応させることにより、前記ゲート絶縁膜上に金属シリサイドからなるゲート電極を形成する工程(g)とを備えている半導体装置の製造方法。

#### 【請求項7】

前記工程(e)では、スパッタ法により前記開口部を逆テーパー形状に加工する請求項6に記載の半導体装置の製造方法。

#### 【請求項8】

前記工程(e)では、酸素ガスを用いた反応性イオンエッチング法により、前記開口部を逆テーパー形状に加工する請求項6に記載の半導体装置の製造方法。

## 【請求項9】

前記工程(e)は、前記開口部を逆テーパー形状に加工した後、前記ゲート電極形成膜上に形成された不純物を除去する工程を含んでいる請求項8に記載の半導体装置の製造方

10

20

30

00

40

法。

### 【請求項10】

前記工程(a)の後に、前記ゲート電極形成膜および前記第1の絶縁膜の側面にサイドウォール膜を形成する工程(h)をさらに備えており、

前記工程(b)では、前記サイドウォール膜および前記第1の絶縁膜をマスクとして、前記ソース領域および前記ドレイン領域を形成し、

前記工程(e)では、前記第2の絶縁膜および前記サイドウォール膜のうち前記開口部に面する部分の上部をそれぞれ除去する請求項6~9のうちいずれか1つに記載の半導体装置の製造方法。

#### 【請求項11】

前記工程(a)で形成される前記第1の絶縁膜の膜厚は、前記ゲート絶縁膜、前記ゲート電極形成膜、および前記第1の絶縁膜の膜厚の和の1/3以上1/2以下である請求項6~10のうちいずれか1つに記載の半導体装置の製造方法。

### 【請求項12】

前記金属膜は、チタン、コバルト、ニッケル、タングステン、タンタル、ハフニウム、 ジルコニウム、モリブデン、および白金のうちいずれか 1 つを少なくとも含んでいる請求 項 6 ~ 1 1 のうちいずれか 1 つに記載の半導体装置の製造方法。

## 【請求項13】

半導体基板上のゲート電極形成領域に、下から順に積層されたゲート絶縁膜、ゲート電極形成膜、および第1の絶縁膜を形成する工程(a)と、

前記半導体基板上且つ前記ゲート電極形成膜および前記第1の絶縁膜の側方に設けられた第1のサイドウォール膜と、前記第1のサイドウォール膜と前記ゲート電極形成膜および前記第1の絶縁膜の側面との間に設けられ、第1のサイドウォール膜と膜質が異なる第2のサイドウォール膜とを形成する工程(b)と、

前記第1の絶縁膜、前記第1のサイドウォール膜、および前記第2のサイドウォール膜をマスクとして前記半導体基板内にイオン注入することにより、ソース領域およびドレイン領域を形成する工程(c)と、

前記半導体基板の全面に第2の絶縁膜を堆積させた後、前記第1の絶縁膜の上面が露出するまで前記第2の絶縁膜を除去する工程(d)と、

前記第1の絶縁膜を除去し、且つ、前記第2のサイドウォール膜の一部を除去することで、前記ゲート電極形成膜に達する開口部を形成する工程(e)と、

前記半導体基板の全面に金属膜を堆積させ、前記開口部に前記金属膜を埋め込む工程(f)と、

前記半導体基板を加熱して前記金属膜と前記ゲート電極形成膜を反応させることにより、前記ゲート絶縁膜上に金属シリサイドからなるゲート電極を形成する工程(g)とを備えている半導体装置の製造方法。

## 【請求項14】

前記工程(e)の後、且つ、前記工程(f)の前に、前記第2の絶縁膜および前記第1のサイドウォール膜のうち前記開口部が形成された部分の上部をそれぞれ除去することにより、上面のゲート長方向の幅が他の部分のゲート長方向の幅よりも大きい逆テーパー形状に前記開口部を加工する工程をさらに備えている請求項13に記載の半導体装置の製造方法。

### 【請求項15】

前記工程(e)では、前記第1の絶縁膜と前記第2のサイドウォール膜の一部とを、同時に除去する請求項13または14に記載の半導体装置の製造方法。

## 【請求項16】

前記第1の絶縁膜と前記第2のサイドウォール膜とは、互いに同じ材料から構成されている請求項15に記載の半導体装置の製造方法。

### 【請求項17】

前記工程(b)では、前記第1のサイドウォール膜は前記第2のサイドウォール膜より

10

20

30

40

も高温で形成される請求項13または14に記載の半導体装置の製造方法。

#### 【請求項18】

前記工程(e)では、前記第1の絶縁膜を除去した後、前記第2のサイドウォール膜の一部を除去する請求項17に記載の半導体装置の製造方法。

#### 【請求項19】

前記工程(e)では、フッ酸を用いたエッチングにより前記第2のサイドウォール膜の一部を除去し、

前記第2のサイドウォール膜の選択比は、前記第1のサイドウォール膜に対して2以上である請求項17または18に記載の半導体装置の製造方法。

## 【請求項20】

前記第2のサイドウォール膜はNSG膜からなる請求項19に記載の半導体装置の製造方法。

#### 【請求項21】

前記工程(a)で形成される前記第1の絶縁膜の膜厚は、前記ゲート絶縁膜、前記ゲート電極形成膜、および前記第1の絶縁膜の膜厚の和の1/3以上1/2以下である請求項13~20のうちいずれか1つに記載の半導体装置の製造方法。

### 【請求項22】

前記金属膜は、チタン、コバルト、ニッケル、タングステン、タンタル、ハフニウム、 ジルコニウム、モリブデン、および白金のうちいずれか 1 つを少なくとも含んでいる請求 項 1 3 ~ 2 1 のうちいずれか 1 つに記載の半導体装置の製造方法。

【発明の詳細な説明】

## 【技術分野】

### [0001]

本 発 明 は 、 シ リ サ イ ド 層 を 有 す る ゲ ー ト 電 極 を 備 え た 半 導 体 装 置 お よ び そ の 製 造 方 法 に 関 す る 。

## 【背景技術】

## [0002]

近年、半導体集積回路装置の高速化を実現する有効な手段として、ゲート電極上に高融点金属シリサイドを形成することで、ゲート電極および拡散層の低抵抗化を図る方法が用いられている。以下、図5を参照しながら従来のゲート電極上にシリサイド層を形成する方法について説明する。図5は、従来のシリサイド層の形成方法を示す断面図である。

#### [00003]

まず、図 5 ( a ) に示すように、シリコン基板 1 の不活性領域にフィールド酸化膜 2 を、シリコン基板 1 の活性領域に膜厚が 5 ~ 1 0 n m のゲート酸化膜 3 をそれぞれ公知の技術を用いて形成する。次に、ゲート酸化膜 3 上に例えば多結晶シリコンからなるゲート電極 4 を 1 5 0 ~ 2 0 0 n m 程度の膜厚で形成した後、シリコン窒化膜 5 を 5 0 n m 程度の膜厚で形成する。

## [0004]

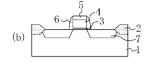

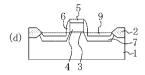

次に、図5(b)に示すように、フォトリソグラフィー工程と異方性エッチングとによりパターニングすることで、シリコン基板1上の所定の領域に、下から順に積層されたゲート酸化膜3、ゲート電極4、およびシリコン窒化膜5を形成する。続いて、CVD(Chemical Vapor Deposition)法により、シリコン基板1の全面に酸化膜(図示せず)を100m程度の膜厚で形成した後、異方性エッチングにより酸化膜を除去することで、ゲート酸化膜3、ゲート電極4、およびシリコン窒化膜5の側面上に酸化膜からなる側壁6を形成する。次いで、シリコン窒化膜5および側壁6をマスクにしてイオン注入を行い、その後、熱処理することで、拡散層7を形成する。

## [0005]

次に、図5(c)に示すように、バッファードフッ酸により拡散層7上に形成された自然酸化膜(図示せず)を除去した後、スパッタ法によりチタン層8を30nm程度の膜厚で形成する。

10

20

30

40

#### [0006]

続いて、図5(d)に示すように、窒素雰囲気中で650~700 で短時間の熱処理(RTA)を行うことによりチタン層8と拡散層7を反応させ、拡散層7上に厚さが約50nmのチタンシリサイド層9を形成する。次に、残存した未反応のチタン層8をアンモニア水と過酸化水素水の混合液を用いて除去する。

#### [00007]

次に、図 5 ( e ) に示すように、シリコン基板 1 の全面に層間絶縁膜 1 0 を 5 0 0 n m 程度の膜厚で形成する。その後、化学的機械的研磨 ( C M P : Chemical Mechanical Poli shing) により、シリコン窒化膜 5 の表面が露出するまで層間絶縁膜 1 0 を平坦化する。 この時、ゲート電極 4 上に形成されたシリコン窒化膜 5 が C M P ストッパーになる。

[00008]

次に、図 5 (f)に示すように、シリコン窒化膜 5 を熱リン酸により除去する。続いて、バッファードフッ酸によりゲート電極 4 上に形成された自然酸化膜(図示せず)を除去した後、スパッタ法によりシリコン基板 1 の全面にチタン層 1 1 を 5 0 n m 程度の膜厚で形成する。

[0009]

次いで、図5(g)に示すように、窒素雰囲気中で650~700 で短時間の熱処理(RTA)を行うことで、チタン層11と多結晶シリコン(ゲート電極4)とを反応させ、ゲート電極上に厚さが約80nmのチタンシリサイド層12を形成する。次に、残存した未反応のチタン層11をアンモニア水と過酸化水素水の混合液により除去する。その後、窒素雰囲気中で800~850 で短時間の熱処理(RTA)を行い、チタンシリサイド層9、12を低抵抗化する。

[0010]

以後、層間絶縁膜をシリコン基板1の全面に堆積して、コンタクト開口部を設けた後、 アルミ電極を形成することで、MOS型トランジスタを作製することができる。

[0011]

以上のような工程を繰り返し行うことにより、ゲート電極の表面上に形成されたシリサイド層の膜厚を厚くすることができ、ゲート電極をさらに低抵抗化することができる(特許文献 1 参照)。

【特許文献 1 】特開平 1 1 - 1 2 1 7 4 5 号公報

【発明の開示】

【発明が解決しようとする課題】

[ 0 0 1 2 ]

しかしながら、ゲート電極4に達する開口部に金属膜を堆積する工程(図5(f))では、半導体装置の微細化に伴って開口部のアスペクト比が大きくなると、開口部に堆積させる金属膜のカバレッジ不良が発生しやすくなり、ゲート電極4上に均一なシリサイド層を形成することが難しくなる。その結果、トランジスタの特性不良の増加や品質のばらつきの増大などが生じるおそれがある。

[0013]

上記の不具合に鑑み、本発明は、均一なシリサイド層を有し、低抵抗化されたゲート電極を備えた半導体装置およびその製造方法を提供することを目的とする。

【課題を解決するための手段】

[0014]

上記課題を解決するために、本発明の半導体装置は、半導体基板と、前記半導体基板内に形成されたソース領域およびドレイン領域と、前記半導体基板のうち平面的に見て前記ソース領域と前記ドレイン領域の間に位置する領域の上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成され、金属シリサイドからなるゲート電極とを備えており、前記ゲート電極の上部におけるゲート長が前記ゲート電極の他の部分におけるゲート長よりも大きくなっている。

[0015]

10

20

30

40

この構成によれば、ゲート電極の上部のゲート長が他の部分のゲート長よりも大きくなっているため、金属シリサイドからなるゲート電極を形成する際には、シリサイド化させる層に金属膜を比較的容易に堆積させることができる。これにより、本発明の半導体装置では、均一な金属シリサイドから構成され、低抵抗化されたゲート電極を備えることができる。その結果、トランジスタの特性不良や品質のばらつきが抑制された半導体装置を実現することができる。

#### [0016]

また、上記の構成においては、ゲート電極全体が金属シリサイドから構成されたメタルゲート電極が備えられているため、ゲート電極の上面上にシリサイド層が設けられた従来の半導体装置と比較して、電流駆動力の低下を抑制することができ、信頼性の高い半導体装置を実現することができる。

[0017]

また、前記半導体基板上で且つ前記ゲート電極の側方に形成された層間絶縁膜と、前記ゲート電極の側面と前記層間絶縁膜との間に形成された第1のサイドウォール膜とをさらに備えていてもよい。なお、この場合、前記第1のサイドウォール膜と前記ゲート電極の下部の側面との間に形成された第2のサイドウォール膜をさらに備えていてもよい。

[0018]

上記の構成では、ゲート電極の側方に第1のサイドウォール膜および第2のサイドウォール膜が備えられているため、ゲート電極は、上部のゲート長が下部のゲート長よりも大きい逆向きの凸形状となっている。この構成によれば、ゲート電極を形成する際には、第2のサイドウォール膜がゲート電極の上部の側面上には形成されていないため、シリサイド化させる層により均一に金属膜を形成しやすくなり、均一な金属シリサイドからなるゲート電極が得られる。その結果、十分に低抵抗化されたゲート電極を備え、トランジスタの特性不良が抑制された半導体装置を実現することができる。

[0019]

また、前記金属シリサイドは、チタンシリサイド、コバルトシリサイド、ニッケルシリサイド、タングステンシリサイド、タンタルシリサイド、ハフニウムシリサイド、ジルコニウムシリサイド、モリブデンシリサイド、および白金シリサイドのうちいずれか 1 つを少なくとも含んでいることが好ましい。

[ 0 0 2 0 ]

本発明の半導体装置の第1の製造方法は、半導体基板上のゲート電極形成領域に、下から順に積層されたゲート絶縁膜、ゲート電極形成膜、および第1の絶縁膜を形成する工程(り、ソース領域およびドレイン領域を形成する工程(り)と、前記半導体基板の全面に第2の絶縁膜を堆積させた後、前記第1の絶縁膜の上面が露出するまで前記第2の絶縁膜を除去して、前記ゲート電極形成膜に達する開口部を形成する工程(d)と、前記第2の絶縁膜のうち前記開口部に面する部分の上部に所記第3の絶縁膜のうち前記開口部に面する部とにより、上面のゲート長方向の幅が他の部分のゲート長方のの幅よりも大度に逆テーパー形状に前記開口部を加工する工程(e)と、前記半導体基板の全面に金属膜を埋積させ、前記開口部に前記金属膜を埋め込む工程(f)と、前記ゲート電極を形成度をしたより、前記ゲート絶縁膜上に金属シリサイドからなるゲート電極を形成する工程(g)とを備えている。

[0021]

この方法によれば、工程(e)において、開口部を逆テーパー形状に加工することにより、金属膜のカバレッジを向上させることができるため、その後の工程で開口部に比較的均一に金属膜を堆積させることができる。これにより、工程(g)における熱処理時に金属膜とゲート電極形成膜とを効率良く且つムラなく反応させることができるため、均一な金属シリサイドからなるゲート電極を形成することができる。その結果、本発明の半導体装置の製造方法を用いると、低抵抗化されたゲート電極を備え、トランジスタの特性不良や品質のばらつきが抑制された半導体装置を作製することが可能となる。

10

20

30

40

#### [0022]

また、本発明の半導体装置の第1の製造方法を用いると、工程(d)で形成される開口部のアスペクト比が大きくなっても、工程(e)で逆テーパー形状に加工することにより、均一な金属シリサイド層を形成することが可能である。このため、トランジスタの縮小化によりゲート長が微細化されても、十分な膜厚を有するシリサイド層を形成することができ、低抵抗化されたゲート電極を備え、高速動作が可能な半導体装置を作製することができる。

## [0023]

さらに、上記の方法で形成されたゲート電極は、上部のゲート長が下部のゲート長よりも大きい逆テーパー形状となっているため、例えばゲート電極上にコンタクトを形成する場合は、一定のゲート長を有するゲート電極を備えた従来の半導体装置に比べてコンタクトを形成可能な領域がより大きくなる。これにより、半導体装置が微細化されても、コンタクトを形成する際に用いるマスクの位置合わせがしやすく、比較的容易にゲート電極上にコンタクトを形成することができる。

#### [0024]

なお、前記工程(a)で形成される前記第1の絶縁膜の膜厚は、前記ゲート絶縁膜、前記ゲート電極形成膜、および前記第1の絶縁膜の膜厚の和の1/3以上1/2以下であると好ましい。この場合、後の工程で第1の絶縁膜が除去された領域に、ゲート電極形成膜全体を十分にシリサイド化させるために必要な金属膜を堆積させることができ、全体が均一な金属シリサイドから構成されたゲート電極を得ることができる。

#### [0025]

また、前記金属膜は、チタン、コバルト、ニッケル、タングステン、タンタル、ハフニウム、ジルコニウム、モリブデン、および白金のうちいずれか1つを少なくとも含んでいることが好ましい。

#### [0026]

また、本発明の半導体装置の第2の製造方法では、半導体基板上のゲート電極形成領域に、下から順に積層されたゲート絶縁膜、ゲート電極形成膜、および第1の絶縁膜を縁膜の側方に設けられた第1のサイドウォール膜と、前記第1のサイドウォール膜とが前記第1のサイドウォール膜とが前記第1のサイドウォール膜とで、前記第1のサイドウォール膜とを形成する工程(b)と、前記第1の絶縁前記第1の絶縁前記第2のサイドウォール膜をマスクとしまり、前記第1のサイドウォール膜、および前記第2のサイドウォール膜をマスクとのでは、前記第1の絶縁前記第1の地域を表して、前記半導体基板の全面に第2の絶縁では、前記第1の絶縁に正の、前記半導体基板の全面に金属膜をは、前記第1の絶縁に正記の表に、前記第2のサイドウォール膜の一部記第1の絶縁に正記に、前記第2のサイドウォール膜の一部記第1の絶縁に記頭の表に、前記第2のサイドウォール膜の一部記半導体基板を加熱して前記金属膜を埋め込む工程(6)と、前記半導体基板を加熱して前記金属膜に記前に前記金属膜を埋め込む工程(6)と、前記ゲート絶縁膜上に金属シリサイドからなるゲート電極を形成する工程(8)とを備えている。

## [0027]

この方法によれば、工程(e)において第1の絶縁膜と共に前記第2のサイドウォール膜の一部とを除去することで、第2のサイドウォール膜の幅の分だけ開口部のゲート長方向における幅を広げることができる。これにより、本発明の半導体装置の第1の製造方法と比較して、より均一に金属膜を堆積させることが可能となるため、均一な金属シリサイドからなり、低抵抗化されたゲート電極を形成することができる。

### 【発明の効果】

## [0028]

本発明の半導体装置によれば、金属シリサイドからなる低抵抗化されたゲート電極を備えているため、トランジスタの特性不良や品質のばらつきが抑制された半導体装置を実現

10

20

30

40

することができる。

### [0029]

また、本発明の半導体装置の製造方法によれば、金属膜のカバレッジを向上させ、均一な金属シリサイドからなるゲート電極を形成することができるため、低抵抗なゲート電極を備え、トランジスタの品質などのばらつきが抑制された半導体装置を作製することができる。さらに、トランジスタの縮小化によりゲート長が微細化されても、均一な金属シリサイドからなり、十分な膜厚を有するゲート電極が得られるため、高速動作が可能な半導体装置を実現することができる。

【発明を実施するための最良の形態】

### [0030]

(第1の実施形態)

以下、本発明の第1の実施形態に係る半導体装置およびその製造方法について、図面を参照しながら説明する。図1(a)~(i)は、本発明の第1の実施形態に係る半導体装置の製造方法を示す断面図である。最初に、図1(i)を用いて本実施形態の半導体装置の構成を簡単に説明する。

#### [ 0 0 3 1 ]

図1(i)に示すように、本実施形態の半導体装置は、シリコンなどからなる半導体基板101と、半導体基板101内にそれぞれ形成された低濃度ソース・ドレイン領域106および高濃度ソース・ドレイン領域108と、半導体基板101のうち平面的に見て低濃度ソース・ドレイン領域106の間に位置する領域の上に形成されたゲート絶縁膜102と、ゲート絶縁膜102上に形成され、金属シリサイドからなるゲート電極103と、半導体基板101上で且つゲート電極103の側方に形成された層間絶縁膜109と、層間絶縁膜109とゲート電極103との間に設けられたサイドウォール膜107とを備えている。

#### [0032]

なお、ゲート絶縁膜102、層間絶縁膜109、およびサイドウォール膜107の材料としては、それぞれ例えばシリコン酸化膜が用いられる。

#### [0033]

ここで、本実施形態の半導体装置では、ゲート電極 1 0 3 は例えばニッケルシリサイドなどの金属シリサイドから構成されている。さらに、ゲート電極 1 0 3 の上部は、その上面のゲート長方向の幅が他の部分のゲート長方向の幅よりも広い逆テーパー形状となっている。

#### [0034]

なお、本実施形態の半導体装置では、ゲート電極 1 0 3 全体が金属シリサイドから構成されたメタルゲート電極が備えられているため、ゲート電極の上面上にシリサイド層が設けられた従来の半導体装置に比べ、電流駆動力の低下を抑制することができ、信頼性の高い半導体装置を実現することができる。

### [0035]

次に、本実施形態の半導体装置の製造方法について図 1 ( a ) ~ (i ) を用いて説明する。

## [0036]

まず、図1(a)に示すように、例えばシリコンからなる半導体基板101上に、厚さが3nmのシリコン酸化膜などからなるゲート絶縁膜102を形成する。その後、半導体基板101の温度を例えば610 として、ゲート絶縁膜102上に厚さが80nmの例えば多結晶シリコンからなるゲート電極形成膜103aを堆積する。次いで、ゲート電極形成膜103a上に、厚さが50nmの例えばシリコン窒化膜からなる第1の絶縁膜104を堆積する。ここで、第1の絶縁膜104の厚みは、ゲート絶縁膜102、ゲート電極形成膜103a、および第1の絶縁膜104の厚みの和の1/3以上1/2以下であることが望ましい。

## [0037]

10

20

30

20

30

40

50

次に、図1(b)に示すように、リソグラフィー工程とドライエッチング工程により、 半導体基板101上のゲート電極形成領域に第1の絶縁膜104、ゲート電極形成膜10 3 a、およびゲート絶縁膜102を残すようにパターニングする。

#### [0038]

次に、図1(c)に示すように、第1の絶縁膜104をマスクにして、半導体基板10 1内にn型不純物であるヒ素をドーズ量3×10<sup>14</sup>ions/cm<sup>2</sup>、注入エネルギー 20keVの注入条件でイオン注入することにより、低濃度ソース・ドレイン領域106 を形成する。

## [0039]

続いて、図1(d)に示すように、半導体基板101上の全面にCVD法により厚さが140nmの例えばシリコン酸化膜を堆積させた後、異方性エッチングによりシリコン酸化膜をエッチバックすることで、ゲート絶縁膜102、ゲート電極形成膜103a、および第1の絶縁膜104の側面上にシリコン酸化膜からなるサイドウォール膜107を形成する。その後、第1の絶縁膜104およびサイドウォール膜107をマスクにして、n型不純物であるヒ素をドーズ量4×10<sup>15</sup>ions/cm²、注入エネルギー50keVの注入条件でイオン注入することにより、高濃度ソース・ドレイン領域108を形成する

## [0040]

次に、図1(e)に示すように、半導体基板101の全面にCVD法により厚さ700nmのシリコン酸化膜などからなる層間絶縁膜109を堆積した後、化学的機械的研磨(СMP)にて第1の絶縁膜104が露出するまで研磨を行う。この時、例えばプラテン回転数が100rpmで、圧力が4.0psi(27.6kPa)となる条件を用いる。

### [0041]

次に、図1(f)に示すように、第1の絶縁膜104をウェットエッチングにて除去して、ゲート電極形成膜103aに達する開口部110を形成する。この時、ウェットエッチングの溶液としてリン酸を用いて、例えば150 で処理を行う。これにより、第1の絶縁膜104の選択比をゲート電極形成膜103aに対して100以上にすることができるため、選択的に第1の絶縁膜104を除去することができる。

### [0042]

## [ 0 0 4 3 ]

次に、図1(h)に示すように、半導体基板101の全面にスパッタ法により厚さが30nmの例えばニッケルからなる金属膜112を堆積する。

### [0044]

続いて、図1(i)に示すように、550 ~600 の温度範囲で、短時間の熱処理 (RTA)を行うことにより、ゲート電極形成膜103aとニッケル(金属膜112)を 反応させる。これにより、ゲート絶縁膜102上に、厚さが例えば130nmのニッケル

20

30

40

50

シリサイドからなるゲート電極103を形成することができる。その後、未反応で残存しているニッケルを塩酸または硫酸に過酸化水素を添加した液体を用いて、ウェットエッチングにより選択的に除去する。次いで、750 ~800 の温度範囲で、さらに短時間の熱処理(RTA)を行うことにより、ニッケルシリサイドからなるゲート電極103を低抵抗化する。以後、所定の方法により、本実施形態の金属シリサイドからなるゲート電極を備えた半導体装置を製造することができる。

#### [0045]

なお、上述の半導体装置の製造方法で挙げたプロセス条件は一例であり、これに限定されるものではない。

#### [0046]

本実施形態の半導体装置の製造方法では、図1(g)に示す工程において、開口部110を逆テーパー形状111に加工することにより、金属膜112のカバレッジを向上させることができるため、その後の工程で開口部110に金属膜112を比較的均一に堆積させることができる。これにより、熱処理時に金属膜112と多結晶シリコン(ゲート電極形成膜103a)を効率的に且つムラなく反応させることができるため、均一な金属シリサイドからなるゲート電極103を形成することができる。その結果、本実施形態の半導体装置の製造方法では、低抵抗化されたゲート電極を備え、トランジスタの特性不良や品質のばらつきが抑制された半導体装置を作製することが可能となる。

### [0047]

また、本実施形態の半導体装置の製造方法によれば、図1(f)で形成される開口部のアスペクト比が大きくなっても、逆テーパー形状に加工することにより、均一な金属シリサイド層を形成することが可能である。このため、トランジスタの縮小化により実効的なゲート長が微細化されても、十分な膜厚を有するシリサイド層を形成することができ、低抵抗化されたゲート電極を備え、高速動作が可能な半導体装置を作製することができる。ここで、「実効的なゲート長」とは、チャネル長に影響を及ぼすゲート電極103下部のゲート長を意味するものとする。

## [0048]

また、本実施形態の製造方法により形成されたゲート電極103は、上部のゲート長が下部のゲート長よりも大きい逆テーパー形状となっているため、例えばゲート電極上にコンタクトを形成する場合、一定のゲート長を有するゲート電極を備えた従来の半導体装置に比べてコンタクトを形成することができる領域がより大きくなっている。これにより、半導体装置が微細化されても、コンタクトを形成する際に用いるマスクの位置合わせがしやすく、比較的容易にゲート電極上にコンタクトを形成することができる。

## [ 0 0 4 9 ]

なお、本実施形態の製造方法では、金属膜が、チタン、コバルト、ニッケル、タングステン、タンタル、ハフニウム、ジルコニウム、モリブデン、および白金のうち少なくとも1つを含んでいることが好ましい。

### [0050]

## (第2の実施形態)

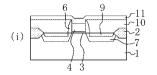

以下、本発明の第2の実施形態に係る半導体装置の製造方法について、図面を参照しながら説明する。ここで、本実施形態の半導体装置は、上述の第1の実施形態の半導体装置と同様な構成を有しているが、その製造方法の一部が異なっている。従って、本実施形態では、半導体装置の構成についての説明は省略する。図2(a)~(i)は、本発明の第1の実施形態に係る半導体装置の製造方法を示す断面図である。なお、図2(g)に示す工程以外はそれぞれ第1の実施形態の製造方法と同様であるため、ここでは簡単に説明する。

#### [0051]

最初に、図2(a)、(b)に示すように、半導体基板101上に、ゲート絶縁膜102、ゲート電極形成膜103a、および第1の絶縁膜104を順次形成した後、ゲート絶縁膜102、ゲート電極形成膜103a、および第1の絶縁膜104を半導体基板101

20

30

40

50

上のゲート電極形成領域に残すようにパターニングする。

#### [0052]

続いて、図2(c)、(d)に示すように、第1の絶縁膜104をマスクにして、半導体基板101内に低濃度ソース・ドレイン領域106を形成した後、ゲート絶縁膜102、ゲート電極形成膜103a、および第1の絶縁膜104の側面にサイドウォール膜107を形成する。

#### [0053]

次に、図2(e)、(f)に示すように、第1の絶縁膜104およびサイドウォール膜107をマスクにして所定の条件でイオン注入することにより、高濃度ソース・ドレイン領域108を形成する。続いて、半導体基板101の全面に層間絶縁膜109を堆積した後、第1の絶縁膜104が露出するまでCMPにて研磨する。その後、第1の絶縁膜104を除去し、開口部110を形成する。

#### [0054]

続いて、図2(g)に示すように、サイドウォール膜107および層間絶縁膜109のうち開口部110に面する部分の上部を反応性イオンエッチング法にて除去し、開口部110を逆テーパー形状211に加工する。この時の反応性イオンエッチング法の条件は、2周波反応性イオンエッチング式のドライエッチング装置を用いて、流量を400sccm(6.68×10・6m³/s)、圧力を3Paとして酸素ガスを供給し、ソース電極のパワーを900W、バイアス電極のパワーを600Wとして、60秒間処理を行うにより、開口部110を逆テーパー形状211に加工することができる。なお、この時により、開口部110のゲート長方向における幅の増加量(t1)が例えば片側20nmずつ広がり、肩落ち量(t2)は例えば20nmとなる。また、この時、開口部110における一方の上端から他方の上端までの距離を×、ゲート電極形成膜103aの両側方にそれぞれ設けられたサイドウォール膜107の下面の幅の和をy、ゲート電極形成膜103aのゲート長方向の幅をzとすると、(1/8y+z)<×<(y+z)であることが望ましい。

## [0055]

ここで、上述の酸素を用いた反応性イオンエッチングを行うと、多結晶シリコン(ゲート電極形成膜103a)の表面が酸化され、例えば酸化シリコンからなる生成物212が形成される。従って、本工程では、反応性イオンエッチングを行った後に、フッ酸洗浄を行うことで、酸化シリコンからなる生成物212を除去する。なお、この時、生成物212と併せて、ゲート電極形成膜103a上に残存する窒素などの不純物も同時に除去される。

## [0056]

次いで、図2(h)、(i)に示すように、半導体基板101の全面に例えばニッケルからなる金属膜112を堆積させる。続いて、短時間の熱処理により、ゲート電極形成膜103aとニッケル(金属膜112)とを反応させることで、ゲート絶縁膜102上にニッケルシリサイドからなるゲート電極103を形成する。その後、未反応で残存しているニッケルをウェットエッチングにより選択的に除去する。次いで、短時間の熱処理を行うことにより、ニッケルシリサイドからなるゲート電極103を低抵抗化する。以後、所定の方法により、本実施形態の金属シリサイド層からなるゲート電極103を備えた半導体装置を製造することができる。

### [0057]

なお、上述の半導体装置の製造方法で挙げたプロセス条件は一例であり、これに限定されるものではない。

## [0058]

本実施形態の半導体装置の製造方法では、第1の実施形態と同様に、図2(g)に示す工程において、開口部110を逆テーパー形状211に加工することにより、金属膜112のカバレッジを向上させることができるため、開口部110に金属膜112を比較的均一に堆積させることができる。これにより、熱処理時に金属膜112と多結晶シリコン(

ゲート電極形成膜103a)を効率的に且つムラなく反応させることができるため、実効的なゲート長が短くなった場合でも、均一な金属シリサイドからなるゲート電極103を形成することができる。その結果、本実施形態の半導体装置の製造方法では、低抵抗化されたゲート電極を備え、トランジスタの特性不良や品質のばらつきが抑制された半導体装置を作製することが可能となる。

### [0059]

また、本実施形態の半導体装置の製造方法では、図2(g)に示す工程は、開口部21 0を逆テーパー形状211に加工した後に、反応性イオンエッチングにより形成された生成物212を除去する工程を有している。この生成物212を除去する工程を有していることで、ゲート電極形成膜103aの表面に残留する窒素などの不純物も併せて取り除くことができるため、該不純物が金属膜と多結晶シリコンとの反応を阻害するのを抑制することができ、より均一な金属シリサイドからなるゲート電極を形成することが可能となる

10

## [0060]

### (第3の実施形態)

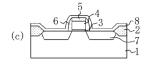

以下、本発明の第3の実施形態に係る半導体装置およびその製造方法について、図面を参照しながら説明する。図3(a)~(i)は、本発明の第3の実施形態に係る半導体装置の製造方法を示す断面図である。最初に、図3(i)を用いて本実施形態の半導体装置の構成を簡単に説明する。

## [0061]

20

図3(i)に示すように、本実施形態の半導体装置は、シリコンなどからなる半導体基板101と、半導体基板101内にそれぞれ形成された低濃度ソース・ドレイン領域106および高濃度ソース・ドレイン領域108と、半導体基板101のうち平面的に見て低濃度ソース・ドレイン領域106の間に位置する領域の上に形成されたゲート絶縁膜102と、ゲート絶縁膜102上に形成され、金属シリサイドからなるゲート電極303と、半導体基板101上で且つゲート電極303の側方に設けられた第1のサイドウォール膜308と、第1のサイドウォール膜308と、第1のサイドウォール膜308とが一ト電極303の下部の側面との間に形成された第2のサイドウォール膜308の側方に形成された層間絶縁膜109とを備えている。

[0062]

30

なお、第1のサイドウォール膜308および第2のサイドウォール膜307の材料としては、それぞれシリコン酸化膜およびシリコン窒化膜が用いられる。また、ゲート絶縁膜102および層間絶縁膜109の材料としては、それぞれ例えばシリコン酸化膜が用いられる。

## [0063]

本実施形態の半導体装置では、ゲート電極 3 0 3 は例えばニッケルシリサイドなどの金属シリサイドから構成されている。さらに、ゲート電極 3 0 3 は、上部の幅が下部の幅よりも広い逆向きの凸形状となっている。

### [0064]

次に、図3(a)~(i)を用いて本実施形態の半導体装置の製造方法について説明する。なお、図3(a)~(c)に示す工程は上述の第1の実施形態と同様であるため、ここでは簡単に述べる。

40

### [0065]

最初に、図3(a)~(c)に示すように、半導体基板101上に、ゲート絶縁膜102、ゲート電極形成膜103a、および第1の絶縁膜104を順次形成した後、ゲート絶縁膜102、ゲート電極形成膜103a、および第1の絶縁膜104を半導体基板101上のゲート電極形成領域に残すようにパターニングする。続いて、第1の絶縁膜104をマスクにして、半導体基板101内に低濃度ソース・ドレイン領域106を形成する。

#### [0066]

次に、図3(d)に示すように、半導体基板101の全面にCVD法により例えばシリ

20

30

40

50

コン酸化膜、シリコン窒化膜を順次堆積させる。その後、異方性エッチングによりシリコン窒化膜およびシリコン酸化膜をエッチバックすることにより、半導体基板 1 0 1 上且つゲート電極形成膜 1 0 3 a および第 1 の絶縁膜 1 0 4 の側方に設けられた第 1 のサイドウォール膜 3 0 8 とゲート電極形成膜 1 0 3 a および第 1 の絶縁膜 1 0 4 の側面との間に設けられた第 2 のサイドウォール膜 3 0 7 とをそれぞれ形成する。

### [0067]

次いで、図3(e)、(f)に示すように、第1の絶縁膜104、第1のサイドウォール膜308、および第2のサイドウォール膜307をマスクにして所定の条件でイオン注入することにより、高濃度ソース・ドレイン領域108を形成する。その後、半導体基板101の全面に層間絶縁膜109を堆積した後、第1の絶縁膜104が露出するまでCMPにて研磨する。

#### [0068]

次に、図3(g)に示すように、第1の絶縁膜104と第2のサイドウォール膜307の上部とをウェットエッチングにより同時に除去し、ゲート電極形成膜103aに達する開口部311を形成する。この時、ウェットエッチングの溶液としてリン酸を用い、例えば150 で処理を行う。これにより、窒化シリコン膜からなる第1の絶縁膜104および第2のサイドウォール膜307の選択比をゲート電極形成膜103aに対して100以上にすることができるため、選択的に第1の絶縁膜104および第2のサイドウォール膜307の一部をそれぞれ除去することができる。

#### [0069]

次いで、図3(h)、(i)に示すように、半導体基板101の全面に例えばニッケルからなる金属膜112を堆積させる。続いて、短時間の熱処理により、ゲート電極形成膜103aとニッケル(金属膜112)とを反応させることで、ゲート絶縁膜102上にニッケルシリサイドからなるゲート電極303を形成する。その後、未反応で残存しているニッケルをウェットエッチングにより選択的に除去する。次いで、短時間の熱処理を行うことにより、ニッケルシリサイドからなるゲート電極303を低抵抗化する。以後、所定の方法により、本実施形態の金属シリサイド層からなるゲート電極303を備えた半導体装置を製造することができる。

### [0070]

なお、上述の半導体装置の製造方法で挙げたプロセス条件は一例であり、これに限定されるものではない。

#### [0071]

本実施形態の半導体装置の製造方法では、図3(g)に示す工程において、第1の絶縁膜104と共に第2のサイドウォール膜307の一部を除去することで、第2のサイドウォール膜307の幅の分だけ開口部311の幅を広げることができる。これにより、第1の絶縁膜104のみを除去して開口部を形成する場合に比べて、開口部311により均一に金属膜112を堆積させることができる。そのため、熱処理時に金属膜112と多結晶シリコン(ゲート電極形成膜103a)を効率的に且つムラなく反応させることができ、実効的なゲート長が短くなった場合でも、均一な金属シリサイドからなるゲート電極303を形成することができる。その結果、本実施形態の半導体装置の製造方法では、低抵抗化されたゲート電極を備え、トランジスタの特性不良や品質のばらつきが抑制された半導体装置を作製することが可能となる。

## [ 0 0 7 2 ]

また、本実施形態の製造方法により形成されたゲート電極303における上面のゲート 長は、第1の実施形態に挙げたゲート電極103に比べて小さくなっている。このため、 例えば高濃度ソース・ドレイン領域108上にコンタクトを形成する場合には、第1の実 施形態の半導体装置と比較してコンタクトを形成可能な領域がより大きくなる。その結果 、半導体装置が微細化されても、コンタクトを形成する際に用いるマスクの位置合わせが しやすく、比較的容易にソース・ドレイン領域上にコンタクトを形成することができる。

20

30

40

50

#### [0073]

なお、本実施形態の半導体装置の製造方法では、図3(g)に示す工程の後、且つ、図3(h)示す工程の前に、層間絶縁膜109および第1のサイドウォール膜308のうち開口部311に面する部分の上部をそれぞれ除去する工程をさらに備えていてもよい。この場合、開口部311を上面のゲート長方向の幅が他の部分のゲート長方向の幅よりも大きい逆テーパー形状に加工することができるため、後の工程で金属膜112のカバレッジをさらに向上させることができ、より均一な金属シリサイドからなるゲート電極303を作製することが可能となる。

### [0074]

また、本実施形態の製造方法では、第1の絶縁膜104と第2のサイドウォール膜307とが互いに同じ材料から構成されていることが好ましい。これにより、図3(g)に示す工程において、比較的容易に第1の絶縁膜104と第2のサイドウォール膜307とをエッチング除去することができる。

### [0075]

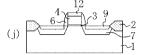

### (第4の実施形態)

以下、本発明の第4の実施形態に係る半導体装置の製造方法について、図面を参照しながら説明する。ここで、本実施形態の半導体装置は、第1のサイドウォール膜と同じ材料からなる第2のサイドウォール膜を備えており、これ以外の部分は上述の第3の実施形態の半導体装置と同様な構成を有している。従って、半導体装置の構成についての説明は省略する。また、本実施形態の半導体装置の製造方法においては、上述の第3の実施形態の半導体装置の製造方法と一部の工程が異なっている。図4(a)~(j)は、本発明の第4の実施形態に係る半導体装置の製造方法を示す断面図である。なお、図4(a)~(c)に示す工程はそれぞれ第1の実施形態の製造方法と同様であるため、ここでは簡単に説明する。

### [0076]

最初に、図4(a)~(c)に示すように、半導体基板101上に、ゲート絶縁膜10 2、ゲート電極形成膜103a、および第1の絶縁膜104を順次形成した後、ゲート絶 縁膜102、ゲート電極形成膜103a、および第1の絶縁膜104を半導体基板101 上のゲート電極形成領域に残すようにパターニングする。続いて、第1の絶縁膜104を マスクにして、半導体基板101内に低濃度ソース・ドレイン領域106を形成する。

### [0077]

次に、図4(d)に示すように、半導体基板101の全面にCVD法により例えばシリコン酸化膜(第1のシリコン酸化膜)を、オゾンガスとTEOS(テトラエトキシシラン)ガスを用いて、300~400の範囲の温度で成膜する。その後、第1のシリコン酸化膜上に、第2のシリコン酸化膜をオゾンガスとTEOS(テトラエトキシシラン)ガスを用いて、700~900の範囲の温度で成膜する。続いて、異方性エッチングにより第1のシリコン酸化膜および第2のシリコン酸化膜をエッチバックすることにより、半導体基板101上且つゲート電極形成膜103aおよび第1の絶縁膜104の側方に設けられた第1のサイドウォール膜408と、第1のサイドウォール膜408とゲート電極形成膜103aおよび第1の絶縁膜104の側面との間に設けられた第2のサイドウォール膜407とをそれぞれ形成する。

#### [0078]

次いで、図4(e)、(f)に示すように、第1の絶縁膜104、第1のサイドウォール膜408、および第2のサイドウォール膜407をマスクにして所定の条件でイオン注入することにより、高濃度ソース・ドレイン領域108を形成する。その後、半導体基板101の全面に層間絶縁膜109を堆積した後、第1の絶縁膜104が露出するまでCMPにて研磨する。

## [0079]

次に、図4(g)に示すように、第1の絶縁膜104をウェットエッチングにより除去する。この時、ウェットエッチングの溶液としてリン酸を用い、例えば150 で処理を

行う。これにより、窒化シリコン膜からなる第1の絶縁膜104の選択比をゲート電極形成膜103aに対して100以上にすることができるため、選択的に第1の絶縁膜104を除去することができる。

[0800]

続いて、図4(h)に示すように、第2のサイドウォール膜407の上部をウェットエッチングにより、例えばゲート電極形成膜103aの上面と同じ高さになるまで除去する。この時、ウェットエッチングの溶液として、例えばフッ酸(100%)を純水で500倍希釈した溶液を用いる。これにより、第2のサイドウォール膜307の選択比を第1のサイドウォール膜308に対して、3以上にすることができるため、選択的に第2のサイドウォール膜307のみを除去することができる。なお、ここでは、ゲート電極形成膜103aの上面と同じ高さになるように第2のサイドウォール膜407をエッチングしたが、これに限定されるものではなく、第2のサイドウォール膜407の上面がゲート電極形成膜103aの上面よりも高くなっても低くなってもよい。

[0081]

次いで、図4(i)、(j)に示すように、半導体基板101の全面に例えばニッケルからなる金属膜112を堆積させる。続いて、短時間の熱処理により、ゲート電極形成膜103aとニッケル(金属膜112)とを反応させることで、ゲート絶縁膜102上にニッケルシリサイドからなるゲート電極303を形成する。その後、未反応で残存しているニッケルをウェットエッチングにより選択的に除去する。次いで、短時間の熱処理を行うことにより、ニッケルシリサイドからなるゲート電極303を低抵抗化する。以後、所定の方法により、本実施形態の金属シリサイド層からなるゲート電極303を備えた半導体装置を製造することができる。

[0082]

なお、上述の半導体装置の製造方法で挙げたプロセス条件は一例であり、これに限定されるものではない。

[0083]

本実施形態の半導体装置の製造方法では、図4(g)に示す工程で第1の絶縁膜104を除去した後、図4(h)に示す工程で第2のサイドウォール膜407の上部も除去することができ、上部の幅が下部の幅よりも広い逆凸形状の開口部411を形成することができる。これにより、開口部411により均一に金属膜112を堆積させることができるため、実効的なゲート長が短くなった場合でも、熱処理時に金属膜112と多結晶シリコン(ゲート電極形成膜103a)とを効率的に且つムラなく反応させて均一な金属シリサイドからなるゲート電極303を形成することができる。その結果、本実施形態の半導体装置の製造方法では、低抵抗化されたゲート電極を備え、トランジスタの特性不良や品質のばらつきが抑制された半導体装置を作製することが可能となる。

[0084]

なお、本実施形態の半導体装置の製造方法では、図4(d)に示す工程において、第1のサイドウォール膜408は第2のサイドウォール膜407よりも高温で形成されることが好ましい。この場合、第1のサイドウォール膜408と第2のサイドウォール膜407とが互いに異なる膜質で形成されるため、図4(h)に示す工程において所定のエッチング条件に設定することで、第2のサイドウォール膜407のみを選択的にエッチングすることが可能となる。

【産業上の利用可能性】

[0085]

本発明の半導体装置およびその製造方法は、シリサイド層を有するゲート電極を備えた半導体装置の微細化に有用である。

【図面の簡単な説明】

[0086]

【図1】(a)~(i)は、本発明の第1の実施形態に係る半導体装置の製造方法を示す 断面図である。 10

20

30

40

【図2】(a)~(i)は、本発明の第2の実施形態に係る半導体装置の製造方法を示す断面図である。

【図3】(a)~(i)は、本発明の第3の実施形態に係る半導体装置の製造方法を示す断面図である。

【図4】(a)~(j)は、本発明の第4の実施形態に係る半導体装置の製造方法を示す断面図である。

【図5】従来の半導体装置におけるシリサイド層の形成方法を示す断面図である。

## 【符号の説明】

4 1 1

開口部

## [0087]

| 1 |   |   |   | ٠. | –          | ٠. | # | += |      |    |   |   |   |   |     |     |    |   |  |  |  |  |  |  |  | 10 |

|---|---|---|---|----|------------|----|---|----|------|----|---|---|---|---|-----|-----|----|---|--|--|--|--|--|--|--|----|

| 1 |   |   |   |    | リコ         |    |   |    | /V   | 中  |   |   |   |   |     |     |    |   |  |  |  |  |  |  |  | 10 |

| 2 |   |   |   | -  | ィー         |    | - |    | . –  | 脵  |   |   |   |   |     |     |    |   |  |  |  |  |  |  |  |    |

| 3 |   |   |   |    | - ト<br>·   |    |   |    |      |    |   |   |   |   |     |     |    |   |  |  |  |  |  |  |  |    |

| 4 |   |   |   |    | <b>-</b> ト |    |   |    | n++- |    |   |   |   |   |     |     |    |   |  |  |  |  |  |  |  |    |

| 5 |   |   |   |    | リコ         | ン  | 至 | 化  | 膜    |    |   |   |   |   |     |     |    |   |  |  |  |  |  |  |  |    |

| 6 |   |   |   | 側  |            |    |   |    |      |    |   |   |   |   |     |     |    |   |  |  |  |  |  |  |  |    |

| 7 |   |   |   |    | 散層         |    |   |    |      |    |   |   |   |   |     |     |    |   |  |  |  |  |  |  |  |    |

| 8 |   |   |   |    | タン         |    |   |    |      |    |   |   |   |   |     |     |    |   |  |  |  |  |  |  |  |    |

|   | ` | 1 | 2 |    |            |    |   |    |      | IJ | サ | 1 | ド | 層 |     |     |    |   |  |  |  |  |  |  |  |    |

| • | 0 |   |   |    | 層 間        |    |   | 膜  |      |    |   |   |   |   |     |     |    |   |  |  |  |  |  |  |  | 00 |

|   | 1 |   |   |    | チタ         |    |   |    |      |    |   |   |   |   |     |     |    |   |  |  |  |  |  |  |  | 20 |

|   | 2 |   |   |    | チタ         |    |   |    |      | 1  | ド | 層 |   |   |     |     |    |   |  |  |  |  |  |  |  |    |

|   | 0 |   |   |    |            | 導  |   |    |      |    |   |   |   |   |     |     |    |   |  |  |  |  |  |  |  |    |

|   | 0 |   |   |    |            |    |   |    | 縁    | 膜  |   |   |   |   |     |     |    |   |  |  |  |  |  |  |  |    |

| 1 | 0 | 3 |   |    |            | _  | - | _  | .—   |    |   |   |   |   |     |     |    |   |  |  |  |  |  |  |  |    |

|   | 0 |   | а |    |            |    |   |    | 極    |    | 成 | 膜 |   |   |     |     |    |   |  |  |  |  |  |  |  |    |

| 1 | 0 | 4 |   |    |            |    |   |    | 縁    |    |   |   |   |   |     |     |    |   |  |  |  |  |  |  |  |    |

|   | 0 |   |   |    |            |    |   |    | -    |    |   |   | レ | 1 | ン   | · 🕎 | 湏: | 域 |  |  |  |  |  |  |  |    |

| 1 | 0 | 7 |   |    |            |    | - | -  | オ    |    |   |   |   |   |     |     |    |   |  |  |  |  |  |  |  |    |

| 1 | 0 | 8 |   |    | 高          | 濃  | 度 | ソ  | -    | ス  | • | ド | レ | 1 | ン   | · 令 | 湏: | 域 |  |  |  |  |  |  |  |    |

| 1 | 0 | 9 |   |    | 層          | 間  | 絶 | 縁  | 膜    |    |   |   |   |   |     |     |    |   |  |  |  |  |  |  |  | 30 |

| 1 | 1 | 0 |   |    | 開          |    | 部 |    |      |    |   |   |   |   |     |     |    |   |  |  |  |  |  |  |  |    |

| 1 | 1 | 1 |   |    | 逆          | テ  | - | パ  | -    | 形  | 状 |   |   |   |     |     |    |   |  |  |  |  |  |  |  |    |

| 1 | 1 | 2 |   |    | 金          | 属  | 膜 |    |      |    |   |   |   |   |     |     |    |   |  |  |  |  |  |  |  |    |

| 2 | 1 | 0 |   |    | 開          | П  | 部 |    |      |    |   |   |   |   |     |     |    |   |  |  |  |  |  |  |  |    |

| 2 | 1 | 1 |   |    | 逆          | テ  | _ | パ  | -    | 形  | 状 |   |   |   |     |     |    |   |  |  |  |  |  |  |  |    |

| 2 | 1 | 2 |   |    | 生          | 成  | 物 |    |      |    |   |   |   |   |     |     |    |   |  |  |  |  |  |  |  |    |

| 3 | 0 | 7 |   |    | 第          | 2  | の | サ  | 1    | ド  | ウ | オ | _ | ル | 膊   | į   |    |   |  |  |  |  |  |  |  |    |

| 3 | 0 | 8 |   |    | 第          | 1  | の | サ  | 1    | ド  | ウ | オ | - | ル | . 膜 | į   |    |   |  |  |  |  |  |  |  |    |

| 3 | 1 | 1 |   |    | 開          |    | 部 |    |      |    |   |   |   |   |     |     |    |   |  |  |  |  |  |  |  |    |

| 4 | 0 | 7 |   |    | 第          | 2  | の | サ  | 1    | ド  | ウ | オ | - | ル | 膊   | į   |    |   |  |  |  |  |  |  |  | 40 |

| 4 | 0 | 8 |   |    | 第          | 1  | の | サ  | 1    | ド  | ウ | オ | - | ル | 膊   | į   |    |   |  |  |  |  |  |  |  |    |

|   |   |   |   |    |            |    |   |    |      |    |   |   |   |   |     |     |    |   |  |  |  |  |  |  |  |    |

## 【図1】

## 【図2】

## 【図3】

【図4】

# 【図5】

## フロントページの続き

(74)代理人 100117581

弁理士 二宮 克也

(74)代理人 100117710

弁理士 原田 智雄

(74)代理人 100121728

弁理士 井関 勝守

(74)代理人 100124671

弁理士 関 啓

(74)代理人 100131060

弁理士 杉浦 靖也

(72)発明者 興梠 隼人

大阪府門真市大字門真1006番地 松下電器産業株式会社内

F ターム(参考) 4M104 BB20 BB21 BB22 BB24 BB25 BB26 BB27 BB28 CC05 DD02

DD23 DD78 DD84 EE09 EE15 EE17 FF06 GG09 GG10 GG14

**HH13**

5F140 AA01 AA39 BA01 BF01 BF08 BF42 BG08 BG09 BG12 BG14

BG22 BG27 BG30 BG34 BG38 BG40 BG44 BG45 BG46 BG51

BG53 BG54 BG56 BG58 BH17 BK02 BK13 CC03 CC12 CE07