### (19) **日本国特許庁(JP)**

(51) Int. CL.

## (12) 特 許 公 報(B2)

FL

(11)特許番号

特許第5309601号 (P5309601)

(45) 発行日 平成25年10月9日(2013.10.9)

(24) 登録日 平成25年7月12日(2013.7.12)

| (01) 1111. 01. | ± ±                           |                                                 |                          |

|----------------|-------------------------------|-------------------------------------------------|--------------------------|

| HO1L 21/8247   | <b>7 (2006.01)</b> HO1L       | 27/10                                           | 4 3 4                    |

| HO1L 27/115    | (2006.01) HO1L                | 27/10                                           | 481                      |

| HO1L 27/10     | (2006.01) HO1L                | 29/78                                           | 3 7 1                    |

| HO1L 21/336    | (2006.01) HO1L                | 21/76                                           | L                        |

| HO1L 29/788    | (2006, 01)                    | ,                                               |                          |

|                | (2000.0.7)                    |                                                 | 請求項の数 10 (全 37 頁) 最終頁に続く |

| (21) 出願番号      | 特願2008-41782 (P2008-41782)    | (73) 特許権                                        | 者 308014341              |

| (22) 出願日       | 平成20年2月22日 (2008.2.22)        |                                                 | 富士通セミコンダクター株式会社          |

| (65) 公開番号      | 特開2009-200340 (P2009-200340A) |                                                 | 神奈川県横浜市港北区新横浜二丁目10番      |

| (43) 公開日       | 平成21年9月3日 (2009.9.3)          |                                                 | 23                       |

| 審査請求日          | 平成22年9月30日 (2010.9.30)        | (74) 代理人                                        | 100087479                |

|                |                               |                                                 | 弁理士 北野 好人                |

|                |                               | (72) 発明者                                        | 小倉 寿典                    |

|                |                               |                                                 | 神奈川県川崎市中原区上小田中4丁目1番      |

|                |                               |                                                 | 1号 富士通株式会社内              |

|                |                               | (72) 発明者                                        | 小倉輝                      |

|                |                               | ( - / <b>)                                 </b> | 神奈川県川崎市中原区上小田中4丁目1番      |

|                |                               |                                                 | 1号 富士通株式会社内              |

|                |                               | (72) 発明者                                        | 兒嶋 秀之                    |

|                |                               | (\*\_)\\                                        | 神奈川県川崎市中原区上小田中4丁目1番      |

|                |                               |                                                 | 1号 富士通株式会社内              |

|                |                               |                                                 | 日々 日工場が八五位内 最終頁に続く       |

|                |                               | ll .                                            | 取が見に加く                   |

(54) 【発明の名称】半導体装置の製造方法

## (57)【特許請求の範囲】

## 【請求項1】

半導体基板の表面に、活性領域を画定する素子分離領域を形成する工程と、

前記素子分離領域が形成された前記半導体基板上に、<u>酸素を含む</u>第1の絶縁膜を形成する工程と、

前記第1の絶縁膜が形成された前記半導体基板上に、<u>窒素を含む</u>第2の絶縁膜を形成する工程と、

前記活性領域と前記素子分離領域との境界を含む第1の領域に形成された前記第2の絶縁膜を、フルオロカーボン系のエッチングガスを用いたドライエッチングにより除去する工程と、

酸素を含む雰囲気に曝すことにより、前記ドライエッチングの際に前記第1の絶縁膜上に付着したフルオロカーボン膜を除去する工程と、

<u>前記フルオロカーボン膜を除去した後、</u>前記第1の領域に形成された前記第1の絶縁膜を、ウェットエッチングにより除去する工程と

を有し、

前記第2の絶縁膜に対する前記ドライエッチングのエッチングレートは、前記第1の絶縁膜に対する前記ドライエッチングレートより高い

ことを特徴とする半導体装置の製造方法。

### 【請求項2】

請求項1記載の半導体装置の製造方法において、

前記フルオロカーボン膜を除去する工程では、アルゴンガスと酸素ガスとを含む混合ガスを用いた反応性イオンエッチングにより、前記フルオロカーボン膜を除去する ことを特徴とする半導体装置の製造方法。

#### 【請求項3】

請求項2記載の半導体装置の製造方法において、

前記酸素ガスの流量は、プロセスガスの総流量に対して、 0 .5 ~ 2 5 %であることを特徴とする半導体装置の製造方法。

#### 【請求項4】

請求項2又は3記載の半導体装置の製造方法において、

前記第2の絶縁膜を除去する工程と、前記フルオロカーボン膜を除去する工程は、同一 10 の処理室内で連続して行う

ことを特徴とする半導体装置の製造方法。

## 【請求項5】

請求項1記載の半導体装置の製造方法において、

前記フルオロカーボン膜を除去する工程では、CF<sub>4</sub>ガスと酸素ガスとを含む混合ガスを用いたケミカルドライエッチングにより、前記フルオロカーボン膜を除去する ことを特徴とする半導体装置の製造方法。

### 【請求項6】

請求項5記載の半導体装置の製造方法において、

前記 C F 4 ガスの流量は、プロセスガスの総流量に対して、 0 . 0 5 ~ 1 0 %であることを特徴とする半導体装置の製造方法。

#### 【請求項7】

請求項1乃至6のいずれか1項に記載の半導体装置の製造方法において、

前記素子分離領域を形成する工程の後、前記第1の絶縁膜を形成する工程の前に、前記素子分離領域を構成する第3の絶縁膜の上部をエッチングする工程を更に有し、

前記第1の絶縁膜の形成の際、前記活性領域と前記素子分離領域との前記境界近傍の前記素子分離領域に、前記活性領域の表面よりも窪んだ窪みが形成されている ことを特徴とする半導体装置の製造方法。

## 【請求項8】

請求項1乃至7のいずれか1項に記載の半導体装置の製造方法において、

前記第1の領域とは異なる第2の領域内の活性領域に、前記第1の絶縁膜及び前記第2の絶縁膜を有する不揮発メモリトランジスタを形成する工程を更に有する

ことを特徴とする半導体装置の製造方法。

## 【請求項9】

請求項8記載の半導体装置の製造方法において、

前記素子分離領域を形成する工程の後、前記第1の絶縁膜を形成する工程の前に、前記第2の領域内の前記活性領域上にトンネル絶縁膜を形成する工程と、前記トンネル絶縁膜上に、前記第2の領域にフローティングゲートを形成する工程とを、

前記第1の絶縁膜を除去する工程の後に、前記第1の絶縁膜及び前記第2の絶縁膜を介して前記フローティングゲート上にコントロールゲートを形成する工程を、更に有し、

前記フローティングゲートと前記コントロールゲートとを有するスタックゲート構造の 前記不揮発メモリトランジスタを形成する

ことを特徴とする半導体装置の製造方法。

## 【請求項10】

請求項8記載の半導体装置の製造方法において、

前記第1の絶縁膜を除去する工程の後に、前記第1の絶縁膜及び前記第2の絶縁膜を介してコントロールゲートを形成する工程を更に有し、

前記第1の絶縁膜及び前記第2の絶縁膜を電荷蓄積層とする単層ゲート構造の前記不揮 発メモリトランジスタを形成する

ことを特徴とする半導体装置の製造方法。

20

30

#### 【発明の詳細な説明】

### 【技術分野】

## [0001]

本発明は、半導体装置の製造方法に係り、特に、不揮発性メモリを混載したロジック半導体装置の製造方法に関する。

### 【背景技術】

#### [0002]

不揮発性半導体メモリを混載したロジック半導体装置は、CPLD (Complex Programm able Logic Device)、FPGA (Field Programmable Gate Array)といった製品分野を形成し、そのプログラマブルという特徴により大きな市場を形成するに至っている。

#### [0003]

不揮発性メモリを混載したロジック半導体装置では、フラッシュメモリセルのほか、フラッシュメモリ制御のための高電圧トランジスタや、高性能ロジック回路のための低電圧トランジスタが、同一半導体チップ上に集積される。ここで、フラッシュメモリセルは、高電圧トランジスタや低電圧トランジスタにおける単層構造のゲート電極とは異なり、フローティングゲートとコントロールゲートとが積層されてなるスタック構造のゲート電極を有する。

#### [0004]

通常、スタックゲート構造からなるフラッシュメモリセルのゲート電極は、フローティングゲートを第1層目の導電膜により形成し、コントロールゲートを第2層目の導電膜により形成する。単層ゲート構造からなる周辺トランジスタのゲート電極は、第2層目の導電膜により形成する。また、フローティングゲートとコントロールゲートとの間には、これら電極間を絶縁して容量結合するためのゲート間絶縁膜が形成されている。このゲート間絶縁膜は、典型的にはシリコン酸化膜とシリコン窒化膜との積層膜(例えばONO膜)により構成され、周辺トランジスタ領域には形成されない。このため、不揮発性メモリを混載したロジック半導体装置の製造プロセスでは、第2層目の導電膜の堆積前に、周辺トランジスタ形成領域のゲート間絶縁膜を除去する工程が必要である。

#### [0005]

また、不揮発性メモリとしては、上記フラッシュメモリのほか、絶縁膜(例えば、ONO膜)を電荷蓄積層とした単層ゲート構造の不揮発性メモリが知られている。この不揮発性メモリの場合にも、ゲート電極の形成前に、周辺トランジスタ形成領域の電荷蓄積層を除去する必要がある。不揮発性メモリの制御に用いられる高電圧トランジスタの形成は、上述のフラッシュメモリの場合と同様の製造プロセスにより行われていた。

【特許文献1】特開平02-244628号公報

【特許文献 2】M. Hayashi et al., "Desorption species from fluorocarbon film by A r+ ion beam bombardment", J. Vac. Sci. Technol. A, VOI. 18, No. 4, Jul/Aug 2000, pp. 1881-1886

#### 【発明の開示】

【発明が解決しようとする課題】

#### [0006]

しかしながら、不揮発性メモリを混載したロジック半導体装置の製造プロセスについて本願発明者等が検討を行ったところ、上述のプロセスにより製造した半導体装置において、周辺トランジスタのゲート絶縁膜の絶縁耐圧が低下する不具合が生じることが判明した

#### [0007]

本発明の目的は、不揮発性メモリを混載したロジック半導体装置において、周辺トランジスタのゲート絶縁膜の絶縁耐圧低下を防止しうる半導体装置の製造方法を提供することにある。

### 【課題を解決するための手段】

## [0008]

10

20

30

50

本発明の一観点によれば、半導体基板の表面に、活性領域を画定する素子分離領域を形成する工程と、前記素子分離領域が形成された前記半導体基板上に、<u>酸素を含む</u>第1の絶縁膜を形成する工程と、前記第1の絶縁膜が形成された前記半導体基板上に、<u>窒素を含む</u>第2の絶縁膜を形成する工程と、前記活性領域と前記素子分離領域との境界を含む第1の領域に形成された前記第2の絶縁膜を、フルオロカーボン系のエッチングガスを用いたドライエッチングにより除去する工程と、酸素を含む雰囲気に曝すことにより、前記ドライエッチングの際に前記第1の絶縁膜上に付着したフルオロカーボン膜を除去する工程と、前記フルオロカーボン膜を除去した後、前記第1の領域に形成された前記第1の絶縁膜を、ウェットエッチングにより除去する工程とを有し、前記第2の絶縁膜に対する前記ドライエッチングのエッチングレートは、前記第1の絶縁膜に対する前記ドライエッチングレートより高い半導体装置の製造方法が提供される。

10

#### 【発明の効果】

## [0009]

本発明によれば、不揮発性メモリを混載したロジック半導体装置の製造方法において、周辺回路領域に形成されたゲート間絶縁膜又は電荷蓄積層を除去する過程において、上層部を除去した後、上層部除去の際に表面に付着したフルオロカーボン膜を除去し、その後に下層部を除去するので、素子分離膜縁部の窪みの形状が変化することを防止することができる。これにより、素子分離膜端部における電界集中が防止され、周辺トランジスタのゲート絶縁膜の絶縁耐圧劣化を防止することができる。これにより、半導体装置の製造歩留まりを向上することができ、ひいては製造コストを削減することができる。

20

## 【発明を実施するための最良の形態】

#### [0010]

#### 「第1実施形態]

本発明の第1実施形態による半導体装置の製造方法について図1乃至図31を用いて説明する。

#### [0011]

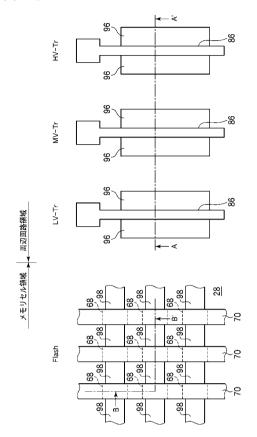

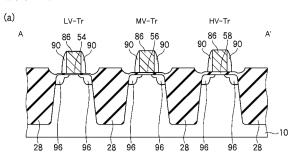

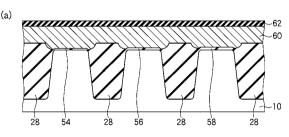

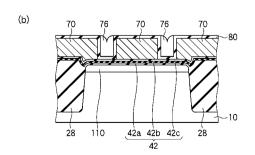

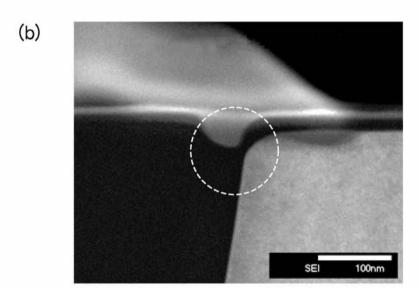

図1は本実施形態による半導体装置の構造を示す平面図、図2は本実施形態による半導体装置の構造を示す概略断面図、図3乃至図28は本実施形態による半導体装置の製造方法を示す工程断面図、図29はONO膜の除去過程におけるフルオロカーボン膜の影響を説明する図、図30はフルオロカーボン膜を除去する工程を行っていない試料と行った試料とにおける素子分離膜端部の断面形状を示すTEM像、図31は高電圧トランジスタのゲート電極に逆バイアスを印加したときのゲート絶縁膜耐圧を示すグラフである。

30

## [0012]

はじめに、本実施形態による半導体装置の構造について図1及び図2を用いて説明する。図2(a)は図1のA-A 線に沿った概略断面図であり、図2(b)は図1のB-B線に沿った概略断面図である。

#### [0013]

本実施形態による半導体装置は、スタックゲート構造の不揮発メモリトランジスタを混載したロジック半導体装置である。図1に示すように、不揮発メモリトランジスタ(F1ash)がマトリクス状に形成されたメモリセル領域と、論理回路を構成するロジックトランジスタや不揮発メモリトランジスタの駆動用の高耐圧トランジスタなどの種々の周辺トランジスタが形成された周辺回路領域を有している。本実施形態では、周辺トランジスタとして、高速ロジック回路を構成する低電圧トランジスタ(LV-Tr)と、入出力回路を構成する中電圧トランジスタ(MV-Tr)と、不揮発メモリトランジスタを制御するための高電圧トランジスタ(HV-Tr)を有しているものとする。

## [0014]

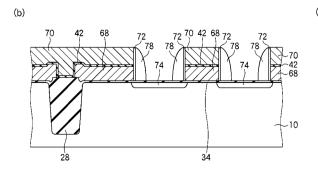

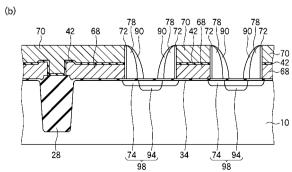

不揮発メモリトランジスタ(Flash)は、図1及び図2に示すように、シリコン基板10上にトンネル絶縁膜34を介して形成されたフローティングゲート68と、フローティングゲート68上にONO膜42を介して形成され、ワード線を兼ねるコントロール

50

ゲート 7 0 と、コントロールゲート 7 0 の両側のシリコン基板 1 0 内に形成されたソース / ドレイン領域 9 8 とを有している。

#### [0015]

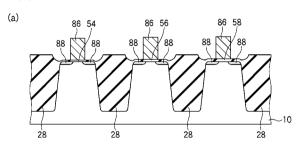

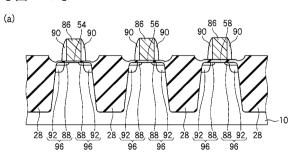

低電圧トランジスタ(LV-Tr)は、図1及び図2に示すように、シリコン基板10上にゲート絶縁膜54を介して形成されたゲート電極84と、ゲート電極84の両側のシリコン基板10内に形成されたソース/ドレイン領域96とを有している。

#### [0016]

中電圧トランジスタ(MV-Tr)は、図1及び図2に示すように、シリコン基板10 上にゲート絶縁膜56を介して形成されたゲート電極84と、ゲート電極84の両側のシ リコン基板10内に形成されたソース/ドレイン領域96とを有している。

## [0017]

高電圧トランジスタ(HV-Tr)は、図1及び図2に示すように、シリコン基板10上にゲート絶縁膜58を介して形成されたゲート電極84と、ゲート電極84の両側のシリコン基板10内に形成されたソース/ドレイン領域96とを有している。

#### [0018]

周辺トランジスタのゲート絶縁膜は、各トランジスタの耐圧に応じて、ゲート絶縁膜 5 4、ゲート絶縁膜 5 6、ゲート絶縁膜 5 8 の順に厚くなっている。

#### [0019]

なお、本実施形態では、低電圧トランジスタ(LV-Tr)、中電圧トランジスタ(M V-Tr)及び高電圧トランジスタ(HV-Tr)をそれぞれ1つずつしか示していないが、実際には、それぞれに導電型の異なるN型及びP型のトランジスタが含まれる。また、閾値電圧の異なる複数のトランジスタを用いることもある。

#### [0020]

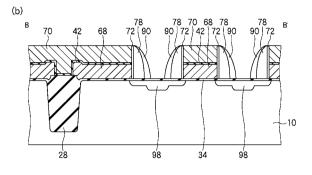

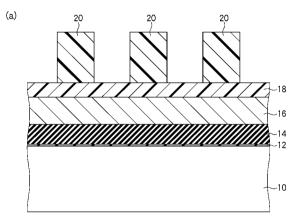

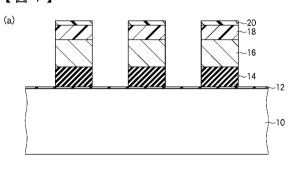

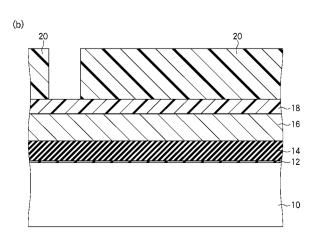

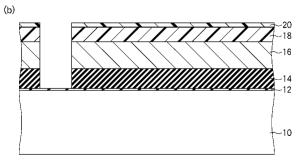

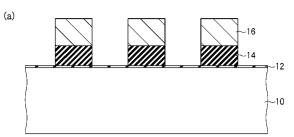

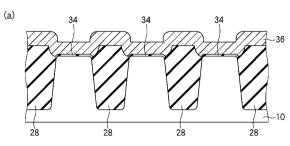

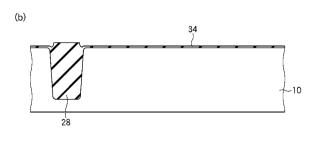

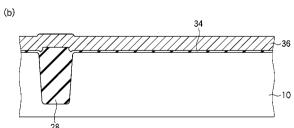

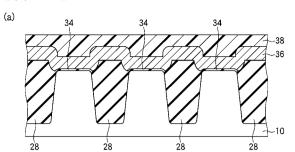

次に、本実施形態による半導体装置の製造方法について図3乃至図28を用いて説明する。各図面において、(a)は周辺回路領域の工程断面図(図1のA-A 線断面に相当)であり、(b)はメモリセル領域の工程断面図(図2のB-B 線断面に相当)である

## [0021]

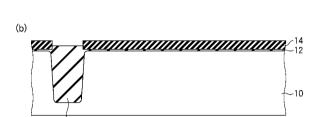

まず、例えば熱酸化法により、シリコン基板10の表面を熱酸化し、例えば膜厚8~1 6nm程度のシリコン酸化膜12を形成する。

#### [0022]

次 N で、 シリコン酸化膜 1 2 上に、例えば 7 0 0 ~ 9 0 0 の温度の熱 C V D (Chemic al Vapor Deposition) 法により、例えば膜厚 5 5 ~ 1 3 0 n m のシリコン窒化膜 1 4 を形成する。

## [0023]

次いで、シリコン窒化膜 1 4 上に、例えば 5 5 0 ~ 6 8 0 の温度の熱 C V D 法により、例えば膜厚 6 0 ~ 1 2 0 n m のポリシリコン膜 1 6 を形成する。

#### [0024]

次いで、ポリシリコン膜 1 6 上に、スピンコート法により、 B A R C (Bottom Anti-Reflective Coating) 膜 1 8 とフォトレジスト膜 2 0 とを形成する。

## [0025]

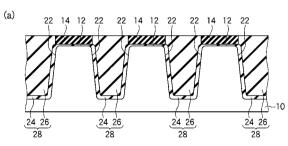

次いで、フォトリソグラフィにより、フォトレジスト膜20に、素子分離膜の形成予定領域を露出する開口部を形成する(図3(a)、図3(b))。

## [0026]

次いで、フォトレジスト膜 2 0 をマスクとして、ドライエッチングにより、 B A R C 膜 1 8、ポリシリコン膜 1 6 及びシリコン室化膜 1 4 をパターニングし、フォトレジスト膜 2 0 のパターンをポリシリコン膜 1 6 及びシリコン窒化膜 1 4 に転写する(図 4 ( a )、図 4 ( b ) )。

### [0027]

なお、ポリシリコン膜16は、シリコン窒化膜14をパターニングする際にハードマス

10

20

30

00

40

クとして用いる膜である。シリコン窒化膜 1 4 のパターニングをフォトレジスト膜 2 0 だけで十分に行える場合には、必ずしもポリシリコン膜 1 6 を形成する必要はない。

#### [0028]

次いで、アッシング及びその後の後処理により、ポリシリコン膜 1 6 上に残存する B A R C 膜 1 8 及びフォトレジスト膜 2 0 を除去する(図 5 ( a )、図 5 ( b ) )。

#### [0029]

次いで、パターニングしたポリシリコン膜16及びシリコン窒化膜14をマスクとして、シリコン酸化膜12及びシリコン基板10をエッチングし、シリコン基板10に、素子分離用のトレンチ22を形成する(図6(a)、図6(b))。なお、ポリシリコン膜16は、シリコン基板10のエッチングとともに除去される。

#### [0030]

次いで、必要に応じて適切な後処理を行い、半導体基板10の表面に付着したエッチングによる副生成物を除去する。

#### [0031]

次いで、例えば熱酸化法により、シリコン窒化膜14をマスクとしてシリコン基板10を熱酸化し、トレンチ22の内面に、例えば膜厚1~18nmのシリコン酸化膜24を形成する。

## [0032]

次いで、全面に、例えば 250~600 の温度の HDP (High Density Plasma) C V D 法により、例えば膜厚 250~750 n m のシリコン酸化膜 26 を形成する(図 7 (a)、図 7 (b))。これにより、トレンチ 22 内はシリコン酸化膜 26 によって完全に埋め込まれる。

#### [0033]

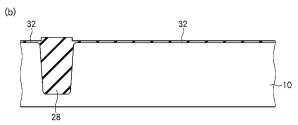

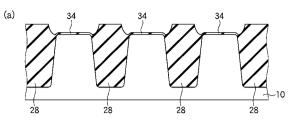

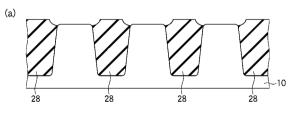

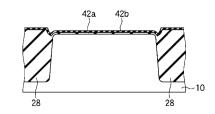

次いで、CMP(Chemical Mechanical Polishing)法により、シリコン窒化膜14の表面が露出するまでシリコン酸化膜26の表面を研磨し、表面を平坦化する。これにより、シリコン酸化膜24,26よりなる素子分離膜28を形成する(図8(a)、図8(b))。これにより、シリコン基板10の表面には、素子分離膜28により画定された複数の活性領域が形成される。

## [0034]

次いで、適切な後処理により、СМРのスラリーを除去する。

#### [0035]

次いで、窒素雰囲気中で、例えば800~1100 の温度で熱処理を行う。

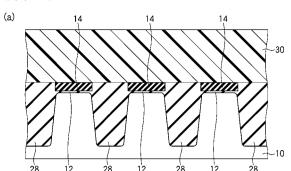

## [0036]

次いで、全面に、スピンコート法によりフォトレジスト膜30を形成した後、フォトリソグラフィによりフォトレジスト膜30パターニングする。これにより、周辺回路領域を覆いメモリセル領域を露出するフォトレジスト膜30を形成する。

## [0037]

次いで、フォトレジスト膜30をマスクとして、例えば弗酸水溶液を用いたウェットエッチングにより、素子分離膜28の上面を例えば10~80nm程度エッチングする(図9(a)、図9(b))。

## [ 0 0 3 8 ]

次いで、例えば純水により10:1~200:1程度に希釈された弗酸水溶液によりウェットエッチングを行い、シリコン窒化膜14上の自然酸化膜(図示せず)を除去する。

## [0039]

次いで、例えば130 の燐酸水溶液によりウェットエッチングを行い、シリコン窒化膜14を除去する。

#### [0040]

次いで、例えば弗酸水溶液を用いたウェットエッチングにより、シリコン酸化膜 1 2 を除去する。

## [0041]

50

10

20

30

10

20

30

40

50

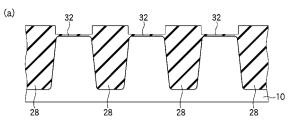

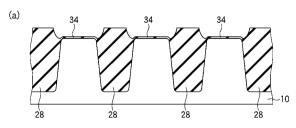

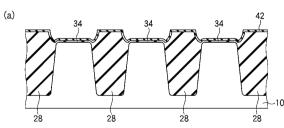

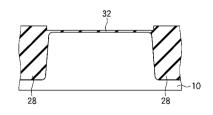

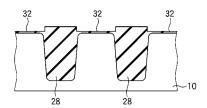

次いで、例えば熱酸化法により、シリコン基板10の表面に、例えば膜厚8~16nmのシリコン酸化膜を形成する。これにより、シリコン酸化膜よりなるイオン注入用の犠牲酸化膜32を形成する(図10(a)、図10(b))。

### [0042]

次いで、フォトリソグラフィ及びイオン注入により、メモリセル領域及び高電圧トランジスタ形成領域に所定のウェル(図示せず)を形成する。例えば、メモリセル領域及びN型高電圧トランジスタ形成領域にはN型ウェル内にP型ウェルが形成された二重ウェルを形成し、P型高電圧トランジスタ形成領域にはN型ウェルを形成する。N型ウェルは、例えば燐イオンを、加速エネルギーを例えば300~500keV、ドーズ量を例えば1x10 $^{1}$   $^{1}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$   $^{2}$

#### [0043]

次いで、窒素雰囲気中で、例えば900~1200 の温度で1~15秒間の熱処理を 行い、注入した不純物を活性化する。

#### [0044]

次いで、例えば純水により10:1~200:1程度に希釈された弗酸水溶液によりウェットエッチングを行い、犠牲酸化膜32を除去する。

#### [0045]

なお、素子分離膜28は、シリコン酸化膜12や犠牲酸化膜32の除去工程などにおいて徐々に膜減りする。これにより、犠牲酸化膜32を除去した後には、素子分離膜28と活性領域との境目に、活性領域表面より窪んだ窪みが形成されている。

#### [0046]

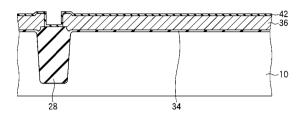

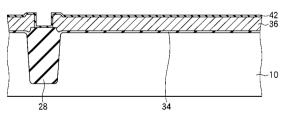

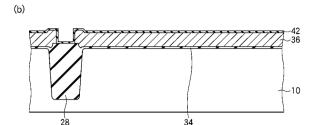

次いで、シリコン基板 1 0 の表面に、例えば膜厚 3 ~ 1 5 n m のシリコン酸化膜よりなるトンネル絶縁膜 3 4 を形成する(図 1 1 ( a )、図 1 1 ( b ) )。トンネル絶縁膜 3 4 は、例えば 3 0 0 ~ 5 5 0 の温度でのラジカル酸化、例えば 8 5 0 ~ 1 1 0 0 の温度での熱酸化等により形成する。

## [0047]

#### [0048]

次いで、アモルファスシリコン膜 3 6 上に、スピンコート法により、 B A R C (Bottom Anti-Reflective Coating) 膜 3 8 とフォトレジスト膜 4 0 とを形成する。

#### 【0049】

次いで、フォトリソグラフィにより、フォトレジスト膜 4 0 に、周辺回路領域と、メモリセル領域内の所定領域を露出する開口部を形成する(図 1 3 ( a )、図 1 3 ( b ) )。 メモリセル領域内の所定領域は、ワード線(コントロールゲート)の形成領域と素子分離 領域とが重なる領域であり、ワード線の延在方向にフローティングゲートを分離するため の領域に相当する。

## [0050]

次いで、フォトレジスト膜 4 0 をマスクとして、例えば誘導結合型プラズマエッチング 装置を用いた異方性エッチングにより、アモルファスシリコン膜 3 6 をパターニングする (図 1 4 (a)、図 1 4 (b))。

## [0051]

次いで、アッシング及びその後の後処理により、アモルファスシリコン膜36上に残存

するBARC膜38及びフォトレジスト膜40を除去する。

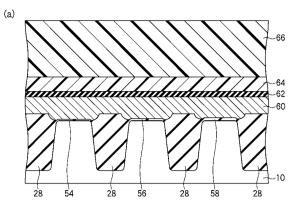

### [0052]

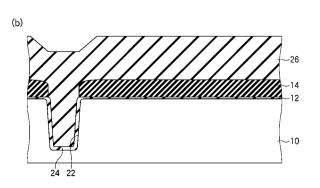

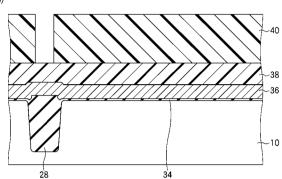

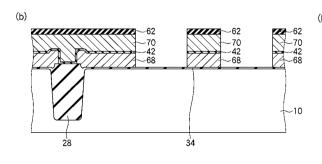

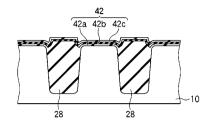

次いで、全面に、シリコン酸化膜 / シリコン窒化膜 / シリコン酸化膜の積層構造よりなる ONO膜 4 2 を形成する(図 1 5 (a)、図 1 5 (b))。 ONO膜 4 2 は、フローティングゲートとコントロールゲートとを絶縁し容量結合するための膜である。 ONO膜 4 2 は、例えば 5 0 0 ~ 9 0 0 の温度の熱 C V D 法により例えば膜厚 3 ~ 5 n m のシリコン酸化膜(ボトム酸化膜)を形成し、例えば 3 0 0 ~ 9 0 0 の温度の熱 C V D 法により例えば膜厚 5 ~ 1 0 n m のシリコン窒化膜を形成した後、例えば 8 0 0 ~ 1 1 0 0 の温度の熱酸化によりシリコン窒化膜を 3 ~ 8 n m 程度酸化してシリコン酸化膜(トップ酸化膜)を形成することにより、形成する。

[0053]

次いで、フォトリソグラフィ及びイオン注入により、低電圧トランジスタ形成領域及び中電圧トランジスタ形成領域に所定のウェル(図示せず)を形成する。例えば、N型低電圧トランジスタ形成領域及びN型中電圧トランジスタ形成領域にP型ウェルを形成し、P型低電圧トランジスタ形成領域にN型ウェルを形成する。

[0054]

次いで、全面に、スピンコート法によりフォトレジスト膜44を形成した後、フォトリソグラフィによりフォトレジスト膜44パターニングする。これにより、周辺回路領域を露出しメモリセル領域を覆うフォトレジスト膜44を形成する。

[0055]

次いで、フォトレジスト膜44をマスクとして、例えばマグネトロン反応性イオンエッチング(RIE)装置を用いたドライエッチングにより、ONO膜42のトップ酸化膜及び中間層のシリコン窒化膜をエッチングする。

[0056]

ONO膜42を形成する各々の膜厚は、10nm以下と極めて薄い。また、活性領域と素子分離膜との境目には窪みが形成されているため、窪み(傾斜部)に形成された膜を除去するために、オーバーエッチング量を程度300%以上に増加する必要がある。このため、ONO膜42の各々の膜をエッチングする際には、下地に対する選択比を十分に確保する必要がある。

[0057]

かかる観点から、トップ酸化膜のエッチングには、例えばエッチングガスに $C_4F_8$ 、 $C_4F_6$ 、Ar、 $O_2$  のいずれかの組み合わせとなる混合ガスを用い、下地のシリコン窒化膜に対して選択比が 6.0 程度以上となる条件を用いる。また、中間層のシリコン窒化膜のエッチングには、 $CH_3F$ 、Ar、 $O_2$  のいずれかの組み合わせとなる混合ガスを用い、下地のボトム酸化膜に対して選択比が 9.0 程度以上となる条件を用いる。

[0058]

フルオロカーボン系のエッチングガスを用いた上記エッチング条件では、エッチングに伴い、副生成物であるフルオロカーボン膜が、基板の表面に付着する。

[0059]

次いで、基板の表面に付着したフルオロカーボン膜を、以下のいずれかの方法で除去する。

[0060]

第1の方法は、マグネトロンRIE装置を用い、アルゴンガスと酸素ガスとの混合ガスのプラズマに基板を曝すことにより、フルオロカーボン膜を除去する方法である。エッチングの副生成物であるフルオロカーボンにアルゴンビームを照射すると、フッ素が抜けてカーボンリッチの膜となる。この膜に酸素が作用することで、フルオロカーボン膜を除去することができる。この方法は、ONO膜42のトップ酸化膜及びシリコン窒化膜のエッチングに引き続き、同一装置内で処理を行うことができるというメリットがある。

[0061]

10

20

40

30

具体的な条件としては、例えば、RFパワーが100~300W、圧力が40~100 MTorr、プロセスガスの総流量が100~600sccm、ガスの混合比Ar:O<sub>2</sub> が100:1~100:15、電極温度が50 、処理時間が10~60秒である。

#### [0062]

なお、酸素ガスの添加量は、プロセスガスの総流量に対して、0.5%~25%の範囲、好ましくは0.5%~10%程度の範囲に設定することが望ましい。酸素の添加量が0.5%よりも低いとフルオロカーボン膜の除去効果が十分に得られず、酸素の添加量が25%を超えるとフォトレジスト膜44のアッシングが顕著となるからである。フォトレジスト膜44は、後述のボトム酸化膜を除去する際のウェットエッチング工程でもマスク膜として用いるため、フルオロカーボン膜の除去後もウェットエッチングに耐えうる膜厚が残っている必要がある。

[0063]

第2の方法は、ダウンフローエッチング装置を用い、酸素ガス、 $CF_4$ ガス及びフォーミングガス(水素 3 % と窒素 9 7 %の混合ガス。以下、「FG」とも表現する。)の混合ガスを用いたケミカルドライエッチングにより、フルオロカーボン膜を除去する方法である。 $CF_4$ ガスは、フルオロカーボン膜に対する酸素ラジカルの反応性を高め、フルオロカーボン膜のエッチングを促進する役割を担うものである。また、フォーミングガスは、酸素ラジカルの寿命を長くする役割を担うものである。

[0064]

具体的な条件としては、例えば、マイクロ波パワーが 8 0 0 ~ 1 1 0 0 W、圧力が 1 5 0 ~ 3 0 0 P a、プロセスガスの総流量が 1 2 0 0 ~ 2 0 0 0 s c c m、ガスの混合比 O 2 : C F 4 : F G が 6 1 7 : 3 7 4 : 1 ~ 6 1 : 3 8 : 1、処理時間が 1 0 ~ 3 3 秒である。

[0065]

なお、  $CF_4$  ガスの添加量は、プロセスガスの総流量に対して、  $0.05\% \sim 3\%$  の範囲、好ましくは  $0.1\% \sim 1\%$  程度に設定することが望ましい。  $CF_4$  ガスの添加量が 0.05% よりも低いと酸素ラジカルの反応性が低すぎてフルオロカーボン膜の除去効果が十分に得られず、  $CF_4$  ガスの添加量 3% を超えると酸素ラジカルの反応性が高くなりすぎフォトレジスト膜 44 のアッシングが顕著となるからである。

[0066]

フルオロカーボン膜を除去する工程の目的及び効果については、後述する。

[0067]

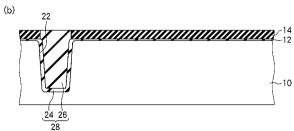

次いで、フォトレジスト膜 4 4 をマスクとして、例えば純水により 1 0 0 : 1 ~ 2 0 0 : 1 程度に希釈された弗酸水溶液によりウェットエッチングを行い、 O N O 膜 4 2 のボトム酸化膜及びトンネル絶縁膜 3 4 を除去する(図 1 6 ( a )、図 1 6 ( b ) )。

[0068]

次いで、アッシング及びその後の後処理により、フォトレジスト膜44を除去する。

[0069]

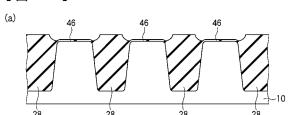

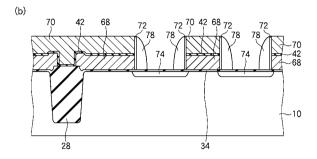

次いで、例えば熱酸化法により、周辺回路領域のシリコン基板10の表面に、例えば膜厚3~20nmのシリコン酸化膜46を形成する(図17(a)、図17(b))。

[0070]

次いで、全面に、スピンコート法によりフォトレジスト膜48を形成した後、フォトリソグラフィによりフォトレジスト膜48パターニングする。これにより、低電圧トランジスタ形成領域及び中電圧トランジスタ形成領域を露出し、高電圧トランジスタ形成領域及びメモリセル領域を覆うフォトレジスト膜48を形成する。

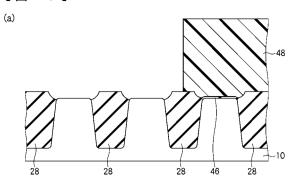

[0071]

次いで、フォトレジスト膜48をマスクとして、例えば純水により100:1~200:1程度に希釈された弗酸水溶液によりウェットエッチングを行い、低電圧トランジスタ形成領域及び中電圧トランジスタ形成領域のシリコン酸化膜46を選択的に除去する(図18(a)、図18(b))。

10

20

30

40

[0072]

次いで、アッシング及びその後の後処理により、フォトレジスト膜48を除去する。

[0073]

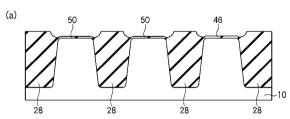

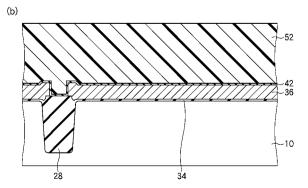

次いで、シリコン基板10を熱酸化し、低電圧トランジスタ形成領域及び中電圧トランジスタ形成領域に、例えば膜厚1~12nmのシリコン酸化膜50を形成する(図19(a)、図19(b))。この際、シリコン酸化膜46は、追加酸化されて膜厚が増加する

[0074]

次いで、全面に、スピンコート法によりフォトレジスト膜52を形成した後、フォトリソグラフィによりフォトレジスト膜52パターニングする。これにより、低電圧トランジスタ形成領域を露出し、中電圧トランジスタ形成領域、高電圧トランジスタ形成領域及びメモリセル領域を覆うフォトレジスト膜52を形成する。

[0075]

次いで、フォトレジスト膜52をマスクとして、例えば純水により100:1~200:1程度に希釈された弗酸水溶液によりウェットエッチングを行い、低電圧トランジスタ 形成領域のシリコン酸化膜50を選択的に除去する(図20(a)、図20(b))。

[0076]

次いで、アッシング及びその後の後処理により、フォトレジスト膜52を除去する。

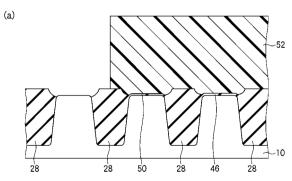

[0077]

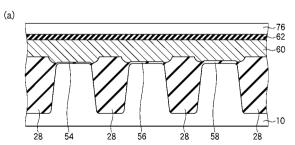

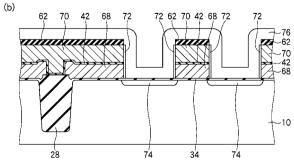

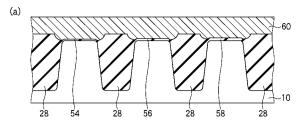

次いで、シリコン基板10を熱酸化し、低電圧トランジスタ形成領域に、例えば膜厚1~3mmのシリコン酸化膜よりなるゲート絶縁膜54を形成する。この際、中電圧トランジスタ形成領域では、シリコン酸化膜50が追加酸化され、例えば膜厚2~15mmのシリコン酸化膜よりなるゲート絶縁膜56が形成される。また、高電圧トランジスタ形成領域では、シリコン酸化膜46が更に追加酸化され、例えば膜厚5~35mmのシリコン酸化膜よりなるゲート絶縁膜58が形成される。こうして、低電圧トランジスタ形成領域、中電圧トランジスタ形成領域及び高電圧トランジスタ形成領域に、互いに膜厚の異なる3種類のゲート絶縁膜52,54,56を形成する(図21(a)、図21(b))。

[0078]

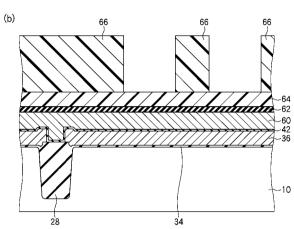

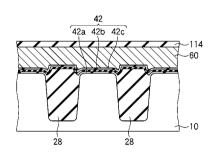

次いで、全面に、例えば C V D 法により、例えば膜厚 5 0 ~ 1 1 0 n m のポリシリコン膜 6 0 を形成する。

[0079]

次いで、ポリシリコン膜 6 0 上に、例えば C V D 法により、例えば最表面に 3 n m 以下の酸化膜が形成された膜厚 1 0 ~ 4 0 n m のシリコン窒化膜 6 2 を形成する。

[0800]

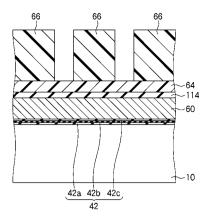

次いで、シリコン窒化膜62上に、スピンコート法により、BARC膜64とフォトレジスト膜66とを形成する。

[0081]

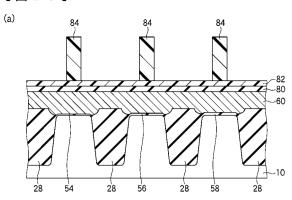

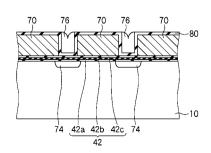

次いで、フォトリソグラフィによりフォトレジスト膜66をパターニングし、周辺回路 領域及びメモリセル領域のコントロールゲート形成領域を覆うフォトレジスト膜66を形 成する(図22(a)、図22(b))。

[0082]

次いで、フォトレジスト膜 6 6 をマスクとして、例えば誘導結合型プラズマエッチング 装置を用いた異方性エッチングにより、BARC膜 6 4、シリコン窒化膜 6 2、ポリシリコン膜 6 0、ONO膜 4 2 及びアモルファスシリコン膜 3 6 をパターニングし、メモリセル領域に、アモルファスシリコン膜 3 6 よりなるフローティングゲート 6 8 と、ポリシリコン膜 6 0 よりなるコントロールゲート 7 0 とを形成する。

[0083]

次いで、アッシング及びその後の後処理により、シリコン窒化膜 6 2 上に残存する B A R C 膜 6 4 及びフォトレジスト膜 6 6 を除去する(図 2 3 (a)、図 2 3 (b))。

[0084]

50

10

20

30

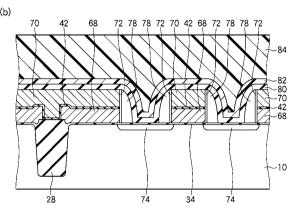

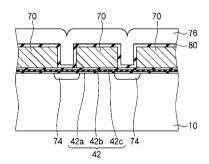

次いで、熱酸化法により、フローティングゲート 6 8 及びコントロールゲート 7 0 の側壁部分に、シリコン酸化膜よりなる側壁絶縁膜 7 2 を形成する。

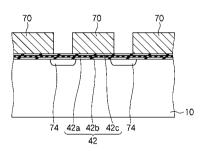

#### [0085]

次いで、コントロールゲート70をマスクとしてイオン注入を行い、コントロールゲート70の両側のシリコン基板10内に、不純物拡散領域74を形成する。

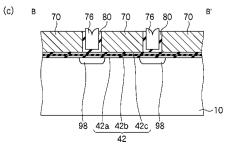

#### [0086]

次いで、全面に、例えば熱 C V D 法により、例えば膜厚 3 0 ~ 1 5 0 n m のシリコン窒化膜 7 6 を形成する(図 2 4 ( a )、図 2 4 ( b ) )。

### [0087]

次いで、ドライエッチングにより、ポリシリコン膜 6 0 及びコントロールゲート 7 0 の上面が露出するまでシリコン窒化膜 7 6 , 6 2 を異方性エッチングし、側壁絶縁膜 7 2 が形成されたフローティングゲート 6 8 及びコントロールゲート 7 0 の側壁部分に、シリコン窒化膜 7 6 よりなる側壁絶縁膜 7 8 を形成する(図 2 5 (a)、図 2 5 (b))。

#### [0088]

次いで、全面に、例えば熱CVD法により、例えば膜厚15~40nmのシリコン酸化膜80を形成する。シリコン酸化膜80は、後工程でポリシリコン膜60のパターニングの際にハードマスクとして用いる膜である。

#### [0089]

次いで、シリコン酸化膜80上に、スピンコート法により、BARC膜82とフォトレジスト膜84とを形成する。

#### [0090]

次いで、フォトリソグラフィによりフォトレジスト膜84をパターニングし、メモリセル領域及び周辺トランジスタ(低電圧トランジスタ、中電圧トランジスタ及び高電圧トランジスタ)のゲート電極形成領域を覆うフォトレジスト膜84を形成する(図26(a)、図26(b))。

#### [0091]

次いで、フォトレジスト膜84をマスクとして、例えば誘導結合型プラズマエッチング 装置を用いた異方性エッチングにより、BARC膜82、シリコン酸化膜80及びポリシ リコン膜60をパターニングし、周辺回路領域に、ポリシリコン膜60よりなるゲート電 極86を形成する。

#### [0092]

次いで、アッシング及びその後の後処理により、シリコン酸化膜 8 0 上に残存する B A R C 膜 8 2 及びフォトレジスト膜 8 4 を除去する。

#### [0093]

次いで、例えば弗酸水溶液を用いたウェットエッチングにより、シリコン酸化膜80を除去する。

## [0094]

次いで、ゲート電極86をマスクとしてイオン注入を行い、ゲート電極86の両側のシリコン基板10内に、不純物拡散領域88を形成する(図27(a)、図27(b))。

### [0095]

次いで、例えば熱 C V D 法により例えばシリコン窒化膜を堆積後、このシリコン窒化膜をエッチバックし、ゲート電極 8 6 の側壁部分、及び側壁絶縁膜 7 8 が形成されたフローティングゲート 6 8 及びコントロールゲート 7 0 の側壁部分に、シリコン窒化膜よりなる側壁絶縁膜 9 0 を形成する。

#### [0096]

次いで、ゲート電極 8 6 及び側壁絶縁膜 9 0 をマスクとして、並びにコントロールゲート及び側壁絶縁膜 7 8 , 9 0 をマスクとしてイオン注入を行い、ゲート電極 8 6 の両側のシリコン基板 1 0 内に不純物拡散領域 9 2 を形成し、コントロールゲート 7 0 の両側のシリコン基板 1 0 内に不純物拡散領域 9 4 を形成する。

## [0097]

50

10

20

30

次いで、窒素雰囲気中で熱処理を行い、注入した不純物を活性化し、ゲート電極 8 6 の両側のシリコン基板 1 0 内に、不純物拡散領域 8 8 , 9 2 よりなるソース / ドレイン領域 9 6 を形成し、コントロールゲート 7 0 の両側のシリコン基板 1 0 内に、不純物拡散領域 7 4 , 9 4 よりなるソース / ドレイン領域 9 8 を形成する(図 2 8 ( a )、図 2 8 ( b ) )。

## [0098]

こうして、メモリセル領域に形成され、トンネル絶縁膜34を介してシリコン基板10上に形成されたフローティングゲート68と、ONO膜42を介してフローティングゲート68上に形成されたコントロールゲート70と、コントロールゲート70の両側のシリコン基板10内に形成されたソース/ドレイン領域98とを有する不揮発メモリトランジスタと、低電圧トランジスタ形成領域に形成され、ゲート絶縁膜54を介してシリコン基板10上に形成されたゲート電極86と、ゲート電極86の両側のシリコン基板10内に形成されたソース/ドレイン領域96とを有する低電圧トランジスタと、中電圧トランジスタ形成領域に形成され、ゲート絶縁膜56を介してシリコン基板10上に形成されたゲート電極86と、ゲート電極86と、ゲート電極86と、ゲート電極86と、ゲート電極86の両側のシリコン基板10上に形成されたゲート電極86と、ゲート電極86の両側のシリコン基板10上に形成されたゲート電極86と、ゲート電極86の両側のシリコン基板10上に形成されたゲート電極86と、ゲート電極86の両側のシリコン基板10上に形成されたゲート電極86と、ゲート電極86の両側のシリコン基板10上に形成されたゲート電極86と、ゲート電極86の両側のシリコン基板10上に形成されたゲート電極86と、ゲート電極86の両側のシリコン基板10内に形成されたゲート電極86と、ゲート電極86の両側のシリコン基板10内に形成されたソース/ドレイン領域96とを有する高電圧トランジスタとを完成する。

## [0099]

この後、サリサイドプロセスや、多層配線プロセスなどの所定のバックエンドプロセス を経て、半導体装置を完成する。

#### [0100]

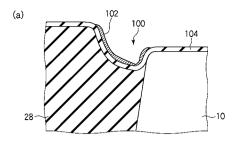

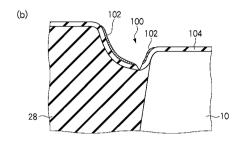

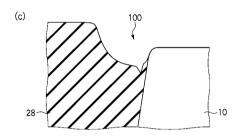

次に、上述の本実施形態による半導体装置の製造方法において、周辺回路領域のONO膜42の除去過程でフルオロカーボン膜を除去する工程を行う目的及び効果について図29乃至図31を用いて説明する。

#### [0101]

本実施形態による半導体装置の製造方法において、周辺回路領域のONO膜42の除去過程においてフルオロカーボン膜を除去しているのは、高電圧トランジスタのゲート絶縁膜の絶縁耐圧の低下に、フルオロカーボン膜が影響しているためである。

#### [0102]

前述のように、ONO膜42を除去する工程に至る過程で、素子分離膜28と活性領域(シリコン基板10)との境界には、窪み100が形成されている。ONO膜42のトップ酸化膜及び中間層のシリコン窒化膜を除去するドライエッチングの過程では、窪み100の内壁に、ドライエッチングの副生成物であるフルオロカーボン膜102が堆積される。フルオロカーボン膜102は、窪み100の側壁器部分に堆積されやすいため、窪み100の深部では膜厚が薄くなっているものと考えられる(図29(a)参照)。

#### [0103]

この状態でボトム酸化膜 1 0 4 のエッチング工程を行うと、フルオロカーボン膜 1 0 2 の付着部分のエッチングレートは遅いため、窪み 1 0 0 の深部におけるエッチングが優先して進行する(図 2 9 (b)参照)。

#### [0104]

この後、ボトム酸化膜104(トンネル絶縁膜34を含む)のエッチングを更に進行すると、先にエッチングが完了した窪み100の深部では素子分離膜28もエッチングされ、窪み100の深部における形状が急峻になる(図29(c)参照)。

## [0105]

この窪み100の急峻な形状は、その後の熱酸化によってゲート絶縁膜58を形成した後も保存される。この結果、窪み100内にゲート電極材料が形成されると電界集中が発生し、高電圧トランジスタのゲート絶縁膜58の絶縁耐圧の低下を引き起こすものと考えられる。

10

20

30

40

#### [0106]

低電圧トランジスタ及び中電圧トランジスタのゲート絶縁膜54,56では、高電圧トランジスタのゲート絶縁膜58で見られるような絶縁耐圧の低下は認められなかった。低電圧トランジスタ形成領域及び中電圧トランジスタ形成領域では、シリコン酸化膜46を除去した後に再酸化してゲート絶縁膜54,56を形成するため、窪み100の形状が緩和されて電界集中が生じないものと考えられる。

#### [ 0 1 0 7 ]

本実施形態のようにフルオロカーボン膜を除去する工程を行うことにより、ボトム酸化膜のエッチングが局所的に進行することが防止され、ボトム酸化膜の除去後の窪みの最深部に急峻な窪みが形成されるのを防止することができる。

#### [0108]

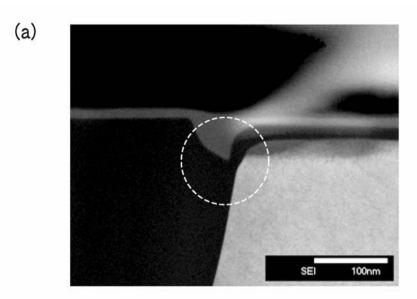

図30はフルオロカーボン膜を除去する工程を行っていない試料と行った試料とにおける素子分離膜端部の断面形状を示すTEM像である。図30(a)はフルオロカーボン膜を除去する工程を行っていない試料の断面TEM像であり、図30(b)はフルオロカーボン膜を除去する工程を行った試料の断面TEM像である。

#### [0109]

図示するように、フルオロカーボン膜を除去する工程を行った試料では、フルオロカーボン膜を除去する工程を行っていない試料と比較して、窪みの深部(図中、点線で囲った部分)における形状がなだらかになっている。

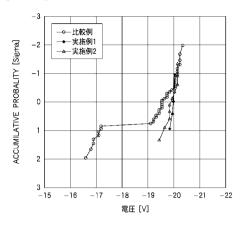

## [0110]

図31は、高電圧トランジスタのゲート電極に逆バイアス(シリコン基板に対して負電圧)を印加したときのゲート絶縁膜耐圧を累積確率分布に表したものである。図中、 印がフルオロカーボン膜を除去する工程を行っていない試料(比較例)、 印が上述の第1の方法によりフルオロカーボン膜を除去する工程を行った試料(実施例1)、 印が上述の第2の方法によりフルオロカーボン膜を除去する工程を行った試料(実施例2)である

#### [0111]

図示するように、フルオロカーボン膜を除去する工程を行っていない試料では、ゲート 絶縁膜耐圧のばらつきが大きいのに対し、フルオロカーボン膜を除去する工程を行った試 料では、第1の方法及び第2の方法のいずれを用いた場合にも、安定した高いゲート絶縁 膜耐圧を得ることができた。

## [0112]

このように、本実施形態によれば、周辺回路領域のONO膜を除去する際に、トップ絶縁膜及び中間層を除去した後、表面に付着したフルオロカーボン膜を除去する工程を行うので、その後のボトム絶縁膜の除去過程において素子分離膜縁部の窪みの形状が変化することを防止することができる。これにより、素子分離膜端部における電界集中が防止され、周辺トランジスタのゲート絶縁膜の絶縁耐圧劣化を防止することができる。

#### [0113]

## 「第2実施形態]

本発明の第2実施形態による半導体装置の製造方法について図32乃至図36を用いて説明する。図1乃至図28に示す第1実施形態による半導体装置及びその製造方法と同様の構成要素には同一の符号を付し説明を省略し又は簡潔にする。

#### [0114]

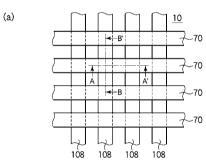

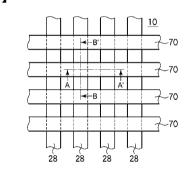

図32は本実施形態による半導体装置の構造を示す平面図及び概略断面図、図33乃至図36は本実施形態による半導体装置の製造方法を示す工程断面図である。

## [0115]

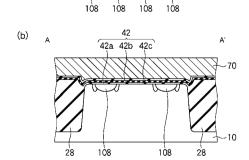

はじめに、本実施形態による半導体装置の構造について図32を用いて説明する。図32(a)は本実施形態による半導体装置の平面図であり、図32(b)は図32(a)のA-A線に沿った概略断面図であり、図32(c)は図32(a)のB-B線に沿った概略断面図である。

10

20

30

40

#### [0116]

本実施形態による半導体装置は、ONO膜を電荷蓄積層とした単層ゲートの不揮発メモリトランジスタを混載したロジック半導体装置である。本実施形態による半導体装置も、第1実施形態による半導体装置と同様、不揮発メモリトランジスタ(Flash)がマトリクス状に形成されたメモリセル領域と、論理回路を構成するロジックトランジスタや不揮発メモリトランジスタの駆動用の高耐圧トランジスタなどの種々の周辺トランジスタが形成された周辺回路領域を有している。本実施形態による半導体装置、周辺トランジスタとして、例えば、高速ロジック回路を構成する低電圧トランジスタ(LV-Tr)と、入出力回路を構成する中電圧トランジスタ(MV-Tr)と、不揮発メモリトランジスタを制御するための高電圧トランジスタ(HV-Tr)を有している。

[0117]

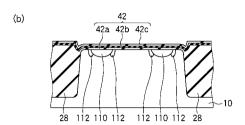

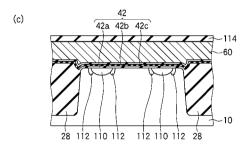

図32(a)に示すように、メモリセル領域のシリコン基板10内には、不純物拡散層よりなる複数のビット線108がストライプ状に形成されている。ビット線108が形成されたシリコン基板10上には、ビット線108に交差する方向に延在する複数のコントロールゲート70がストライプ状に形成されている。シリコン基板10とコントロールゲート70との間には、ONO膜42(シリコン酸化膜42c/シリコン室化膜42b/シリコン酸化膜42a)よりなる電荷蓄積層が形成されている(図32(b)及び図32(c)を参照)。

[0118]

これにより、隣接するビット線108線間の領域とコントロールゲート70との交差部にそれぞれ、コントロールゲート70と、当該隣接するビット線108により構成されるソース/ドレイン領域とを有し、ONO膜42を電荷蓄積層とする不揮発メモリトランジスタが構成されている。コントロールゲート70間の領域には、図32(c)に示すように、シリコン酸化膜80よりなるライナー膜と、シリコン窒化膜76が埋め込まれている。なお、図32(b)及び図32(c)では説明の便宜上、両端に素子分離膜28を記載しているが、実際には、素子分離膜28はメモリセル領域の周辺を囲うように形成される

[0119]

周辺回路領域に形成された低電圧トランジスタ(LV-Tr)、中電圧トランジスタ(MV-Tr)及び高電圧トランジスタ(HV-Tr)は、第1実施形態による半導体装置の場合と同様であるので、ここでは説明を省略する。

[0120]

次に、本実施形態による半導体装置の製造方法について図33乃至図36を用いて説明する。図33及び図34は図32のA-A 線に沿った工程断面図であり、図35及び図36は図32(a)のB-B 線に沿った工程断面図である。

[0121]

なお、周辺トランジスタの製造プロセスは第1実施形態による半導体装置の製造方法と基本的に同じであるため、ここでは不揮発メモリトランジスタの製造プロセスを中心に説明する。周辺トランジスタの製造プロセスについては、必要に応じて第1実施形態の図面を参照しながら説明する。

[0122]

まず、図3万至図10に示す第1実施形態による半導体装置の製造方法と同様にして、 STI法により、活性領域を画定する素子分離膜28を形成する。

[0123]

次いで、素子分離膜28により画定されたシリコン基板10の活性領域上に、例えば熱酸化法により、シリコン酸化膜よりなる犠牲酸化膜32を形成する(図33(a))。

[0124]

次いで、フォトリソグラフィ及びイオン注入により、メモリセル領域及び高電圧トランジスタ形成領域に所定のウェル(図示せず)を形成する。例えば、メモリセル領域及びN型高電圧トランジスタ形成領域にはN型ウェル内にP型ウェルが形成された二重ウェルを

10

20

30

40

10

20

30

50

形成し、P型高電圧トランジスタ形成領域にはN型ウェルを形成する。

### [0125]

次いで、窒素雰囲気中で、例えば900~1200 の温度で1~15秒間の熱処理を 行い、注入した不純物を活性化する。

#### [0126]

次いで、例えば純水により10:1~200:1程度に希釈された弗酸水溶液によりウェットエッチングを行い、犠牲酸化膜32を除去する。

### [0127]

なお、素子分離膜28は、シリコン酸化膜12や犠牲酸化膜32の除去工程などにおいて徐々に膜減りする。これにより、犠牲酸化膜32を除去した後には、素子分離膜28と活性領域との境目に、活性領域表面より窪んだ窪みが形成されている。

#### [0128]

次いで、シリコン基板 1 0 の表面に、熱酸化法により、例えば膜厚 5 ~ 1 4 n m のシリコン酸化膜 4 2 a を形成する。

### [0129]

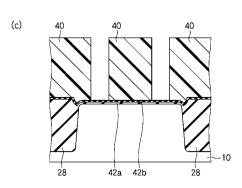

次いで、全面に、例えば熱 C V D 法により、例えば膜厚が 5 ~ 1 4 n m のシリコン窒化膜 4 2 b を形成する(図 3 3 ( b ) )。

## [0130]

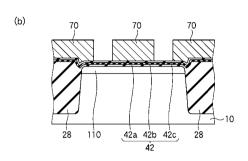

次いで、シリコン窒化膜42b上に、フォトリソグラフィにより、周辺回路領域の全面を覆い、メモリセル領域のビット線形成領域を露出するフォトレジスト膜40を形成する(図33(c))。

#### [0131]

次いで、フォトレジスト膜40をマスクとしてイオン注入を行い、メモリセル領域内に、ビット線108となる不純物拡散領域110と、不純物拡散領域110の縁部に設けられたポケット領域としての不純物拡散領域112とを形成する(図34(a))。

#### [0132]

次いで、アッシング及びその後の後処理により、シリコン窒化膜42b上のフォトレジスト膜40を除去する。

## [0133]

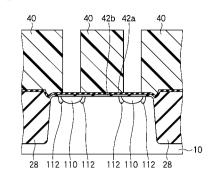

次いで、シリコン窒化膜42b上に、シリコン酸化膜42cを形成する。シリコン酸化膜42cは、例えば、熱酸化法によりシリコン窒化膜42bを熱酸化した後、熱CVD法により高温酸化(HTO:High Temperature Oxide)膜を形成することにより、形成する

## [0134]

こうして、シリコン酸化膜 4 2 c / シリコン窒化膜 4 2 b / シリコン酸化膜 4 2 b の積層膜を形成し、ONO膜 4 2 よりなる電荷蓄積層とする(図 3 4 (b))。このように形成したONO膜 4 2 は、第 1 実施形態の場合と同様、周辺回路領域にも形成される(図 1 5 (a)参照)。

## [0135]

次いで、フォトリソグラフィ及びイオン注入により、低電圧トランジスタ形成領域及び中電圧トランジスタ形成領域に所定のウェル(図示せず)を形成する。例えば、N型低電圧トランジスタ形成領域及びN型中電圧トランジスタ形成領域にP型ウェルを形成し、P型低電圧トランジスタ形成領域及びP型中電圧トランジスタ形成領域にN型ウェルを形成する。

#### [0136]

次いで、図15(a)~図16(a)に示す第1実施形態による半導体装置の製造方法と同様にして、周辺回路領域のONO膜42を除去する。本実施形態の場合にも、ONO膜42は、素子分離膜28と活性領域との境目の窪み内にも形成されている。そこで、シリコン酸化膜42c及びシリコン窒化膜42bを除去した後には、第1実施形態と同様のフルオロカーボン膜の除去工程を行い、高電圧トランジスタの絶縁耐圧劣化を防止する。

#### [0137]

具体的には、周辺回路領域を露出しメモリセル領域を覆うフォトレジスト膜44を形成後、このフォトレジスト膜44をマスクとして、例えばマグネトロン反応性イオンエッチング装置を用いたドライエッチングにより、シリコン酸化膜42c及びシリコン窒化膜42bをエッチングする。次いで、シリコン酸化膜42c及びシリコン窒化膜42bのエッチングに伴い基板の表面に付着したフルオロカーボン膜を、第1実施形態に記載の第1の方法又は第2の方法により、除去する。次いで、フォトレジスト膜44をマスクとして、例えば純水により100:1~200:1程度に希釈された弗酸水溶液によりウェットエッチングを行い、シリコン酸化膜42aを除去する。次いで、アッシング及びその後の後処理により、フォトレジスト膜44を除去する。

10

20

## [0138]

このようにしてONO膜42を除去することにより、素子分離膜28と活性領域との境目の窪みの形状が変化することを防止することができる。

## [0139]

次いで、図17(a)~図21(a)に示す第1実施形態による半導体装置の製造方法と同様にして、低電圧トランジスタ形成領域、中電圧トランジスタ形成領域及び高電圧トランジスタ形成領域に、互いに膜厚の異なる3種類のゲート絶縁膜52,54,56を形成する(図21(a)参照)。

[0140]

次いで、全面に、例えば C V D 法により、例えば膜厚 5 0 ~ 2 0 0 n m のポリシリコン膜 6 0 を形成する。ポリシリコン膜 6 0 は、不揮発メモリトランジスタのコントロールゲート 7 0 及び周辺トランジスタのゲート電極 8 4 となる膜である。

[0141]

次いで、ポリシリコン膜 60 上に、例えば CVD 法により、例えば膜厚  $15 \sim 40$  n m のシリコン酸化膜 114 を形成する(図 34 ( c ))。

[0142]

次いで、シリコン酸化膜 1 1 4 上に、スピンコート法により、 B A R C 膜 6 4 とフォトレジスト膜 6 6 とを形成する。

[0143]

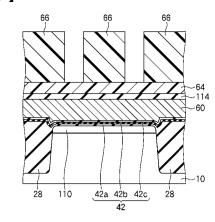

次いで、フォトリソグラフィによりフォトレジスト膜66をパターニングし、周辺回路 領域の全面及びメモリセル領域のコントロールゲート形成領域を覆うフォトレジスト膜6 6を形成する(図35(a))。

30

#### [0144]

次いで、フォトレジスト膜66をマスクとして、例えば誘導結合型プラズマエッチング 装置を用いた異方性エッチングにより、BARC膜64、シリコン酸化膜114及びポリシリコン膜60をパターニングし、メモリセル領域に、ポリシリコン膜60よりなるコントロールゲート70を形成する。

[0145]

次いで、アッシング及びその後の後処理により、ポリシリコン膜60上に残存するシリコン酸化膜114、BARC膜64及びフォトレジスト膜66を除去する(図35(b))。なお、周辺回路領域は、ポリシリコン膜60によって全面が覆われたままの状態である(図25(a)参照)。

40

## [0146]

次いで、全面に、例えば熱 C V D 法により、例えば膜厚 1 ~ 2 0 n m のシリコン酸化膜 8 0 と、例えば膜厚 5 0 ~ 1 7 0 n m のシリコン窒化膜 7 6 とを形成する(図 3 6 ( a ) 。

#### [0147]

次いで、ドライエッチングにより、シリコン酸化膜80の上面が露出するまでシリコン 窒化膜76を異方性エッチングし、コントロールゲート70間の間隙を、シリコン酸化膜 116及びシリコン窒化膜76により埋め込む(図36(b))。こうして、本実施形態

の不揮発メモリトランジスタを完成する。

## [0148]

次いで、図26乃至図28に示す第1実施形態による半導体装置の製造方法と同様にして、周辺回路領域のポリシリコン膜60をパターニングしてゲート電極84を形成後、ソース/ドレイン領域96を形成し、低電圧トランジスタ、中電圧トランジスタ及び高電圧トランジスタを完成する。

#### [0149]

この後、サリサイドプロセスや、多層配線プロセスなどの所定のバックエンドプロセス を経て、半導体装置を完成する。

## [0150]

このように、本実施形態によれば、周辺回路領域のONO膜を除去する際に、トップ絶縁膜及び中間層を除去した後、表面に付着したフルオロカーボン膜を除去する工程を行うので、その後のボトム絶縁膜の除去過程において素子分離膜縁部の窪みの形状が変化することを防止することができる。これにより、素子分離膜端部における電界集中が防止され、周辺トランジスタのゲート絶縁膜の絶縁耐圧劣化を防止することができる。

#### [0151]

#### 「第3実施形態]

本発明の第3実施形態による半導体装置の製造方法について図37乃至図40を用いて説明する。図1乃至図28に示す第1実施形態による半導体装置及びその製造方法、並びに図32乃至図36に示す第2実施形態による半導体装置及びその製造方法と同様の構成要素には同一の符号を付し説明を省略し又は簡潔にする。

#### [ 0 1 5 2 ]

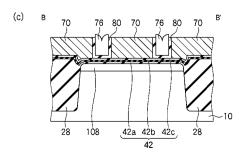

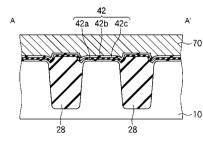

図37は本実施形態による半導体装置の構造を示す平面図及び概略断面図、図38乃至 図40は本実施形態による半導体装置の製造方法を示す工程断面図である。

#### [0153]

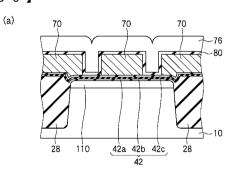

はじめに、本実施形態による半導体装置の構造について図37を用いて説明する。図37(a)は本実施形態による半導体装置の平面図であり、図37(b)は図37(a)のA-A線に沿った概略断面図であり、図37(c)は図37(a)のB-B線に沿った概略断面図である。

## [0154]

本実施形態による半導体装置は、ONO膜を電荷蓄積層とした単層ゲートの不揮発メモリトランジスタを混載したロジック半導体装置である。本実施形態による半導体装置も、第1実施形態による半導体装置と同様、不揮発メモリトランジスタ(Flash)がマトリクス状に形成されたメモリセル領域と、論理回路を構成するロジックトランジスタや不揮発メモリトランジスタの駆動用の高耐圧トランジスタなどの種々の周辺トランジスタが形成された周辺回路領域を有している。本実施形態による半導体装置、周辺トランジスタとして、例えば、高速ロジック回路を構成する低電圧トランジスタ(LV・Tr)と、入出力回路を構成する中電圧トランジスタ(MV・Tr)と、不揮発メモリトランジスタを制御するための高電圧トランジスタ(HV・Tr)を有している。

#### [0155]

図37(a)に示すように、メモリセル領域のシリコン基板10内には、複数の素子分離膜28がストライプ状に形成されている。素子分離膜28が形成されたシリコン基板10上には、素子分離膜28に交差する方向に延在する複数のコントロールゲート70がストライプ状に形成されている。シリコン基板10とコントロールゲート70との間には、ONO膜42(シリコン酸化膜42c/シリコン窒化膜42b/シリコン酸化膜42a)よりなる電荷蓄積層が形成されている。コントロールゲート70間の領域のシリコン基板10内には、ソース/ドレイン領域98が形成されている。(図37(b)及び図37(c)を参照)。

### [0156]

これにより、隣接する素子分離膜28間の領域とコントロールゲート70との交差部に

10

20

30

40

それぞれ、コントロールゲート70と、コントロールゲート70の両側のシリコン基板10内に形成されたソース/ドレイン領域98とを有し、ONO膜42を電荷蓄積層とする不揮発メモリトランジスタが構成されている。コントロールゲート70間の領域には、図37(c)に示すように、シリコン酸化膜80よりなるライナー膜と、シリコン窒化膜76が埋め込まれている。

#### [0157]

周辺回路領域に形成された低電圧トランジスタ(LV-Tr)、中電圧トランジスタ(MV-Tr)及び高電圧トランジスタ(HV-Tr)は、第1実施形態による半導体装置の場合と同様であるので、ここでは説明を省略する。

#### [0158]

次に、本実施形態による半導体装置の製造方法について図38万至図40を用いて説明する。図38は図37のA-A線に沿った工程断面図であり、図39及び図40は図37(a)のB-B線に沿った工程断面図である。

## [0159]

なお、周辺トランジスタの製造プロセスは第1実施形態による半導体装置の製造方法と基本的に同じであるため、ここでは不揮発メモリトランジスタの製造プロセスを中心に説明する。周辺トランジスタの製造プロセスについては、必要に応じて第1実施形態の図面を参照しながら説明する。

#### [ 0 1 6 0 ]

まず、図3乃至図10に示す第1実施形態による半導体装置の製造方法と同様にして、 STI法により、活性領域を画定する素子分離膜28を形成する。

#### 【 0 1 6 1 】

次いで、素子分離膜28により画定されたシリコン基板10の活性領域上に、例えば熱酸化法により、シリコン酸化膜よりなる犠牲酸化膜32を形成する(図38(a))。

#### [0162]

次いで、フォトリソグラフィ及びイオン注入により、メモリセル領域及び高電圧トランジスタ形成領域に所定のウェル(図示せず)を形成する。例えば、メモリセル領域及びN型高電圧トランジスタ形成領域にはN型ウェル内にP型ウェルが形成された二重ウェルを形成し、P型高電圧トランジスタ形成領域にはN型ウェルを形成する。

## [0163]

次いで、窒素雰囲気中で、例えば900~1200 の温度で1~15秒間の熱処理を 行い、注入した不純物を活性化する。

#### **7** 0 1 6 4 3

次いで、例えば純水により10:1~200:1程度に希釈された弗酸水溶液によりウェットエッチングを行い、犠牲酸化膜32を除去する。

#### [0165]

なお、素子分離膜28は、シリコン酸化膜12や犠牲酸化膜32の除去工程などにおいて徐々に膜減りする。これにより、犠牲酸化膜32を除去した後には、素子分離膜28と活性領域との境目に、活性領域表面より窪んだ窪みが形成されている。

#### [0166]

次いで、シリコン基板 1 0 の表面に、熱酸化法により、例えば膜厚 5 ~ 1 4 n m のシリコン酸化膜 4 2 a を形成する。

## [0167]

次いで、全面に、例えば熱 C V D 法により、例えば膜厚が 5 ~ 1 4 n m のシリコン窒化膜 4 2 b を形成する(図 3 3 ( b ) )。

## [0168]

次いで、シリコン窒化膜 4 2 b 上に、例えば熱酸化法により、例えば膜厚が 3 ~ 1 5 n m のシリコン酸化膜 4 2 c を形成する。

### [0169]

こうして、シリコン酸化膜42c/シリコン窒化膜42b/シリコン酸化膜42bの積

10

20

30

50

40

層膜を形成し、ONO膜42よりなる電荷蓄積層とする(図38(b))。このように形成したONO膜42は、第1実施形態の場合と同様、周辺回路領域にも形成される(図15(a)参照)。

### [0170]

次いで、フォトリソグラフィ及びイオン注入により、低電圧トランジスタ形成領域及び中電圧トランジスタ形成領域に所定のウェル(図示せず)を形成する。例えば、N型低電圧トランジスタ形成領域及びN型中電圧トランジスタ形成領域にP型ウェルを形成し、P型低電圧トランジスタ形成領域にN型ウェルを形成する。

## [0171]

次いで、図15(a)~図16(a)に示す第1実施形態による半導体装置の製造方法と同様にして、周辺回路領域のONO膜42を除去する。本実施形態の場合にも、ONO膜42は、素子分離膜28と活性領域との境目の窪み内にも形成されている。そこで、シリコン酸化膜42c及びシリコン窒化膜42bを除去した後には、第1実施形態と同様のフルオロカーボン膜の除去工程を行い、高電圧トランジスタの絶縁耐圧劣化を防止する。【0172】

具体的には、周辺回路領域を露出しメモリセル領域を覆うフォトレジスト膜44を形成後、このフォトレジスト膜44をマスクとして、例えばマグネトロン反応性イオンエッチング装置を用いたドライエッチングにより、シリコン酸化膜42c及びシリコン窒化膜42bのエッチングに伴い基板の表面に付着したフルオロカーボン膜を、第1実施形態に記載の第1の方法又は第2の方法により、除去する。次いで、フォトレジスト膜44をマスクとして、例えば純水により100:1~200:1程度に希釈された弗酸水溶液によりウェットエッチングを行い、シリコン酸化膜42aを除去する。次いで、アッシング及びその後の後処理により、フォトレジスト膜44を除去する。

#### [0173]

このようにしてONO膜42を除去することにより、素子分離膜28と活性領域との境目の窪みの形状が変化することを防止することができる。

## [0174]

次いで、図17(a)~図21(a)に示す第1実施形態による半導体装置の製造方法と同様にして、低電圧トランジスタ形成領域、中電圧トランジスタ形成領域及び高電圧トランジスタ形成領域に、互いに膜厚の異なる3種類のゲート絶縁膜52,54,56を形成する(図21(a)参照)。

## [0175]

次いで、全面に、例えば C V D 法により、例えば膜厚 5 0 ~ 2 0 0 n m のポリシリコン膜 6 0 を形成する。ポリシリコン膜 6 0 は、不揮発メモリトランジスタのコントロールゲート 7 0 及び周辺トランジスタのゲート電極 8 4 となる膜である。

#### [0176]

次いで、ポリシリコン膜 60 上に、例えば CVD 法により、例えば膜厚  $15 \sim 40$  nmのシリコン酸化膜 114 を形成する(図 38 ( c ))。

## [0177]

次いで、シリコン酸化膜 1 1 4 上に、スピンコート法により、 B A R C 膜 6 4 とフォトレジスト膜 6 6 とを形成する。

## [0178]

次いで、フォトリソグラフィによりフォトレジスト膜66をパターニングし、周辺回路 領域の全面及びメモリセル領域のコントロールゲート形成領域を覆うフォトレジスト膜6 6を形成する(図39(a))。

## [0179]

次いで、フォトレジスト膜66をマスクとして、例えば誘導結合型プラズマエッチング 装置を用いた異方性エッチングにより、BARC膜64、シリコン酸化膜114及びポリ 10

20

30

40

シリコン膜 6 0 をパターニングし、メモリセル領域に、ポリシリコン膜 6 0 よりなるコントロールゲート 7 0 を形成する。

#### [0180]

次いで、フォトレジスト膜66及びコントロールゲート70をマスクとしてイオン注入を行い、コントロールゲート70間の領域に、ソース/ドレイン領域98となる不純物拡散領域74を形成する。

#### [0181]

次いで、アッシング及びその後の後処理により、ポリシリコン膜 6 0 上に残存するシリコン酸化膜 1 1 4 、 B A R C 膜 6 4 及びフォトレジスト膜 6 6 を除去する(図 3 9 ( b ) )。なお、周辺回路領域は、ポリシリコン膜 6 0 によって全面が覆われたままの状態である(図 2 5 ( a ) 参照)。

#### [0182]

次いで、全面に、例えば熱 C V D 法により、例えば膜厚 1 ~ 2 0 n m のシリコン酸化膜 8 0 と、例えば膜厚 5 0 ~ 1 7 0 n m のシリコン窒化膜 7 6 とを形成する(図 4 0 ( a ) 。

#### [0183]

次いで、ドライエッチングにより、シリコン酸化膜80の上面が露出するまでシリコン窒化膜76を異方性エッチングし、コントロールゲート70間の間隙を、シリコン酸化膜116及びシリコン窒化膜76により埋め込む(図40(b))。こうして、本実施形態の不揮発メモリトランジスタを完成する。

#### [0184]

次いで、図26乃至図28に示す第1実施形態による半導体装置の製造方法と同様にして、周辺回路領域のポリシリコン膜60をパターニングしてゲート電極84を形成後、ソース/ドレイン領域96を形成し、低電圧トランジスタ、中電圧トランジスタ及び高電圧トランジスタを完成する。

#### [0185]

この後、サリサイドプロセスや、多層配線プロセスなどの所定のバックエンドプロセス を経て、半導体装置を完成する。

## [0186]

このように、本実施形態によれば、周辺回路領域のONO膜を除去する際に、トップ絶縁膜及び中間層を除去した後、表面に付着したフルオロカーボン膜を除去する工程を行うので、その後のボトム絶縁膜の除去過程において素子分離膜縁部の窪みの形状が変化することを防止することができる。これにより、素子分離膜端部における電界集中が防止され、周辺トランジスタのゲート絶縁膜の絶縁耐圧劣化を防止することができる。

## [0187]

「変形実施形態]

本発明は上記実施形態に限らず種々の変形が可能である。

#### [0188]

例えば、上記実施形態では、ゲート間絶縁膜又は電荷蓄積層としてのONO膜を除去する際に本発明を適用した場合を説明したが、本発明の適用対象はONO膜に限定されるものではない。本発明は、素子分離領域とエッチング特性の同等な下層絶縁膜と、この下層絶縁膜上に形成された上層絶縁膜を有し、上層絶縁膜のエッチングにフルオロカーボン系のガスを用いる製造プロセスを用いた半導体装置の製造方法に広く適用することができる

#### [0189]

シリコン系の半導体デバイスでは、下層絶縁膜として、シリコン酸化物系の絶縁膜(シリコン酸化膜やシリコン窒化酸化膜)を適用することができる。また、上層絶縁膜としては、シリコン窒化膜の単層、シリコン窒化膜とシリコン酸化膜との積層膜や、アルミナ(Al $_2$ O $_3$ )膜やハフニア(HfO $_2$ )膜等の高誘電率絶縁膜を含む膜等を適用することができる。

20

10

30

40

#### [0190]

また、上層絶縁膜のエッチングに用いるフルオロカーボン系のガスとしては、上記実施 形態に記載のガスに限らず、ハイドロフルオロカーボン(HFC)やフルオロカーボン( FC)などのフロン類のガスを用いることができる。

## [0191]

また、上記実施形態に記載の半導体装置の構造やプロセス条件は、一例を示したものであり、必要に応じて適宜変更できるものである。

### [0192]

また、上記実施形態では、不揮発メモリトランジスタを混載したロジック半導体装置の 製造プロセスに適用した例を示したが、本発明は、不揮発メモリトランジスタを混載した ロジック半導体装置への適用に限定されるものではない。

#### [0193]

上述のように本発明は、素子分離領域とエッチング特性の同等な下層絶縁膜と、この下層絶縁膜上に形成された上層絶縁膜を有し、上層絶縁膜のエッチングにフルオロカーボン系のガスを用いる製造プロセスを用いた半導体装置の製造方法に広く適用できるものである。特に、下層絶縁膜の下地が段差を有する場合に、本発明を適用する効果がある。

#### [0194]

以上詳述したように、本発明の特徴をまとめると以下の通りとなる。

#### [0195]

(付記1) 半導体基板の表面に、活性領域を画定する素子分離領域を形成する工程と <sup>20</sup>

前記素子分離領域が形成された前記半導体基板上に、第1の絶縁膜を形成する工程と、前記第1の絶縁膜が形成された前記半導体基板上に、前記第1の絶縁膜とはエッチング特性の異なる第2の絶縁膜を形成する工程と、

少なくとも前記活性領域と前記素子分離領域との境界を含む第 1 の領域に形成された前記第 2 の絶縁膜を、フルオロカーボン系のエッチングガスを用いたドライエッチングにより除去する工程と、

酸素を含む雰囲気に曝すことにより、前記ドライエッチングの際に前記第1の絶縁膜上に付着したフルオロカーボン膜を除去する工程と、

前記第1の領域に形成された前記第1の絶縁膜を、ウェットエッチングにより除去する 工程と

を有することを特徴とする半導体装置の製造方法。

#### [0196]

(付記2) 付記1記載の半導体装置の製造方法において、

前記フルオロカーボン膜を除去する工程では、アルゴンガスと酸素ガスとを含む混合ガスを用いた反応性イオンエッチングにより、前記フルオロカーボン膜を除去する ことを特徴とする半導体装置の製造方法。

#### [0197]

(付記3) 付記2記載の半導体装置の製造方法において、

前記酸素ガスの流量は、プロセスガスの総流量に対して、 0 . 5 ~ 2 5 %であることを特徴とする半導体装置の製造方法。

#### [0198]

(付記4) 付記2又は3記載の半導体装置の製造方法において、

前記第2の絶縁膜を除去する工程と、前記フルオロカーボン膜を除去する工程は、同一の処理室内で連続して行う

ことを特徴とする半導体装置の製造方法。

#### [0199]

(付記5) 付記1記載の半導体装置の製造方法において、

前記フルオロカーボン膜を除去する工程では、CF<sub>4</sub>ガスと酸素ガスとを含む混合ガスを用いたケミカルドライエッチングにより、前記フルオロカーボン膜を除去する

50

10

30

ことを特徴とする半導体装置の製造方法。

### [0200]

(付記6) 付記5記載の半導体装置の製造方法において、

前記混合ガスは、フォーミングガスを更に含む

ことを特徴とする半導体装置の製造方法。

#### [0201]

(付記7) 付記5又は6記載の半導体装置の製造方法において、

前記CF』ガスの流量は、プロセスガスの総流量に対して、0.05~10%である ことを特徴とする半導体装置の製造方法。

[0202]

10

(付記8) 付記1乃至7のいずれか1項に記載の半導体装置の製造方法において、 前記素子分離領域を形成する工程の後、前記第1の絶縁膜を形成する工程の前に、前記 素子分離領域を構成する第3の絶縁膜の上部をエッチングする工程を更に有し、

前記第1の絶縁膜の形成の際、前記活性領域と前記素子分離領域との前記境界近傍の前 記素子分離領域に、前記活性領域の表面よりも窪んだ窪みが形成されている

ことを特徴とする半導体装置の製造方法。

#### [0203]

(付記9) 付記8記載の半導体装置の製造方法において、 前記第3の絶縁膜は、前記第1の絶縁膜と同等のエッチング特性を有する ことを特徴とする半導体装置の製造方法。

20

#### [0204]

(付記10) 付記1乃至9のいずれか1項に記載の半導体装置の製造方法において、 前記第1の絶縁膜を除去する工程の後に、前記第1の領域内の前記活性領域にゲート絶 縁膜を形成する工程と、前記ゲート絶縁膜上にゲート電極を形成する工程とを更に有し、 前記第1の領域内の前記活性領域に、前記ゲート絶縁膜及び前記ゲート電極を有するM ISトランジスタを形成する

ことを特徴とする半導体装置の製造方法。

#### [0205]

(付記11) 付記10記載の半導体装置の製造方法において、

前記ゲート電極を形成する工程では、前記第1の絶縁膜を除去することにより露出した 前記半導体基板を熱酸化することにより形成した第4の絶縁膜を少なくとも含む前記ゲー ト電極を形成する

30

ことを特徴とする半導体装置の製造方法。

## [0206]

(付記12) 付記1乃至11のいずれか1項に記載の半導体装置の製造方法において

前記第1の領域とは異なる第2の領域内の活性領域に、前記第1の絶縁膜及び前記第2 の絶縁膜を有する不揮発メモリトランジスタを形成する工程を更に有する

ことを特徴とする半導体装置の製造方法。

#### [0207]

40

(付記13) 付記12記載の半導体装置の製造方法において、

前記素子分離領域を形成する工程の後、前記第1の絶縁膜を形成する工程の前に、前記 第2の領域内の前記活性領域上にトンネル絶縁膜を形成する工程と、前記トンネル絶縁膜 上に、前記第2の領域にフローティングゲートを形成する工程とを、

前記第1の絶縁膜を除去する工程の後に、前記第1の絶縁膜及び前記第2の絶縁膜を介 して前記フローティングゲート上にコントロールゲートを形成する工程を、更に有し、

前記フローティングゲートと前記コントロールゲートとを有するスタックゲート構造の 前記不揮発メモリトランジスタを形成する

ことを特徴とする半導体装置の製造方法。

## [0208]

(付記14) 付記12記載の半導体装置の製造方法において、

前記第1の絶縁膜を除去する工程の後に、前記第1の絶縁膜及び前記第2の絶縁膜を介してコントロールゲートを形成する工程を更に有し、

前記第1の絶縁膜及び前記第2の絶縁膜を電荷蓄積層とする単層ゲート構造の前記不揮発メモリトランジスタを形成する

ことを特徴とする半導体装置の製造方法。

[0209]

(付記15) 付記1乃至14のいずれか1項に記載の半導体装置の製造方法において

前記素子分離領域を形成する工程では、前記半導体基板に形成されたトレンチに絶縁膜を埋め込むことにより、前記素子分離領域を形成する

ことを特徴とする半導体装置の製造方法。

[0210]

(付記16) 付記1乃至15のいずれか1項に記載の半導体装置の製造方法において

前記第1の絶縁膜は、シリコン酸化膜であることを特徴とする半導体装置の製造方法。

[ 0 2 1 1 ]

(付記17) 付記1乃至16のいずれか1項に記載の半導体装置の製造方法において

20

10

前記第2の絶縁膜は、シリコン窒化膜であることを特徴とする半導体装置の製造方法。

[0212]

(付記18) 付記1乃至16のいずれか1項に記載の半導体装置の製造方法において

前記第2の絶縁膜は、シリコン窒化膜とシリコン酸化膜との積層膜であることを特徴とする半導体装置の製造方法。

【図面の簡単な説明】

[0213]

【図1】本発明の第1実施形態による半導体装置の構造を示す平面図である。

30

- 【図2】本発明の第1実施形態による半導体装置の構造を示す概略断面図である。

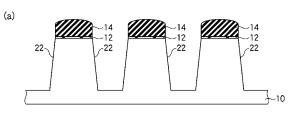

- 【図3】本発明の第1実施形態による半導体装置の製造方法を示す工程断面図(その1)である。

- 【図4】本発明の第1実施形態による半導体装置の製造方法を示す工程断面図(その2)である。

- 【図5】本発明の第1実施形態による半導体装置の製造方法を示す工程断面図(その3)である。

- 【図 6 】本発明の第1実施形態による半導体装置の製造方法を示す工程断面図(その4) である。

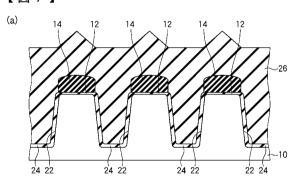

- 【図7】本発明の第1実施形態による半導体装置の製造方法を示す工程断面図(その5) 40 である。

- 【図8】本発明の第1実施形態による半導体装置の製造方法を示す工程断面図(その6) である。

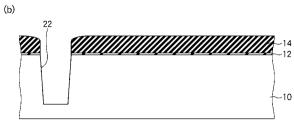

- 【図9】本発明の第1実施形態による半導体装置の製造方法を示す工程断面図(その7) である。

- 【図10】本発明の第1実施形態による半導体装置の製造方法を示す工程断面図(その8)である。

- 【図11】本発明の第1実施形態による半導体装置の製造方法を示す工程断面図(その9)である。

- 【図12】本発明の第1実施形態による半導体装置の製造方法を示す工程断面図(その1

10

30

40

- 0)である。

- 【図13】本発明の第1実施形態による半導体装置の製造方法を示す工程断面図(その11)である。

- 【図14】本発明の第1実施形態による半導体装置の製造方法を示す工程断面図(その1 2)である。

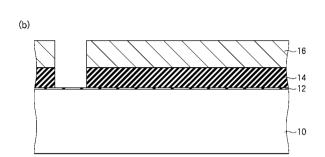

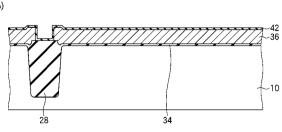

- 【図15】本発明の第1実施形態による半導体装置の製造方法を示す工程断面図(その13)である。

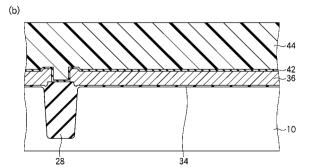

- 【図16】本発明の第1実施形態による半導体装置の製造方法を示す工程断面図(その14)である。

- 【図17】本発明の第1実施形態による半導体装置の製造方法を示す工程断面図(その1 5)である。

- 【図18】本発明の第1実施形態による半導体装置の製造方法を示す工程断面図(その16)である。

- 【図19】本発明の第1実施形態による半導体装置の製造方法を示す工程断面図(その17)である。

- 【図 2 0 】本発明の第 1 実施形態による半導体装置の製造方法を示す工程断面図(その 1 8 )である。

- 【図21】本発明の第1実施形態による半導体装置の製造方法を示す工程断面図(その19)である。

- 【図22】本発明の第1実施形態による半導体装置の製造方法を示す工程断面図(その2 200)である。

- 【図23】本発明の第1実施形態による半導体装置の製造方法を示す工程断面図(その21)である。

- 【図24】本発明の第1実施形態による半導体装置の製造方法を示す工程断面図(その2 2)である。

- 【図25】本発明の第1実施形態による半導体装置の製造方法を示す工程断面図(その23)である。

- 【図26】本発明の第1実施形態による半導体装置の製造方法を示す工程断面図(その24)である。

- 【図27】本発明の第1実施形態による半導体装置の製造方法を示す工程断面図(その25)である。

- 【図28】本発明の第1実施形態による半導体装置の製造方法を示す工程断面図(その2 6)である。

- 【図29】ONO膜の除去過程におけるフルオロカーボン膜の影響を説明する図である。

- 【図30】フルオロカーボン膜を除去する工程を行っていない試料と行った試料とにおける素子分離膜端部の断面形状を示すTEM像である。

- 【図31】高電圧トランジスタのゲート電極に逆バイアスを印加したときのゲート絶縁膜 耐圧を示すグラフである。

- 【図32】本発明の第2実施形態による半導体装置の構造を示す平面図及び概略断面図である。

- 【図33】本発明の第2実施形態による半導体装置の製造方法を示す工程断面図(その1)である

- 【図34】本発明の第2実施形態による半導体装置の製造方法を示す工程断面図(その2)である。

- 【図35】本発明の第2実施形態による半導体装置の製造方法を示す工程断面図(その3)である。

- 【図36】本発明の第2実施形態による半導体装置の製造方法を示す工程断面図(その4)である。

- 【図37】本発明の第3実施形態による半導体装置の構造を示す平面図及び概略断面図である。

- 【図38】本発明の第3実施形態による半導体装置の製造方法を示す工程断面図(その1)である。

- 【図39】本発明の第3実施形態による半導体装置の製造方法を示す工程断面図(その2)である。

- 【図40】本発明の第3実施形態による半導体装置の製造方法を示す工程断面図(その3)である。

#### 【符号の説明】

- [0214]

- 10…シリコン基板

- 12,24,26,42a、42c,46,50,80,114...シリコン酸化膜

- 14,42b,62,76...シリコン窒化膜

- 16,36,60...ポリシリコン膜

- 18,38,64,82...BARC膜

- 20,30,40,44,48,52,66,84...フォトレジスト膜

- 22...トレンチ

- 28...素子分離膜

- 3 2 ... 犠牲酸化膜

- 3 4 ... トンネル絶縁膜

- 4 2 ... O N O 膜

- 5 4 , 5 6 , 5 8 ... ゲート絶縁膜

- 68...フローティングゲート

- 70…コントロールゲート

- 7 2 , 7 8 , 9 0 ... 側壁絶縁膜

- 74,88,92,94,110,112...不純物拡散領域

- 8 6 ... ゲート電極

- 96,98...ソース/ドレイン領域

- 100…窪み

- 102…フルオロカーボン膜

- 104...ボトム酸化膜

- 108...ビット線

30

10

【図1】

【図2】

【図3】

【図4】

## 【図5】

## 【図6】

## 【図7】

## 【図8】

## 【図9】

## 【図10】

## 【図11】

## 【図12】

## 【図13】

## 【図14】

(b)

(b) 38 36 10

# 【図15】

【図16】

## 【図17】

## 【図18】

(b)

(b) 48 42 36

# 【図19】

# 【図20】

【図21】

(a) 54 56 58 10 10

## 【図22】

【図23】

【図24】

## 【図25】

## 【図26】

## 【図27】

# 【図28】

【図29】

【図32】

【図31】

## 【図33】

(a)

## 【図34】

(a)

## 【図35】

(a)

## 【図36】

## 【図37】

(a)

## 【図38】

(a)

(b)

(c)

# 【図40】

(a)

(b)

## 【図39】

(a)

【図30】

## フロントページの続き

(51) Int.CI. F I

H 0 1 L 29/792 (2006.01) H 0 1 L 21/76 (2006.01)

(72)発明者 姉崎 徹

神奈川県川崎市中原区上小田中4丁目1番1号 富士通株式会社内

(72)発明者 小川 裕之

神奈川県川崎市中原区上小田中4丁目1番1号 富士通株式会社内

(72)発明者 有吉 潤一

神奈川県川崎市中原区上小田中4丁目1番1号 富士通株式会社内

審査官 堀江 義隆

(56)参考文献 特開2006-286788(JP,A)

特開2003-282743(JP,A)

特開平11-265882(JP,A)

(58)調査した分野(Int.CI., DB名)

H01L 21/8247

H01L 21/336

H01L 21/76

H01L 27/10

H01L 27/115

H01L 29/788

H01L 29/792