## (19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第6546258号 (P6546258)

(45) 発行日 令和1年7月17日(2019.7.17)

(24) 登録日 令和1年6月28日 (2019.6.28)

| (51) Int.Cl. |               |           | FΙ   |        |         |          |        |

|--------------|---------------|-----------|------|--------|---------|----------|--------|

| G02F         | 1/1368        | (2006.01) | GO2F | 1/1368 |         |          |        |

| GO2F         | 1/1343        | (2006.01) | GO2F | 1/1343 |         |          |        |

| G09F         | 9/30          | (2006.01) | GO9F | 9/30   | 338     |          |        |

| GO3B         | 21/00         | (2006.01) | GO3B | 21/00  | E       |          |        |

| HO1L         | <i>29/786</i> | (2006.01) | HO1L | 29/78  | 612C    |          |        |

|              |               |           |      |        | 請求項の数 2 | (全 23 頁) | 最終頁に続く |

(21) 出願番号 特願2017-240891 (P2017-240891) (22) 出願日 平成29年12月15日 (2017.12.15) (62) 分割の表示 特願2016-92848 (P2016-92848) の分割 平成12年8月24日 (2000.8.24) 原出願日 (65) 公開番号 特開2018-87980 (P2018-87980A) (43) 公開日 平成30年6月7日(2018.6.7) 審査請求日 平成29年12月18日 (2017.12.18) (31) 優先権主張番号 特願平11-246798 (32) 優先日 平成11年8月31日 (1999.8.31) (33) 優先権主張国 日本国(JP)

||(73)特許権者 000153878

株式会社半導体エネルギー研究所 神奈川県厚木市長谷398番地

(72)発明者 柴田 寬

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

|(72)発明者 磯部 敦生

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 岩村 貴

最終頁に続く

(54) 【発明の名称】液晶表示装置、プロジェクター

## (57)【特許請求の範囲】

## 【請求項1】

基板と、

前記基板上の走査線と、

前記走査線上の第1の絶縁膜と、

前記第1の絶縁膜上の、結晶質シリコン膜を有する半導体層と、

前記半導体層上の第2の絶縁膜と、

前記第2の絶縁膜上のゲート電極と、

前記第2の絶縁膜上の第1の導電膜と、

前記ゲート電極上及び前記第1の導電膜上の第3の絶縁膜と、

前記第3の絶縁膜上の信号線と、

前記第3の絶縁膜上の電極と、

前記信号線上及び前記電極上の第4の絶縁膜と、

前記第4の絶縁膜上の画素電極と、を有する画素を複数有し、

前記信号線は、前記半導体層と電気的に接続され、

前記画素電極は、前記電極を介して前記半導体層と電気的に接続され、

前記ゲート電極は、前記走査線と電気的に接続され、

前記走査線は、第1の方向にのびており、

前記信号線は、第2の方向にのびており、

前記半導体層は、前記第1の方向に沿ってのび且つ前記走査線と重なる部分と、前記第

2 の方向に沿ってのび且つ前記信号線と重なる部分と、を有し、

前記ゲート電極は、前記半導体層のチャネル形成領域と重なり、

前記第1の導電膜は、前記半導体層の一部と重なり、

前記半導体層の前記一部は、保持容量の下部電極として機能し、

前記第1の方向における前記走査線の長さは、前記第1の方向における前記ゲート電極の長さよりも長いことを特徴とする液晶表示装置。

#### 【 請 求 項 2 】

請求項1に記載の液晶表示装置を用いたプロジェクター。

【発明の詳細な説明】

### 【技術分野】

[0001]

本願発明は薄膜トランジスタ(以下、TFTという)で構成された回路を有する半導体装置およびその作製方法に関する。例えば、液晶表示パネルに代表される電気光学装置およびその様な電気光学装置を部品として搭載した電子機器に関する。

#### [0002]

なお、本明細書中において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指し、電気光学装置、半導体回路および電子機器は全て半導体装置である。

### 【背景技術】

[0003]

近年、絶縁表面を有する基板上に形成された半導体薄膜(厚さ数~数百nm程度)を用いて薄膜トランジスタ(TFT)を構成する技術が注目されている。薄膜トランジスタはICや電気光学装置のような電子デバイスに広く応用され、特に液晶表示装置のスイッチング素子として開発が急がれている。

#### [0004]

液晶表示装置において、高品位な画像を得るために、画素電極をマトリクス状に配置し、画素電極の各々に接続するスイッチング素子としてTFTを用いたアクティブマトリクス型液晶表示装置が注目を集めている。

## [00005]

このアクティブマトリクス型液晶表示装置において、良好な品質の表示を行わせるには、TFTに接続された各画素電極に映像信号の電位を次回の書き込み時まで保持できるようにする必要がある。一般的には、画素内に保持容量(CS)を備えることで映像信号の電位を保持している。

### [0006]

上記保持容量(Cs)の構造やその形成法として様々な提案がなされているが、製造工程の簡素さ、また信頼性の観点から、画素を構成する絶縁膜のうち、最も質の高い絶縁膜であるTFTのゲート絶縁膜を保持容量(Cs)の誘電体として利用することが望ましい。従来では、図18に示したように走査線と同じ配線層を用いて上部電極となる容量配線を設け、上部電極(容量配線)/誘電体層(ゲート絶縁膜)/下部電極(半導体膜)により保持容量(Cs)を構成することが行われていた。

### [0007]

また、表示性能の面から画素には大きな保持容量を持たせるとともに、高開口率化が求められている。各画素が高い開口率を持つことによりバックライトの光利用効率が向上し、所定の表示輝度を得るためのバックライト容量が抑制できる結果、表示装置の省電力化および小型化が達成できる。また、各画素が大きな保持容量を備えることにより、各画素の表示データ保持特性が向上して表示品質が向上する。

## [0008]

こうした要求は、液晶表示装置の高精細化(画素数の増大)及び小型化に伴う各表示画素ピッチの微細化を進める上で大きな課題となっている。

## [0009]

加えて、上述した従来の画素構成では高開口率と大きな保持容量の両立が難しいという問

10

20

30

40

題がある。

## 【発明の概要】

【発明が解決しようとする課題】

#### [ 0 0 1 0 ]

従来の画素構成を表 1 のデザインルールに従い 1 9 . 2 μm の画素サイズで実施した 従来例を図 1 8 に示す。

### 【表1】

Si層:min. Size=0. 8μm, min. Spacing=1. 5μm ゲート電極:min. Size=1. 0μm, min. Spacing=1. 5μm

10

20

走査線: min. Size=1. 5 μ m, min. Spacing=1. 5 μ m 信号線とSi層とのコンタクトホール: min. Size=1 μ m コンタクトホールとSi層とのmargin=1. 0 μ m コンタクトホールと走査線(ゲート電極)との間隔min. Spacing=1. 3 μ m

信号線: min. Size=1. 5  $\mu$  m, min. Spacing=1. 5  $\mu$  m コンタクトホールと信号線とのmargin=1. 3  $\mu$  m

画素サイズ:19.2μm□

画素TFT:L=1.5  $\mu$  m、W=0.8  $\mu$  m、シングルゲート

走査線:配線幅min. Size=1.0 μ m

走査線:Si層乗り越え部における配線幅min. Size=1.5μm

|容量配線:min. Size=2. 0μm

### [0011]

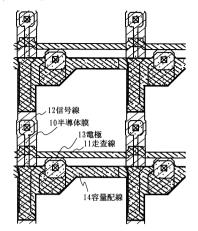

走査線と容量配線の2本を各々連続的に形成する関係上、配線を2本(走査線と容量配線)平行に配置していることが従来の特徴である。図18において、10は半導体膜、11は走査線、12は信号線、13は電極、14は容量配線である。なお、図18は、画素の上面図を簡略化したものであり、電極13に接続する画素電極及び電極13に達するコンタクトホールは図示していない。

## [0012]

30

こうした上部電極(容量配線)/誘電体層(ゲート絶縁膜)/下部電極(半導体膜)による保持容量構成とした場合、画素の回路構成に必要な回路要素(画素 TFT,保持容量,コンタクトホール等)は全てゲート絶縁膜関連のものとなり、回路要素を構成するこれらの素子は各画素中にほぼ平面的に配置される。

## [0013]

このことから、規定の画素サイズの中で各画素の高開口率と大きな保持容量とを両方得るためには、画素の回路構成に必要な回路要素を効率よくレイアウトすることが不可欠である。このことは、回路要素が全てゲート絶縁膜関連のものであることからゲート絶縁膜の利用効率を向上することが不可欠と言い換えることができる。

## [0014]

40

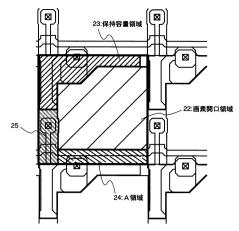

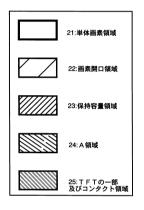

こうした観点から図18の例において画素の回路構成における平面レイアウト効率を表したものが図19である。図19中、21は単体画素領域、22は画素開口領域、23は保持容量領域、24はA領域、25はTFTの一部及びコンタクト領域を示している。

## [0015]

図 1 9 では画素開口領域 2 2 の面積 2 1 6 . 7  $\mu$  m<sup>2</sup> (開口率 5 8 . 8 %) に対し、保持容量領域 2 3 の面積 6 4 . 2  $\mu$  m<sup>2</sup>、 T F T の一部及びコンタクト領域 2 5 の面積 4 2 . 2  $\mu$  m<sup>2</sup>、 A 領域 2 4 の面積 3 4 . 1  $\mu$  m<sup>2</sup>で構成されている。

### [0016]

このA領域24は、TFTのゲート電極として働いている領域を相互に接続する配線部及び走査線と容量配線とを平行に配置していることに起因する走査線及び容量配線の分離領

域であり、A領域のゲート絶縁膜は本来の機能を与えられておらず、レイアウト効率を低下させる原因となっている。

#### [0017]

さらに、上記構造の場合、容量配線抵抗に対する要求が厳しくなる問題がある。

### [0018]

通常の液晶表示装置駆動では、各走査線に接続されている複数の各画素に走査線方向で連続的に(点順次駆動の場合)、または同時に(線順次駆動の場合)映像信号の電位の書き込みが行われる。

## [0019]

この際、上記の画素構成では容量配線が走査線に平行に配置されている関係上、各走査線に接続されている複数の画素が共通の容量配線に接続されているため、該当する容量配線には画素書き込み電流に対応する対向電流が複数画素分、連続的にまたは同時に流れることになり、容量配線の電位変動による表示品質の低下を避けるためには容量配線抵抗を十分に下げておく必要がある。

## [0020]

しかし、容量配線抵抗の低抵抗化のために線幅を広げることは保持容量の占める面積を拡 大する一方、画素の開口率を損なってしまっていた。

### [0021]

本発明は上述の問題に設計側から解決策を与えるものであり、高い開口率を得ながら十分な保持容量(Cs)を確保し、また同時に容量配線の負荷(画素書き込み電流)を時間的に分散させて実効的に低減する事により、高い表示品質をもつ液晶表示装置を提供するものである。

【課題を解決するための手段】

#### [0022]

本明細書で開示する発明の構成は、

絶縁表面上に第1配線と、

前記第1配線上に第1絶縁膜と、

前記第1絶縁膜上に半導体膜と、

前記半導体膜上に第2絶縁膜と、

前記第2絶縁膜上に第2配線と、前記第1配線と接続するゲート電極と、

前記第2配線及び前記ゲート電極上に第3絶縁膜と、

前記第3絶縁膜上に前記半導体膜と接続する第3の配線とを有することを特徴とする半 導体装置である。

### [0023]

また、上記構成において、前記第2絶縁膜を介して前記半導体膜と前記第2配線とが重なることを特徴としている。

## [0024]

また、上記各構成において、前記第 2 絶縁膜を介して前記第 2 配線と前記半導体膜とが重なる領域には、前記第 2 絶縁膜を誘電体とする保持容量が形成されることを特徴としている。

[0025]

また、上記各構成において、前記半導体膜のうち、前記第2絶縁膜を介して前記第2配線と重なる領域には、半導体に導電型(p型またはn型)を付与する不純物元素が添加されていることを特徴としている。

### [0026]

また、上記各構成において、前記第3絶縁膜上に前記半導体膜と接する電極と、該電極と接続する画素電極とを有することを特徴としている。

### [0027]

また、上記各構成において、前記第 1 配線は、前記第 2 配線とは直交する方向に配置されていることを特徴としている。

10

20

30

40

### [0028]

また、上記各構成において、前記第1配線は、前記第3配線と直交する方向に配置されていることを特徴としている。即ち、画素部において、前記第2配線と前記第3配線は平行な方向(Y方向)に配置され、これらの配線に直交する方向(X方向)に第1配線が配置されている。

## [0029]

また、上記各構成において、前記ゲート電極は、前記第1配線と異なる層に形成されていることを特徴としている。

## [0030]

また、上記各構成において、前記ゲート電極は、島状にパターニングされていることを 特徴としている。

### [0031]

また、上記各構成において、前記第1配線は、走査線である。この走査線は、前記第1 絶縁膜を介して前記半導体膜の一部と重なっており、半導体膜への光を遮る遮光膜の役目 を果たす。

## [0032]

また、上記各構成において、前記第2配線は、容量配線である。

#### [0033]

また、上記各構成において、前記第3配線は、信号線である。

## [0034]

また、上記各構成において、前記第2絶縁膜は、ゲート絶縁膜である。

#### [0035]

また、上記各構成において、前記ゲート電極は、導電型を付与する不純物元素がドープされたpoly-Si、W、WSix、Al、Ta、Cr、またはMoから選ばれた元素を主成分とする膜またはそれらの積層膜からなることを特徴としている。

## [0036]

また、他の発明の構成は、

信号線駆動回路に接続され互いに平行に所定の間隔を隔てて配置される複数の信号線と

走査線駆動回路に接続され互いに平行に所定の間隔を隔てて配置される複数の走査線と

前記信号線と平行に配置される容量配線とを有することを特徴とする半導体装置。

### **[** 0 0 2 7 **]**

また、上記構成において、前記走査線は、前記信号線と直交することを特徴としている

### [0038]

また、上記構成において、前記信号線と直交する走査線に接続されたゲート電極を有する薄膜トランジスタと、前記トランジスタと接続された画素電極とを有することを特徴としている。

## [0039]

また、上記各構成において、前記ゲート電極は、前記走査線と異なる層に形成されていることを特徴としている。

## [0040]

また、上記各構成において、前記ゲート電極は、島状にパターニングされていることを 特徴としている。

## [0041]

また、上記構造を実現するための発明の構成は、

絶縁表面を有する基板上に第1配線を形成する第1工程と、

前記第1配線上に第1絶縁膜を形成する第2工程と、

前記第1配線上に半導体膜を形成する第3工程と、

20

10

30

40

前記半導体膜上に第2絶縁膜を形成する第4工程と、

前記第1絶縁膜及び第2絶縁膜に選択的なエッチングを施して、前記第1配線に達する 第1コンタクトホールを形成する第5工程と、

前記第1コンタクトホールを通じて前記第1配線と接続し、且つ、前記第2絶縁膜上に前記半導体膜の一部と重なるゲート電極を形成する第6工程と、

前記ゲート電極上に第3絶縁膜を形成する第7工程と、

前記第2絶縁膜及び第3絶縁膜に選択的なエッチングを施して、前記半導体膜に達する第2コンタクトホールを形成する第8工程と、

前記第2コンタクトホールを通じて前記半導体膜と接続した第3配線を前記第3絶縁膜上に形成する第9工程と、を有することを特徴とする半導体装置の作製方法である。

[0042]

また、上記構成において、前記ゲート電極と同じ工程により前記半導体膜の一部と重なる第2配線を前記第2絶縁膜上に形成することを特徴としている。

[0043]

また、上記構成において、前記半導体膜上に第2絶縁膜を形成する工程の後、前記第2 配線と重なる前記第2絶縁膜を部分的に薄くする工程を有することを特徴としている。

[0044]

また、上記構成において、前記第2絶縁膜はゲート絶縁膜、前記第1配線は走査線、前記第2配線は容量配線、前記第3配線は信号線である。

【発明の効果】

[0045]

本発明により、従来では走査線内の配線領域及び走査線・容量配線分離領域として使われていた領域(図 1 9 中の A 領域に相当する)を保持容量として使うことができること、また各走査線に接続されている複数の画素が各々独立した容量配線を持つ構成になることにより各画素は隣接する画素と連続的、又は同時に信号書き込みが行われる場合にも隣接画素の書き込み電流の影響を受けず、さらに各容量配線は電流負荷が時間的に分散される事から実効負荷が低減、容量配線抵抗への要求が緩和される。

[0046]

従って、本発明を用いた液晶表示装置によれば、高い開口率と各画素内に十分な表示信号 電位を保持する保持容量を併せ持つ液晶表示素子が得られ、装置の小型化、省電力化を達 成しながら良好な表示画像を得る事ができる。

【図面の簡単な説明】

[0047]

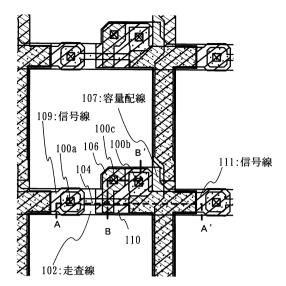

- 【図1】画素上面図を示す図。

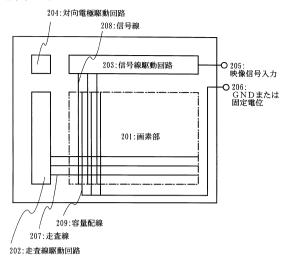

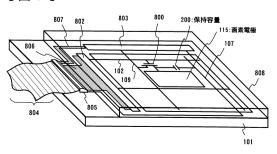

- 【図2】TFT基板の回路図を示す図。

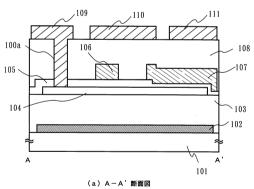

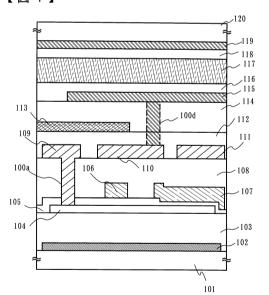

- 【図3】断面構造図を示す図。

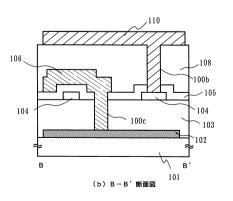

- 【図4】アクティブマトリクス型液晶表示装置の断面構造図を示す図。

- 【図5】AM-LCDの外観を示す図。

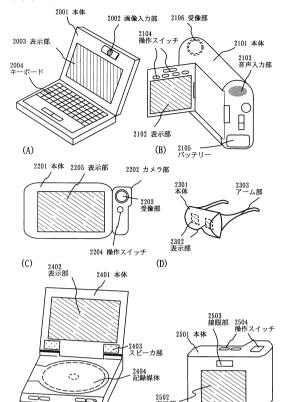

- 【図6】電子機器の一例を示す図。

- 【図7】電子機器の一例を示す図。

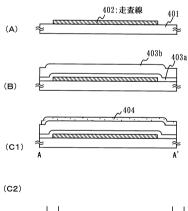

- 【図8】画素部の作製工程断面図および上面図。

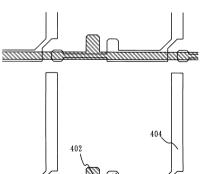

- 【図9】画素部の作製工程断面図および上面図。

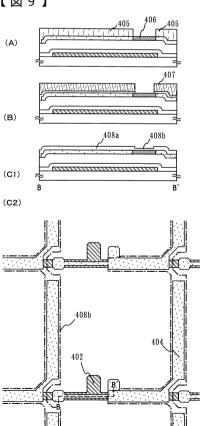

- 【図10】画素部の作製工程断面図および上面図。

- 【図11】画素部の作製工程断面図および上面図。

- 【図12】画素部の作製工程断面図および上面図。

- 【図13】TFT特性を示す図。

- 【図14】画素上面図を示す図。

- 【図15】断面構造図を示す図。

- 【図16】断面構造図を示す図。

- 【図17】画素上面図を示す図。

20

10

30

40

【図18】従来の画素上面図。

【図19】従来の画素開口領域を示す図。

【発明を実施するための形態】

### [0048]

本願発明の実施形態について、以下に説明する。

### [0049]

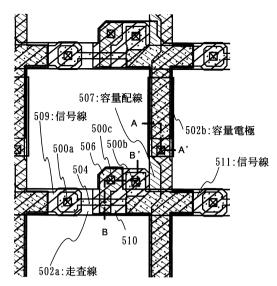

本発明は、開口率を向上させるとともに保持容量の増大を図るため、ゲート電極と異なる層に走査線を形成することを特徴としている。本発明の画素構成の一例を図1に示した

### [0050]

図1において、ゲート電極106は、島状にパターニングされており、絶縁膜に形成されたコンタクトホール100cを通じて走査線102と接続している。また、半導体膜104は、コンタクトホール100bを通じて信号線109と接続している。また、半導体膜104は、コンタクトホール100bを通じて電極110と接続している。また、信号線109または電極110と接する半導体膜の領域をソース領域あるいはドレイン領域と呼んでいる。また、ソース領域とドレイン領域との間にはチャネル形成領域が形成されており、チャネル形成領域上にはゲート絶縁膜を介してゲート電極106が存在している。なお、簡略化のため、ソース領域、ドレイン領域、及びチャネル形成領域は図示していない。

## [0051]

また、本発明において、図1に示したようにゲート電極106の下層に走査線102を 形成した場合、半導体膜104の下層に走査線102が設けられるので遮光膜として機能 させることも可能である。また、保持容量は、下部電極を半導体膜とし、半導体膜を覆う 絶縁膜を誘電体とし、上部電極を容量配線107として形成する。なお、半導体膜を覆う 絶縁膜を部分的に薄膜化することで保持容量の増大を図ってもよい。

## [0052]

また、本構成によれば、各画素のTFTは、チャネル形成領域の上方及び下方に絶縁膜を介してゲート電極を備えたデュアルゲート構造とすることができ、第1絶縁膜を適切な膜厚に設定することにより、走査線と他の配線とで形成される寄生容量を抑制しながらTFTの特性を向上することができる。

## [0053]

また、本発明は従来(容量配線が走査線と平行)と異なり、容量配線が信号線と平行になるよう配置されていることを特徴としている。従って、駆動方式から各走査線に対応する画素には連続的に映像信号の書き込みが行われるが、この際該当する各画素はそれぞれ独立した容量配線で形成された保持容量と接続されているため隣接画素の書き込み電流による容量配線電位の変動を回避でき、良好な表示画像を得る事ができる。

## [0054]

また、従来は各走査線書き込み期間中の信号線電位(書き込み電位)の低下を防ぐために各信号線にはサンプルホールド容量が設けられていたが、本発明においては容量配線が信号線と平行で、且つ重なるよう配置されているため、信号線の寄生容量が増大して信号線電位の保持特性が向上することから周辺回路部にサンプルホールド容量を設ける必要がなくなり、従来と比べ周辺回路を小型化することができる。

## [0055]

また、同じ理由により容量配線抵抗への要求性能が緩和されるため容量配線の配置やサイズ、膜厚の設計自由度が増し、また容量配線材料の選択の幅が広がることにより設計上の難度及び製造上の難度が下がり、より高い製造歩留まりを得ることにも繋がる。

### [0056]

以上の構成でなる本願発明について、以下に示す実施例でもってさらに詳細な説明を行うこととする。

## 【実施例1】

10

20

30

#### [0057]

以下、本発明の実施例を投写型の点順次駆動の液晶表示装置を一例にとり説明する。

### [0058]

TFTをスイッチング素子として用いるアクティブマトリクス型液晶表示装置は、画素電極がマトリクス状に配置された基板(TFT基板)と、対向電極が形成された対向基板とを液晶層を介して対向配置した構造となっている。両基板間はスペーサ等を介して所定の間隔に制御され、画素部の外周部にシール材を用いることで液晶層を封入している。

## [0059]

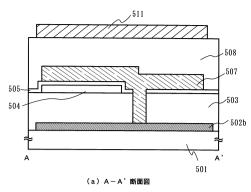

図4は、本実施例の液晶表示装置の概略を示す断面構造図である。図4において、101は基板(TFT基板)、102は走査線、103は第1絶縁膜、104は半導体膜、105はゲート絶縁膜(第2絶縁膜)、106はゲート電極、107は容量配線、108は第3絶縁膜、109及び111は信号線、または信号線から分岐された電極、110は第3絶縁膜に形成されたコンタクトホール(図示しない)を通じて半導体膜に接続され、TFTと画素電極とを接続するための電極である。

### [0060]

なお、本明細書中において「電極」とは、「配線」の一部であり、他の配線との電気的接続を行う箇所、または半導体層と交差する箇所を指す。従って、説明の便宜上、「配線」と「電極」とを使い分けるが、「電極」という文言に「配線」は常に含められているものとする。

## [0061]

なお、本明細書中では、TFTを、101~110で示した部分と定義している。また、109及び110においては、配線から分岐された電極であっても、配線であってもよい。

#### [0062]

また、112はTFTを覆う第4絶縁膜、113はTFTの光劣化を防ぐ遮光膜、11 4は第5絶縁膜、115は、コンタクトホール100dを通じて電極110と接続された 画素電極、116は液晶層117を配向させる配向膜である。

### [0063]

また、図4においては、対向基板120に、対向電極119と、配向膜118とを設けたが、必要に応じて遮光膜やカラーフィルタを設けてもよい。

### [0064]

この基板(TFT基板)101は、図2に示されるように画素部201と、その周辺に形成される走査線駆動回路202、信号線駆動回路203を備えている。

## [0065]

走査線駆動回路202は、走査信号を順次転送するシフトレジスタによって主に構成されている。また、信号線駆動回路203は、シフトレジスタとシフトレジスタ出力に基づいて入力される映像信号をサンプリングした後、保持し信号線を駆動するサンプルホールド回路により主に構成されている。

## [0066]

画素部 2 0 1 には走査線駆動回路 2 0 2 に接続され互いに平行に所定の間隔で配置された複数の走査線(ゲート配線) 2 0 7 と、信号線駆動回路 2 0 3 に接続され互いに平行に所定の間隔で配置された複数の信号線 2 0 8 とが交差して配置されており、その交差するそれぞれの位置にTFT(図示しない)を配置するとともに、走査線と信号線とで区画される各領域に画素電極(図示しない)が配置されている。この構成から各画素電極はマトリクス状の配置となる。また、GND(接地)または固定電位 2 0 6 に接続された複数の容量配線 2 0 9 が、信号線 2 0 8 と平行に設けられている。なお、図 2 においては、簡略化のため信号線、走査線、及び容量配線を数本しか図示していない。

### [0067]

以下、図4に示した半導体装置の作製工程を簡略に示す。なお、説明には図3及び図1 も用いる。 10

20

30

40

#### [0068]

まず、基板101にはガラス基板の他に、石英基板、プラスチック基板を用いることができる。ガラス基板を用いる場合には、ガラス歪み点よりも10~20 程度低い温度であらかじめ熱処理しておいても良い。また、基板101のTFTを形成する表面に、基板101からの不純物拡散を防ぐために、酸化シリコン膜、窒化シリコン膜または酸化窒化シリコン膜などの絶縁膜から成る下地膜を形成するとよい。

#### [0069]

次に、基板上に導電膜を形成し、パターニングを施すことにより走査線 102 を形成する。走査線 102 としては、導電型を付与する不純物元素がドープされた poly - Si や  $WSi_X(X=2.0~2.8)$ 、 Al、 Ta、 W、 Cr、 Mo 等の導電性材料及びその積層構造を用いることができる。本実施例では、  $WSi_X(膜厚:100nm)/poly - Si(膜厚:50nm)$ の積層構造の高い遮光性を持つ導電性材料により所定の間隔で走査線 102 を形成した。

## [0070]

次に、走査線102を覆って500nm程度の膜厚を有する第1絶縁膜103を形成する。この第1絶縁膜103は、プラズマCVD法、またはスパッタ法等で形成されるシリコンを含む絶縁膜を用いる。また、この第1絶縁膜は、有機絶縁物材料膜、酸化シリコン膜、酸化窒化シリコン膜、窒化シリコン膜、またはこれらを組み合わせた積層膜で形成すれば良い。

## [0071]

次いで、25~80nm(好ましくは30~60nm)の厚さの半導体膜をプラズマCVD法やスパッタ法等の公知の方法で形成し、所望の形状にパターニングする。本実施例では、プラズマCVD法で非晶質シリコン膜を50nm程度の厚さに成膜し、公知の方法により結晶化の工程を行って結晶質シリコン膜(poly-Si)を形成した後、島状にパターニングを施した。本実施例では、結晶質シリコン膜(poly-Si)を用いたが、半導体膜であれば特に限定されない。

### [0072]

なお、本明細書中において、「半導体膜」とは、単結晶半導体膜、結晶質半導体膜(poly y - Si等)、非晶質半導体膜(a - Si等)、または微結晶半導体膜を指しており、さらにシリコンゲルマニウム膜などの化合物半導体膜をも含められている。

### [0073]

次いで、プラズマCVD法、またはスパッタ法等で形成されるシリコンを含む絶縁膜、 又は半導体膜(Si膜等)の熱酸化で形成される酸化膜を用いて第2絶縁膜(ゲート絶縁膜)105を形成する。この第2絶縁膜105は、必要に応じて二層あるいは三層といった複数の層から成る積層構造としても良い。

## [0074]

次いで、各島状の半導体膜を用いて映像信号書き込みスイッチの機能を得るTFTを構成するため、半導体膜に選択的にn型またはp型を付与する不純物元素(リンまたはボロン等)を公知の技術を用いて添加し、低抵抗のソース領域及びドレイン領域と、さらに低抵抗領域を形成する。この低抵抗領域はドレイン領域と同様に不純物元素(代表的にはリンまたはボロン)を添加して低抵抗化されている半導体膜の一部である。なお、選択的に不純物元素を添加する工程順序は特に限定されず、例えば、第1絶縁膜形成前、ゲート電極形成前、またはゲート電極形成後であればよい。加えて、LDD領域やオフセット領域を回路に応じて形成する構成としてもよい。なお、簡略化のために、各領域の図示は行っていない。

## [0075]

こうして、半導体膜104にソース領域とドレイン領域とに挟まれたチャネル形成領域が形成される。

## [0076]

次いで、第1絶縁膜103及び第2絶縁膜105に選択的なエッチングを施して走査線

20

10

30

40

102に達する第1コンタクトホール100c(図3(b)中に示した)を形成する。

## [0077]

次いで、第 2 絶縁膜 1 0 5 上に導電膜を形成し、パターニングを施すことによりゲート電極 1 0 6 及び容量配線 1 0 7 を形成する。ゲート電極 1 0 6 及び容量配線 1 0 7 は、導電型を付与する不純物元素がドープされた p o 1 y - S i やW S i  $_x$  ( X = 2 . 0 ~ 2 . 8 )、 A 1、 T a、 W、 C r、 M o 等の導電性材料及びその積層構造により 3 0 0 n m程度の膜厚で形成する。また、ゲート電極 1 0 6 及び容量配線 1 0 7 は単層で形成しても良いが、必要に応じて二層あるいは三層といった複数の層から成る積層構造としても良い。この際、島状に配置される各ゲート電極は第 1 絶縁膜 1 0 3 及び第 2 絶縁膜 1 0 5 に形成された第 1 コンタクトホール 1 0 0 c を介して走査線 1 0 2 に電気的に接続する。

[0078]

また、各画素のチャネル形成領域上には第2絶縁膜105を介して島状のゲート電極106が配置される。また、低抵抗領域上には第2絶縁膜105を介して容量配線107が配置される。なお、容量配線107と重なる第2絶縁膜105の領域を部分的に薄膜化する工程を加えて保持容量の増大を図ってもよい。また、容量配線107は信号線方向に各画素連続的に配置し、画素部外で電気的に接地、または固定電位に接続する。

[0079]

次いで、ゲート電極 1 0 6 及び容量配線 1 0 7 を覆う第 3 絶縁膜 1 0 8 を形成する。この第 3 絶縁膜 1 0 8 は、プラズマ C V D 法、またはスパッタ法等で形成されるシリコンを含む絶縁膜を用いる。また、この第 3 絶縁膜 1 0 8 は、酸化シリコン膜、酸化窒化シリコン膜、窒化シリコン膜、またはこれらを組み合わせた積層膜で形成すれば良い。

[0800]

次いで、第2絶縁膜105及び第3絶縁膜108に選択的なエッチングを施して半導体膜(ソース領域、またはドレイン領域)に達する第2コンタクトホール100a(図3( a)中)、100b(図3(b)中)を形成する。

[0081]

次いで、第3絶縁膜108上にA1、W、Ti、TiNを主成分とする膜、またはそれらの積層構造を有する導電膜(膜厚:500 $\mu$ m)を形成し、パターニングを施すことにより信号線109、111と、後に形成される画素電極と接続するための島状の電極110を形成する。この信号線109、111は、半導体膜に達する第2コンタクトホール100a、100bを通じてソース領域あるいはドレイン領域と接続する。同様に島状の電極110は、半導体膜に達する第2コンタクトホール100aを通じてソース領域あるいはドレイン領域と接続する。また、信号線109、111は容量線107と平行な方向に配置する。

[0082]

また、島状の電極110は、信号線109と隔離して配置される。ただし、信号線10 9と島状の電極110とが両方、ソース領域に接続されることはない。同様に、信号線1 09と島状の電極110とが両方、ドレイン領域に接続されることはない。

[0083]

この段階での画素上面図が図1に相当し、図1中のA-A'点線に沿って切断した概略断面構造図が図3(a)に相当し、B-B'点線に沿って切断した概略断面構造図が図3(b)に相当する。

[0084]

次いで、信号線109及び島状の電極110を覆う第4絶縁膜112を形成する。この第4絶縁膜112は、有機絶縁物材料膜、酸化シリコン膜、酸化窒化シリコン膜、窒化シリコン膜、またはこれらを組み合わせた積層膜で形成すれば良い。

[0085]

次いで、第4絶縁膜112上にTi、Al、W、Cr、または黒色樹脂等の高い遮光性を持つ膜を所望の形状にパターニングして遮光膜113を形成する。この遮光膜113は画素の開口部以外を遮光するように網目状に配置する。

10

20

30

40

#### [0086]

本実施例において、遮光膜 1 1 3 は電気的にフローティングとなるが遮光膜材料に低抵抗膜を選んだ場合、表示部の外側で遮光膜を任意の電位に制御する事も可能である。

### [0087]

次いで、遮光膜113上に第5絶縁膜114を形成する。この第5絶縁膜114は、有機 絶縁物材料膜で形成すれば良い。なお、第5絶縁膜114を有機絶縁物材料で形成するこ とにより、表面を良好に平坦化させることができる。また、有機樹脂材料は一般に誘電率 が低いので、寄生容量を低減するできる。しかし、吸湿性があり保護膜としては適さない ので、酸化シリコン膜、酸化窒化シリコン膜、窒化シリコン膜などと組み合わせた積層構 造としても良い。

[0088]

次いで、第4絶縁膜112及び第5絶縁膜114に選択的なエッチングを行ない、島状の電極に達する第3コンタクトホール100dを形成する。図4では便宜上、第3コンタクトホール100dを点線で図示した。

## [0089]

次いで、ITO等の透明導電体膜を形成し、パターニングを施すことにより画素電極115を形成する。画素電極115は、第3コンタクトホール100dを通じて島状の電極110と接続する。各画素電極はそれぞれ独立に且つ画素開口部を覆うように配置される

[0090]

こうして形成したTFT基板に液晶層117を配向させる配向膜116を形成し、公知のセル組み技術を用いて、対向電極119と配向膜118とが設けられた対向基板120と貼り合わせた後、液晶材料を注入、封止して両基板間に液晶層が保持された液晶セルを完成させた。

## [0091]

以上のような作製工程を用い、さらに表 2 のデザインルールに従って配線及び半導体膜等を配置することによって、 2 3 6 . 9  $\mu$  m<sup>2</sup>の画素開口領域の面積(開口率 6 4 . 3 %) と保持容量領域の面積 6 2 . 8  $\mu$  m<sup>2</sup>が得られた。

## 【表2】

Si層:min. Size=0. 8 μm, min. Spacing=1. 5 μm ゲート電極:min. Size=1. 0 μm, min. Spacing=1. 5 μm 走査線とゲート電極とのコンタクトホール:min. Size=1 μm□ コンタクトホールとゲート電極とのmargin=1. 0 μ m

走査線:min. Size=1. 5 μm, min. Spacing=1. 5 μm 信号線とSi層とのコンタクトホール:min. Size=1 μm□ コンタクトホールとSi層とのmargin=1. 0 μm コンタクトホールと走査線(ゲート電極)との間隔min. Spacing=1. 3 μm

信号線:min. Size=1.5  $\mu$  m, min. Spacing=1.5  $\mu$  m コンタクトホールと信号線とのmargin=1.3  $\mu$  m

画素サイズ:19. 2μm□

画素TFT:L=1.5 $\mu$ m、W=0.8 $\mu$ m、シングルゲート

走査線:配線幅min. Size=1. 0μm

走査線:Si層乗り越え部における配線幅min. Size=1.5μm

|容量配線∶min. Size=2. 0μm

## [0092]

本実施例では、画素領域に新たにゲート電極106と走査線102とを接続するコンタクトホール100cのための領域を設ける必要がある。また、本実施例では島状Si膜のチャネル形成領域周辺部を遮光する膜は上部遮光膜のみとなるため、上部遮光膜を備えた

10

20

30

40

構造とすることが望ましい。

## [0093]

また、本構成によれば走査線102がチャネル形成領域及びその周辺部に対する下部遮光膜として機能するため液晶層117から入射した光がTFT基板の下部界面で反射し、チャネル形成領域及びその周辺部に入射してTFTの光リークを発生することを防ぐことができ、より良好な表示品質を得る事が可能である。

### 【実施例2】

## [0094]

本実施例では、実施例1に示したアクティブマトリクス型液晶表示装置の構成を図5の斜視図を用いて説明する。なお、実施例1と対応する部分は、同じ符号を用いている。

### [0095]

図5においてアクティブマトリクス基板は、基板101上に形成された、画素部と、走査線駆動回路802と、信号線駆動回路803とその他の信号処理回路とで構成される。画素部には画素TFT800と保持容量200が設けられ、画素部の周辺に設けられる駆動回路はCMOS回路を基本として構成されている。

## [0096]

また、容量配線107は信号線109と平行な方向に設けられ、保持容量200の上部電極として機能している。また、容量配線107は接地または固定電位に接続する。

#### [0097]

走査線駆動回路 8 0 2 と信号線駆動回路 8 0 3 からは、それぞれ走査線 1 0 2 と信号線 1 0 9 が画素部に延在し、画素 T F T 8 0 0 に接続している。また、フレキシブルプリント配線板 (Flexible Printed Circuit: F P C ) 8 0 4 が外部入力端子 8 0 5 に接続していて画像信号などを入力するのに用いる。 F P C 8 0 4 は補強樹脂によって強固に接着されている。そして接続配線 8 0 6 、 8 0 7 でそれぞれの駆動回路に接続している。また、対向基板 8 0 8 には図示していないが、遮光膜や透明電極が設けられている。

## 【実施例3】

## [0098]

本願発明を実施して形成された画素マトリクス回路は様々な電気光学装置(アクティブマトリクス型液晶ディスプレイ、アクティブマトリクス型 ELディスプレイ、アクティブマトリクス型 ECディスプレイ)に用いることができる。即ち、それら電気光学装置を表示部として組み込んだ電子機器全てに本願発明を実施できる。

## [0099]

その様な電子機器としては、ビデオカメラ、デジタルカメラ、プロジェクター(リア型またはフロント型)、ヘッドマウントディスプレイ(ゴーグル型ディスプレイ)、カーナビゲーション、パーソナルコンピュータ、携帯情報端末(モバイルコンピュータ、携帯電話または電子書籍等)などが挙げられる。それらの一例を図6及び図7に示す。

## [0100]

図 6 ( A ) はパーソナルコンピュータであり、本体 2 0 0 1、画像入力部 2 0 0 2、表示部 2 0 0 3、キーボード 2 0 0 4で構成される。本願発明を表示部 2 0 0 3 に適用することができる。

## [0101]

図6(B)はビデオカメラであり、本体2101、表示部2102、音声入力部210 3、操作スイッチ2104、バッテリー2105、受像部2106で構成される。本願発明を表示部2102に適用することができる。

## [0102]

図6(C)はモバイルコンピュータ(モービルコンピュータ)であり、本体2201、カメラ部2202、受像部2203、操作スイッチ2204、表示装置2205で構成される。本願発明は表示部2205に適用できる。

## [0103]

図6(D)はゴーグル型ディスプレイであり、本体2301、表示部2302、アーム

20

10

30

40

部2303で構成される。本発明は表示部2302に適用することができる。

#### [0104]

図6(E)はプログラムを記録した記録媒体(以下、記録媒体と呼ぶ)を用いるプレーヤーであり、本体2401、表示部2402、スピーカ部2403、記録媒体2404、操作スイッチ2405で構成される。なお、この装置は記録媒体としてDVD(Digtial Versatile Disc)、CD等を用い、音楽鑑賞や映画鑑賞やゲームやインターネットを行うことができる。本発明は表示部2402に適用することができる

## [0105]

図 6 (F)はデジタルカメラであり、本体 2 5 0 1、表示部 2 5 0 2、接眼部 2 5 0 3、操作スイッチ 2 5 0 4、受像部(図示しない)で構成される。本願発明を表示部 2 5 0 2 に適用することができる。

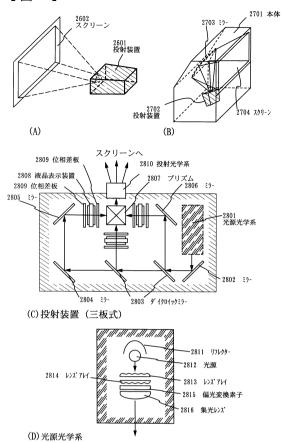

#### [0106]

図7(A)はフロント型プロジェクターであり、投射装置2601、スクリーン2602等を含む。本発明は投射装置2601の一部を構成する液晶表示装置2808に適用することができる。

## [0107]

図7 (B)はリア型プロジェクターであり、本体2701、投射装置2702、ミラー2703、スクリーン2704等を含む。本発明は投射装置2702の一部を構成する液晶表示装置2808に適用することができる。

#### [0108]

なお、図7(C)は、図7(A)及び図7(B)中における投射装置2601、2702の構造の一例を示した図である。投射装置2601、2702は、光源光学系2801、ミラー2802、2804~2806、ダイクロイックミラー2803、プリズム2807、液晶表示装置2808、位相差板2809、投射光学系2810で構成される。投射光学系2810は、投射レンズを含む光学系で構成される。本実施例は三板式の例を示したが、特に限定されず、例えば単板式であってもよい。また、図7(C)中において矢印で示した光路に実施者が適宜、光学レンズや、偏光機能を有するフィルムや、位相差を調節するためのフィルム、IRフィルム等の光学系を設けてもよい。

## [0109]

また、図7(D)は、図7(C)中における光源光学系2801の構造の一例を示した図である。本実施例では、光源光学系2801は、リフレクター2811、光源2812、レンズアレイ2813、2814、偏光変換素子2815、集光レンズ2816で構成される。なお、図7(D)に示した光源光学系は一例であって特に限定されない。例えば、光源光学系に実施者が適宜、光学レンズや、偏光機能を有するフィルムや、位相差を調節するフィルム、IRフィルム等の光学系を設けてもよい。

## [0110]

以上の様に、本願発明の適用範囲は極めて広く、あらゆる分野の電子機器に適用することが可能である。また、本実施例の電子機器は実施例1または実施例2のどのような組み合わせからなる構成を用いても実現することができる。

## 【実施例4】

### [0111]

実施例1はシングルゲートのTFTの例を示したが本実施例ではダブルゲートのTFTを用いた例を示す。ただし、基本的な構造は同一である。

### [0112]

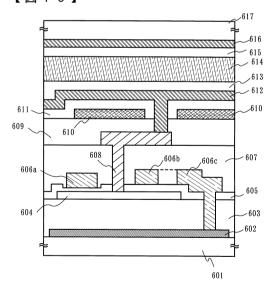

まず、絶縁表面を有する基板 4 0 1 上に導電膜を形成し、パターニングを施すことにより走査線 4 0 2 を形成する。(図 8 ( A ) ) この走査線 4 0 2 は後に形成される活性層を光から保護する遮光層としても機能する。ここでは基板 4 0 1 として石英基板を用い、走査線 4 0 2 としてポリシリコン膜(膜厚 5 0 n m ) とタングステンシリサイド(W - S i ) 膜(膜厚 1 0 0 n m ) の積層構造を用いた。また、ポリシリコン膜はタングステンシリ

10

20

30

40

サイドから基板への汚染を保護するものである。

#### [0113]

次いで、走査線402を覆う絶縁膜403a、403bを膜厚100~1000nm(代表的には300~500nm)で形成する。(図8(B))ここではCVD法を用いた膜厚100nmの酸化シリコン膜とLPCVD法を用いた膜厚280nmの酸化シリコン膜を積層させた。

#### [0114]

次いで、非晶質半導体膜を膜厚10~100mmで形成する。ここでは膜厚69mmの非晶質シリコン膜(アモルファスシリコン膜)をLPCVD法を用いて形成した。次いで、この非晶質半導体膜を結晶化させる技術として特開平8-78329号公報記載の技術を用いて結晶化させた。同公報記載の技術は、非晶質シリコン膜に対して結晶化を助長する金属元素を選択的に添加し、加熱処理を行うことで添加領域を起点として広がる結晶質シリコン膜を形成するものである。ここでは結晶化を助長する金属元素としてニッケルを用い、脱水素化のための熱処理(450 、1時間)の後、結晶化のための熱処理(600 、12時間)を行った。

#### [0115]

次いで、TFTの活性層とする領域からNiをゲッタリングする。TFTの活性層とする領域をマスク(酸化シリコン膜)で覆い、結晶質シリコン膜の一部に燐(P)を添加し、熱処理(窒素雰囲気下で600 、12時間)を行った。

## [0116]

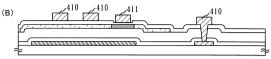

次いで、マスクを除去した後、パターニングを行い結晶質シリコン膜の不要な部分を除去して、半導体層 4 0 4 を形成する。(図 8 ( C 1 ) ) なお、半導体層 4 0 4 を形成した後の画素上面図を図 8 ( C 2 ) に示す。図 8 ( C 2 ) において、点線 A - A ' で切断した断面図が図 8 ( C 1 ) に相当する。

#### [0117]

次いで、保持容量を形成するため、マスク405を形成して半導体層の一部(保持容量とする領域)406にリンをドーピングする。(図9(A))

### [0118]

次いで、マスク405を除去し、半導体層を覆う絶縁膜を形成した後、マスク407を 形成して保持容量とする領域406上の絶縁膜を除去する。(図9(B))

### [0119]

次いで、マスク407を除去し、熱酸化を行って絶縁膜(ゲート絶縁膜)408aを形成する。この熱酸化によって最終的なゲート絶縁膜の膜厚は80nmとなった。なお、保持容量とする領域上に他の領域より薄い絶縁膜408bを形成した。(図9(C1))ここでの画素上面図を図9(C2)に示す。図9(C2)において、点線B-B'で切断した断面図が図9(C1)に相当する。また、図9中の鎖線内で示した領域は、薄い絶縁膜408bが形成されている部分である。

## [0120]

次いで、TFTのチャネル領域となる領域にp型またはn型の不純物元素を低濃度に添加するチャネルドープ工程を全面または選択的に行った。このチャネルドープ工程は、TFTしきい値電圧を制御するための工程である。なお、ここではジボラン(B₂H6)を質量分離しないでプラズマ励起したイオンドープ法でボロンを添加した。もちろん、質量分離を行うイオンインプランテーション法を用いてもよい。

## [0121]

次いで、絶縁膜408a、及び絶縁膜403a、403b上にマスク409を形成し、 走査線402に達するコンタクトホールを形成する。(図10(A))そして、コンタクトホールの形成後、マスクを除去する。

### [0122]

次いで、導電膜を形成し、パターニングを行ってゲート電極 4 1 0 および容量配線 4 1 1 を形成する。(図 1 0 ( B ) ) ここでは、リンがドープされたシリコン膜(膜厚 1 5 0

10

20

30

40

nm)とタングステンシリサイド(膜厚150nm)との積層構造を用いた。なお、保持容量は、絶縁膜408bを誘電体とし、容量配線411と半導体層の一部406とで構成されている。

## [0123]

次いで、ゲート電極 4 1 0 および容量配線 4 1 1 をマスクとして自己整合的にリンを低濃度に添加する。(図 1 0 ( C 1 ) ) ここでの画素上面図を図 1 0 ( C 2 ) に示す。図 1 0 ( C 2 ) において、点線 C - C 'で切断した断面図が図 1 0 ( C 1 ) に相当する。この低濃度に添加された領域のリンの濃度が、 1 × 1 0  $^{16}$  ~ 5 × 1 0  $^{18}$  a t o m s / c m  $^3$  、代表的には 3 × 1 0  $^{17}$  ~ 3 × 1 0  $^{18}$  a t o m s / c m  $^3$  となるように調整する。

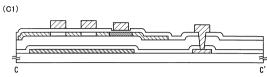

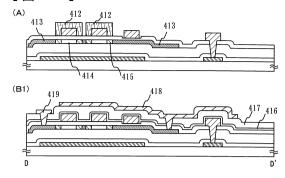

## [0124]

次いで、マスク412を形成してリンを高濃度に添加し、ソース領域またはドレイン領域となる高濃度不純物領域413を形成する。(図11(A))この高濃度不純物領域のリンの濃度が1×10 $^{20}$ ~1×10 $^{21}$ atoms/cm $^{3}$ (代表的には2×10 $^{20}$ ~5×10 $^{20}$ atoms/cm $^{3}$ )となるように調整する。なお、半導体層404のうち、ゲート電極410と重なる領域はチャネル形成領域414となり、マスク412で覆われた領域は低濃度不純物領域415となりLDD領域として機能する。そして、不純物元素の添加後、マスク412を除去する。

## [0125]

次いで、ここでは図示しないが、画素と同一基板上に形成される駆動回路に用いるpチャネル型TFTを形成するために、マスクでnチャネル型TFTとなる領域を覆い、ボロンを添加してソース領域またはドレイン領域を形成する。

#### [0126]

次いで、マスク412を除去した後、ゲート電極410および容量配線411を覆うパッシベーション膜416を形成する。ここでは、酸化シリコン膜を70nmの膜厚で形成した。次いで、半導体層にそれぞれの濃度で添加されたn型またはp型不純物元素を活性化するための熱処理工程を行う。ここでは850 、30分の加熱処理を行った。

### [ 0 1 2 7 ]

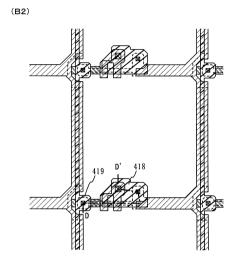

次いで、有機樹脂材料からなる層間絶縁膜417を形成する。ここでは膜厚400nmのアクリル樹脂膜を用いた。次いで、半導体層に達するコンタクトホールを形成した後、電極418及びソース配線419を形成する。本実施例では電極418及びソース配線419を、Ti膜を100nm、Tiを含むアルミニウム膜を300nm、Ti膜150nmをスパッタ法で連続して形成した3層構造の積層膜とした。(図11(B1))なお、図11(B2)において点線D-D,で切断した断面図が図11(B1)に相当する。

## [0128]

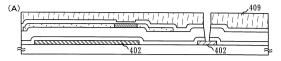

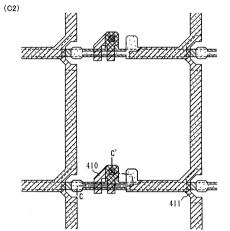

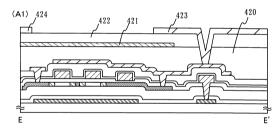

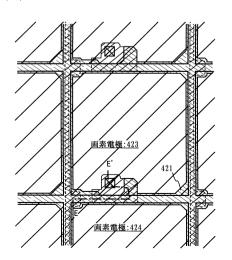

次いで、水素化処理をおこなった後、アクリルからなる層間絶縁膜420を形成する。(図12(A1))次いで、層間絶縁膜420上に遮光性を有する導電膜100nmを成膜し、遮光層421を形成する。次いで、層間絶縁膜422を形成する。次いで、電極418に達するコンタクトホール形成する。次いで、100nmの透明導電膜(ここでは酸化インジウム・スズ(ITO)膜)を形成した後、パターニングして画素電極423、424を形成する。図12(A2)において、点線E-E<sup>\*</sup>で切断した断面図が図12(A1)に相当する。

## [0129]

こうして画素部には、表示領域(画素サイズ 2 6  $\mu$  m × 2 6  $\mu$  m ) の面積(開口率 7 6 . 5 % ) を確保しつつ、 n チャネル型 T F T でなる画素 T F T が形成され、十分な保持容量 (5 1 . 5 f F ) を得ることができる。

## [0130]

なお、本実施例は一例であって本実施例の工程に限定されないことはいうまでもない。例えば、各導電膜としては、タンタル(Ta)、チタン(Ti)、モリブデン(Mo)、タングステン(W)、クロム(Cr)、シリコン(Si)から選ばれた元素、または前記元素を組み合わせた合金膜(代表的には、Mo W合金、Mo Ta合金)を用いること

10

20

30

40

ができる。また、各絶縁膜としては、酸化シリコン膜や窒化シリコン膜や酸化窒化シリコン膜や有機樹脂材料(ポリイミド、アクリル、ポリアミド、ポリイミドアミド、BCB(ベンゾシクロブテン)等)膜を用いることができる。

### [0131]

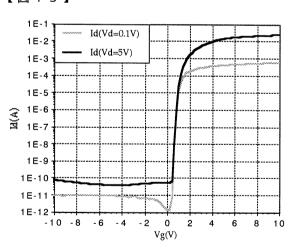

また、こうして得られたTFTの特性は、良好な値を示した。図13にそのTFT特性(V-I特性)を示す。特に本発明の構造はデュアルゲート構造となっているため、S値は105.8(m V / d e c )と優れた値を示している。また、本発明の構造とすることによって、V-I特性グラフにおける立ち上がり点での電圧値を示すしきい値(Vth)は、Vd = 0.1Vである場合に0.946V、Vd = 5 Vである場合に0.886Vとなっており、その差は0.06と非常に小さい。この差が小さければ小さいほど短チャネル効果が抑えられていると言える。また、移動度( $\mu_{FE}$ )は220( $cm^2$ / Vs)と優れたものとなっている。

## 【実施例5】

## [0132]

本実施例は、開口率を向上させるとともに保持容量の増大を図るため、ゲート電極と異なる層に走査線502aを形成し、さらに走査線502aと同じ層に容量電極502bを 形成することを特徴としている。本発明の画素構成の一例を図14、図15に示した。

## [0133]

なお、図14中のA-A′点線に沿って切断した概略断面構造図が図15(a)に相当し、B-B′点線に沿って切断した概略断面構造図が図15(b)に相当する。

### [0134]

図14において、ゲート電極506は、島状にパターニングされており、絶縁膜に形成されたコンタクトホール500cを通じて走査線502aと接続している。また、半導体膜504は、コンタクトホール500bを通じて電極510と接続している。また、半導体膜504は、コンタクトホール500bを通じて電極510と接続している。また、半導体膜509または電極510と接する半導体膜の領域をソース領域あるいはドレイン領域と呼んでいる。また、ソース領域とドレイン領域との間にはチャネル形成領域が形成されており、チャネル形成領域上にはゲート絶縁膜を介してゲート電極506が存在している。なお、簡略化のため、ソース領域、ドレイン領域、及びチャネル形成領域は図示していない。

## [0135]

また、本実施例において、図14に示したようにゲート電極506の下層に走査線502aを形成した場合、半導体膜504の下層に走査線502aが設けられるので遮光膜として機能させることも可能である。また、保持容量は、下部電極を半導体膜とし、半導体膜を覆う絶縁膜を誘電体とし、上部電極を容量配線507として形成する。なお、半導体膜を覆う絶縁膜を部分的に薄膜化することで保持容量の増大を図ってもよい。

## [0136]

さらに、本実施例の保持容量は、図15に示したように、容量配線507に接続している容量電極502bも、絶縁膜503を誘電体として保持容量を形成することができる。そのため、保持容量を効率よく確保することができ、この画素構造を用いた液晶表示装置のコントラストが向上する。

### [0137]

また、本実施例の構成によれば、各画素のTFTは、チャネル形成領域の上方及び下方に絶縁膜を介してゲート電極を備えたデュアルゲート構造とすることができ、第1絶縁膜を適切な膜厚に設定することにより、走査線と他の配線とで形成される寄生容量を抑制しながらTFTの特性を向上することができる。

### [0138]

また、本実施例で示した画素構造の作製方法は、実施例1または実施例4とほぼ同一であり、ここではその説明を省略する。

## [0139]

50

10

20

30

なお、本実施例は実施例1乃至4のいずれか一と自由に組み合わせることができる。

## 【実施例6】

### [0140]

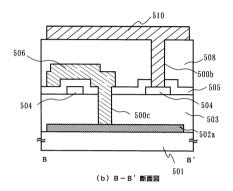

本実施例は、画素サイズを縮小した際、開口率を向上させるとともに保持容量の増大を図る。本実施例は、遮光膜と画素電極とで保持容量を形成することを特徴としている。

## [0141]

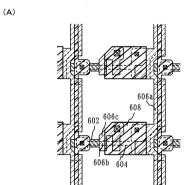

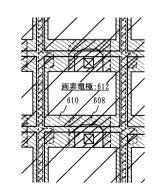

図16は、本実施例の液晶表示装置の概略を示す断面構造図である。図16において、601は基板(TFT基板)、602は走査線、603は第1絶縁膜、604は半導体膜、605はゲート絶縁膜(第2絶縁膜)、606bはゲート電極、606cはゲート配線、606aは容量配線、607は第3絶縁膜、608は第3絶縁膜に形成されたコンタクトホールを通じて半導体膜604に接続され、TFTと画素電極612とを接続するための電極である。

### [0142]

また、609はTFTを覆う第4絶縁膜、610はTFTの光劣化を防ぐ遮光膜、61 1は第5絶縁膜、612は、コンタクトホールを通じて電極608と接続された画素電極、613は液晶層614を配向させる配向膜である。

## [0143]

また、図16においては、対向基板617に、対向電極616と、配向膜615とを設けたが、必要に応じて遮光膜やカラーフィルタを設けてもよい。

## [0144]

図16に示すように、本実施例の保持容量は、絶縁膜605を誘電体とし、容量配線606aと半導体膜604とで形成した第1の保持容量と、さらに絶縁膜611を誘電体とし、遮光膜610と画素電極612とで形成した第2の保持容量とで構成される。なお、絶縁膜611としては有機樹脂膜を用いてもよいし、酸化窒化シリコン膜や酸化シリコン膜等の無機絶縁膜を用いてもよく、その膜厚は実施者が適宜設計すればよい。

## [0145]

例えば、画素サイズを14 $\mu$  m × 1 4  $\mu$  m とした場合においても、図16に示す断面構造とし、図17(B)に示すような上面図に設計することで十分な保持容量(100fF程度)を確保することができ、かつ開口率を48.7%とすることができた。

## [0146]

なお、図17(A)は、電極608を形成した段階での上面図であり、図17(B)は、さらに遮光膜610と画素電極612とを形成した段階での上面図であり、図16に対応する箇所には同じ符号を用いた。

## [0147]

なお、本実施例は実施例1乃至5のいずれか一と自由に組み合わせることができる。

10

20

【図1】

【図2】

【図3】

【図4】

【図5】

## 【図6】

2405 操作スイッチ

(F)

## 【図7】

## 【図8】

(E)

## 【図9】

# 【図10】

# 【図11】

# 【図12】

(A2)

# 【図13】

【図14】

【図15】

【図16】

【図17】

(B)

【図18】

【図19】

## フロントページの続き

(51) Int.CI. F I

H 0 1 L 29/78 6 1 7 K

(56)参考文献 特開平09-281465(JP,A)

特開平01-274117(JP,A)

特開2000-284723(JP,A)

独国特許出願公開第03015936(DE,A1)

特開平4-217230(JP,A)

(58)調査した分野(Int.CI., DB名)

G02F 1/1368

G02F 1/1343

G 0 3 B 2 1 / 0 0

G09F 9/30

H01L 29/786