### (19) **日本国特許庁(JP)**

# (12) 特許 公報(B2)

(11)特許番号

特許第5783186号 (P5783186)

(45) 発行日 平成27年9月24日(2015.9.24)

(24) 登録日 平成27年7月31日 (2015.7.31)

京都府長岡京市東神足1丁月10番1号

株式会社村田製作所内

| (51) Int.Cl. | FΙ                            |                     |

|--------------|-------------------------------|---------------------|

| HO1L 23/12   | (2006.01) HO1L                | 23/12 B             |

| HO1F 17/00   | <b>(2006.01)</b> HO1F         | 17/00 A             |

| HO5K 3/46    | <b>(2006.01)</b> HO5K         | 3/46 N              |

|              | но 5 К                        | 3/46 Z              |

|              | НО5К                          | 3/46 Q              |

|              |                               | 請求項の数 6 (全 20 頁)    |

| (21) 出願番号    | 特願2013-7997 (P2013-7997)      | (73) 特許権者 000006231 |

| (22) 出願日     | 平成25年1月21日 (2013.1.21)        | 株式会社村田製作所           |

| (65) 公開番号    | 特開2014-139962 (P2014-139962A) | 京都府長岡京市東神足1丁目10番1号  |

| (43) 公開日     | 平成26年7月31日 (2014.7.31)        | (74) 代理人 110000970  |

| 審査請求日        | 平成26年7月22日 (2014.7.22)        | 特許業務法人 楓国際特許事務所     |

|              |                               | (72) 発明者 小暮 武       |

|              |                               | 京都府長岡京市東神足1丁目10番1号  |

|              |                               | 株式会社村田製作所内          |

審査官 小山 和俊

(72) 発明者 北嶋 宏通

最終頁に続く

(54) 【発明の名称】積層基板モジュール

### (57)【特許請求の範囲】

# 【請求項1】

導体パターンが形成された複数の層を積層した積層回路基板と、

前記積層回路基板の一方主面に形成された第1外部接続用端子と、

前記積層回路基板の他方主面に形成された第2外部接続用端子と、を備え、

前記積層回路基板の内部には、前記第1外部接続用端子と前記第2外部接続用端子とを結ぶ配線と、前記配線の一部を構成するインダクタと、前記インダクタより前記一方主面側に位置する第1グランド導体と、前記インダクタより前記他方主面側に位置する第2グランド導体と、が前記導体パターンにより形成されており、

<u>前記インダクタの一部は第1インダクタを構成し、前記インダクタの残りの部分は第2</u>インダクタを構成し、

前記第1インダクタは、前記積層回路基板の前記一方主面または前記他方主面を正面視したとき、前記第2インダクタと異なる箇所に形成され、

前記<u>第1</u>インダクタの形成箇所は、前記積層回路基板の前記一方主面または前記他方主面を正面視したとき、前記第1、第2グランド導体の内、前記<u>第1</u>インダクタが形成されている層に近い方の前記第1グランド導体の形成箇所と異なり、

前記第2インダクタの形成箇所は、前記積層回路基板の前記一方主面または前記他方主面を正面視したとき、前記第1、第2グランド導体の内、前記第2インダクタが形成されている層に近い方の前記第2グランド導体の形成箇所と異なる、積層基板モジュール。

【請求項2】

20

前記インダクタの形成箇所は、前記積層回路基板の前記一方主面または前記他方主面を 正面視したとき、前記第1外部接続用端子および前記第2外部接続用端子の少なくとも一 方の形成箇所と重なる、請求項1に記載の積層基板モジュール。

### 【請求項3】

前記グランド導体は、その形成箇所が、前記積層回路基板の前記一方主面または前記他方主面を正面視したときに前記インダクタの形成箇所と異なるように開口している、請求項1又は2に記載の積層基板モジュール。

## 【請求項4】

前記インダクタの形成箇所は、前記積層回路基板の前記一方主面または前記他方主面を 正面視したとき、前記第1、第2グランド導体の両方の形成箇所と異なる、請求項1から 3のいずれか1項に記載の積層基板モジュール。

# 6

10

# 【請求項5】

前記インダクタは、前記第1外部接続用端子と直列に接続されている、請求項1から<u>4</u>のいずれか1項に記載の積層基板モジュール。

## 【請求項6】

前記インダクタは、前記配線を前記第 1 グランド導体または前記第 2 グランド導体に接続する、請求項 1 から 4 のいずれか 1 項に記載の積層基板モジュール。

【発明の詳細な説明】

#### 【技術分野】

#### [00001]

20

本発明は、携帯電話などの通信機器に実装される積層基板モジュールに関するものである。

### 【背景技術】

#### [00002]

従来より、携帯電話などの通信機器に実装される積層基板モジュールが各種知られている。従来の積層基板モジュールは、導体パターンが形成された複数の層を積層した積層回路基板と、積層回路基板の一方主面に形成された実装用ランドと、積層回路基板の他方主面に形成された入出力端子と、を備える。この積層回路基板の内部には、実装用ランドと入出力端子とを結ぶ配線と、グランド導体と、が導体パターンにより形成されている。

#### [0003]

30

近年、積層基板モジュールは、積層回路基板の低背化に伴い、入出力端子に接続される配線とグランド導体との間隔が狭くなる傾向にある。そのため、配線とグランド導体との間で容量が形成されて、入出力端子のインピーダンスが容量性になり、インピーダンス不整合によるIL(挿入損失)が増大するという問題があった。

# [0004]

そこで、特許文献 1 では、整合を改善するために、入出力端子に接続されたインダクタ が積層回路基板の内部に形成された積層基板モジュールが開示されている。

【先行技術文献】

#### 【特許文献】

# [0005]

40

【特許文献 1 】特開 2 0 1 1 - 7 7 7 2 3 号公報

# 【発明の概要】

【発明が解決しようとする課題】

# [0006]

しかしながら、特許文献1のように積層基板モジュールの内部にインダクタが形成され、グランド導体に近接している場合、信号がインダクタを伝播する時にインダクタで磁界が発生し、インダクタと対向するグランド導体の一部で渦電流が発生する。特に、低背な構造の積層基板モジュールでは、インダクタとグランド導体との間隔がより狭くなるため、この渦電流は大きくなる。

#### [0007]

そのため、特許文献1の積層基板モジュールでは、インダクタのQ値が劣化し、ILの 改善効果が十分に得られないという問題がある。

#### [0008]

そこで本発明の目的は、インダクタのQ値を向上させ、IL改善効果が十分に得られる 積層基板モジュールを提供することにある。

### 【課題を解決するための手段】

#### [0009]

本発明の積層基板モジュールは、前記課題を解決するために以下の構成を備えている。

#### [0010]

(1)導体パターンが形成された複数の層を積層した積層回路基板と、

前記積層回路基板の一方主面に形成された第1外部接続用端子と、

前記積層回路基板の他方主面に形成された第2外部接続用端子と、を備え、

前記積層回路基板の内部には、前記第1外部接続用端子と前記第2外部接続用端子とを 結ぶ配線と、前記配線の一部を構成するインダクタと、前記インダクタより前記一方主面 側に位置する第1グランド導体と、前記インダクタより前記他方主面側に位置する第2グ ランド導体と、が前記導体パターンにより形成されており、

前記インダクタの形成箇所は、前記積層回路基板の前記一方主面または前記他方主面を 正面視したとき、前記第1、第2グランド導体の内、前記インダクタが形成されている層 に近い方のグランド導体の形成箇所と異なる、積層基板モジュール。

## [0011]

この構成では、第 1 、第 2 グランド導体の内、インダクタが形成されている層に近い方のグランド導体がインダクタと対向しない。そのため、信号がインダクタを伝播する時にインダクタで磁界が発生しても、その磁界が当該グランド導体に殆ど作用せず、当該グランド導体における渦電流の発生を十分に抑制できる。

#### [0012]

したがって、この構成によれば、インダクタのQ値を向上させ、IL改善効果を十分に得ることができる。

#### [0013]

(2)前記インダクタの形成箇所は、前記積層回路基板の前記一方主面または前記他方主面を正面視したとき、前記第1外部接続用端子および前記第2外部接続用端子の少なくとも一方の形成箇所と重なることが好ましい。

# [0014]

この構成では、積層回路基板の一方主面の内、第1外部接続用端子が形成されていない領域に第3外部接続用端子が形成される。または、積層回路基板の他方主面の内、第2外部接続用端子が形成される。

#### [0015]

そのため、この構成では、インダクタの形成箇所が第3外部接続用端子の形成箇所と重ならない。すなわち、この構成では、第3外部接続用端子が積層回路基板においてインダクタから離れた構造になる。したがって、この構成によれば、インダクタを設けているが、第3外部接続用端子のアイソレーション特性の劣化を防ぐことができる。

# [0016]

(3)前記グランド導体は、その形成箇所が、前記積層回路基板の前記一方主面または前記他方主面を正面視したときに前記インダクタの形成箇所と異なるように開口していることが好ましい。

#### [0017]

この構成では、グランド導体の一部に開口を設けることで、積層回路基板の一方主面または他方主面を正面視したときにおけるインダクタの形成箇所が前記グランド導体の形成 箇所と重ならない。

### [0018]

よって、この構成では、グランド導体の一部に開口を設けるだけで、インダクタの形成

10

20

30

40

10

20

30

40

50

箇所を前記グランド導体の形成箇所と異ならせた積層回路基板を作成できる。したがって、この構成によれば、インダクタの形成箇所に応じた前記グランド導体の導体パターンの設計変更が不要なため、積層基板モジュールの製造コストを低減できる。

#### [0019]

(4)前記インダクタの一部は、第1インダクタを構成し、

前記インダクタの残りの部分は、第2インダクタを構成し、

前記第1インダクタは、前記積層回路基板の前記一方主面または前記他方主面を正面視したとき、前記第2インダクタと異なる箇所に形成されていることが好ましい。

### [0020]

この構成では、積層回路基板の一方主面または他方主面を正面視したとき、第1、第2 グランド導体の内、第1インダクタが形成されている層に近い方の第1グランド導体の形 成箇所と、第1インダクタの形成箇所とを異ならせることができる。

#### [0021]

同様に、この構成では、積層回路基板の一方主面または他方主面を正面視したとき、第 1、第2グランド導体の内、第2インダクタが形成されている層に近い方の第2グランド 導体の形成箇所と、第2インダクタの形成箇所とを異ならせることができる。

### [0022]

よって、この構成では、信号がインダクタを伝播する時にインダクタで磁界が発生して も、その磁界が第1グランド導体および第2グランド導体に殆ど作用せず、第1グランド 導体および第2グランド導体の両方における渦電流の発生を十分に抑制できる。

#### [0023]

したがって、この構成によれば、インダクタのQ値をより向上させることができる。そのため、より高いIL改善効果が得られる。

#### [0024]

(5)前記インダクタの形成箇所は、前記積層回路基板の前記一方主面または前記他方主面を正面視したとき、前記第1、第2グランド導体の両方の形成箇所と異なることが好ましい。

### [0025]

この構成では、信号がインダクタを伝播する時にインダクタで磁界が発生しても、その磁界が第1グランド導体および第2グランド導体に殆ど作用せず、第1グランド導体および第2グランド導体の両方における渦電流の発生を十分に抑制できる。

# [0026]

したがって、この構成によれば、インダクタのQ値をより向上させることができる。そのため、より高いIL改善効果が得られる。

### [0027]

(6)前記インダクタは、前記第1外部接続用端子と直列に接続されていることが好ましい。

### [0028]

(7)前記インダクタは、前記配線を前記第1グランド導体または前記第2グランド導体 に接続することが好ましい。

# 【発明の効果】

#### [0029]

この発明によれば、インダクタのQ値を向上させ、IL改善効果が十分に得ることができる。

### 【図面の簡単な説明】

# [0030]

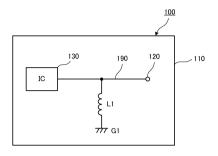

- 【図1】本発明の第1実施形態に係る積層基板モジュール100の回路図である。

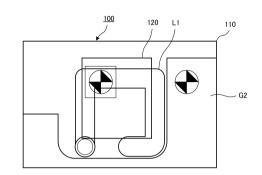

- 【図2】図1に示す積層基板モジュール100の主要部の平面透視図である。

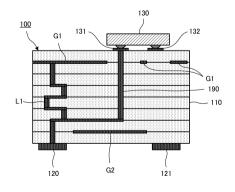

- 【図3】図1に示す積層基板モジュール100の主要部の断面図である。

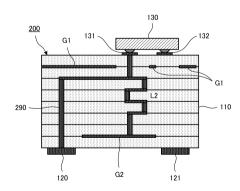

- 【図4】本発明の第2実施形態に係る積層基板モジュール200の主要部の断面図である

【図5】本発明の第3実施形態に係る積層基板モジュール300の主要部の断面図である

【図6】本発明の第4実施形態に係る積層基板モジュール400の主要部の断面図である

【図7】本発明の第5実施形態に係る積層基板モジュール500の主要部の断面図である

【図8】本発明の第6実施形態に係る積層基板モジュール600の主要部の断面図である

。 【 図 9 】本発明の第7実施形態に係る積層基板モジュール700の主要部の断面図である

【図10】本発明の第8実施形態に係る積層基板モジュール800の主要部の断面図であ

【図11】本発明の第9実施形態に係る積層基板モジュール900の主要部の断面図である。

【図12】本発明の第10実施形態に係る積層基板モジュール1000の主要部の断面図である。

【発明を実施するための形態】

[0031]

《本発明の第1実施形態》

以下、本発明の第1実施形態に係る積層基板モジュール100について説明する。

[0032]

図1は、本発明の第1実施形態に係る積層基板モジュール100の回路図である。図2は、図1に示す積層回路基板110の他方主面を正面視したときの積層基板モジュール100の主要部の平面透視図である。図3は、図1に示す積層基板モジュール100の主要部の断面図である。

[0033]

積層基板モジュール100は、積層回路基板110と、実装用ランド131、132と、入出力端子120、121と、を備えている。

なお、実装用ランド131が、本発明の「第1外部接続用端子」に相当する。また、入出力端子120が、本発明の「第2外部接続用端子」に相当する。また、実装用ランド132及び入出力端子121のそれぞれが、前記「第3外部接続用端子」に相当する。

[0034]

積層回路基板110は、導体パターンが形成された複数の誘電体層を積層してなる積層体である。誘電体層は、例えばセラミック又は樹脂からなる。積層回路基板110の各誘電体層に対する導体パターンの形成は、例えばスクリーン印刷版を用いたスクリーン印刷法で行われる。

[0035]

入出力端子120、121は、積層回路基板110の他方主面(底面)に導体パターンにより形成されている。入出力端子120、121は、積層基板モジュール100の外部回路と接続するための端子である。

[0036]

実装用ランド131、132は、積層回路基板110の一方主面(上面)に導体パターンにより形成されている。実装用ランド131、132の上には、積層基板モジュール100のスイッチIC130が実装される。

[0037]

スイッチIC130は、例えばCMOS構造からなり、平面視して略矩形からなるFETスイッチICである。スイッチIC130は、アンテナに接続するアンテナ接続ポートと複数の高周波入出力ポート(送信ポートや受信ポート、さらには送受兼用ポート)とを有する。スイッチIC130は、制御信号により、高周波信号入出力ポートのいずれかと

20

10

30

40

アンテナ接続ポートとを接続するように切替制御を行う。

#### [0038]

積層回路基板110の内部には、図1、図3に示すように、実装用ランド131及び入出力端子120を結ぶ配線190と、配線190の一部を構成するインダクタL1と、インダクタL1より一方主面側に位置する第1グランド導体G1と、インダクタL1より他方主面側に位置する第2グランド導体G2とが、導体パターンにより形成されている。

#### [0039]

インダクタL1は、配線190を第1グランド導体G1にシャント接続する。また、インダクタL1の形成箇所は、図2、図3に示すように、積層回路基板110の一方主面または他方主面を正面視したとき、入出力端子120の形成箇所と重なる。

# [0040]

ここで、インダクタL1の形成箇所は、図2、図3に示すように、積層回路基板110の一方主面または他方主面を正面視したとき、第1グランド導体G1及び第2グランド導体G2の内、インダクタL1が形成されている層に近い方の第2グランド導体G2の形成箇所と異なる。すなわち、第2グランド導体G2は、インダクタL1と対向しない。

#### [0041]

そのため、信号がインダクタ L 1 を伝播する時にインダクタ L 1 で磁界が発生しても、その磁界が第 2 グランド導体 G 2 に殆ど作用せず、第 2 グランド導体 G 2 における渦電流の発生を十分に抑制できる。

# [0042]

したがって、積層基板モジュール100によれば、インダクタL1のQ値を向上させ、 IL改善効果が十分に得られる。

# [0043]

また、インダクタL1の形成箇所は、図2、図3に示すように、積層回路基板110の一方主面または他方主面を正面視したとき、入出力端子120の形成箇所と重なる。そして、積層回路基板110の他方主面の内、入出力端子120が形成されていない領域に別の入出力端子121が形成されている。

#### [0044]

そのため、積層基板モジュール100では、インダクタL1の形成箇所が入出力端子1 2 1の形成箇所と重ならない。すなわち、積層基板モジュール100は、入出力端子12 1 が積層回路基板110においてインダクタL1から離れた構造になる。

# [0045]

したがって、積層基板モジュール100によれば、インダクタL1を設けているが、入出力端子121のアイソレーション特性の劣化を防ぐことができる。

# [0046]

《本発明の第2実施形態》

以下、本発明の第2実施形態に係る積層基板モジュール200について説明する。

### [0047]

図4は、本発明の第2実施形態に係る積層基板モジュール200の主要部の断面図である。第2実施形態に係る積層基板モジュール200が第1実施形態に係る積層基板モジュール100と相違する点は、配線290である。その他の積層基板モジュール200の構成については積層基板モジュール100と同じであるため、説明を省略する。

#### [0048]

詳述すると、積層回路基板 1 1 0 の内部には、図 4 に示すように、実装用ランド 1 3 1 及び入出力端子 1 2 0 を結ぶ配線 2 9 0 と、配線 2 9 0 の一部を構成するインダクタ L 2 と、第 1 グランド導体 G 1 と、第 2 グランド導体 G 2 とが、導体パターンにより形成されている。

# [0049]

インダクタL2は、配線290を第2グランド導体G2にシャント接続する。また、インダクタL2の形成箇所は、積層回路基板110の一方主面または他方主面を正面視した

10

20

30

40

10

20

30

40

50

とき、実装用ランド131の形成箇所と重なる。

### [0050]

ここで、インダクタL2の形成箇所は、図4に示すように、積層回路基板110の一方 主面または他方主面を正面視したとき、第1グランド導体G1及び第2グランド導体G2 の内、インダクタL2が形成されている層に近い方の第1グランド導体G1の形成箇所と 異なる。すなわち、第1グランド導体G1は、インダクタL2と対向しない。

#### [0051]

そのため、信号がインダクタL2を伝播する時にインダクタL2で磁界が発生しても、その磁界が第1グランド導体 G 1 に殆ど作用せず、第1グランド導体 G 1 における渦電流の発生を十分に抑制できる。

[0052]

したがって、積層基板モジュール 2 0 0 によれば、積層基板モジュール 1 0 0 と同様の効果を奏する。

[0053]

また、インダクタL2の形成箇所は、図4に示すように、積層回路基板110の一方主面または他方主面を正面視したとき、実装用ランド131の形成箇所と重なる。そして、積層回路基板110の一方主面の内、実装用ランド131が形成されていない領域に別の実装用ランド132が形成されている。

[0054]

そのため、積層基板モジュール200では、インダクタL2の形成箇所が実装用ランド132の形成箇所と重ならない。すなわち、積層基板モジュール200は、実装用ランド132が積層回路基板110においてインダクタL2から離れた構造になる。

[0055]

したがって、積層基板モジュール 2 0 0 によれば、インダクタ L 2 を設けているが、実 装用ランド 1 3 2 のアイソレーション特性の劣化を防ぐことができる。

[0056]

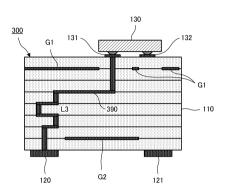

《本発明の第3実施形態》

以下、本発明の第3実施形態に係る積層基板モジュール300について説明する。

[0057]

図5は、本発明の第3実施形態に係る積層基板モジュール300の主要部の断面図である。第3実施形態に係る積層基板モジュール300が第1実施形態に係る積層基板モジュール100と相違する点は、配線390である。その他の積層基板モジュール300の構成については積層基板モジュール100と同じであるため、説明を省略する。

[0058]

詳述すると、積層回路基板110の内部には、図5に示すように、実装用ランド131及び入出力端子120を結ぶ配線390と、配線390の一部を構成するインダクタL3と、第1グランド導体G1と、第2グランド導体G2とが、導体パターンにより形成されている。

[0059]

インダクタL3は、実装用ランド131と直列に接続されている。また、インダクタL3の形成箇所は、積層回路基板110の一方主面または他方主面を正面視したとき、入出力端子120の形成箇所と重なる。

[0060]

ここで、インダクタL3の形成箇所は、図5に示すように、積層回路基板110の一方主面または他方主面を正面視したとき、第1グランド導体G1及び第2グランド導体G2の内、インダクタL3が形成されている層に近い方の第2グランド導体G2の形成箇所と異なる。すなわち、第2グランド導体G2は、インダクタL3と対向しない。

[0061]

そのため、信号がインダクタL3を伝播する時にインダクタL3で磁界が発生しても、 その磁界が第2グランド導体G2に殆ど作用せず、第2グランド導体G2における渦電流 の発生を十分に抑制できる。

# [0062]

したがって、積層基板モジュール300によれば、積層基板モジュール100と同様の効果を奏する。

### [0063]

また、インダクタL3の形成箇所は、図5に示すように、積層回路基板110の一方主面または他方主面を正面視したとき、入出力端子120の形成箇所と重なる。そして、積層回路基板110の他方主面の内、入出力端子120が形成されていない領域に別の入出力端子121が形成されている。

## [0064]

そのため、積層基板モジュール300では、インダクタL3の形成箇所が入出力端子121の形成箇所と重ならない。すなわち、積層基板モジュール300は、入出力端子121が積層回路基板110においてインダクタL3から離れた構造になる。

### [0065]

したがって、積層基板モジュール300によれば、インダクタL3を設けているが、入出力端子121のアイソレーション特性の劣化を防ぐことができる。

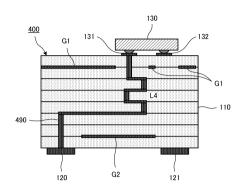

### [0066]

《本発明の第4実施形態》

以下、本発明の第4実施形態に係る積層基板モジュール400について説明する。

### [0067]

図6は、本発明の第4実施形態に係る積層基板モジュール400の主要部の断面図である。第4実施形態に係る積層基板モジュール400が第1実施形態に係る積層基板モジュール100と相違する点は、配線490である。その他の積層基板モジュール400の構成については積層基板モジュール100と同じであるため、説明を省略する。

#### [0068]

詳述すると、積層回路基板110の内部には、図6に示すように、実装用ランド131及び入出力端子120を結ぶ配線490と、配線490の一部を構成するインダクタL4と、第1グランド導体G1と、第2グランド導体G2とが、導体パターンにより形成されている。

# [0069]

インダクタL4は、実装用ランド131と直列に接続されている。また、インダクタL4の形成箇所は、積層回路基板110の一方主面または他方主面を正面視したとき、実装用ランド131の形成箇所と重なる。

# [0070]

ここで、インダクタL4の形成箇所は、図6に示すように、積層回路基板110の一方 主面または他方主面を正面視したとき、第1グランド導体G1及び第2グランド導体G2 の内、インダクタL4が形成されている層に近い方の第1グランド導体G1の形成箇所と 異なる。すなわち、第1グランド導体G1は、インダクタL4と対向しない。

## [0071]

そのため、信号がインダクタL4を伝播する時にインダクタL4で磁界が発生しても、その磁界が第1グランド導体G1に殆ど作用せず、第1グランド導体G1における渦電流の発生を十分に抑制できる。

## [0072]

したがって、積層基板モジュール400によれば、積層基板モジュール100と同様の 効果を奏する。

# [0073]

また、インダクタL4の形成箇所は、図6に示すように、積層回路基板110の一方主面または他方主面を正面視したとき、実装用ランド131の形成箇所と重なる。そして、積層回路基板110の一方主面の内、実装用ランド131が形成されていない領域に別の実装用ランド132が形成されている。

10

20

30

40

#### [0074]

そのため、積層基板モジュール400では、インダクタL4の形成箇所が実装用ランド132の形成箇所と重ならない。すなわち、積層基板モジュール400は、実装用ランド132が積層回路基板110においてインダクタL4から離れた構造になる。

### [0075]

したがって、積層基板モジュール400によれば、インダクタL4を設けているが、実 装用ランド132のアイソレーション特性の劣化を防ぐことができる。

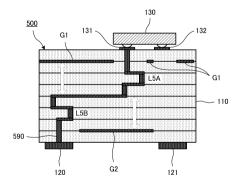

## [0076]

《本発明の第5実施形態》

以下、本発明の第5実施形態に係る積層基板モジュール500について説明する。

# [0077]

図7は、本発明の第5実施形態に係る積層基板モジュール500の主要部の断面図である。第5実施形態に係る積層基板モジュール500が第1実施形態に係る積層基板モジュール100と相違する点は、配線590である。その他の積層基板モジュール500の構成については積層基板モジュール100と同じであるため、説明を省略する。

#### [0078]

詳述すると、積層回路基板 1 1 0 の内部には、図 7 に示すように、実装用ランド 1 3 1 及び入出力端子 1 2 0 を結ぶ配線 5 9 0 と、配線 5 9 0 の一部を構成するインダクタ L 5 A、 L 5 B と、第 1 グランド導体 G 1 と、第 2 グランド導体 G 2 とが、導体パターンにより形成されている。

#### [0079]

なお、インダクタ L 5 A が、本発明の「第 1 インダクタ」に相当する。また、インダクタ L 5 B が、本発明の「第 2 インダクタ」に相当する。

# [0800]

インダクタL5A、L5Bは、実装用ランド131と直列に接続されている。インダクタL5Aは、積層回路基板110の一方主面または他方主面を正面視したとき、インダクタL5Bと異なる箇所に形成されている。

#### [0081]

また、インダクタL5Aの形成箇所は、積層回路基板110の一方主面または他方主面を正面視したとき、実装用ランド131の形成箇所と重なる。また、インダクタL5Bの形成箇所は、積層回路基板110の一方主面または他方主面を正面視したとき、入出力端子120の形成箇所と重なる。

### [0082]

ここで、インダクタL5Aの形成箇所は、図7に示すように、積層回路基板110の一方主面または他方主面を正面視したとき、第1グランド導体G1及び第2グランド導体G2の内、インダクタL5Aが形成されている層に近い方の第1グランド導体G1の形成箇所と異なる。

### [0083]

同様に、インダクタL5Bの形成箇所は、図7に示すように、積層回路基板110の一方主面または他方主面を正面視したとき、第1グランド導体G1及び第2グランド導体G2の内、インダクタL5Bが形成されている層に近い方の第2グランド導体G2の形成箇所と異なる。

# [0084]

すなわち、第 1 グランド導体 G 1 は、インダクタ L 5 A と対向せず、第 2 グランド導体 G 2 は、インダクタ L 5 B と対向しない。

# [0085]

さらに、積層基板モジュール500におけるインダクタL5Aと第2グランド導体G2との間隔は、積層基板モジュール400におけるインダクタL4と第2グランド導体G2との間隔より広い(図6、図7の矢印参照)。

## [0086]

10

20

30

同様に、積層基板モジュール500におけるインダクタL5Bと第1グランド導体G1との間隔は、積層基板モジュール100におけるインダクタL1と第1グランド導体G1との間隔より広い(図3、図7の矢印参照)。

#### [0087]

そのため、信号がインダクタ L 5 B を伝播する時にインダクタ L 5 B で磁界が発生しても、その磁界が第 1 グランド導体 G 1 及び第 2 グランド導体 G 2 に殆ど作用せず、第 1 グランド導体 G 1 及び第 2 グランド導体 G 2 の両方における渦電流の発生を十分に抑制できる。

### [0088]

同様に、信号がインダクタL5Aを伝播する時にインダクタL5Aで磁界が発生しても、その磁界が第1グランド導体G1及び第2グランド導体G2に殆ど作用せず、第1グランド導体G1及び第2グランド導体G2の両方における渦電流の発生を十分に抑制できる

# [0089]

したがって、積層基板モジュール500によれば、積層基板モジュール100よりインダクタL5A、L5BのQ値を向上させることができる。そのため、積層基板モジュール500によれば、積層基板モジュール100より高いIL改善効果が得られる。

#### [0090]

また、インダクタL5Aの形成箇所は、図7に示すように、積層回路基板110の一方主面または他方主面を正面視したとき、実装用ランド131の形成箇所と重なる。そして、積層回路基板110の一方主面の内、実装用ランド131が形成されていない領域に別の実装用ランド132が形成されている。

#### [0091]

また、インダクタL5Bの形成箇所は、図7に示すように、積層回路基板110の一方主面または他方主面を正面視したとき、入出力端子120の形成箇所と重なる。そして、積層回路基板110の他方主面の内、入出力端子120が形成されていない領域に別の入出力端子121が形成されている。

#### [0092]

そのため、積層基板モジュール500ではインダクタL5A、L5Bの形成箇所が、実装用ランド132及び入出力端子121の形成箇所と重ならない。すなわち、積層基板モジュール500は、実装用ランド132及び入出力端子121が積層回路基板110においてインダクタL5A、L5Bから離れた構造になる。

#### [0093]

したがって、積層基板モジュール 5 0 0 によれば、インダクタL 5 A 、L 5 B を設けているが、実装用ランド 1 3 2 及び入出力端子 1 2 1 のアイソレーション特性の劣化を防ぐことができる。

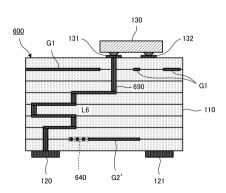

# [0094]

《本発明の第6実施形態》

以下、本発明の第6実施形態に係る積層基板モジュール600について説明する。

#### [0095]

図8は、本発明の第6実施形態に係る積層基板モジュール600の主要部の断面図である。第6実施形態に係る積層基板モジュール600が第1実施形態に係る積層基板モジュール100と相違する点は、配線690及び第2グランド導体G2 である。その他の積層基板モジュール600の構成については積層基板モジュール100と同じであるため、説明を省略する。

# [0096]

詳述すると、積層回路基板 1 1 0 の内部には、図 8 に示すように、実装用ランド 1 3 1 及び入出力端子 1 2 0 を結ぶ配線 6 9 0 と、配線 6 9 0 の一部を構成するインダクタ L 6 と、第 1 グランド導体 G 1 と、第 2 グランド導体 G 2 とが、導体パターンにより形成されている。

10

20

30

40

#### [0097]

第2グランド導体 G 2 は、積層回路基板 1 1 0 の一方主面または他方主面を正面視したときにインダクタ L 6 の形成箇所を含むように、開口部 6 4 0 によって開口している。つまりインダクタ L 6 の形成箇所は、積層回路基板 1 1 0 の一方主面または他方主面を正面視したときに開口部 6 4 0 とは重なり、また、第2グランド導体 G 2 とは異なる。その他の第2グランド導体 G 2 の構成については第2グランド導体 G 2 と同じであるため、説明を省略する。

### [0098]

インダクタL6は、実装用ランド131と直列に接続されている。また、インダクタL6の形成箇所は、積層回路基板110の一方主面または他方主面を正面視したとき、入出力端子120の形成箇所と重なる。

#### [0099]

ここで、インダクタL6の形成箇所は、図8に示すように、積層回路基板110の一方 主面または他方主面を正面視したとき、第1グランド導体G1及び第2グランド導体G2 の内、インダクタL6が形成されている層に近い方の第2グランド導体G2 の形成箇 所と異なる。すなわち、第2グランド導体G2 は、インダクタL6と対向しない。

### [0100]

そのため、信号がインダクタL6を伝播する時にインダクタL6で磁界が発生しても、 その磁界が第2グランド導体G2 に殆ど作用せず、第2グランド導体G2 における渦 電流の発生を十分に抑制できる。

20

30

10

#### [0101]

したがって、積層基板モジュール600によれば、積層基板モジュール100と同様の 効果を奏する。

### [0102]

また、インダクタL6の形成箇所は、図8に示すように、積層回路基板110の一方主面または他方主面を正面視したとき、入出力端子120の形成箇所と重なる。そして、積層回路基板110の他方主面の内、入出力端子120が形成されていない領域に別の入出力端子121が形成されている。

## [0103]

そのため、積層基板モジュール600では、インダクタL6の形成箇所が入出力端子121の形成箇所と重ならない。すなわち、積層基板モジュール600では、入出力端子121が積層回路基板110においてインダクタL6から離れた構造になる。したがって、積層基板モジュール600によれば、インダクタL6を設けているが、入出力端子121のアイソレーション特性の劣化を防ぐことができる。

[0104]

さらに、積層基板モジュール600では、第2グランド導体G2の一部に開口を設けるだけで、インダクタL6の形成箇所を第2グランド導体G2 の形成箇所と異ならせた積層回路基板110を作成できる。

## [0105]

したがって、積層基板モジュール600によれば、インダクタL6の形成箇所に応じた 導体パターンの設計変更が不要なため、積層基板モジュール600の製造コストを低減で きる。 40

## [0106]

《本発明の第7実施形態》

以下、本発明の第7実施形態に係る積層基板モジュール700について説明する。

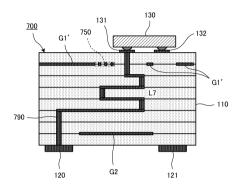

# [0107]

図9は、本発明の第7実施形態に係る積層基板モジュール700の主要部の断面図である。第7実施形態に係る積層基板モジュール700が第1実施形態に係る積層基板モジュール100と相違する点は、配線790及び第1グランド導体G1 である。その他の積層基板モジュール700の構成については積層基板モジュール100と同じであるため、

説明を省略する。

### [0108]

詳述すると、積層回路基板 1 1 0 の内部には、図 9 に示すように、実装用ランド 1 3 1 及び入出力端子 1 2 0 を結ぶ配線 7 9 0 と、配線 7 9 0 の一部を構成するインダクタ L 7 と、第 1 グランド導体 G 1 と、第 2 グランド導体 G 2 とが、導体パターンにより形成されている。

#### [0109]

第1グランド導体 G 1 は、積層回路基板 1 1 0 の一方主面または他方主面を正面視したときにインダクタ L 7 の形成箇所を含むように、開口部 7 5 0 によって開口している。つまりインダクタ L 7 の形成箇所は、積層回路基板 1 1 0 の一方主面または他方主面を正面視したときに開口部 7 5 0 とは重なり、また、第1グランド導体 G 1 とは異なる。その他の第1グランド導体 G 1 の構成については第1グランド導体 G 1 と同じであるため、説明を省略する。

# [0110]

インダクタL7は、実装用ランド131と直列に接続されている。また、インダクタL7の形成箇所は、積層回路基板110の一方主面または他方主面を正面視したとき、実装用ランド131の形成箇所と重なる。

#### [0111]

ここで、インダクタL7の形成箇所は、図9に示すように、積層回路基板110の一方主面または他方主面を正面視したとき、第1グランド導体G1 及び第2グランド導体G2の内、インダクタL7が形成されている層に近い方の第1グランド導体G1 の形成箇所と異なる。すなわち、第1グランド導体G1 は、インダクタL7と対向しない。

### [0112]

そのため、信号がインダクタL7を伝播する時にインダクタL7で磁界が発生しても、 その磁界が第1グランド導体G1 に殆ど作用せず、第1グランド導体G1 における渦 電流の発生を十分に抑制できる。

#### [0113]

したがって、積層基板モジュール700によれば、積層基板モジュール100と同様の 効果を奏する。

# [0114]

また、インダクタL7の形成箇所は、図9に示すように、積層回路基板110の一方主面または他方主面を正面視したとき、実装用ランド131の形成箇所と重なる。そして、積層回路基板110の一方主面の内、実装用ランド131が形成されていない領域に別の実装用ランド132が形成されている。

### [0115]

そのため、積層基板モジュール700では、インダクタL7の形成箇所が実装用ランド132の形成箇所と重ならない。すなわち、積層基板モジュール700では、実装用ランド132が積層回路基板110においてインダクタL7から離れた構造になる。したがって、積層基板モジュール700によれば、インダクタL7を設けているが、実装用ランド132のアイソレーション特性の劣化を防ぐことができる。

# [0116]

さらに、積層基板モジュール700では、第1グランド導体G1の一部に開口を設けるだけで、インダクタL7の形成箇所を第1グランド導体G1 の形成箇所と異ならせた積層回路基板110を作成できる。

#### [0117]

したがって、積層基板モジュール700によれば、インダクタL7の形成箇所に応じた 導体パターンの設計変更が不要なため、積層基板モジュール700の製造コストを低減で きる。

### [0118]

《本発明の第8実施形態》

10

20

30

10

20

30

40

50

以下、本発明の第8実施形態に係る積層基板モジュール800について説明する。

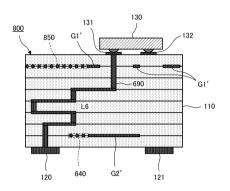

#### [0119]

図10は、本発明の第8実施形態に係る積層基板モジュール800の主要部の断面図である。第8実施形態に係る積層基板モジュール800が第6実施形態に係る積層基板モジュール600と相違する点は、第1グランド導体G1 である。その他の積層基板モジュール800の構成については積層基板モジュール600と同じであるため、説明を省略する。

# [0120]

詳述すると、積層回路基板 1 1 0 の内部には、図 1 0 に示すように、実装用ランド 1 3 1 及び入出力端子 1 2 0 を結ぶ配線 6 9 0 と、配線 6 9 0 の一部を構成するインダクタ L 6 と、第 1 グランド導体 G 1 と、第 2 グランド導体 G 2 とが、導体パターンにより形成されている。

# [0121]

第1グランド導体 G 1 は、積層回路基板 1 1 0 の一方主面または他方主面を正面視したときにインダクタ L 7 の形成箇所を含むように、開口部 8 5 0 によって開口している。その他の第1グランド導体 G 1 と同じであるため、説明を省略する。

# [0122]

ここで、インダクタL6の形成箇所は、図10に示すように、積層回路基板110の一方主面または他方主面を正面視したとき、第1グランド導体 G 1 及び第2グランド導体 G 2 の両方の形成箇所と異なる。すなわち、第1グランド導体 G 1 及び第2グランド 導体 G 2 のそれぞれは、インダクタL6と対向しない。

### [0123]

そのため、信号がインダクタL6を伝播する時にインダクタL6で磁界が発生しても、その磁界が第1グランド導体G1 及び第2グランド導体G2 に殆ど作用せず、第1グランド導体G1 及び第2グランド導体G2 の両方における渦電流の発生を十分に抑制できる。

### [0124]

したがって、積層基板モジュール800によれば、積層基板モジュール100よりインダクタL6のQ値を向上させることができる。そのため、積層基板モジュール800によれば、積層基板モジュール100より高いIL改善効果が得られる。

# [0125]

また、インダクタL6の形成箇所は、図10に示すように、積層回路基板110の一方主面または他方主面を正面視したとき、入出力端子120の形成箇所と重なる。そして、積層回路基板110の他方主面の内、入出力端子120が形成されていない領域に別の入出力端子121が形成されている。

# [0126]

そのため、積層基板モジュール800では、インダクタL6の形成箇所が入出力端子1 21の形成箇所と重ならない。すなわち、積層基板モジュール800は、入出力端子12 1が積層回路基板110においてインダクタL6から離れた構造になる。

# [0127]

したがって、積層基板モジュール800によれば、インダクタL6を設けているが、入出力端子121のアイソレーション特性の劣化を防ぐことができる。

# [0128]

さらに、積層基板モジュール 8 0 0 では、第 1 グランド導体 G 1 の一部と第 2 グランド 導体 G 2 の一部とに開口を設けるだけで、インダクタ L 6 の形成箇所を第 1 グランド導体 G 1 及び第 2 グランド導体 G 2 のそれぞれの形成箇所と異ならせた積層回路基板 1 1 0 を作成できる。

# [0129]

したがって、積層基板モジュール800によれば、インダクタL6の形成箇所に応じた

導体パターンの設計変更が不要なため、積層基板モジュール800の製造コストを低減できる。

#### [0130]

《本発明の第9実施形態》

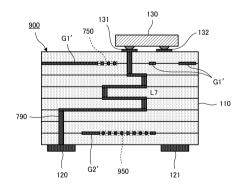

以下、本発明の第9実施形態に係る積層基板モジュール900について説明する。

#### [0131]

図11は、本発明の第9実施形態に係る積層基板モジュール900の主要部の断面図である。第9実施形態に係る積層基板モジュール900が第7実施形態に係る積層基板モジュール700と相違する点は、第2グランド導体G2 である。その他の積層基板モジュール900の構成については積層基板モジュール700と同じであるため、説明を省略する。

[0132]

詳述すると、積層回路基板110の内部には、図11に示すように、実装用ランド13 1及び入出力端子120を結ぶ配線790と、配線790の一部を構成するインダクタL 7と、第1グランド導体G1 と、第2グランド導体G2 とが、導体パターンにより形成されている。

[0133]

第2グランド導体G2 は、積層回路基板110の一方主面または他方主面を正面視したときにインダクタL7の形成箇所を含むように、開口部950によって開口している。その他の第2グランド導体G2 の構成については第2グランド導体G2と同じであるため、説明を省略する。

[0134]

ここで、インダクタL7の形成箇所は、図11に示すように、積層回路基板110の一方主面または他方主面を正面視したとき、第1グランド導体G1 及び第2グランド導体G2 の両方の形成箇所と異なる。すなわち、第1グランド導体G1 及び第2グランド導体G2 のそれぞれは、インダクタL7と対向しない。

[0135]

そのため、信号がインダクタL7を伝播する時にインダクタL7で磁界が発生しても、その磁界が第1グランド導体G1 及び第2グランド導体G2 に殆ど作用せず、第1グランド導体G1 及び第2グランド導体G2 の両方における渦電流の発生を十分に抑制できる。

[0136]

したがって、積層基板モジュール900によれば、積層基板モジュール100よりインダクタL7のQ値を向上させることができる。そのため、積層基板モジュール900によれば、積層基板モジュール100より高いIL改善効果が得られる。

[0137]

また、インダクタL7の形成箇所は、図11に示すように、積層回路基板110の一方主面または他方主面を正面視したとき、実装用ランド131の形成箇所と重なる。そして、積層回路基板110の一方主面の内、実装用ランド131が形成されていない領域に別の実装用ランド132が形成されている。

[0138]

そのため、積層基板モジュール900では、インダクタL7の形成箇所が実装用ランド132の形成箇所と重ならない。すなわち、積層基板モジュール900は、実装用ランド132が積層回路基板110においてインダクタL7から離れた構造になる。

[0139]

したがって、積層基板モジュール900によれば、インダクタL7を設けているが、実 装用ランド132のアイソレーション特性の劣化を防ぐことができる。

[0140]

さらに、積層基板モジュール900では、第1グランド導体G1の一部と第2グランド 導体G2の一部とに開口を設けるだけで、インダクタL7の形成箇所を第1グランド導体 10

20

30

40

G 1 及び第 2 グランド導体 G 2 のそれぞれの形成箇所と異ならせた積層回路基板 1 1 0 を作成できる。

### [0141]

したがって、積層基板モジュール900によれば、インダクタL7の形成箇所に応じた 導体パターンの設計変更が不要なため、積層基板モジュール900の製造コストを低減で きる。

#### [0142]

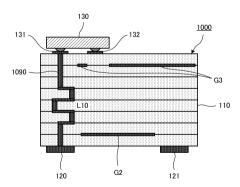

《本発明の第10実施形態》

以下、本発明の第10実施形態に係る積層基板モジュール1000について説明する。

#### [0143]

図12は、本発明の第10実施形態に係る積層基板モジュール1000の主要部の断面 図である。第10実施形態に係る積層基板モジュール1000が第1実施形態に係る積層 基板モジュール100と相違する点は、配線1090及び第1グランド導体G3である。 その他の積層基板モジュール1000の構成については積層基板モジュール100と同じ であるため、説明を省略する。

#### [0144]

詳述すると、積層回路基板 1 1 0 の内部には、図 1 2 に示すように、実装用ランド 1 3 1 及び入出力端子 1 2 0 を結ぶ配線 1 0 9 0 と、配線 1 0 9 0 の一部を構成するインダクタ L 1 0 と、第 1 グランド導体 G 3 と、第 2 グランド導体 G 2 とが、導体パターンにより形成されている。

#### [0145]

第1グランド導体G3は、積層回路基板110の一方主面または他方主面を正面視したときにインダクタL10の形成箇所と異なるように、形成されている。

#### [0146]

同様に、第2グランド導体G2も、積層回路基板110の一方主面または他方主面を正面視したときにインダクタL10の形成箇所と異なるように、形成されている。

# [0147]

また、インダクタL10は、実装用ランド131と直列に接続されている。また、インダクタL10の形成箇所は、積層回路基板110の一方主面または他方主面を正面視したとき、入出力端子120の形成箇所と実装用ランド131の形成箇所とに重なる。

#### [0148]

ここで、インダクタL10の形成箇所は、図12に示すように、積層回路基板110の一方主面または他方主面を正面視したとき、第1グランド導体G3及び第2グランド導体G2の両方の形成箇所と異なる。すなわち、第1グランド導体G3及び第2グランド導体G2のそれぞれは、インダクタL10と対向しない。

## [0149]

そのため、信号がインダクタL10を伝播する時にインダクタL10で磁界が発生しても、その磁界が第1グランド導体G3及び第2グランド導体G2に殆ど作用せず、第1グランド導体G3及び第2グランド導体G2の両方における渦電流の発生を十分に抑制できる。

# [0150]

したがって、積層基板モジュール1000によれば、積層基板モジュール100よりインダクタL10のQ値を向上させることができる。そのため、積層基板モジュール100 0によれば、積層基板モジュール100より高いIL改善効果が得られる。

#### [0151]

また、インダクタL10の形成箇所は、図12に示すように、積層回路基板110の一方主面または他方主面を正面視したとき、実装用ランド131の形成箇所と重なる。そして、積層回路基板110の一方主面の内、実装用ランド131が形成されていない領域に別の実装用ランド132が形成されている。

# [0152]

10

20

30

また、インダクタL10の形成箇所は、図12に示すように、積層回路基板110の一方主面または他方主面を正面視したとき、入出力端子120の形成箇所と重なる。そして、積層回路基板110の他方主面の内、入出力端子120が形成されていない領域に別の入出力端子121が形成されている。

# [0153]

そのため、積層基板モジュール1000ではインダクタL10の形成箇所が、実装用ランド132及び入出力端子121の形成箇所と重ならない。すなわち、積層基板モジュール1000は、実装用ランド132及び入出力端子121が積層回路基板110においてインダクタL10から離れた構造になる。

#### [0154]

したがって、積層基板モジュール1000によれば、インダクタL10を設けているが、実装用ランド132及び入出力端子121のアイソレーション特性の劣化を防ぐことができる。

# [0155]

## 《その他の実施形態》

なお、前記各実施形態では実装用ランド 131、 132 に IC130 が実装されているが、これに限るものではない。例えば実装用ランド 131、 132 に、SAW (Surface Acoustic Wave Filter) デバイス等の他の実装部品が実装されていてもよい。

# [0156]

最後に、上述の実施形態の説明は、すべての点で例示であって、制限的なものではないと考えられるべきである。本発明の範囲は、上述の実施形態ではなく、特許請求の範囲によって示される。さらに、本発明の範囲には、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

#### 【符号の説明】

# [0157]

100、200、300、400、500、600、700、800、900、1000 .... 積層基板モジュール

110...積層回路基板

1 2 0 、 1 2 1 ... 入出力端子

130 ... スイッチIC

131、132…実装用ランド

190、290、390、490、590、690、790、1090...配線

6 4 0 、 7 5 0 、 8 5 0 、 9 5 0 ... 開口部

10

20

【図1】 【図2】 図2

【図3】 図3 図4】

【図5】 【図6】 図6

【図7】 【図8】 図8

図10

【図10】 【図9】

【図11】 【図12】 図11 図12

# フロントページの続き

(56)参考文献 特開平04-082297(JP,A)

特開2011-171501(JP,A)

特開2011-151367(JP,A)

(58)調査した分野(Int.CI., DB名)

H01L 23/12

H01F 17/00

H 0 5 K 3 / 4 6