심사관 :

진수영

# (19) 대한민국특허청(KR)

# (12) 등록특허공보(B1)

(51) Int. Cl.

**H01L 33/38** (2010.01)

(21) 출원번호 10-2009-0013157

(22) 출원일자 **2009년02월17일** 심사청구일자 **2009년02월17일**

(65) 공개번호 10-2010-0093977

(43) 공개일자 **2010년08월26일**

(56) 선행기술조사문헌

US20090039367 A1

US5113232 A US6903381 B2

KR100640496 B1

전체 청구항 수 : 총 16 항

(45) 공고일자 2011년02월10일

(11) 등록번호 10-1014136

(24) 등록일자 2011년02월01일

(73) 특허권자

## 엘지이노텍 주식회사

서울특별시 중구 남대문로5가 541 서울스퀘어

(72) 발명자

#### 정환희

울산 남구 야음동 신정현대홈타운아파트 204동 602호

(74) 대리인

서교준

## (54) 반도체 발광소자 및 그 제조방법

## (57) 요 약

실시 예는 반도체 발광소자 및 그 제조방법에 관한 것이다.

실시 예에 따른 반도체 발광소자는 복수의 화합물 반도체층을 포함하는 발광 구조물; 상기 발광 구조물 아래의 외측 둘레를 따라 형성된 복수의 아이솔레이션층; 상기 복수의 아이솔레이션층 사이에 형성된 금속층; 상기 발광 구조물의 아래에 형성된 제2전극층을 포함한다.

## 대 표 도 - 도1

### 특허청구의 범위

### 청구항 1

복수의 화합물 반도체층을 포함하는 발광 구조물;

상기 발광 구조물 아래의 외측 둘레를 따라 형성된 복수의 아이솔레이션층;

상기 복수의 아이솔레이션층 사이에 형성된 금속층; 및

상기 발광 구조물의 아래에 형성된 제2전극층을 포함하는 반도체 발광소자.

#### 청구항 2

제 1항에 있어서,

상기 복수의 아이솔레이션층은 내측이 상기 발광 구조물 아래의 외측 둘레와 상기 금속층 사이에 형성되며, 외측이 상기 발광 구조물의 아래 외측에 노출된 제1아이솔레이션층; 및 상기 금속층 아래에 형성된 제2아이솔레이션층을 포함하는 반도체 발광소자.

### 청구항 3

제 1항에 있어서,

상기 복수의 아이솔레이션층은 ITO, IZO, IZTO, IAZO, IGZO, IGTO, AZO, ATO, SiO<sub>2</sub>, SiO<sub>x</sub>, SiO<sub>x</sub>N<sub>y</sub>, Si<sub>3</sub>N<sub>4</sub>, Al<sub>2</sub>O<sub>3</sub>, TiO<sub>2</sub> 중 적어도 하나를 포함하는 반도체 발광소자.

#### 청구항 4

제 1항 또는 제3항에 있어서,

상기 금속층은 Ag, Ni, Al, Rh, Pd, Ir, Ru, Mg, Zn, Pt, Au, Hf 및 그 조합으로 구성된 그룹으로부터 선택된 물질로 이루어진 적어도 하나의 층을 포함하는 반도체 발광소자.

#### 청구항 5

제 1항에 있어서,

상기 제2전극층 및 상기 복수의 아이솔레이션층의 아래에 형성된 전도성 지지부재를 포함하는 반도체 발광소자.

## 청구항 6

제 1항에 있어서,

상기 발광 구조물은 3족-5족 화합물 반도체를 포함하며,

제1전극이 형성된 제1도전형 반도체층; 상기 제1도전형 반도체층 아래에 활성층; 상기 활성층과 상기 제2전극층 사이 및 상기 복수의 아이솔레이션층과 상기 제2전극층 사이에 제2도전형 반도체층을 포함하는 반도체 발광소자.

## 청구항 7

제 1항에 있어서, 상기 복수의 아이솔레이션층 중 적어도 하나는 전도성 투과물질을 포함하는 반도체 발광소자.

## 청구항 8

제 1항에 있어서, 상기 복수의 아이솔레이션층 중 적어도 하나는 절연 물질을 포함하는 반도체 발광소자.

## 청구항 9

제 2항에 있어서, 상기 제1아이솔레이션층과 상기 제2아이솔레이션층은 서로 다른 물질로 형성되는 반도체 발광소자.

## 청구항 10

제1 도전형 반도체층, 활성층, 제2 도전형 반도체층을 포함하는 발광 구조물;

상기 발광 구조물 아래의 외측 둘레를 따라 배치된 제1 아이솔레이션층;

상기 제1 아이솔레이션층 아래에 배치된 금속층;

상기 금속층 아래에 배치된 제2 아이솔레이션층; 및

상기 제2 도전형 반도체층의 아래에 배치된 제2 전극층을 포함하는 반도체 발광소자.

### 청구항 11

제 10항에 있어서, 상기 제1 아이솔레이션층의 내측이 상기 금속층의 측면 및 상기 제2 도전형 반도체층의 하부 에 접촉되어 배치되고, 상기 제1 아이솔레이션층의 외측이 상기 제2 도전형 반도체층의 하부 외측으로 연장되어 형성된 반도체 발광소자.

### 청구항 12

복수의 화합물 반도체층으로 발광 구조물을 형성하는 단계;

상기 발광 구조물의 외측 둘레를 따라 제1아이솔레이션층을 형성하는 단계;

상기 제1 아이솔레이션층 위에 금속층을 형성하는 단계;

상기 금속층 위에 제2아이솔레이션층을 형성하는 단계; 및

상기 발광 구조물 및 상기 제2아이솔레이션층 위에 제2전극층을 형성하는 단계를 포함하는 반도체 발광소자 제조방법.

## 청구항 13

제12항에 있어서,

에칭하여 상기 발광 구조물의 외측 둘레를 제거하여 상기 제1아이솔레이션층의 외측을 노출시켜 주는 단계;

상기 발광 구조물 아래에 제1전극을 형성하는 단계를 포함하는 반도체 발광소자 제조방법.

#### 청구항 14

제 12항에 있어서,

기판 위에 상기 발광 구조물이 형성되며,

상기 제2전극층 위에 전도성 지지부재를 형성하고, 상기 기판을 제거하는 반도체 발광소자 제조방법.

## 청구항 15

제 12항에 있어서,

상기 제1 및 제2아이솔레이션층은 광 투과 특성을 갖는 전도성 물질 또는 절연 물질을 포함하는 반도체 발광소 자 제조방법.

## 청구항 16

제 12항에 있어서,

상기 금속층은 반사 금속 재료를 포함하는 반도체 발광소자 제조방법.

## 명 세 서

## 발명의 상세한 설명

## 기술분야

[0001] 실시 예는 반도체 발광소자 및 그 제조방법에 관한 것이다.

## 배경기술

- [0002] Ⅲ-V족 질화물 반도체(group Ⅲ-V nitride semiconductor)는 물리적, 화학적 특성으로 인해 발광 다이오드 (LED) 또는 레이저 다이오드(LD) 등의 발광 소자의 핵심 소재로 각광을 받고 있다. Ⅲ-V족 질화물 반도체는 통상 In<sub>x</sub>Al<sub>y</sub>Ga<sub>1-x-y</sub>N (0≤x≤1, 0≤y≤1, 0≤x+y≤1)의 조성식을 갖는 반도체 물질로 이루어져 있다.

- [0003] 발광 다이오드(Light Emitting Diode : LED)는 화합물 반도체의 특성을 이용하여 전기를 적외선 또는 빛으로 변환시켜서 신호를 주고 받거나, 광원으로 사용되는 반도체 소자의 일종이다.

- [0004] 이러한 질화물 반도체 재료를 이용한 LED 혹은 LD는 광을 얻기 위한 발광 소자에 많이 사용되고 있으며, 핸드 폰의 키패드 발광부, 전광판, 조명 장치 등 각종 제품의 광원으로 응용되고 있다.

## 발명의 내용

## 해결 하고자하는 과제

- [0005] 실시 예는 발광 구조물의 측 방향에서 손실되는 광 효율을 개선시켜 줄 수 있는 반도체 발광소자 및 그 제조방법을 제공한다.

- [0006] 실시 예는 아이솔레이션층 사이에 금속층을 삽입함으로써, 박리, 깨짐 현상을 최소화시킬 수 있는 반도체 발광소자 및 그 제조방법을 제공한다.

### 과제 해결수단

- [0007] 실시 예에 따른 반도체 발광소자는 복수의 화합물 반도체층을 포함하는 발광 구조물; 상기 발광 구조물 아래의 외측 둘레를 따라 형성된 복수의 아이솔레이션층; 상기 복수의 아이솔레이션층 사이에 형성된 금속층; 상기 발광 구조물의 아래에 형성된 제2전극층을 포함한다.

- [0008] 실시 예에 따른 반도체 발광소자 제조방법은, 복수의 화합물 반도체층으로 발광 구조물을 형성하는 단계; 상기 발광 구조물의 외측 둘레를 따라 제1아이솔레이션층을 형성하는 단계; 상기 제1 아이솔레이션층 위에 금속층을 형성하는 단계; 상기 금속층 위에 제2아이솔레이션층을 형성하는 단계; 상기 발광 구조물 및 상기 제2아이솔레이션층 위에 제2전극층을 형성하는 단계를 포함한다.

## 直 과

- [0009] 실시 예는 발광 구조물과 다른 층과의 접착력을 개선시켜 줄 수 있는 효과가 있다.

- [0010] 실시 예는 반도체 발광소자의 광 추출 효율을 개선시키고, 박리 현상을 개선시켜 줄 수 있다.

## 발명의 실시를 위한 구체적인 내용

- [0011] 이하, 첨부된 도면을 참조하여 실시 예를 설명하면 다음과 같다. 실시 예를 설명함에 있어서, 각 층의 위 또는 아래에 대한 설명은 도면을 기준으로 설명하며, 각 층의 두께는 일 예이며, 도면의 두께로 한정하지는 않는다. 또한 실시 예의 설명에 있어서, 각 층(막), 영역, 패턴 또는 구조물들이 기판, 각 층(막), 영역, 패드 또는 패턴들의 "위(on)"에 또는 "아래(under)"에 형성되는 것으로 기재되는 경우에 있어, "위(on)"와 "아래(under)"는 "directly"와 "indirectly"의 의미를 모두 포함한다.

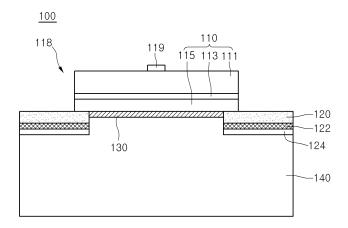

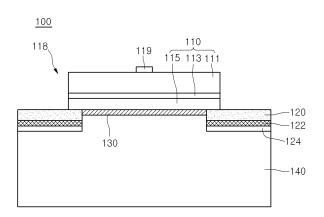

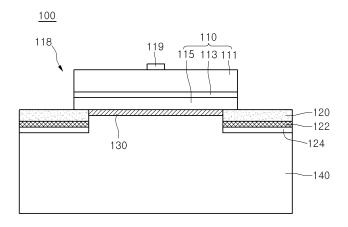

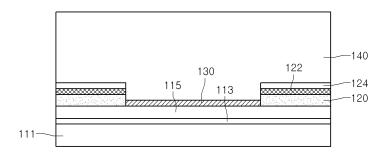

- [0012] 도 1은 실시 예에 따른 반도체 발광소자를 나타낸 단면도이다.

- [0013] 도 1을 참조하면, 반도체 발광소자(100)는 발광 구조물(110), 제1아이솔레이션층(120), 금속층(122), 제2아이솔레이션층(124), 제2전극층(130), 전도성 지지부재(140)를 포함한다.

- [0014] 상기 발광 구조물(110)은 제 1도전형 반도체층(111), 활성층(113), 제 2도전형 반도체층(115)을 포함하며, 상기 제 1 및 제2도전형 반도체층(111,115) 사이에 활성층(113)이 개재된 구성이다.

- [0015] 상기 제 1도전형 반도체층(111)은 제1도전형 도펀트가 도핑된 적어도 하나의 반도체층으로 구현될 수 있으며, 상기 반도체층은 3족-5족 화합물 반도체이며 예컨대, GaN, InN, AIN, InGaN, AlGaN, InAlGaN, AlInN 중 적어도 하나를 포함한다. 상기 제1도전형 반도체층(111)은 N형 반도체층인 경우, 상기 제1도전형 도펀트는 N형 도펀트

가 되며, 상기 N형 도펀트는 Si, Ge, Sn, Se, Te 등을 포함한다.

- [0016] 상기 제1도전형 반도체충(111)의 상면에는 소정 패턴의 제1전극(119)이 형성된다. 상기 제1도전형 반도체충 (111)의 상면 일부 또는 전 영역에는 요철 형태의 러프니스가 형성될 수 있다.

- [0017] 상기 제 1도전형 반도체층(111) 아래에는 상기 활성층(113)이 형성된다. 상기 활성층(113)은 단일 또는 다중 양자우물(MQW) 구조로 형성된다. 상기 활성층(113)은 3족-5족 화합물 반도체 재료를 이용하여 우물층과 장벽층의 주기를 형성되며, 예컨대, InGaN 우물층/GaN 장벽층의 주기 또는 AlGaN 우물층/GaN 장벽층의 주기를 포함할 수있다.

- [0018] 상기 활성층(113)은 발광시키는 빛의 파장에 따른 밴드 캡 에너지를 갖는 재료로 선택되며, 예를 들면, 파장이 460~470mm의 청색 발광의 경우, InGaN 우물층/GaN 장벽층을 한 주기로 하여, 단일 또는 다중 양자 우물 구조로 형성될 수 있다. 상기 활성층(113)은 청색 파장의 광, 레드 파장의 광, 녹색 파장의 광 등의 유색 광을 발광하는 재료를 포함할 수 있다.

- [0019] 상기 활성층(113)의 위 또는/및 아래에는 도전형 클래드층이 형성될 수 있으며, 상기 도전형 클래드층은 AlGaN 층을 포함할 수 있다.

- [0020] 상기 활성층(113) 아래에는 상기 제2도전형 반도체층(115)이 형성될 수 있다. 상기 제 2도전형 반도체층(115)은 제2도전형 도펀트가 도핑된 적어도 하나의 반도체층으로 구현될 수 있으며, 상기 반도체층은 3족-5족 화합물 반도체이며 예컨대, GaN, InN, AlN, InGaN, AlGaN, InAlGaN, AlInN 중 적어도 하나로 형성될 수 있다. 상기 제2도전형 반도체층(115)은 P형 반도체층인 경우, 상기 제2도전형 도펀트는 P형 도펀트가 되며, 상기 P형 도펀트는 Mg, Zn, Ca, Sr, Ba 등을 포함한다.

- [0021] 상기 제 2도전형 반도체층(115) 위에는 제 3도전형 반도체층(미도시)을 형성할 수 있다. 상기 제 1도전형 반도체층(111)이 P형 반도체층인 경우, 상기 제 2도전형 반도체층(115)이 N형 반도체층으로 구현될 수 있다. 상기 제 3도전형 반도체층은 제1도전형 도펀트가 도핑된 반도체층으로 구현될 수 있다. 상기 발광 구조물(110)은 N-P 접합 구조, P-N 접합 구조, N-P-N 접합 구조, P-N-P 접합 구조 중 어느 하나로 형성될 수 있다.

- [0022] 상기 제 2도전형 반도체층(115)의 아래에는 제1아이솔레이션층(120) 및 제2전극층(130)이 형성된다.

- [0023] 상기 제1아이솔레이션층(120)의 내측은 상기 제2도전형 반도체층(115)의 아래 외측 둘레를 따라 형성되며, 외측은 상기 제2도전형 반도체층(115)의 아래에서 외측으로 연장되며 상기 발광 구조물(110)의 외측 영역(118)을 따라 노출된 구조이다.

- [0024] 상기 제1아이솔레이션층(120)은 광 투과성 특성을 갖는 전도성 물질 또는 절연 물질이 틀 형태로 상기 제2도전 형 반도체층(115) 아래를 따라 형성된다.

- [0025] 상기 제1아이솔레이션층(120)이 전도성 물질 예컨대, ITO, IZO, IZTO, IAZO, IGZO, IGTO, AZO, ATO 등과 같은 물질로 형성될 수 있다. 상기 제1아이솔레이션층(120)이 전도성 물질로 형성된 경우, 메사 에칭 등의 과정에서 조사되는 레이저가 투과됨으로써, 상기 발광 구조물(110)의 외측에 전기적인 영향을 주지 않게 되므로, 전기적인 특성이 개선될 수 있어, 발광 효율이 개선될 수 있다.

- [0026] 상기 제1아이솔레이션층(120)이 절연 물질 예컨대, SiO<sub>2</sub>, SiO<sub>x</sub>, SiO<sub>x</sub>N<sub>y</sub>, Si<sub>3</sub>N<sub>4</sub>, Al<sub>2</sub>O<sub>3</sub>, TiO<sub>2</sub>등과 같은 물질로 형성 될 수 있다. 상기 제1아이솔레이션층(120)이 절연물질로 형성된 경우, 상기 전도성 지지부재(140)와 상기 발광 구조물(110) 사이의 간격을 이격시켜 줄 수 있다. 또한 상기 제1아이솔레이션층(120)은 상기 제2도전형 반도체 층(115)과의 접착력을 개선시켜 줄 수 있다.

- [0027] 상기 제1아이솔레이션층(120)의 아래에는 금속층(122)이 형성되며, 상기 금속층(122)은 반사율이 높은 금속 예 컨대, Ag, Ni, Al, Rh, Pd, Ir, Ru, Mg, Zn, Pt, Au, Hf 및 그 조합으로 구성된 그룹으로부터 선택된 물질로 이루어진 적어도 하나의 층을 포함하는 구조로 형성될 수 있다.

- [0028] 상기 금속층(122)의 아래에는 제2아이솔레이션층(124)이 형성되며, 상기 제2아이솔레이션층(124)은 ITO, IZO, IZTO, IAZO, IGZO, IGTO, AZO, ATO, SiO<sub>2</sub>, SiO<sub>x</sub>, SiO<sub>x</sub>N<sub>y</sub>, Si<sub>3</sub>N<sub>4</sub>, Al<sub>2</sub>O<sub>3</sub>, TiO<sub>2</sub> 중 적어도 하나를 포함한다. 상기 제1아이솔레이션층(122) 및 제2아이솔레이션층(124)은 서로 동일한 물질 또는 서로 다른 물질로 형성될 수 있다.

- [0029] 상기 발광 구조물(110)의 아래 외측 둘레에 상기 제1아이솔레이션층(120), 금속층(122) 및 제2아이솔레이션층

(124)은 하나의 장비(insitu)의 공정을 통해 형성될 수 있다. 또한 상기 복수개의 아이솔레이션층(120,124) 사이에 금속층(122)이 삽입됨으로써, 층 사이의 접착력 및 박리 현상을 최소화할 수 있다.

- [0030] 상기 발광 구조물(110)의 아래 즉, 내측 아래에는 제2전극층(130)이 형성되며, 상기 제2전극층(130)은 Ag, Ni, Al, Rh, Pd, Ir, Ru, Mg, Zn, Pt, Au, Hf 및 이들의 조합으로 구성된 그룹으로부터 적어도 한 물질로, 적어도 하나의 층으로 형성될 수 있다.

- [0031] 상기 제2전극층(130)은 상기 금속층(122)와 일체로 형성되지 않기 때문에, 열 팽창에 따른 간섭이 발생되지 않 게 된다.

- [0032] 상기 제2전극층(130)과 상기 제2도전형 반도체층(115) 사이에는 소정 패턴의 오믹층(미도시)이 형성될 수 있다. 상기 오믹층의 패턴 형태는 매트릭스 형태, 십자형, 다각형, 원형 등의 형상으로 형성될 수 있으며, 그 재질은 ITO( indium tin oxide), IZO(indium zinc oxide), IZTO( indium zinc tin oxide), IAZO( indium aluminum zinc oxide), IGZO( indium gallium zinc oxide), IGTO( indium gallium tin oxide), AZO( aluminium zinc oxide), ATO( antimony tin oxide) 중에서 선택적으로 형성될 수 있다.

- [0033] 상기 제2전극층(130)의 아래에는 전도성 지지부재(140)가 형성된다. 상기 전도성 지지부재(140)는 구리, 금, 캐리어 웨이퍼(예: Si, Ge, GaAs, ZnO, SiC 등) 등과 같은 물질로 형성될 수 있다. 상기 제2전극층(130)의 두께 또는 강도에 따라 상기 전도성 지지부재(140)은 형성되지 않을 수 있거나, 두 층이 단일 층으로 형성될 수 있다.

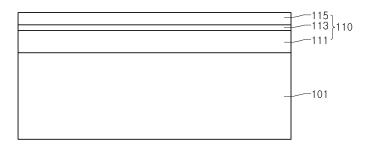

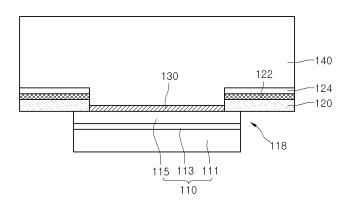

- [0034] 도 2내지 도 9는 실시 예에 따른 발광 소자 제조 과정을 나타낸 도면이다.

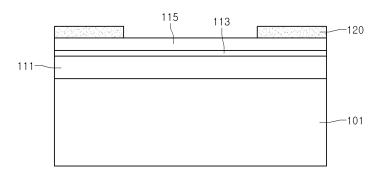

- [0035] 도 2를 참조하면, 기판(101) 위에는 제 1도전형 반도체층(111)이 형성되고, 상기 제 1도전형 반도체층(111) 위에는 활성층(113)이 형성되며, 상기 활성층(113) 위에는 제 2도전형 반도체층(115)이 형성된다.

- [0036] 상기 기판(101)에는 사파이어 기판(Al<sub>2</sub>O<sub>3</sub>), GaN, SiC, ZnO, Si, GaP, InP, 그리고 GaAs 등으로 이루어진 군에서 선택될 수 있다. 상기 기판(101) 위에는 소정의 요철 패턴이 형성될 수 있다. 상기 기판(101) 위에는 다른 반도 체층 예컨대, 버퍼층 및/또는 언도프드 반도체층이 형성될 수 있으며, 이에 대해 한정하지는 않는다.

- [0037] 상기 제 1도전형 반도체층(113)은 N형 반도체층인 경우, 제 2도전형 반도체층(115)은 P형 반도체층으로 구현될수 있으며, 또는 그 역의 구조로 구현할 수도 있다. 상기 기판(101)과 상기 제1도전형 반도체층(113) 사이에는다른 반도체층 예컨데, 버퍼층 또는/및 언도프드 반도체층이 형성될 수도 있으며, 박막 성장 후 분리 또는 제거될 수도 있다.

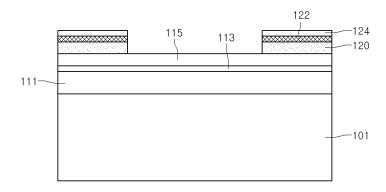

- [0038] 도 3을 참조하면, 상기 제2도전형 반도체층(115) 위의 외측 둘레에는 제1아이솔레이션층(120)이 형성된다. 상기 제1아이솔레이션층(120)은 포토 레지스트 패턴을 형성한 후 상기 제2도전형 반도체층(115) 위의 외측 둘레에 틀형태 예컨대, 개별 칩의 제 2도전형 반도체층(115)의 테두리 영역에 틀형태로 배치될 수 있다.

- [0039] 상기 제1아이솔레이션층(120)은 ITO, IZO, IZTO, IAZO, IGZO, IGTO, AZO, ATO, SiO<sub>2</sub>, SiO<sub>x</sub>, SiO<sub>x</sub>N<sub>y</sub>, Si<sub>3</sub>N<sub>4</sub>, Al<sub>2</sub>O<sub>3</sub> \_ TiO<sub>2</sub> 등의 물질로 형성될 수 있다.

- [0040] 도 3 및 도 4를 참조하면, 상기 제1아이솔레이션층(120) 위에는 금속층(122)이 형성되며, 상기 금속층(122) 위에는 제2아이솔레이션층(124)이 형성된다.

- [0041] 여기서, 상기 제1아이솔레이션층(120), 금속층(122), 제2아이솔레이션층(124)은 순차적으로 적층되는 데, 이 경우 스퍼터링 장비를 이용하여 insitu 공정으로 상기 층(120,122,124)를 순차적으로 형성시켜 줄 수 있으며, 이들 층(120,122,124)의 두께는 수 um 또는 수 십 um 이하로 형성될 수 있다.

- [0042] 상기 금속층(122)은 Ag, Ni, Al, Rh, Pd, Ir, Ru, Mg, Zn, Pt, Au, Hf 및 그 조합으로 구성된 그룹으로부터 선택된 물질로 이루어진 적어도 하나의 층으로 형성될 수 있다.

- [0043] 상기 금속층(122)은 복수개의 아이솔레이션층(120,124) 사이에 형성됨으로써, 상기 제1 및 제2아이솔레이션층 (120,124)은 상기 금속층(122)의 열 팽창을 줄여줄 수 있다. 이에 따라 칩 분리 공정에서 칩의 외측 둘레가 들 뜨는 문제를 해결할 수 있다. 또한 상기 제1아이솔레이션층(120)을 형성하면서 금속층(122)를 동시에 형성시켜 줌으로써, 접착력을 개선시켜 줄 수 있다.

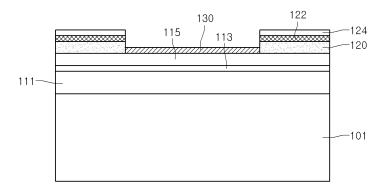

- [0044] 도 5 및 도 6를 참조하면, 상기 제2도전형 반도체층(115) 위의 내측에는 제2전극층(130)이 형성되며, 상기 제2

전극층(130) 위에는 전도성 지지부재(140)이 형성된다.

- [0045] 상기 제2전극층(130) 및 상기 전도성 지지부재(140)은 전도층으로서 제2전극층으로 기능하게 된다. 상기 제 2도 전형 반도체층(115)과 상기 제2전극층(130) 사이에는 소정 패턴의 오믹층(미도시)이 형성될 수 있다.

- [0046] 상기 제2전극층(130)은 Ag, Ni, Al, Rh, Pd, Ir, Ru, Mg, Zn, Pt, Au, Hf 및 그 조합으로 구성된 그룹으로부터 선택된 물질로 이루어진 적어도 하나의 층을 포함하는 구조로 형성될 수 있다. 상기 전도성 지지부재(140)은 구리, 금, 캐리어 웨이퍼(예: Si, Ge, GaAs, ZnO, SiC 등) 등과 같은 물질로 소정 두께로 형성될 수 있다.

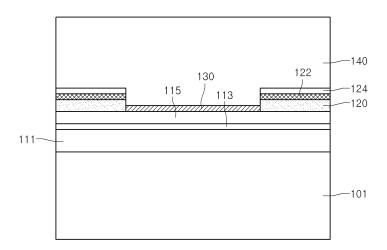

- [0047] 도 6 및 도 7을 참조하면, 상기 제 1도전형 반도체층(111) 아래에 형성된 기판(101)을 레이저 리프트 오프(LLO : Laser Lift Off) 과정으로 제거하게 된다. 상기 기판(101)의 제거 과정은 상기 기판(101)에 대해 일정 영역의 과장을 가지는 레이저를 조사하면, 상기 기판(101)과 제 1도전형 반도체층(111) 사이의 경계면에서 열 에너지가 집중되어, 상기 기판(101)이 분리된다. 상기 기판(101)은 다른 방식으로 분리할 수 있는 데, 예컨대 상기 기판(101)과 상기 제1도전형 반도체층(111) 사이에 다른 반도체층(예: 버퍼층)이 존재할 경우, 습식 식각액을 상기 버퍼층 영역에 주입하여 상기 버퍼층을 제거함으로써, 상기 기판(101)을 분리할 수 있다.

- [0048] 그리고 상기 기판(101)이 제거된 제 1도전형 반도체층(111)의 하면에 대해 ICP/RIE(Inductively coupled Plasma/Reactive Ion Etching) 방식으로 연마하는 공정을 수행할 수 있다.

- [0049] 도 7 및 도 8을 참조하면, 상기 기판이 제거되면, 메사 에칭을 수행하여 칩 경계 영역의 상기 제1아이솔레이션 충(120)의 외측 하부를 노출시켜 준다. 여기서, 상기 에칭 방식은 건식 또는/및 습식 에칭 방식을 이용할 수 있다.

- [0050] 이때 상기 제1 및 제2아이솔레이션층(120,124)은 그 내부에 형성된 상기 금속층(122)의 열 팽창을 줄여줄 수 있다. 이에 따라 칩 분리 공정에서 칩의 외측 둘레가 들뜨는 문제를 해결할 수 있다. 또한 상기 제1아이솔레이션 층(120)을 형성하면서 상기 금속층(122) 및 제2아이솔레이션층(124)을 형성시켜 줌으로써, 층들 사이의 접착력을 개선시켜 줄 수 있다.

- [0051] 상기 제1아이솔레이션층(120)은 전도 물질인 경우, 메사 에칭 방식에 의해 반도체 재료가 다른 층에 흘러내리는 것을 방지하여, 전기적인 쇼트를 방지할 수 있다. 즉, 공정의 안정성을 개선시켜 줄 수 있다. 또한 제1아이솔레이션층(120)의 오믹 특성에 의해 발광 효율이 개선될 수 있으며, 상기 금속층(122)에 의해 반사 효율이 개선될수 있다.

- [0052] 상기 제1아이솔레이션층(120)이 절연 물질인 경우, 상기 전도성 지지부재(140)와 제2도전형 반도체층(115) 사이의 간격을 공간적으로 이격시켜 줄 수 있다.

- [0053] 도 8 및 도 9를 참조하면, 상기 제 1도전형 반도체층(111) 아래에는 소정 패턴의 제 1전극(119)이 형성될 수 있다. 상기 제1전극(119)의 형성 전 또는 형성 후 개별 칩으로 분리하는 공정을 수행하게 된다.

- [0054] 반도체 발광소자(100)는 상기 발광 구조물(110)의 외측 영역(118)을 따라 상기 제1아이솔레이션층(120)이 노출되고, 상기 제1아이솔레이션층(120)과 제2아이솔레이션층(124) 사이에 금속층(122)를 형성시켜 줌으로써, 박리현상을 줄이고, 반사 효율을 개선시켜 줄 수 있다.

- [0055] 이상에서 본 발명에 대하여 그 바람직한 실시 예를 중심으로 설명하였으나 이는 단지 예시일 뿐 본 발명을 한정하는 것이 아니며, 본 발명이 속하는 분야의 통상의 지식을 가진 자라면 본 발명의 본질적인 특성을 벗어나지 않는 범위에서 이상에 예시되지 않은 여러 가지의 변형과 응용이 가능함을 알 수 있을 것이다. 예를 들어, 본 발명의 실시 예에 구체적으로 나타난 각 구성 요소는 변형하여 실시할 수 있는 것이다. 그리고 이러한 변형과 응용에 관계된 차이점들은 첨부된 청구 범위에서 규정하는 본 발명의 범위에 포함되는 것으로 해석되어야 할 것이다.

## 도면의 간단한 설명

- [0056] 도 1은 실시 예에 따른 반도체 발광소자를 나타낸 측 단면도.

- [0057] 도 2내지 도 9는 실시 예에 따른 반도체 발광소자 제조과정을 나타낸 도면.

# 도면

# 도면1

## 도면2

## 도면3

# 도면4

## 도면5

# 도면6

# 도면7

## 도면8

## 도면9