# (19) 国家知识产权局

# (12) 发明专利

(10) 授权公告号 CN 114296181 B (45) 授权公告日 2024.04.12

(21)申请号 202210013185.4

(22)申请日 2022.01.07

(65) 同一申请的已公布的文献号 申请公布号 CN 114296181 A

(43) 申请公布日 2022.04.08

(73) 专利权人 吉林大学 地址 130012 吉林省长春市长春高新技术 产业开发区前进大街2699号

(72) 发明人 孙小强 李鹏飞 范晓健 刘庭瑜 刘崧岳 张大明

(74) **专利代理机构** 长春吉大专利代理有限责任 公司 22201

专利代理师 刘世纯 王恩远

(51) Int.CI.

GO2B 6/12 (2006.01)

#### (56) 对比文件

CN 108463752 A,2018.08.28

CN 110568560 A, 2019.12.13

CN 112987183 A, 2021.06.18

CN 113238324 A.2021.08.10

US 2005084200 A1,2005.04.21

US 2020241209 A1,2020.07.30

梁磊等.聚合物/Si02混合波导2X2热光开关的制备与测试.《光电子 激光》.2014,第25卷(第4期),全文.

审查员 田莉

权利要求书3页 说明书6页 附图6页

#### (54) 发明名称

一种基于硅基光波导的双层开关阵列

#### (57) 摘要

一种基于硅基光波导的双层开关阵列,属于集成光电子学技术领域。本发明器件集成在双层硅结构晶圆上,由电光开关阵列、层间耦合器以及光波导组成,电光开关阵列由第一级电光开关阵列(TS21~TS24)、第三级电光开关阵列(BS31~BS34)、第四级电光开关阵列(BTS41~BS44)和第五级电光开关阵列(BS51~BS54)组成,每级电光开关阵列内有4个电光开关单元;电光开关单元采用的是马赫-曾德尔干涉仪结构,由两个双端口3-dB分光器和两条相移臂组成,3-dB分光器采用多模干涉器结构,为双臂推挽型电光调制。本发明可以显著减小单层器件的面积,提高集成度。

第一级电光开关阵列TS11~TS14共有8个输入端口和8个输出端口,其中4个输入端口分别与作为双层开关阵列4个输入端口 $I_1$ 、 $I_3$ 、 $I_5$ 、 $I_7$ 的光波导相连接,其余4个输入端口各连接一个由器件层2向器件层1进行光信号传输的层间耦合器C1、C2、C3、C4,4个层间耦合器C1、C2、C3、C4又分别与4个位于器件层2作为双层开关阵列输入端口 $I_2$ 、 $I_4$ 、 $I_6$ 、 $I_8$ 的光波导相连接;第一级电光开关阵列的8个输出端口各自通过一条光波导分别与第二级电光开关阵列的8个输入端口相连接;

第二级电光开关阵列TS21~TS24共有8个输入端口和8个输出端口,8个输入端口各自通过一条光波导分别与第一级电光开关阵列的8个输出端口相连接,即TS11的第一输出端口与TS21的第一输入端口相连,TS11的第二输出端口与TS23的第一输入端口相连;TS12的第一输出端口与TS21的第二输入端口相连,TS12的第二输出端口与TS23的第二输入端口相连;TS13的第一输出端口与TS22的第一输入端口相连,TS13的第二输出端口与TS24的第一输入端口相连;TS14的第一输出端口与TS22的第二输入端口相连,TS14的第二输出端口与TS24的第二输入端口相连;第二级电光开关阵列的8个输出端口各连接一个由器件层1向器件层2进行光信号传输的层间耦合器C9~C16,这8个层间耦合器分别与8个位于器件层2、弯曲半径为20 μm、弯曲度数为180°的弯曲光波导的一端相连接;

第三级电光开关阵列BS31~BS34共有8个输入端口和8个输出端口,8个输入端口各自通过一条光波导分别与8个弯曲光波导的另一端相连接,即TS21的第一输出端口通过层间耦合器C9与BS31的第一输入端口相连接,TS21的第二输出端口通过层间耦合器C10与BS32的第一输入端口相连接;TS22的第一输出端口通过层间耦合器C11与BS31的第二输入端口相连接,TS23的第二输出端口通过层间耦合器C12与BS32的第二输入端口相连接;TS23的第一输出端口通过层间耦合器C13与BS33的第一输入端口相连接,TS23的第二输出端口通过层间耦合器C15与BS33的第二输入端口相连接,TS24的第一输出端口通过层间耦合器C15与BS33的第二输入端口相连接,TS24的第二输出端口通过层间耦合器C16与BS34的第二输入端口相连接;第三级电光开关阵列的8个输出端口各自通过一条光波导分别与第四级电光开关单元的8个输入端口相连接;

第四级电光开关阵列BS41~BS44共有8个输入端口和8个输出端口,8个输入端口各自通过一条光波导分别与第三级电光开关单元的8个输出端口相连接,即BS31的第一输出端口与BS41的第一输入端口相连接,BS31的第二输出端口与BS42的第一输入端口相连接;BS32的第二输出端口与BS42的第二输入端口相连接;BS33的第一输出端口与BS43的第一输入端口相连接,BS33的第二输出端口与

BS44的第一输入端口相连接;BS34的第一输出端口与BS43的第二输入端口相连接,BS34的第二输出端口与BS44的第二输入端口相连接;第四级电光开关阵列的8个输出端口各自通过一条光波导分别与第五级电光开关单元的8个输入端口相连接;

第五级电光开关阵列BS51~BS54共有8个输入端口和8个输出端口,8个输入端口各自通过一条光波导分别与第四级电光开关单元的8个输出端口相连接,即BS41的第一输出端口与BS51的第一输入端口相连接,BS41的第二输出端口与BS52的第一输入端口相连接;BS42的第一输入端口相连接;BS43的第一输入端口相连接;BS43的第一输出端口与BS51的第二输入端口相连接,BS43的第二输出端口与BS52的第二输入端口相连接;BS44的第一输出端口与BS53的第二输入端口相连接,BS44的第二输出端口与BS54的第二输入端口相连接;BS44的第二输出端口与BS54的第二输入端口相连接;第五级电光开关阵列的8个输出端口中,4个输出端口分别与4个位于器件层2作为阵列输出端口0<sub>1</sub>、0<sub>3</sub>、0<sub>5</sub>、0<sub>7</sub>的光波导相连接,其余4个输出端口各连接一个由器件层2向器件层1进行光信号传输的层间耦合器C5、C6、C7、C8、4个层间耦合器C5、C6、C7、C8又各自与4个位于器件层1作为阵列输出端口0<sub>2</sub>、0<sub>4</sub>、0<sub>6</sub>、0<sub>8</sub>的光波导相连接;

该双层开关阵列基于双层硅结构晶圆制备,即在500 $\mu$ m厚的Si衬底上依次为3 $\mu$ m厚的Si $0_2$ 下包层、220 nm厚的Si器件层2、150nm 厚的Si $0_2$ 中间层、220 nm厚的Si器件层1和3 $\mu$ m厚的Si $0_2$ 上包层;

其中,电光开关单元是由第一2×2多模干涉器MMI-1、相互平行的相移臂1与相移臂2、第二2×2 多模干涉器MMI-2三部分顺次级联形成的对称MZI结构,MMI-1、MMI-2结构尺寸完全一致,其主体结构为脊型波导,脊长度L\_MMI = 29.2  $\mu$ m,脊宽度W\_MMI = 5  $\mu$ m;MMI-1和MMI-2均带有两条输入波导和两条输出波导,输入波导和输出波导均为脊型波导结构,宽度相同,均为0.5  $\mu$ m;在输入波导、输出波导与多模干涉器的MMI主体结构间引入了长10  $\mu$ m、宽度0.5 ~1.2  $\mu$ m间线性变化的过渡波导,过渡波导为脊型波导结构,靠近MMI主体结构的过渡波导的宽度较宽为1.2 $\mu$ m,远离MMI主体结构的过渡波导的宽度较宽为1.2 $\mu$ m,远离MMI主体结构的过渡波导的宽度较宽为0.5  $\mu$ m,过渡波导中心距MMI主体结构中心的距离为offset = 0.86  $\mu$ m;两个过渡波导的脊结构均与MMI主体的脊波导结构连接;MMI-1、MMI-2、相移臂1和相移臂2位于平行于衬底层的同一器件层内,MMI-1的两个输入波导分别作为电光开关单元的第一输入端口 $I_1$ 和第二输入端口 $I_2$ ,MMI-2的两个输出波导分别作为电光开关的第一输出端口 $I_2$ ,MMI-2的两个输出波导分别作为电光开关的第一输出端口 $I_2$ ,MMI-2的两个输出波导分别作为电光开关的第一输出端口 $I_3$ 和第二输出端口 $I_2$ 。

- 2.如权利要求1所述的一种基于硅基光波导的双层开关阵列,其特征在于:光波导为脊型结构,其中脊高150 nm,平板层高度为70 nm,其上、下包层材料均为Si0<sub>2</sub>,衬底材料是硅;对于处于器件层2 的光波导,其下包层为厚度3 $\mu$ m的Si0<sub>2</sub>下包层,上包层为厚度150nm的Si0<sub>2</sub>中间层,衬底为厚度500  $\mu$ m的硅衬底;对于处于器件层1的光波导,其下包层为厚度150nm的Si0<sub>2</sub>中间层,上包层为厚度3 $\mu$ m的Si0<sub>2</sub>上包层,衬底是220nm厚的器件层2;光波导的宽度为0.5 $\mu$ m。

- 3.如权利要求1所述的一种基于硅基光波导的双层开关阵列,其特征在于:电光开关单元采用基于等离子体色散效应的电光调制方式,相移臂为脊型波导结构,其中脊高150 nm,平板层高度为70 nm;脊连同其两侧的部分平板层为n型背景掺杂区域,被n型背景掺杂区域分开的平板层分别为p型重掺杂区域和n型重掺杂区域;p型重掺杂区域的宽度为4μm,掺杂浓度为2×10<sup>20</sup>/cm<sup>-3</sup>;n型重掺杂区域的宽度为4μm,掺杂浓度为5×10<sup>20</sup>/cm<sup>-3</sup>;n型背景掺杂区

域的宽度为 $1.5\mu m$ ,掺杂浓度为 $5\times10^{17}/cm^{-3}$ ;上、下包层材料均为 $SiO_2$ ,衬底材料是硅;在  $SiO_2$ 上包层中设置有宽度为 $0.5\mu m$ 的通孔1和通孔2,在通孔1和通孔2中填充铝;p型重掺杂区域和n型重掺杂区域分别通过通孔1和通孔2同位于 $SiO_2$ 上包层之上的宽度为 $3\mu m$ 、厚度 $1\mu$  m的电极1和电极2相连;相移臂的长度为 $400~\mu m$ 。

- 4.如权利要求1所述的一种基于硅基光波导的双层开关阵列,其特征在于:层间耦合器由分别放置在器件层1和器件层2的两个结构相同、宽度渐变方向相反、平行放置的光波导组成;该光波导长度L =  $9.5 \mu m$ ,窄端宽度W = 210nm,粗端宽度Wt = 500nm。

- 5.如权利要求1所述的一种基于硅基光波导的双层开关阵列,其特征在于:当信号由器件层1的输入端口 $I_1$ 、 $I_3$ 、 $I_5$ 、 $I_7$ 输入时,将直接通过第一级电光开关阵列TS11~TS14;当信号由器件层2的输入端口 $I_2$ 、 $I_4$ 、 $I_6$ 、 $I_8$ 输入时,先经过层间耦合器C1~C4到达器件层1,再进入第一级电光开关阵列TS11~TS14;利用开关网络的路由算法确定各开关路径状态,光信号通过第二级电光开关阵列TS21~TS24后,通过层间耦合器C9~C14到达器件层2,经过弯曲波导到达第三级电光开关阵列BS31~BS34,再通过所有开关单元路径选择后到达相应的输出端口;当路径选择使信号由位于器件层2的端口输出时,信号经第五级电光开关阵列BS51~BS54后,由器件层2的输出端口 $0_1$ 、 $0_3$ 、 $0_5$ 、 $0_7$ 输出;当路径选择使信号由器件层1的输出时,信号经第5级开关后,经过层间耦合器C5~C8耦合至器件层1,由位于器件层1的输出端口 $0_2$ 、 $0_4$ 、 $0_6$ 、 $0_8$ 输出。

## 一种基于硅基光波导的双层开关阵列

#### 技术领域

[0001] 本发明属于集成光电子学技术领域,具体涉及一种基于硅基光波导的双层开关阵列,该双层开关阵列在实现多层芯片互联和信号传输等方向有着十分重要的应用和良好的发展前景,在多维光通信和光交换中具有重要作用。

## 背景技术

[0002] 近年来,互联网通信数据容量每年以50~60%的速度迅速增长,人们对带宽的需求也越来越大,海量数据信息的传输和处理面临着越来越高的要求。这也使得电交换的瓶颈愈发凸显出来,即通信带宽和互连密度接近达到极限,网络节点和电交换设备的耗电量接近了许可极限,纳米工艺下电子的量子效应导致器件集成数目达到极限。多核处理器芯片可在一定程度上解决数据传输量增加产生的带宽问题,但芯片间和芯片内核之间的数据传输,对带宽、速率和功耗也提出了很高的要求。相比较电互连的延时,片上光网络中的光信号可以光速传输,且更容易实现高带宽、低功耗、小体积、低串扰等优点。因此光互连是片上互连一个很有吸引力的方案。但无论是远程的光信号交换还是片上的光互连,光开关都是其中关键器件之一。不同类型的光开关中,硅基光波导开关具有体积小、成本低、易于与电芯片集成,以及与CMOS工艺相兼容等特性,在电信网络、数据中心和高性能计算领域具有良好应用前景。但随着信号传输对于器件集成度要求的提高,单层器件排布方式需要较大的尺寸,不利于实现大规模单片集成。因此,采用多层硅波导结构构建三维光开关阵列对减小芯片面积,提高集成度方面具有重要作用。

#### 发明内容

[0003] 本发明的目的在于提供一种能够对光信号在多个芯片间传输进行通断控制的基于硅基光波导的双层开关阵列。

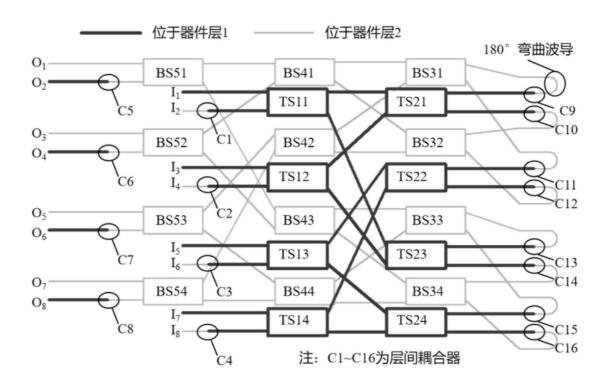

[0004] 本发明所有的器件都集成在双层硅结构晶圆上(双层硅结构晶圆由代工企业提供),未刻蚀的双层硅结构晶圆的横截面结构如图1所示:在500 $\mu$ m厚硅衬底上集成了3 $\mu$ m厚的SiO<sub>2</sub>下包层,SiO<sub>2</sub>下包层向上的结构依次是厚度为220nm的器件层2(Si)、厚度为150nm的SiO<sub>2</sub>中间层、厚度为220nm的器件层1(Si)以及厚度为3 $\mu$ m的SiO<sub>2</sub>上包层。

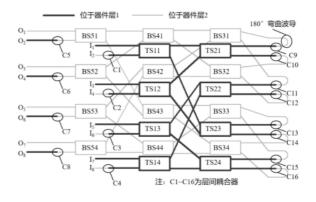

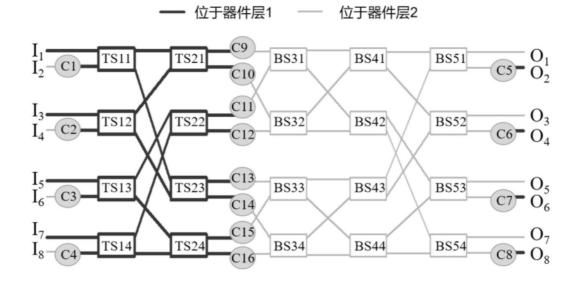

[0005] 如图2所示和图10,本发明所述的基于硅基光波导的双层开关阵列由电光开关阵列、层间耦合器以及光波导组成,电光开关阵列由第一级电光开关阵列(TS11~TS14)、第二级电光开关阵列(TS21~TS24)、第三级电光开关阵列(BS31~BS34)、第四级电光开关阵列(BTS41~BS44)和第五级电光开关阵列(BS51~BS54)五个部分组成,每级电光开关阵列内有4个电光开关单元;第一级电光开关阵列、第二级电光开关阵列制备于器件层1内,第三级电光开关阵列、第四级电光开关阵列和第五级电光开关阵列制备于器件层2内;该双层开关阵列由8条光波导作为输入端口,其中4个输入端口( $I_1$ 、 $I_3$ 、 $I_5$ 、 $I_7$ )位于器件层1,其余4个输入端口( $I_2$ 、 $I_4$ 、 $I_6$ 、 $I_8$ )位于器件层2;双层开关阵列由8条光波导作为输出端口,其中4个输出端口( $0_2$ 、 $0_4$ 、 $0_6$ 0、 $0_8$ )位于器件层1,其余4个输出端口( $0_1$ 、 $0_3$   $0_5$  、 $0_7$ )位于器件层2。

[0006] 第一级电光开关阵列 (TS11~TS14) 共有8个输入端口和8个输出端口,其中4个输入端口分别与作为双层开关阵列4个输入端口 ( $I_1$ 、 $I_3$ 、 $I_5$ 、 $I_7$ ) 的光波导相连接,其余4个输入端口各连接一个由器件层2向器件层1进行光信号传输的层间耦合器 (C1、C2、C3、C4),4个层间耦合器 (C1、C2、C3、C4) 又分别与4个位于器件层2作为双层开关阵列输入端口 ( $I_2$ 、 $I_4$ 、 $I_6$ 、 $I_8$ ) 的光波导相连接;第一级电光开关阵列的8个输出端口各自通过一条光波导分别与第二级电光开关阵列的8个输入端口相连接。

[0007] 第二级电光开关阵列(TS21~TS24)共有8个输入端口和8个输出端口,8个输入端口各自通过一条光波导分别与第一级电光开关阵列的8个输出端口相连接,,即TS11的第一输出端口与TS21的第一输入端口相连,TS11的第二输出端口与TS23的第一输入端口相连;TS12的第一输出端口与TS21的第二输入端口相连,TS12的第二输出端口与TS23的第二输入端口相连;TS13的第一输出端口与TS22的第一输入端口相连,TS13的第二输出端口与TS24的第一输入端口相连;TS14的第一输出端口与TS22的第二输入端口相连,TS14的第二输出端口与TS24的第二输入端口相连。第二级电光开关阵列的8个输出端口各连接一个由器件层1向器件层2进行光信号传输的层间耦合器(C9~C16),这8个层间耦合器分别与8个位于器件层2、弯曲半径为20μm、弯曲度数为180°的弯曲光波导的一端相连接。

[0008] 第三级电光开关阵列(BS31~BS34)共有8个输入端口和8个输出端口,8个输入端口各自通过一条光波导分别与8个弯曲光波导的另一端相连接,即TS21的第一输出端口通过层间耦合器C9与BS31的第一输入端口相连接,TS21的第二输出端口通过层间耦合器C10与BS32的第一输入端口相连接;TS22的第一输出端口通过层间耦合器C11与BS31的第二输入端口相连接,TS22的第一输出端口通过层间耦合器C12与BS32的第二输入端口相连接;TS23的第一输出端口通过层间耦合器C13与BS33的第一输入端口相连接,TS23的第二输出端口通过层间耦合器C15与BS33的第二输入端口相连接;TS24的第一输出端口通过层间耦合器C16与BS34的第二输入端口相连接;第三级电光开关阵列的8个输出端口通过层间耦合器C16与BS34的第二输入端口相连接;第三级电光开关阵列的8个输出端口各自通过一条光波导分别与第四级电光开关单元的8个输入端口相连接。

[0009] 第四级电光开关阵列(BS41~BS44)共有8个输入端口和8个输出端口,8个输入端口各自通过一条光波导分别与第三级电光开关单元的8个输出端口相连接,即BS31的第一输出端口与BS41的第一输入端口相连接,BS31的第二输出端口与BS42的第一输入端口相连接;BS32的第一输出端口与BS42的第二输入端口相连接;BS33的第一输出端口与BS43的第一输入端口相连接,BS33的第二输出端口与BS44的第一输入端口相连接;BS34的第一输出端口与BS43的第二输入端口相连接,BS34的第二输入端口相连接,BS34的第二输入端口相连接,BS34的第二输入端口相连接,BS34的第二输入端口相连接,BS34的第二输入端口相连接,BS34的第二输入端口相连接,BS34的第二输入端口相连接,BS34的第二输入端口相连接,BS34的第二输入端口有连接,BS34的第二输入端口有连接。

[0010] 第五级电光开关阵列(BS51~BS54)共有8个输入端口和8个输出端口,8个输入端口各自通过一条光波导分别与第四级电光开关单元的8个输出端口相连接,即BS41的第一输出端口与BS51的第一输入端口相连接,BS41的第二输出端口与BS52的第一输入端口相连接;BS42的第一输出端口与BS53的第一输入端口相连接,BS43的第二输出端口与BS51的第二输入端口相连接,BS43的第二输出端口与BS52的第二输入端口相连接;BS44的第一输出端口与BS53的第二输入端口相连接,

BS44的第二输出端口与BS54的第二输入端口相连接;第五级电光开关阵列的8个输出端口中,4个输出端口分别与4个位于器件层2作为阵列输出端口 $(0_1,0_3,0_5,0_7)$ 的光波导相连接,其余4个输出端口各连接一个由器件层2向器件层1进行光信号传输的层间耦合器(C5,C6,C7,C8),4个层间耦合器(C5,C6,C7,C8)又各自与4个位于器件层1作为阵列输出端口 $(0_2,0_4,0_6,0_8)$ 的光波导相连接。从而实现分布在两层上的8个输入和8个输出端口间光信号的传输和切换,可以显著减小单层器件的面积,提高集成度。

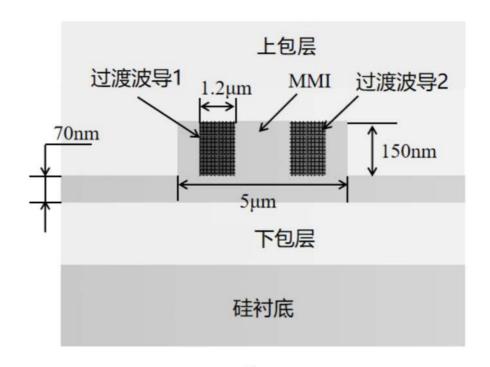

[0011] 阵列中所使用的光波导结构及尺寸如图3所示,采用脊型波导结构,其中脊高 150nm,平板层高度为70nm,其上、下包层材料均为 $Si0_2$ ,衬底材料是硅。包层和衬底材料的厚度会因光波导处于器件层1或器件层2而有所区别:对于处于器件层2的光波导,其下包层为双层硅结构晶圆的 $Si0_2$ 下包层,厚度为 $3\mu$ m,上包层为 $Si0_2$ 中间层厚度为150nm,衬底厚度为初始SOI晶圆的硅衬底厚度,厚度为 $500\mu$ m;对于处于器件层1的光波导,其下包层为 $Si0_2$ 中间层厚度为150nm,上包层为双层硅结构晶圆的 $Si0_2$ 上包层,厚度为 $3\mu$ m,衬底则是220nm厚度的器件层2。整个波导的宽度为 $0.5\mu$ m。

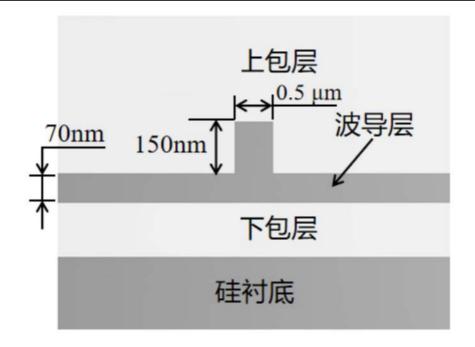

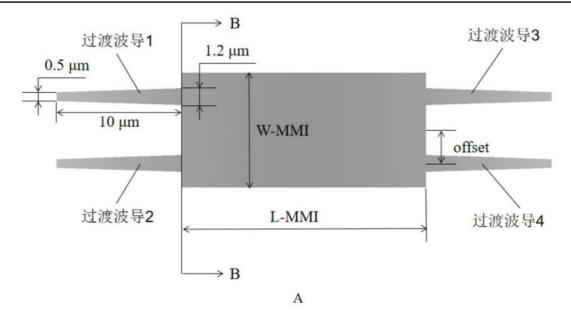

电光开关单元采用的是马赫-曾德尔干涉仪(Mach-Zehnder interferometer, MZI)结构,由两个双端口3-dB分光器和两条相移臂组成,3-dB分光器采用多模干涉器 (Multimode interference, MMI)结构,调制方式为双臂推挽型电光调制。电光开关单元是 由第一2×2多模干涉器、相互平行的相移臂1与相移臂2、第二2×2多模干涉器三部分顺次 级联形成的对称MZI结构,如图4所示。其中,第一2×2多模干涉器和第二2×2多模干涉器分 别记作MMI-1和MMI-2。MMI-1、MMI-2结构尺寸完全一致,其尺寸参数如图5A所示:其主体结 构为脊型波导,脊长度L\_MMI=29.2μm,脊宽度W\_MMI=5μm,MMI-1和MMI-2均带有两条输入 波导和两条输出波导;输入波导和输出波导均采用图3所示的脊型波导结构,宽度相同,均 为0.5µm。为了减小光学反射和散射带来的损耗,在输入波导、输出波导与多模干涉器的MMI 主体结构间引入了长10μm、宽度0.5~1.2μm间线性变化的过渡波导,过渡波导为脊型波导 结构,靠近MMI主体结构的过渡波导的宽度较宽为1.2µm,远离MMI主体结构的过渡波导的宽 度较窄为0.5μm,过渡波导中心距MMI主体结构中心的距离为offset=0.86μm。过渡波导与 MMI主体结构间的连接关系如图5B所示,两个过渡波导的脊结构均与MMI主体的脊波导结构 连接。MMI-1、MMI-2、相移臂1和相移臂2位于平行于衬底层的同一器件层内,MMI-1的两个输 入波导分别作为电光开关单元的第一输入端口(I,)和第二输入端口(I,),MMI-2的两个输出 波导分别作为电光开关的第一输出端口(0,)和第二输出端口(0,)。

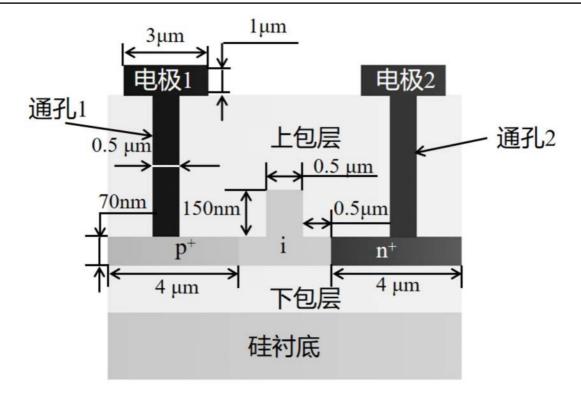

[0013] 电光开关单元采用基于等离子体色散效应的电光调制方式,图4中的电光开关单元的相移臂横截面结构尺寸如图6所示,采用脊型波导结构,其中脊高150nm,平板层高度为70nm;脊连同其两侧的部分平板层为n型背景掺杂区域,被n型背景掺杂区域分开的平板层分别为p型重掺杂区域和n型重掺杂区域;图中标注为p<sup>†</sup>的区域为p型重掺杂区域,其宽度为4 $\mu$ m,掺杂浓度为2×10<sup>20</sup>/cm<sup>-3</sup>;标注为n<sup>†</sup>的区域为n型重掺杂区域,其宽度为4 $\mu$ m,掺杂浓度为5×10<sup>20</sup>/cm<sup>-3</sup>;标注为i的区域为n型背景掺杂区域,其宽度为1.5 $\mu$ m,掺杂浓度为5×10<sup>17</sup>/cm<sup>-3</sup>,上下包层材料均为SiO<sub>2</sub>,衬底材料是硅。在SiO<sub>2</sub>上包层中设置有宽度为0.5 $\mu$ m的通孔1和通孔2,在通孔1和通孔2中填充铝;p型重掺杂区域和n型重掺杂区域分别通过通孔1和通孔2同位于SiO<sub>2</sub>上包层之上的宽度为3 $\mu$ m、厚度1 $\mu$ m的电极1和电极2相连。同未添加掺杂的光波导结构一样,包层和衬底材料的厚度会因光波导处于器件层1或器件层2而有所区别:包层

和衬底材料的厚度会因光波导处于器件层1或器件层2而有所区别:对于处于器件层2的光波导,其下包层为双层硅结构晶圆的Si0<sub>2</sub>下包层,厚度为3μm,上包层为Si0<sub>2</sub>中间层厚度为150nm,衬底厚度为初始S0I晶圆的硅衬底厚度,厚度为500μm;对于处于器件层1的光波导,其下包层为Si0<sub>2</sub>中间层厚度为150nm,上包层为双层硅结构晶圆的Si0<sub>2</sub>上包层,厚度为3μm,衬底则是220nm厚度的器件层2。整个器件的刻蚀掺杂都是基于通用的0.18μm CMOS工艺代工制作,设置相移臂长度为400μm。

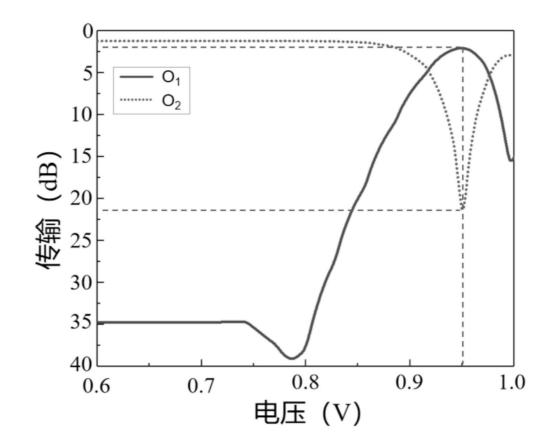

该电光开关工作原理为:从输入端口I<sub>1</sub>或I<sub>2</sub>输入的光信号在经过MMI-1时,由于多 模干涉效应,被平均分光成两部分,分别进入到相移臂1和相移臂2,在对相移臂不施加外部 电压时,该相移臂的波导中(标注为i的区域)没有载流子注入,两条相移臂的折射率均不发 生改变,此时从两条相移臂分别输出到MMI-2的光信号相位差为0,再经过MMI-2时,同样由 于多模干涉效应,从输入端口I,输入的光信号在输出端口0,发生反向干涉,在输出端口0,处 发生正向干涉,因此从输入端口I,输入的光信号将完整地从输出端口0,输出,同理,从输入 端口I,输入的光信号将从输出端口0,输出,此时即为电光开关单元的"CROSS"状态;如果对 任意一条相移臂施加外部电压,被施加外部电压的相移臂的波导因载流子的注入而发生折 射率的改变,当外部电压足够大时,使得从两条相移臂分别输出到MMI-2的光信号相位差为 π,再经过MMI-2时,由于多模干涉效应,从输入端口I<sub>1</sub>输入的光信号在输出端口0<sub>1</sub>发生正向 干涉,在输出端口0,处发生反向干涉,因此从输入端口I,输入的光信号将完整地从输出端口 0,输出,同理,从输入端口I,输入的光信号将从输出端口0,输出,此时即为电光开关单元 "BAR"状态。该开关单元的电压传输曲线如图7所示:设置一条相移臂的外部电压为0V,对另 一条相移臂施加的外部电压小于0.72V时处于初始的"CROSS"状态,"CROSS"状态下光损耗 为1.18dB, 串扰为-33.56dB; 设置一条相移臂的外部电压为0V, 对另一条相移臂施加的外部 电压为0.95V时处于"BAR"状态,BAR状态下光损耗为1.18dB,串扰为-19.18dB。

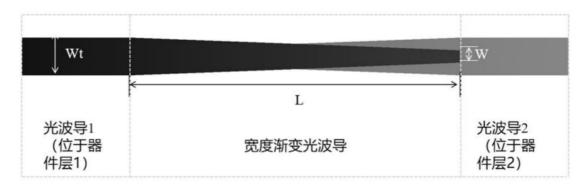

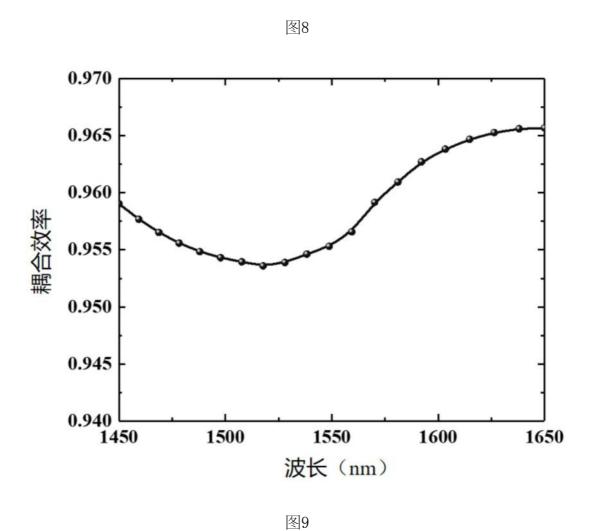

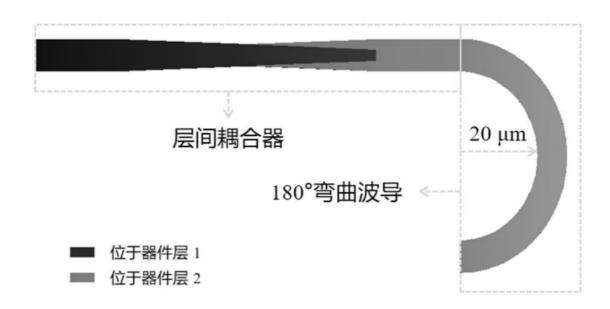

[0015] 层间耦合器是实现光信号在器件层1和器件层2间相互传输的关键器件,如图8所示一个由器件层1向器件层2进行光信号传输的层间耦合器结构示意图:它由分别放置在器件层1和器件层2的两个结构相同、宽度渐变方向相反、平行放置的光波导组成,该宽度渐变光波导长度L=9.5 $\mu$ m,窄端宽度W=210nm,粗端宽度Wt=500nm,由于与之互连的电光开关的输入波导和输出波导的宽度也为500nm,从而实现电光开关与层间耦合器的连接,器件层1和器件层2层厚度d=220nm,间距D=150nm,在满足上述几何参数条件下,单模光的层间耦合效率可达96.12%,带宽>100nm(耦合效率>90%)。图9为图8所示层间耦合器的波长响应,在1500~1600nm带宽范围内,该层间耦合器耦合效率>95%。

[0016] 图10为该本发明所述基于硅基光波导的双层开关阵列的平面结构示意图, $8\times8$ 双层开关阵列由五级电光开关单元组成,其中TS (Top Switch) 代表了器件层1内的电光开关 (包括第一级电光开关阵列TS11~TS14和第二级电光开关TS21~TS24),BS (Bottom Switch) 代表器件层2内的电光开关 (包括第三级电光开关阵列BS31~BS34、第四级电光开关BS41~BS44和第五级电光开关BS51~TS54),标注为C1~C8 (Coupler 1~Coupler 8) 的位置代表一个层间耦合器;在第2级电光开关阵列和第3级电光开关阵列间,标注为C9~C16的位置代表层间耦合器连接着180°的弯曲波导以实现层与层间的反向传输(如图11所示)。该开关阵列工作原理为:当信号由器件层1的输入端口 $I_1$ 、 $I_3$ 、 $I_5$ 、 $I_7$ 输入时,将直接通过第TS1 (TS11~TS14) 级开关;当信号由器件层2的输入端口 $I_2$ 、 $I_4$ 、 $I_6$ 、 $I_8$ 输入时,先经过层间耦

合器C1~C4到达器件层1,再进入第TS1 (TS11~TS14)级开关。利用开关网络的路由算法确定各开关路径状态,光信号通过第TS2 (TS21~TS24)级开关后,通过层间耦合器C9~C14到达器件层2,经过弯曲波导到达第BS3级 (BS31~BS34),再通过所有开关单元路径选择后到达相应的输出端口。当路径选择使信号由位于器件层2的端口输出时,信号经第BS5 (BS51~BS54)级开关后,由器件层2的输出端口 $0_1$ 、 $0_3$ 、 $0_5$ 、 $0_7$ 输出;当路径选择使信号由器件层1的输出时,信号经第5级开关后,经过层间耦合器C5~C8耦合至器件层1,由位于器件层1的输出端口 $0_2$ 、 $0_4$ 、 $0_6$ 、 $0_8$ 输出。两层均有四个输入/输出端口,从而减少单层器件个数,降低单层开关阵列尺寸,提高集成度。

#### 附图说明

[0017] 图1是双层硅结构晶圆的横截面结构示意图;

[0018] 图2是双层开关阵列结构示意图,在器件层1和器件层2间分布着8个输入端口、8个输出端口和20个双层开关单元;

[0019] 图3是光波导结构及尺寸示意图;

[0020] 图4是MZI开关单元示意图,MMI-1的两个输入波导分别作为电光开关的第一输入端口 $I_1$ 和第二输入端口 $I_2$ ,MMI-2的两个输出波导分别作为电光开关的第一输出端口 $0_1$ 和第二输出端口 $0_2$ ;

[0021] 图5是MMI结构以及参数示意图;

[0022] 图6是相移臂横截面示意图,包括波导结构、掺杂区域以及电极等结构;

[0023] 图7是图2所示开关单元的电压传输曲线,当一条调制臂的电压为0V,另一条调制臂调制电压小于0.72V时是开关的"CROSS"状态,光损耗为1.18dB,串扰为-33.56dB;当一条调制臂的电压为0V,另一条调制臂调制电压为0.95V时处于"BAR"状态,BAR状态下光损耗为1.18dB,串扰为-19.18dB;

[0024] 图8是所采用的层间耦合器结构示意图;

[0025] 图9是层间耦合器的波长-耦合效率关系曲线,在1500~1600nm带宽范围内,该层间耦合器能实现95%以上的耦合效率;

[0026] 图10是双层开关阵列结构示意图。

[0027] 图11是通过TS2 (TS21 ~ TS24) 级和BS3 (BS31 ~ BS34) 级间的180°弯曲波导与图8所示层间耦合器的组合示意图:

[0028] 具体实施试

[0029] 实施例1:

[0030] 对于图4所示开关阵列,设置一条调制臂的电压为0V,当另一条调制臂调制电压小于0.72V时处于初始的"CROSS"状态,此时 $I_1$ 的输入从 $0_2$ 输出, $I_2$ 的输入从 $0_1$ 输出,光损耗为1.18dB,串扰为-33.56dB;设置一条调制臂的电压为0V,另一条调制臂调制电压为0.95V时处于"BAR"状态,此时 $I_1$ 的输入从 $0_1$ 输出, $I_2$ 的输入从 $0_2$ 输出,损耗为1.18dB,串扰为-19.18dB。

[0031] 实施例2:

[0032] 对于图10所示开关阵列,当开关阵列输入/输出对应关系为"I<sub>2</sub>—0<sub>4</sub>"时,根据路由算法,可实现该光信号传输的可能开关路径之一为:TS11(直通态)、TS23(直通态)、BS33(直

通态)、BS43(交叉态)、BS52(直通态)。光信号首先自输入光纤,通过端口 $I_2$ 耦合进器件层1,经层间耦合器C1耦合至器件层1,经过处于直通态的开关TS11、TS23后,再经层间耦合器C13耦合至器件层2,通过180°波导后进入开关BS33(直通态),通过BS43(交叉态)和BS52(直通态)后,通过层间耦合器C6耦合至器件层1的 $0_4$ 端口输出。

## [0033] 实施例3:

[0034] 对于图10所示开关阵列,当所有的开关状态都处于直通态时,对应的输入输出路径为:  $I_1$ -TS11-TS21-C9-BS31-BS41-BS51- $0_1$ 、 $I_2$ -C1-TS11-TS23-C13-BS33-BS43-BS51-C5- $0_2$ 、 $I_3$ -TS12-TS21-C10-BS32-BS41-BS52- $0_3$ 、 $I_4$ -C2-TS12-TS23-C14-BS34-BS43-BS52-C6- $0_4$ 、  $I_5$ -TS13-TS22-C11-BS31-BS42-BS53- $0_5$ 、 $I_6$ -C3-TS13-TS24-C15-BS33-BS44-BS53-C7- $0_6$ 、 $I_7$ -TS14-TS22-C12-BS32-BS42-BS54- $0_7$ 、 $I_8$ -C4-TS14-TS24-C16-BS34-BS44-BS54-C8- $0_8$ 。

## [0035] 实施例4:

[0036] 对于图10所示开关阵列,当所有的开关状态都处于交叉态时,对应的输入输出路径为:  $I_1$ -TS11-TS23-C14-BS34-BS44-BS53- $0_5$ 、 $I_2$ -C1-TS11-TS21-C10-BS32-BS42-BS53-C7- $0_6$ 、 $I_3$ -TS12-TS23-C13-BS33-BS44-BS54- $0_7$ 、 $I_4$ -C2-TS12-TS21-C9-BS31-BS42-BS54-C8- $0_8$ 、  $I_5$ -TS13-TS24-C16-BS34-BS43-BS51- $0_1$ 、 $I_6$ -C3-TS13-TS22-C12-BS32-BS41-BS51-C5- $0_2$ 、 $I_7$ -TS14-TS24-C135-BS33-BS43-BS52- $0_3$ 、 $I_8$ -C4-TS14-TS22-C11-BS31-BS41-BS52-C6- $0_4$ 。

图1

图2

图3

图4

В

图5

图6

图7

■ 位于器件层 1■ 位于器件层 2

图10

图11