(19) **日本国特許庁(JP)**

審查請求日

# (12)特 許 公 報(B2)

(11)特許番号

特許第4940894号 (P4940894)

(45) 発行日 平成24年5月30日(2012.5.30)

(24) 登録日 平成24年3月9日(2012.3.9)

(51) Int. Cl. F. L.

**G11C** 11/407 (2006.01) G11C 11/34 362S G11C 11/401 (2006.01) G11C 11/34 362C

平成21年7月22日 (2009.7.22)

請求項の数 4 (全 9 頁)

(21) 出願番号 特願2006-293486 (P2006-293486) (22) 出願日 平成18年10月30日 (2006.10.30) (65) 公開番号 特開2008-112485 (P2008-112485A) (43) 公開日 平成20年5月15日 (2008.5.15)

(73)特許権者 000005108

株式会社日立製作所

東京都千代田区丸の内一丁目6番6号

|(74)代理人 100100310

弁理士 井上 学

||(72)発明者 長谷川 雅俊

東京都青梅市新町六丁目16番地の3 株式会社日立製作所 マイクロデバイス事業

部内

||(72)発明者 中山 道明

東京都青梅市新町六丁目16番地の3 株式会社日立製作所 マイクロデバイス事業

部内

最終頁に続く

(54) 【発明の名称】同期型メモリ回路

### (57)【特許請求の範囲】

#### 【請求項1】

読み出し命令により読み出しデータのバースト長が変更される第1の制御回路と、

第1の書き込み命令の直前のサイクルにて第2の書き込み命令が与えられているか否か に応じて、書き込みデータのバースト長が変更される第2の制御回路と、を有し、

ラッチされているライトデータを上記バースト長で書き込み、

上記読み出し命令と同じサイクルで上記第2書き込み命令を与えることが可能なことを 特徴とする同期型メモリ回路。

## 【請求項2】

請求項1において、

上記第2の書き込み命令が与えられた場合の上記第1の書き込み命令による書き込みデータのバースト長は、上記第2の書き込み命令が与えられなかった場合の上記第1の書き 込み命令による書き込みデータのバースト長よりも短いことを特徴とする同期型メモリ回

路。

## 【請求項3】

請求項1において、

上記第1の書き込み命令または上記第2の書き込み命令と同じサイクルで読み出し命令を与えることが可能なことを特徴とする同期型メモリ回路。

## 【請求項4】

請求項3において、

10

<u>複数のバンクを有し、上記第1の書き込み命令、上記第2の書き込み命令及び上記読み</u> 出し命令は、それぞれ異なるバンクに作用することを特徴とする同期型メモリ回路。

【発明の詳細な説明】

【技術分野】

[0001]

この発明は同期型メモリ回路に関する。

【背景技術】

[0002]

シンクロナス スタティック型RAM等では、製品ごとにバースト長(データを連続して書き込み / 読み出しするビット数)を変えているものがある。また、シンクロナス ダイナミック型RAM等では、書き込み / 読み出し動作の前にモードレジスタセットによりバースト長をモード設定で可変にしているものがある。

[0003]

しかし、いずれも書き込み/読み出し動作を開始した後のバースト長は固定であり、様々なビット数のデータを取り扱うアプリケーションでは、バーストデータの一部しか使用しないケースが存在してメモリ容量の使用効率が低下する場合があった。

[0004]

本発明後に、バースト長を可変にできるメモリという観点で公知例調査を行ったところ、特許文献1のようなものが見出された。本公知例にはバースト長を変更するための専用命令を有するメモリ回路が開示されている。

[0005]

【特許文献 1 】特開 2 0 0 0 - 9 0 6 6 5 号公報

【発明の開示】

【発明が解決しようとする課題】

[0006]

サーバー等のコンピュータシステムにおいては一般にデータをバイト単位(1バイト=8ビット)で処理することが多く、メモリに書き込んだり読み出したりする動作も8ビットや4ビットを単位に行うことが多いため、バースト長も8や4に設定することが多い。これに対して、ネットワークシステム等においては扱うデータの長さがランダムなため、バースト長があまり長いとバーストの中で有効なデータは一部で、残りは無効なデータになり、メモリの使用効率が低下することがあった。そのため、バースト長を短く設定すると上記のような無効なデータの領域は減るが、メモリに対し頻繁に読み出し命令や書き込み命令を与える必要があり、制御の煩雑さや消費電力の増加を招く。さらに、メモリが読み出し命令や書き込み命令を受け取ることができる周期がバースト長より長い場合は、全データを読み出しまたは書き込みするまでの時間がかかり、システムの性能向上を妨げる要因となる。

[0007]

そこで本発明者は、メモリのバースト長を自由に変更することができれば、格納したいデータの長さに応じてバースト長を変更してメモリの使用効率と性能向上、消費電力低減等が両立できると考えた。このためには従来のシンクロナス ダイナミック型RAMのように電源投入後の書き込み、読み出し前にバースト長をモードレジスタで設定する機能では不十分で、書き込み、読み出しするその時々にデータの長さから最適なバースト長を判断して選択できることが望ましい。

[0008]

本発明の目的は、簡単な構成で書き込み、読み出しするその時々にバースト長を変更可能にしたメモリ回路を備えた半導体集積回路装置を提供することにある。 この発明の前記ならびにそのほかの目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

[0009]

10

20

30

40

50

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば、下記の通りである。 メモリの読み出し制御回路において、読み出し命令が与えられた次のサイクルに読み出し命令が与えられたか否かを判断する回路を設け、その結果によってバースト長を変更する。 また書き込み制御回路において、書き込み命令が与えられた前のサイクルに書き込み命令が与えられたか否かを判断する回路を設け、その結果によってバースト長を変更する。

#### 【発明の効果】

#### [0010]

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば、下記の通りである。読み出し命令または書き込み命令を与えるときにバースト長の切り替えが可能であるため、メモリ使用効率の向上と制御の簡便さが両立可能である。特に、本発明の同期型メモリ回路がデータ長のバリエーションが多いシステムにおいて有効である。

【発明を実施するための最良の形態】

#### [0011]

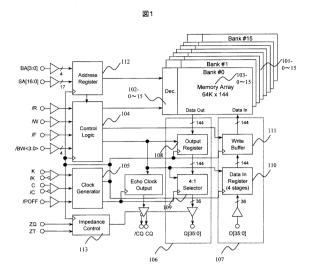

図 1 に、半導体集積回路装置に搭載される同期型メモリ回路の機能ブロック図を示す。デコーダ102とメモリアレイ103とでそれぞれ独立に動作可能な単位であるバンク101を構成する。図 1 の例では、1 6 バンク(101-0~101-15)を搭載している。例えば、メモリアレイ103はダイナミック型メモリセルで構成される6 4 K × 1 4 4 = 9 M ビットから構成され、メモリ回路全体で1 4 4 M ビットのメモリ容量を持っている。

[0012]

なお、一つのバンクが読み出しまたは書き込みの動作を開始してからその動作を完結し、次の命令が受付可能になるためには5サイクルを要する。しかし、バンク101-0~101-15はそれぞれ独立に動作することができるため、同期型メモリ回路としては異なるバンクを選択することにより、毎サイクル読み出しまたは書き込みの命令を受け取ることが可能になる。

#### [0013]

同期型メモリ回路を制御する制御回路104には、クロック発生回路105から供給されるクロックのほか、読み出し命令信号 / R、書き込み命令信号 / W、データレート指示信号 / F、その他命令が入力され、各種の制御信号を読み出し回路106、書き込み回路107に供給している。

[0014]

図 1 に示されるように、読み出し回路106及び書き込み回路107は、複数のバンク101-0~101-15に共通に設けられている。また、読み出し回路106と書き込み回路107とは独立に設けられていて、同期型メモリ回路としては一つのサイクルで読み出し命令 / 書き込み命令の両方を受け取ることができる。ただしその場合は、読み出し命令と書き込み命令とが別のバンクに与えられなければいけない。データバスも読み出し系Q[35:0] / 書き込み系D[35:0]で分かれているため、命令の受け取りと同時に読み出し / 書込みが可能となっている。読み出し回路106は、バンク101のメモリアレイ103から読み出しデータを一時的に格納する出力レジスタ108と、出力レジスタ108に格納された読み出しデータを選択的に読み出し系データバスに出力するセレクタ109とを備える。また、書き込み回路107は、書き込み系データバスからの書き込みデータを一時的に格納する入力レジスタ110と、入力レジスタ110に格納された書き込みデータのうち、アドレス(BA、SA)により指定されるバンク101のメモリアレイ103に書き込むべきデータが格納されるライトバッファ111とを備える。

## [0015]

書き込みデータはデータレート指示信号 / Fの極性により S D R (シングルデータレート) または D D R (ダブルデータレート) で取り込まれる。詳細は後述するが、バースト長制御信号(書き込み) WRBL4Tにより、バースト長が 4 のときには 3 6 : 1 4 4 のシリアル-パラレル変換が、バースト長が 2 のときには 3 6 : 7 2 のシリアル-パラレル変換が行

10

20

30

40

50

10

20

30

40

50

われ、メモリアレイに書き込みを行う。また、読み出しデータは1回の命令で144ビットがメモリアレイ103から読み出され、144:36のパラレル-シリアル変換が行われる。詳細は後述するが、バースト長制御信号(読み出し)RDBL4Tにより、バースト長が4のときには2サイクルかけて144ビット分全てがメモリ回路から読み出されるのに対し、バースト長が2のときには72ビット分のみがメモリ回路から読み出される。

#### [0016]

なお、以上本発明に特に関係のある部分を中心に説明したが、以下他の回路ブロックについても簡単に説明する。アドレスレジスタ112はアクセスするメモリアドレスを格納する。メモリアドレスはバンクアドレスBAとシンクロナスアドレスSAとからなる。クロック発生回路105は、例えばPLLで構成され、この構成例では、基本クロック(K, /K)と出力クロック(C, /C)の2系統を有している。また、エコークロック(CQ, /CQ)として同期型メモリ回路の外部に供給される(図6参照)。インピーダンス制御回路113により、クロック(CQ, /CQ)ドライバ、読み出し系データバスへのドライバに対してインピーダンス制御が行われる。

#### [0017]

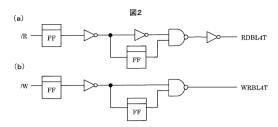

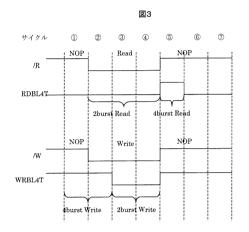

図 2 ( a ) , ( b ) はそれぞれ、バースト長制御信号(読み出し/書き込み)RDBL4T/WRBL4Tを生成するバースト長制御回路(読み出し/書き込み)の構成例である。バースト長制御回路は、制御回路104に含まれる。また図 3 に、図 2 に示したバースト長制御信号(読み出し/書き込み)のタイミングチャートを示している。

## [0018]

まず、バースト長制御回路(読み出し)の動作について説明する。図3では、読み出し命令信号 / Rが第1サイクルでHigh、第2~第4サイクルでLow、第5サイクル以降が再度Highに戻っているような波形である場合のバースト長制御信号(読み出し)RDBL4Tの波形を示している。図2(a)の回路動作に基づき、バースト長制御信号(読み出し)RDBL4Tの波形は、第1~第4サイクルでLow、第5サイクルでHigh、第6サイクル以降再度Lowが出力される。この場合、第1サイクルでは読み出し命令信号 / RがHighであり、読み出し動作は実行されずNOP(No Operation)となっている。第2サイクルで読み出し命令信号 / RがLowになって読み出し動作が実行される。第2サイクルではバースト長制御信号(読み出し)RDBL4TはLowであり、バースト長2の読み出し動作が行われる。読み出し命令信号 / Rが連続してLowの間(第2~第4サイクル)はバースト長2の読み出し動作が続き、読み出し命令信号 / RがHighになると(第5サイクル)、バースト長制御信号(読み出し)RDBL4TがHighになり、バースト長4の読み出し動作が行われる。読み出し命令信号 / RがHighということで新規のアドレスに対して読み出し動作は行われないが、バースト長が4になることで一つ前のアドレスに対する読み出しずータのうち出力されていなかったデータが出力され、データバスを埋めることができる。

#### [0019]

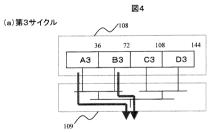

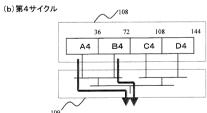

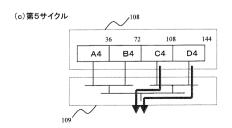

図4を用いてバースト長制御回路(読み出し)の動作をさらに説明する。出力レジスタ108は、図1の構成では144ビットの容量を有し、これが36ビットずつの4領域に分かれている。バースト長2の読み出しの場合はセレクタ109において2つの領域が選択され、読み出し系データバスに出力される。より詳細に図3の第3~第5サイクルにおける読み出しデータについて説明する。第3サイクルでは、読み出し命令信号/R(Low)を受けて、アドレス信号(BA,SA)にしたがって、A3~D3(A3~D3はそれぞれ36ビットの読み出しデータ)がメモリアレイから出力レジスタ108に読み出される。セレクタ109では、バースト長制御信号(読み出し)RDBL4TがLowであるため、そのうちの2領域の読み出しデータ(例えば、A3,B3)の72ビット分のデータをデータバスに読み出す(バースト長2の読み出し)。第4サイクルでは、読み出し命令信号/R(Low)を受けて、アドレス信号(BA,SA)にしたがって、A4~D4(A4~D4はそれぞれ36ビットの読み出しデータ)が新たにメモリアレイから出力レジスタ108に読み出される。セレクタ109では、バースト長制御信号(読み出し)RDBL4TがLowであるため、そのうちの2領域の読み出しデータ(例えば、A4,B4)の72ビット分のデータをデータバスに読み出す。

10

20

30

40

50

さらに、第5サイクルでは、読み出し命令信号 / R (High)を受けて、新たなメモリアレイからの読み出しは行われず、一方、セレクタ109では、バースト長制御信号(読み出し)R DBL4TがHighであるため、残る2領域の読み出しデータ(上記の例では、C4,D4)の72ビット分のデータをデータバスに読み出す。これによりバースト長4の読み出しが実現される。

### [0020]

次に、バースト長制御回路(書き込み)の動作について説明する。図3では、書き込み命令信号 / Wが第1サイクルでHigh、第2~第4サイクルでLow、第5サイクル以降が再度Highに戻っているような波形である場合のバースト長制御信号(書き込み)WRBL4Tの波形を示している。図2(b)の回路動作に基づき、バースト長制御信号(書き込み)WRBL4Tの波形は、第1~第2サイクルでHigh、第3~第4サイクルでLow、第5サイクル以降再度Highが出力される。この場合、第1サイクルでは書き込み命令信号 / WがHighであり、書き込み動作は実行されずNOP(No Operation)となっている。このとき、いつ書き込み命令がきても書き込み動作が開始できるように、毎サイクル書き込みずータをラッチしている。第2サイクルで書き込み命令信号 / WがLowになると書き込み動作が実行される。このとき、バースト長制御信号(書き込み)WRBL4TはHighであり、バースト長4の書き込み動作が行われる。さらに、書き込み命令信号 / Wが連続して2サイクル以上Lowになるとバースト長制御信号(書き込み)WRBL4TはLowになり(第3及び第4サイクル)、バースト長2の書き込み動作が行われる。

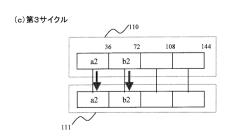

## [0021]

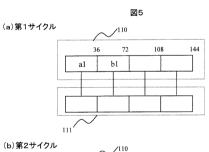

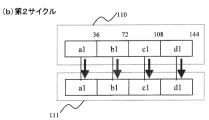

図 5 を用いてバースト長制御回路(書き込み)の動作をさらに説明する。入力レジスタ 110は、図 1 の構成では 1 4 4 ビットの容量を有し、これが 3 6 ビットずつの 4 領域に分かれている。より詳細に図 3 の第 1 ~ 第 3 サイクルにおける書き込みデータについて説明する。第 1 サイクルでは、書き込み命令信号 / W (High)であるが、書き込みデータ a 1 , b 1 ( a 1 , b 1 はそれぞれ 3 6 ビットの書き込みデータ)をラッチしている。第 2 サイクルでは、書き込み命令信号 / W (Low)となり、バースト長制御信号(書き込み)WRBL4TがHighであるため、書き込みデータ c 1 , d 1 はそれぞれ 3 6 ビットの書き込みデータ)がラッチされ、書き込みデータ a 1 ~ d 1 の 1 4 4 ビットがライトバッファ111に転送され、指定されたアドレス(BA,SA)に書き込まれる(バースト長4の書き込み)。第 3 サイクルでは書き込み命令信号 / W (Low)であり、バースト長制御信号(書き込み)WRBL4TがLowであるため、書き込みデータ a 2 , b 2 がラッチされ、ラッチされた書き込みデータ a 2 , b 2 の 7 2 ビットがライトバッファ111に転送され、指定されたアドレス(BA,SA)に書き込まれる(バースト長 2 の書き込み)。バースト長制御信号(書き込み)WRBL4Tがライトバッファ111に入力されることにより、活性化される範囲を 7 2 ビット分とするか、 1 4 4 ビット分とするか切り替えている。

#### [0022]

なお、本実施例ではバースト長は2と4での切り替えを行っているため、NOPが2サイクル以上続くとデータバスの空きが生じるのに対し、バースト長を例えば8などに長くすることによって、読み出しNOPが連続した時でもデータバス効率を上げることができる利点がある。しかしながら、バースト長が長いと、データが入力、出力されている間は新しいアドレスに対する読み出し、書き込み動作ができないので、システムとしての性能を逆に落とす可能性もある。切り替えするバースト長の長さは、本発明の同期型メモリ回路が使用されるシステム性能向上に有利なように定めればよい。

## [0023]

図 6 に読み出し / 書き込みを同時に行っているときの図 1 に示した同期型メモリ回路のタイミングチャートの例を示す。この期間、データレート指示信号 / FはLowであり、DDRで動作している場合のタイミングチャートを示している。サイクル#0で読み出し命令信号 / RがLowになることにより、バンクアドレス#B0のアドレス#A0に対する読み出し命令が与えられている。この読み出し命令に対する読み出しデータは、サイクル#5の後半からDDRで2ビット(Q0a、Q0b)である。サイクル#1でも読み出し命

10

20

30

40

令信号 / RがLowで読み出し命令が与えられているので、サイクル#0の読み出し命令に対する読み出しデータはバースト長2で上記2ビット(Q0a、Q0b)のみとなる。サイクル#2ではバンクアドレス#B4のアドレス#A4に対し読み出し命令が与えられているが、次のサイクル#3では読み出し命令が与えられていないためバースト長は4となり、サイクル#7の後半からDDRで4ビット(Q4a、Q4b、Q4c、Q4d)が読み出される。

#### [0024]

また、サイクル#0では書き込み命令信号 / WもLowになっており、サイクル#0の後半で与えられているバンクアドレス#B1のアドレス#A1に対し書き込み命令が与えられている。直前のサイクル#(-1)は書き込み命令信号 / WがHighであるのでバースト長4の書き込み動作となり、サイクル#(-1)からDDRで4ビット(D1a、D1b、D1c、D1d)のデータが書き込まれる。次のサイクル#1も書き込み命令信号 / WはLowであるためバースト長は2となり、サイクル#1からDDRで2ビット(D3a、D3b)のデータが書き込まれる。

## [0025]

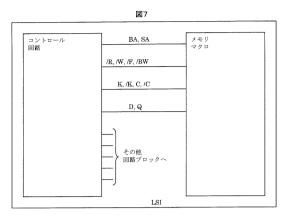

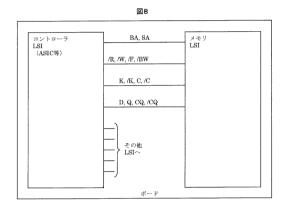

図7には本発明を実施したメモリマクロをLSI内に実装した例を示す。また、図8には本発明を実施した集積回路装置をボード上に実装した例を示す。図7の例では、コントロール回路と図1の構成に相当するメモリマクロとが一チップ上に集積され、図8の例では、図7のコントロール回路が一チップのコントローラLSIに集積され、図1の構成に相当するメモリLSIが一チップに集積され、これら複数のチップがボード上に実装されている。いずれの場合もコントロール回路からメモリマクロへの制御信号(図7)あるいはコントローラLSIからメモリLSIへの制御信号(図8)は図に示されるような基本的な読み出しあるいは書き込み動作に必要な制御信号であり、バースト長を指示するための信号は有していない。

#### 【図面の簡単な説明】

### [0026]

- 【図1】同期型メモリ回路の回路ブロック図である。

- 【図2】バースト長制御回路(読み出し/書き込み)の構成例である。

- 【図3】図2のバースト長制御回路(読み出し/書き込み)のタイミングチャートである

- 【図4】読み出し動作をより詳細に説明するための図である。

- 【図5】書き込み動作をより詳細に説明するための図である。

- 【図6】図1の同期型メモリ回路のタイミングチャートである。

- 【図7】本発明を実施したメモリマクロをLSIに実装した例である。

- 【図8】本発明を実施した集積回路装置(メモリLSI)をボードに実装した例である。

## 【符号の説明】

## [0027]

BA…バンクアドレス、SA…シンクロナスアドレス、/R…読み出し命令信号(ネガ極性)、/W…書き込み命令信号(ネガ極性)、/F…データレート指示信号、/BW…バイトライト命令信号(ネガ極性)、K…基本クロック(ポジ極性)、/K…基本クロック(ネガ極性)、/C…出力用クロック(ネガ極性)、〇二読み出しデータ信号、D…書き込みデータ信号、CQ…エコークロック信号(ポジ極性)、/CQ…エコークロック信号(ポジ極性)、

## 【図1】

## 【図2】

## 【図3】

## 【図4】

## 【図5】

【図6】

図6

【図7】

【図8】

### フロントページの続き

## (72)発明者 坂本 将俊

東京都青梅市新町六丁目16番地の3 株式会社日立製作所 マイクロデバイス事業部内

審査官 小林 紀和

(56)参考文献 特開2001-135079(JP,A)

特開平11-345487 (JP,A)

特開平10-208468(JP,A)

(58)調査した分野(Int.CI., DB名)

G 1 1 C 1 1 / 4 0 1

G11C 11/407