## (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2005-285950 (P2005-285950A)

(43) 公開日 平成17年10月13日(2005.10.13)

(51) Int.C1.<sup>7</sup>

FI

テーマコード (参考)

HO1L 29/78

HO1L 29/78 3O1D

5F14O

審査請求 未請求 請求項の数 2 OL (全 9 頁)

| (21) 出願番号<br>(22) 出願日 | 特願2004-95282 (P2004-95282)<br>平成16年3月29日 (2004.3.29) | (71) 出願人                                | 000006220<br>ミツミ電機株式会社<br>東京都多摩市鶴牧2丁目11番地2 |

|-----------------------|------------------------------------------------------|-----------------------------------------|--------------------------------------------|

|                       |                                                      | (72) 発明者                                | 木村 啓                                       |

|                       |                                                      | (-),,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | 神奈川県厚木市酒井1601 ミツミ電機                        |

|                       |                                                      |                                         | 株式会社厚木事業所内                                 |

|                       |                                                      | (72) 発明者                                | 白石 尚寬                                      |

|                       |                                                      |                                         | 神奈川県厚木市酒井1601 ミツミ電機                        |

|                       |                                                      |                                         | 株式会社厚木事業所内                                 |

|                       |                                                      | (72) 発明者                                | 菅原 亜季                                      |

|                       |                                                      |                                         | 神奈川県厚木市酒井1601 ミツミ電機                        |

|                       |                                                      |                                         | 株式会社厚木事業所内                                 |

|                       |                                                      |                                         |                                            |

|                       |                                                      |                                         |                                            |

|                       |                                                      |                                         |                                            |

|                       |                                                      |                                         | 最終百に続く                                     |

### (54) 【発明の名称】半導体装置及びその製造方法

## (57)【要約】

【課題】 ドレイン領域とチャネルとの間の耐圧を高めながら、製品毎の実効ゲート長の変動を抑制する。

【解決手段】 ソース領域4と、ドレイン領域3と、ソース領域4とドレイン領域3との間のチャネルの上方にゲート酸化膜7を介して形成された第1ゲート電極8と、ドレイン領域3の一部の及び第1ゲート電極8の一部の上方に酸化膜を介して形成された第2ゲート電極9とを有する。ドレイン領域3が、深さの深い低濃度拡散領域3Bと、低濃度拡散領域3Bと同じ導電型であって低濃度拡散領域3Bに設けられた浅い高濃度拡散領域3Aとから構成される。

【選択図】 図1

### 【特許請求の範囲】

### 【請求項1】

ソース領域と、ドレイン領域と、前記ソース領域と前記ドレイン領域との間のチャネルの上方にゲート酸化膜を介して形成された第1ゲート電極と、前記ドレイン領域の一部の上方及び前記第1ゲート電極の一部の上方に形成された第2ゲート電極とを有し、

前記ドレイン領域が、深さの深い低濃度拡散領域と、前記低濃度拡散領域と同じ導電型であって前記低濃度拡散領域に設けられた浅い高濃度拡散領域とから構成され、

前記ドレイン領域の深さの深い低濃度拡散領域が、前記第1ゲート電極をマスクとするイオン注入により形成されるとともに、この深さの深い低濃度拡散領域の一部を覆って第2ゲート電極が形成され、

前記ドレイン領域の浅い高濃度拡散領域及び前記ソース領域は、前記第1ゲート電極及び第2ゲート電極をマスクとするイオン注入により形成されていることを特徴とする半導体装置。

## 【請求項2】

半導体基板上にゲート酸化膜を形成した後、前記ゲート酸化膜上に第1ゲート電極とを 形成する工程と、

ドレイン領域が形成される領域以外を覆うレジスト及び前記第 1 ゲート電極をマスクとして、前記半導体基板の前記ドレイン領域が形成される領域にイオン注入し、前記ドレイン領域のうち深さの深い低濃度拡散領域を形成する工程と、

前記半導体基板の前記低濃度拡散領域の一部及び前記第1ゲート電極の一部を覆って、第2ゲート電極を形成する工程と、

前記第1ゲート電極及び第2ゲート電極をマスクとして、前記低濃度拡散領域及び半導体基板のソース領域が形成される領域に前記低濃度拡散領域と同じ導電型のイオンを注入し、高濃度拡散領域及びソース領域を形成する工程とを有することを特徴とする半導体装置の製造方法。

### 【発明の詳細な説明】

### 【技術分野】

#### [00001]

本発明は、ドレイン領域が深さの深い低濃度拡散領域と浅い高濃度拡散領域との2層構造を有する半導体装置及びその製造方法に関する。

### 【背景技術】

## [0002]

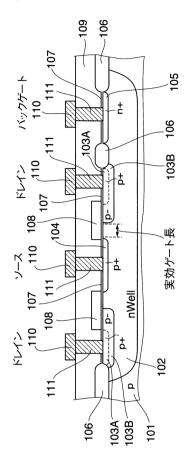

MOSFET等の半導体装置の素子耐圧の向上を目的として、例えばドレイン領域に低濃度領域を追加形成した構造の半導体装置が提案されている(特許文献 1 参照。)。このような構造の半導体装置(MOSFET)の一例を、図3に示す。このMOSFETにおいては、使用されるシリコン(Si)半導体基板 1 0 1 は p型であり、この表面に n型のウェル(well) 1 0 2 が深く形成されている。 n型ウェル 1 0 2 の表面には、 pチャネルのMOSFET(以下、 PMOSと称する。)が形成されている。 n型ウェル 1 0 2 の表面には、 PMOSのドレイン領域 1 0 3 として、浅く形成された p +型の高濃度拡散領域 1 0 3 Bとが形成されている。また、 n型ウェル 1 0 2 には p +型のソース領域 1 0 4 が浅く形成されている。また、 n型ウェル 1 0 2 には p +型のソース領域 1 0 4 が浅く形成されている。また、 n型ウェル 1 0 2 の所定の領域には、 n型ウェル 1 0 2 にバイアス電圧を印加するバックゲート用の n +型拡散領域 1 0 5 が浅く形成されている。

## [0003]

この半導体基板 1 0 1 の表面は、素子領域間及びドレイン領域 1 0 3 とバックゲート用の n+2拡散領域 1 0 5 との間が、厚いフィールド酸化膜( $SiO_2$ ) 1 0 6 によって分離されている。ゲート酸化膜 1 0 7 の上には、多結晶シリコンからなるゲート電極 1 0 8 が形成され、ゲート電極 1 0 8 の下方がチャネル領域となる。半導体基板 1 0 1 の表面全体には、例えば BPSG(ボロフォスフォシリケートグラス)等の絶縁膜 1 0 9 が積層されている。この絶縁膜 1 0 9 の上層には、アルミニウム等の金属配線層 1 1 0 が積層され

10

20

30

40

50

る。金属配線層110は、絶縁膜109に形成されたコンタクトホール111を介して、 それぞれドレイン領域103の高濃度拡散領域103A、ソース領域104、バックゲー ト用n+拡散領域105にそれぞれ接続される。

### [0004]

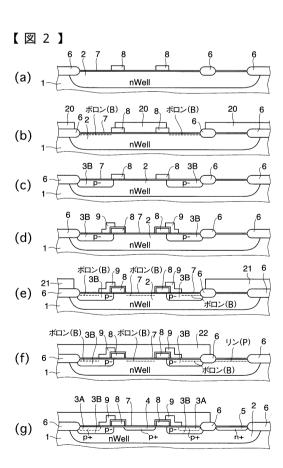

前述の図3に示す半導体装置は、例えば、p型シリコン単結晶をウェーハに切り出し、表面を鏡面研磨し、そのウェーハを高温の酸素雰囲気中にさらし、シリコンの酸化膜を成長させた後、フォトレジストを使って酸化膜上にn型ウェルの領域となるパターンを形成し、n型ウェル用不純物をドープし、熱拡散して、n型ウェルを形成(n型ウェル形成工程)してから、図4に示すようなプロセスにより製造される。

#### [00005]

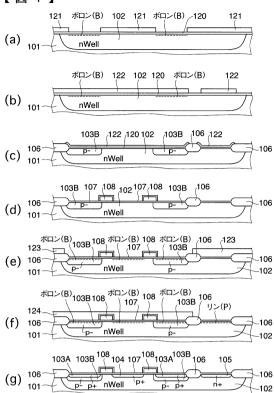

先ず、図4(a)に示すように、上記ウェル102、及び半導体基板101上にパッド酸化膜120を形成し、そのパッド酸化膜120上にレジスト121を形成する。そしてn型ウェル102の必要箇所に低濃度のドレイン領域を形成するために、レジスト121の開口からパッド酸化膜120を通してB(ボロン)をイオン注入する。

### [0006]

次に、図4(b)及び図4(c)に示すように、低濃度のドレイン領域上に窒化膜122を形成し、この窒化膜122を利用して、熱を加えフィールド酸化膜106を形成する。それと同時に上記注入されたBイオンを拡散して、PMOSのp-型低濃度拡散領域103Bを形成する。

### [0007]

さらに、図4(d)に示すように、窒化膜122及びパッド酸化膜120を除去し、ゲート酸化膜107を形成した後、上面に導電性の多結晶シリコン層を形成し、多結晶シリコン層の不要部分を除去してゲート電極108を形成する。ゲート電極108の周囲は、SiO,等の酸化膜で覆っておく。

### [0008]

次に、図4(e)に示すように、ドレイン領域103の低濃度拡散領域103Bに高濃度拡散領域を形成するため、また、n型ウェル102にソース領域を形成するために、半導体基板101の必要箇所にレジスト123を形成し、レジスト123、フィールド酸化膜106及びゲート電極108の開口からゲート酸化膜120を通してB(ボロン)イオンを注入する。

### [0009]

次いで、図4(f)に示すように、ウェル102にバックゲート用のn+型拡散領域を 形成するために、半導体基板101の必要箇所にレジスト124を形成し、レジスト12 4の開口からゲート酸化膜120を通して、P(リン)をイオン注入する。

## [0010]

次に、図4(g)に示すように、半導体基板101を熱処理して、上記注入されたBイオン及びPイオンを拡散して、ドレイン領域103のp+型高濃度拡散領域103A、ソース領域104、及びバックゲート用のn+型拡散領域105を浅く形成する。

## [0011]

最後に、半導体基板101の全面に絶縁膜109を積層し、その後絶縁膜109にコンタクトホール111を開け、絶縁膜109上に所定のパターンの金属配線層110を形成することにより、図3に示すようなMOSFETが形成される。

### [0012]

この半導体装置によれば、ドレイン領域103を高濃度拡散領域103Aと低濃度拡散領域103Bとの2層構造とすることで、ドレイン領域103とチャネルとの間の電界傾斜を緩やかにし、高耐圧を得るようにしている。

【特許文献 1 】特開 2 0 0 0 - 3 4 0 6 7 6 号公報

### 【発明の開示】

【発明が解決しようとする課題】

## [0013]

30

20

10

50

40

20

30

40

50

ところで、図3に示す半導体装置においては、ドレイン領域103の低濃度拡散領域103Bのゲート電極108の下方の端部と、ソース領域104のゲート電極108の下方の端部との距離が、実効ゲート長となる。この実効ゲート長は、図4(a)のBイオン注入工程におけるレジスト121のフォトリソグラフィ工程でのアラインメント精度や、図4(d)のゲート電極108のパターニング精度に依存しており、これらに位置ずれが生ずると、製品毎に実効ゲート長が変動し、特性にばらつきを生じるという問題がある。

[ 0 0 1 4 ]

そこで本発明はこのような従来の実情に鑑みて提案されたものであり、ドレイン領域とチャネルとの間の耐圧が高く、製品毎の実効ゲート長の変動を抑制することが可能な半導体装置を提供することを目的とする。また、本発明は、ドレイン領域とチャネルとの間の耐圧が高い半導体装置を、製品毎の実効ゲート長の変動を抑制して製造することが可能な半導体装置の製造方法を提供することを目的とする。

【課題を解決するための手段】

[0015]

上述の問題を解決するために、本発明に係る半導体装置は、ソース領域と、ドレイン領域と、前記ソース領域と前記ドレイン領域との間のチャネルの上方にゲート酸化膜を介して形成された第1ゲート電極と、前記ドレイン領域の一部の上方及び前記第1ゲート電極の一部の上方に酸化膜を介して形成された第2ゲート電極とを有し、前記ドレイン領域が、深さの深い低濃度拡散領域と、前記低濃度拡散領域と同じ導電型であって前記低濃度拡散領域に設けられた浅い高濃度拡散領域とから構成され、前記ドレイン領域の深さの深い低濃度拡散領域が、前記第1ゲート電極をマスクとするイオン注入により形成され、前記ドレイン領域の浅い高濃度拡散領域の一部を覆って第2ゲート電極が形成され、前記ドレイン領域の浅い高濃度拡散領域及び前記ソース領域は、前記第1ゲート電極及び第2ゲート電極をマスクとするイオン注入により形成されていることを特徴とする。

[0016]

また、本発明の半導体装置の製造方法は、半導体基板上にゲート酸化膜を形成した後、前記ゲート酸化膜上に第1ゲート電極とを形成する工程と、ドレイン領域が形成される領域以外を覆うレジスト及び前記第1ゲート電極をマスクとして、前記半導体基板の前記ドレイン領域が形成される領域にイオン注入し、前記ドレイン領域のうち深さの深い低濃度拡散領域を形成する工程と、前記半導体基板の前記低濃度拡散領域の一部及び前記第1ゲート電極の一部を覆って、第2ゲート電極を形成する工程と、前記第1ゲート電極及び第2ゲート電極をマスクとして、前記低濃度拡散領域及び半導体基板のソース領域が形成される領域に前記低濃度拡散領域と同じ導電型のイオンを注入し、高濃度拡散領域及びソース領域を形成する工程とを有することを特徴とする。

[0017]

本発明の半導体装置では、ドレイン領域に低濃度拡散領域が追加形成されているので、動作時におけるドレイン領域とチャネルとの間の電界傾斜が緩和され、耐圧が高くなる。ただし、このような2層構造を採用した場合、アライメント精度に依存して、実効ゲート長の変動が生じ易い。そこで、本発明では、2層構造のドレイン領域を有する半導体装置において、実効ゲート長を決める一方の端部を構成する低濃度拡散領域を、第1ゲート電極のセルフアラインを利用して深く形成する。また、実効ゲート長を決める他方の端部を構成するソース領域を、第1ゲート電極及び第2ゲート電極のセルフアラインを利用して浅く形成する。このような方法を採用することにより、実効ゲート長のばらつきは、第1ゲート電極の加工精度のみにより決定される。したがって、低濃度拡散領域の端部の位置ずれに起因する実効ゲート長の変動が抑制される。

【発明の効果】

[0018]

本発明の半導体装置によれば、ドレイン領域が低濃度拡散領域と高濃度拡散領域との2層構造を有するので、素子耐圧を高くすることができる。また、本発明の半導体装置によれば、低濃度拡散領域の端部の位置ずれに起因する実効ゲート長の変動が抑制されるので

30

40

50

、素子耐圧が高く、特性のばらつきが小さく、優れた品質の半導体装置を提供することができる。

#### [0019]

また、本発明の半導体装置の製造方法によれば、ドレイン領域が低濃度拡散領域と高濃度拡散領域との2層構造を有する構造とするので、素子耐圧の高い半導体装置を製造することができる。また、本発明の半導体装置の製造方法によれば、ドレイン領域が低濃度拡散領域と高濃度拡散領域との2層構造を有する構造の半導体装置を製造するにあたって、第1ゲート電極によるセルフアラインを利用して低濃度拡散領域及びソース領域の両方を形成するので、低濃度拡散領域の端部の位置ずれに起因する実効ゲート長の変動を抑制することができ、特性のばらつきが小さく、優れた品質の半導体装置を製造することができる。

【発明を実施するための最良の形態】

#### [ 0 0 2 0 ]

以下、本発明に係る半導体装置及びその製造方法について、図面を参照しながら説明する。

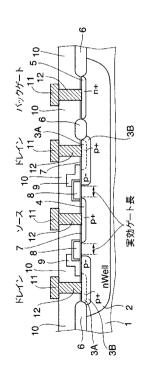

#### [0021]

本発明の半導体装置の一例として、高耐圧MOSFETを構成した半導体装置を、図1に示す。この半導体装置は、ドレイン領域に低濃度拡散領域を追加形成した構造を有している。この半導体装置においては、使用されるシリコン(Si)半導体基板1はp型であり、この表面にn型のウェル(we11)2が深く形成されている。n型ウェル2の表面には、pチャネルのMOSFET(PMOS)が形成されている。n型ウェル2の表面には、PMOSのドレイン領域3として、浅く形成されたp+型の高濃度拡散領域3Aと、高濃度拡散領域3Aより深く形成されたp-型の低濃度拡散領域3Bとが形成されている。また、n型ウェル2にはp+型のソース領域4が浅く形成されている。また、n型ウェル2にバイアス電圧を印加するためのバックゲートであるn+型の拡散領域5が浅く形成されている。

### [0022]

この半導体基板 1 の表面は、素子領域間及びドレイン領域 3 とバックゲート用の n+2 拡散領域 5 との間が、厚いフィールド酸化膜( $SiO_2$ ) 6 によって分離されている。ゲート酸化膜 7 の上には、例えば多結晶シリコンからなる高耐圧 MOSFET 用の第 1 ゲート電極 8 が形成され、第 1 ゲート電極 8 の下方がチャネル領域となる。

## [0023]

また、低濃度拡散領域3B及び第1ゲート電極8の上方に、例えば多結晶シリコンからなる標準耐圧MOSFET用の第2ゲート電極9が形成されている。第2ゲート電極9は、低濃度拡散領域3B及び第1ゲート電極8の両方の一部にまたがるように、段差を有して形成されている。

### [0024]

半導体基板 1 の表面全体には、例えば B P S G 等の絶縁膜 1 0 が積層されている。この絶縁膜 1 0 の上層には、アルミニウム等の金属配線層 1 1 が積層される。金属配線層 1 1 は、絶縁膜 1 0 に形成されたコンタクトホール 1 2 を介して、それぞれドレイン領域 3 の高濃度拡散領域 3 A、ソース領域 4、バックゲート用 n + 拡散領域 5 にそれぞれ接続される。

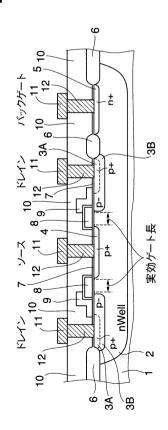

## [ 0 0 2 5 ]

以上のような構成の半導体装置は、例えば、図2に示すようなプロセスにより製造される。先ず、p型シリコン単結晶をウェーハに切り出し、表面を鏡面研磨し、そのウェーハを高温の酸素雰囲気中にさらし、シリコンの酸化膜を成長させた後、フォトレジストを使って酸化膜上にn型ウェルの領域となるパターンを形成し、n型ウェル用不純物をドープし、熱拡散して、半導体基板1の所定の領域にn型ウェル2を形成(n型ウェル形成工程)する。次に、n型ウェル2及び半導体基板1上にゲート酸化膜7、各素子間及びドレイン領域3とバックゲート用のn+型拡散領域5とを分離するフィールド酸化膜(SiO。

20

30

40

50

) 6、並びに第 1 ゲート電極 8 を形成する。第 1 ゲート電極 8 は、ゲート酸化膜 7 上に堆積された 3 結晶シリコン層をフォトリソグラフィ及びエッチングによりパターニングして 形成される。

[0026]

次に、図 2 ( b )に示すように、 n 型ウェル 2 に低濃度拡散領域を形成するために、必要箇所にレジスト 2 0 を形成し、第 1 ゲート電極 8 のセルフアラインを利用してゲート酸化膜 7 を通してボロン( B )イオンを注入する。

[0027]

次いで、図2(c)に示すように、レジスト20を除去し、半導体基板1を熱処理して、上記注入されたBイオンを拡散して、ドレイン領域3のp-型低濃度拡散領域3Bを深く形成する。

[0028]

さらに、図2(d)に示すように、第1ゲート電極8の周囲をSiO<sub>2</sub>等の酸化膜で覆う。それから、低濃度拡散領域3B及び第1ゲート電極8の両方にまたがるように、段差状の構造の第2ゲート電極9を形成する。第2ゲート電極9は、堆積された多結晶シリコン層をフォトリソグラフィ及びエッチングによりパターニングして形成される。

[0029]

次に、図 2 ( e )に示すように、ドレイン領域 3 の低濃度拡散領域 3 B に高濃度拡散領域 3 A を形成するため、及び n 型ウェル 2 にソース領域を形成するため、必要箇所をレジスト 2 1 で覆い、第 1 ゲート電極 8 及び第 2 ゲート電極 9 のセルフアラインを利用して、ゲート酸化膜 7 を通してボロン(B)をイオン注入する。

[0030]

次に、図2(f)に示すように、n型ウェル2にバックゲート用のn+型拡散領域を形成するために、半導体基板1の必要箇所をレジスト22で覆い、レジスト22の開口からゲート酸化膜7を通して、P(リン)をイオン注入する。

[0031]

次に、図2(g)に示すように、半導体基板1を熱処理して、上記注入されたBイオン及びPイオンを拡散して、ドレイン領域3のp+型高濃度拡散領域3A、ソース領域4、及びバックゲート用のn+型拡散領域5を浅く形成する。

[ 0 0 3 2 ]

最後に、半導体基板1の全面に絶縁膜10を積層し、その後絶縁膜10にコンタクトホール12を開け、絶縁膜10上に所定のパターンの金属配線層11を形成することにより、図1に示すようなp-MOSデバイスが形成される。

[0033]

以上により製造される本発明の半導体装置は、動作時において、ドレイン領域3の低濃度拡散領域3Bとチャネルとの間に逆電界が印加されるが、その際に空乏層が生じる。そして、その空乏層はドレイン領域3の低濃度拡散領域3Bの方向へも広がる分が増え、この結果ドレイン領域3とチャネルとの間の電界傾斜が緩和され耐圧を高くしている。

[0034]

また、このPMOSデバイスでは、ドレイン領域3のうち低濃度拡散領域3B及びソース領域4の両方を高耐圧用の第1ゲート電極8とセルフアラインに形成するので、実効ゲート長のばらつきが第1ゲート電極8の加工精度で決定される。したがって、従来のようにイオン注入のためのレジストマスクのフォトリソグラフィが不要となるので、フォトリソグラフィのアラインメント精度による位置ずれの影響がなくなり、低濃度拡散領域3Bのゲート電極側端部の位置ずれに起因する実効ゲート長のばらつきを抑制することができる。

[0035]

なお、上述の説明では、p-MOSを例に挙げたが、本発明は、n-MOSの場合についても同様に適用可能である。

【図面の簡単な説明】

## [0036]

- 【図1】本発明を適用した半導体装置の一例を示す要部概略断面図である。

- 【図2】本発明を適用した半導体装置の製造方法を説明するための要部概略断面図である

- 【図3】従来の半導体装置の一例を示す要部概略断面図である。

- 【図4】従来の半導体装置の製造方法を説明するための要部概略断面図である。

## 【符号の説明】

## [0037]

1 半導体基板、2 n型ウェル、3 ドレイン領域、3 A p + 型高濃度拡散領域、3 B p - 型低濃度拡散領域、4 ソース領域、5 バックゲート用 n + 型拡散領域、6 フィールド酸化膜、7 ゲート酸化膜、8 第 1 ゲート電極、9 第 2 ゲート電極、1 0 絶縁膜、1 1 金属配線層、1 2 コンタクトホール

## 【図1】

【図3】

【図4】

## フロントページの続き

F ターム(参考) 5F140 AA06 AA25 AC01 AC21 BA01 BC06 BF01 BF04 BG37 BH17 BH30 BH43 BH47 BK02 BK13 BK21 BK25 CA03 CC01 CC03 CC07 CD09