# (19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(51) 국제특허분류(Int. Cl.)

*G06F* 12/00 (2006.01) *G06F* 13/14 (2006.01) *G06F* 9/30 (2006.01)

(21) 출원번호 **10-2012-0033541**

(22) 출원일자 **2012년03월30일**

심사청구일자 없음

(30) 우선권주장

13/077,261 2011년03월31일 미국(US)

(11) 공개번호 10-2012-0112265

(43) 공개일자

(71) 출원인

모시스 인코포레이티드

미국 캘리포니아주(우편번호 95054) 산타 클라라 올콧 스트리트 3301

2012년10월11일

(72) 발명자

모리슨, 마이클 제이.

미국 94086 캘리포니아주 서니베일 콘플라워 코트 1072

파텔, 제이 비.

미국 95032 캘리포니아주 로스 가토스 크래이그 웨이 127

(74) 대리인

백만기, 양영준, 정은진

전체 청구항 수 : 총 24 항

## (54) 발명의 명칭 가변 기입 명령 스케쥴링을 포함하는 메모리 시스템

#### (57) 요 약

시스템은 시스템 메모리에 대하여 메모리 요청을 시작하도록 구성될 수 있는 호스트 장치를 포함한다. 시스템은 메모리 요청을 수신하여 메모리 요청을 메모리 인터페이스를 통해 메모리 장치에 전달되는 메모리 트랜잭션으로 포맷하도록 구성될 수 있는 메모리 컨트롤러를 또한 포함한다. 메모리 트랜잭션은 복수의 메모리 기입 명령 타입들을 포함한다. 각각의 메모리 기입 명령 타입은 대응하는 데이터 페이로드를 전달하기 위한 상이한 해당 스케쥴러에 대응한다.

## 대 표 도 - 도1

## 특허청구의 범위

## 청구항 1

메모리 서브시스템으로서,

데이터 저장을 위한 하나 이상의 메모리 어레이를 포함하는 메모리 장치; 및

상기 메모리 장치에 결합되며, 메모리 인터페이스를 통한 메모리 트랜잭션의 수신에 응답하여 상기 데이터를 상기 하나 이상의 메모리 어레이에 독출 및 기입하도록 구성되는 제어부

를 포함하고,

상기 메모리 트랜잭션은 복수의 메모리 기입 명령 타입을 포함하며, 상기 메모리 기입 명령 각각은 대응하는 데이터 페이로드를 전달하기 위한 각각의 스케쥴에 대응하는

메모리 서브시스템.

## 청구항 2

제1항에 있어서.

상기 메모리 트랜잭션 각각은 제1 명령 슬롯 및 제2 명령 슬롯을 갖는 적어도 하나의 프레임을 포함하는 메모리 서브시스템.

#### 청구항 3

제2항에 있어서,

상기 복수의 메모리 기입 명령 타입들 중 하나는 상기 제1 명령 슬롯 또는 상기 제2 명령 슬롯 중 하나에 위치하는 대응하는 메모리 기입 명령을 포함하는 제1 프레임, 상기 대응하는 데이터 페이로드의 제1 부분을 전달하는 제2 프레임, 및 상기 대응하는 데이터 페이로드의 나머지 부분을 전달하는 제3 프레임을 포함하는 메모리 서브시스템.

#### 청구항 4

제2항에 있어서,

상기 복수의 메모리 기입 명령 타입들 중 하나는 상기 제1 명령 슬롯 또는 상기 제2 명령 슬롯 중 하나에 위치하는 대응하는 메모리 기입 명령을 포함하는 제1 프레임, 및 상기 제1 명령 슬롯 내의 대응하는 데이터 페이로 드의 제1 부분과 상기 제2 명령 슬롯 내의 상기 대응하는 데이터 페이로드의 나머지 부분을 전달하는 제2 프레임을 포함하는 메모리 서브시스템.

## 청구항 5

제2항에 있어서.

상기 복수의 메모리 기입 명령 타입들 중 하나는 상기 제1 명령 슬롯 또는 상기 제2 명령 슬롯 중 하나에 위치하는 대응하는 메모리 기입 명령을 포함하는 제1 프레임 및 복수의 후속하는 프레임을 포함하며,

상기 복수의 후속하는 프레임 각각은 상기 제1 명령 슬롯 내의 상기 대응하는 데이터 페이로드의 제1 부분 및 상기 제2 명령 슬롯 내의 상기 대응하는 데이터 페이로드의 나머지 부분을 전달하도록 구성되는 메모리 서브시 스템.

#### 청구항 6

제2항에 있어서.

상기 복수의 메모리 기입 명령 타입들 중 하나는 상기 제1 명령 슬롯 또는 상기 제2 명령 슬롯 중 하나에 위치하는 대응하는 메모리 기입 명령을 포함하는 단일 프레임 및 나머지 명령 슬롯 내의 상기 데이터 페이로드의 부

분을 포함하는 메모리 서브시스템.

#### 청구항 7

제1항에 있어서.

메모리 기입 명령 타입 각각은 각각의 인코딩을 갖는 각각의 메모리 기입 명령을 포함하는 메모리 서브시스템.

#### 청구항 8

제1항에 있어서.

상기 메모리 트랜잭션은 메모리 독출 명령을 더 포함하며,

상기 메모리 기입 명령 타입들 중 적어도 일부는 나머지 명령 슬롯에 위치하는 메모리 독출 명령을 포함하도록 구성되는 메모리 서브시스템.

## 청구항 9

제1항에 있어서,

상기 메모리 트랜잭션은 복수의 메모리 독출-변경-기입 명령 타입을 더 포함하며,

상기 메모리 독출-변경-기입 명령 타입 각각은 상기 메모리 장치 내의 특정 어드레스로부터 독출되어 상기 메모리 장치의 특정 어드레스에 다시 후속하여 기입되는 데이터에 대하여 수행되는 각각의 동작에 대응하며,

상기 독출-변경-기입 명령 타입 각각은 상기 메모리 인터페이스를 통해서 보내지고 있는 하나의 독출-변경-기입 트랜잭션에 대응하는 메모리 서브시스템.

#### 청구항 10

제9항에 있어서,

상기 메모리 장치 내의 상기 특정 어드레스는 상기 제어부의 저장 장치 내에 저장된 베이스 어드레스에 대한 오 프셋을 사용하여 액세스되는 메모리 서브시스템.

## 청구항 11

시스템으로서,

시스템 메모리에 대한 메모리 요청을 시작하도록 구성되는 호스트 장치; 및

상기 호스트 장치에 결합되며, 상기 메모리 요청을 수신하여 상기 메모리 요청을 메모리 인터페이스를 통하여 상기 메모리 장치에 전달되는 메모리 트랜잭션으로 포맷하도록 구성되는 메모리 컨트롤러

를 포함하고,

상기 메모리 트랜잭션은 복수의 메모리 기입 명령 타입을 포함하며, 상기 메모리 기입 명령 타입 각각은 대응하는 데이터 페이로드를 전달하기 위한 각각의 스케쥴에 대응하는

시스템.

## 청구항 12

제11항에 있어서,

상기 복수의 메모리 기입 명령 타입들 중 하나는 제1 명령 슬롯 또는 제2 명령 슬롯 중 하나에 위치하는 대응하는 메모리 기입 명령을 포함하는 제1 프레임, 상기 대응하는 데이터 페이로드의 제1 부분을 전달하는 제2 프레임, 및 상기 대응하는 데이터 페이로드의 나머지 부분을 전달하는 제3 프레임을 포함하는 시스템.

## 청구항 13

제11항에 있어서,

상기 복수의 메모리 기입 명령 타입들 중 하나는 제1 명령 슬롯 또는 제2 명령 슬롯 중 하나에 위치하는 대응하

는 메모리 기입 명령을 포함하는 제1 프레임, 및 상기 제1 명령 슬롯 내의 상기 대응하는 데이터 페이로드의 제 1 부분 및 상기 제2 명령 슬롯 내의 상기 대응하는 데이터 페이로드의 나머지 부분을 전달하는 제2 프레임을 포함하는 시스템.

## 청구항 14

제11항에 있어서,

상기 복수의 메모리 기입 명령 타입들 중 하나는 제1 명령 슬롯 또는 제2 명령 슬롯 중 하나에 위치하는 대응하는 메모리 기입 명령을 포함하는 제1 프레임, 및 복수의 후속하는 프레임을 포함하며, 상기 복수의 후속하는 프레임 각각은 상기 제1 명령 슬롯 내의 상기 대응하는 데이터 페이로드의 제1 부분 및 상기 제2 명령 슬롯 내의 상기 대응하는 데이터 페이로드의 나머지 부분을 전달하도록 구성되는 시스템.

#### 청구항 15

제11항에 있어서,

상기 복수의 메모리 기입 명령 타입들 중 하나는 제1 명령 슬롯 또는 제2 명령 슬롯 중 하나에 위치하는 대응하는 메모리 기입 명령을 포함하는 단일 프레임, 및 나머지 명령 슬롯 내의 데이터 페이로드의 일부를 포함하는 시스템.

## 청구항 16

제11항에 있어서,

상기 메모리 트랜잭션은 복수의 메모리 독출-변경-기입 명령 타입을 더 포함하며,

상기 메모리 독출-변경-기입 명령 타입 각각은 상기 메모리 장치 내의 특정 어드레스부터 독출되어 상기 메모리 장치의 상기 특정 어드레스에 후속하여 다시 기입되는 데이터 상에서 수행되는 각각의 동작에 대응하며,

상기 독출-변경-기입 명령 타입 각각은 상기 메모리 인터페이스를 통해 보내지고 있는 하나의 독출-변경-기입 트랜잭션에 대응하는 시스템.

## 청구항 17

방법으로서,

시스템 메모리에 데이터를 독출하고 기입하기 위한 메모리 요청을 수신하는 단계; 및

상기 메모리 요청을 상기 시스템 메모리에 전달되는 메모리 트랜잭션으로 포맷하는 단계

를 포함하고.

상기 메모리 트랜잭션은 복수의 메모리 기입 명령 타입을 포함하며, 상기 메모리 기입 명령 타입 각각은 대응하는 데이터 페이로드를 전달하기 위한 각각의 스케쥴에 대응하는

방법.

## 청구항 18

시스템으로서,

데이터 저장을 위한 하나 이상의 메모리 어레이를 갖는 메모리 장치를 포함하는 시스템 메모리;

상기 시스템 메모리에 대한 메모리 요청을 시작하도록 구성되는 호스트 장치;

상기 호스트 장치에 결합되며, 상기 메모리 요청을 수신하여 상기 메모리 요청을 메모리 트랜잭션으로 포맷하여 상기 메모리 트랜잭션을 메모리 인터페이스를 통해 보내도록 구성되는 메모리 컨트롤러; 및

상기 메모리 장치에 결합되며, 상기 메모리 트랜잭션의 수신에 응답하여 하나 이상의 메모리 어레이에 데이터를 독출 및 기입하도록 구성되는 제어부

를 포함하고,

상기 메모리 트랜잭션은 복수의 메모리 기입 명령 타입을 포함하며, 상기 메모리 기입 명령 타입 각각은 대응하는 데이터 페이로드를 전달하가 위한 각각의 스케쥴에 대응하는

시스템.

#### 청구항 19

제18항에 있어서,

상기 복수의 메모리 기입 명령 타입들 중 하나는 제1 명령 슬롯 또는 제2 명령 슬롯 중 하나에 위치하는 대응하는 메모리 기입 명령을 포함하는 제1 프레임, 상기 대응하는 데이터 페이로드의 제1 부분을 전달하는 제2 프레임, 및 상기 대응하는 데이터 페이로드의 나머지 부분을 전달하는 제3 프레임을 포함하는 시스템.

#### 청구항 20

제18항에 있어서.

상기 복수의 메모리 기입 명령 타입들 중 하나는 제1 명령 슬롯 또는 제2 명령 슬롯 중 하나에 위치하는 대응하는 메모리 기입 명령을 포함하는 제1 프레임, 및 상기 제1 명령 슬롯 내의 상기 대응하는 데이터 페이로드의 제1 부분 및 상기 제2 명령 슬롯 내의 상기 대응하는 데이터 페이로드의 나머지 부분을 전달하는 제2 프레임을 포함하는 시스템.

#### 청구항 21

제18항에 있어서.

상기 복수의 메모리 기입 명령 타입들 중 하나는 제1 명령 슬롯 또는 제2 명령 슬롯 중 하나에 위치하는 대응하는 메모리 기입 명령을 포함하는 제1 프레임, 및 복수의 후속하는 프레임들을 포함하며,

상기 복수의 후속하는 프레임 각각은 상기 제1 명령 슬롯 내의 상기 대응하는 데이터 페이로드의 제1 부분 및 상기 제2 명령 슬롯 내의 상기 대응하는 데이터 페이로드의 나머지 부분을 전달하도록 구성되는 시스템.

## 청구항 22

제18항에 있어서,

상기 복수의 메모리 기입 명령 타입들 중 하나는 제1 명령 슬롯 또는 제2 명령 슬롯 중 하나에 위치하는 대응하는 메모리 기입 명령을 포함하는 단일 프레임, 및 나머지 명령 슬롯 내의 상기 데이터 페이로드의 일부를 포함하는 시스템.

## 청구항 23

제18항에 있어서,

상기 메모리 트랜잭션은 복수의 메모리 독출-변경-기입 명령 타입을 포함하며,

상기 메모리 독출-변경-기입 명령 타입 각각은 상기 메모리 장치 내의 특정 어드레스로부터 독출되어 상기 메모리 장치의 상기 특정 어드레스에 다시 후속하여 기입되는 데이터에 대하여 수행되는 각각의 동작에 대응하며,

상기 독출-변경-기입 명령 타입 각각은 상기 메모리 인터페이스를 통해 보내지고 있는 하나의 독출-변경-기입 트랜잭션에 대응하는 시스템.

## 청구항 24

제18항에 있어서,

상기 메모리 트랜잭션은 메모리 독출 명령을 더 포함하며,

상기 메모리 기입 명령 타입들 중 적어도 일부는 나머지 명령 슬롯 내에 위치하는 메모리 독출 명령을 포함하도록 구성되는 시스템.

## 명 세 서

## 기 술 분 야

[0001] 본 개시물은 메모리 시스템에 관한 것으로서, 특히, 메모리 인터페이스 상에서의 메모리 명령 스케쥴링에 관한 것이다.

## 배경기술

[0002] 많은 컴퓨터 시스템에 있어서, 다양한 종래의 메모리 인터페이스 및 프로토콜을 사용하여 메모리 장치에 대한 기입과 독출이 행해질 수 있다. 예를 들어, 몇몇 종래의 프로토콜에 있어서는, 메모리 명령, 어드레스, 및 관련 기입 데이터를 전송하기 위하여 별도의 채널들이 존재할 수 있다. 해당 채널에 대한 대역폭 요구에 기초하여 이러한 채널들 각각에 대하여 대역폭이 할당될 수 있다. 이러한 타입의 인터페이스는 단점을 가질 수 있다. 더 구체적으로, 채널 중 일부는 거의 다른 채널들만큼 대역폭을 필요로 하지 않으므로, 채널 중 일부 상에서 대역폭이 소실될 수 있다. 일부 종래의 메모리 프로토콜들은 이에 더한 단점들을 가질 수도 있다. 예를 들어, 기입 명령에 대하여 특정 시간에만 기입 명령에 대한 데이터가 보내질 수 있다. 이러한 타입의 명령 및 데이터스케쥴링은 언제 또한 현재 얼마나 많은 독출 명령 또는 기타의 명령들이 펜딩(pending) 상태인가에 따라서 대역폭을 제한할 수 있다.

## 발명의 내용

## 해결하려는 과제

[0003] 상기 중래 기술의 문제점을 해결할 수 있는 가변 기입 명령 스케쥴링을 포함하는 메모리 시스템을 제공한다.

# 과제의 해결 수단

- [0004] 가변 기입 명령 스케쥴링을 포함하는 메모리 시스템의 다양한 실시예들이 개시된다. 일 실시예에 있어서, 메모리 서브시스템은 메모리 장치와 제어부를 포함한다. 메모리 장치는 데이터 저장을 위한 하나 이상의 메모리 어레이를 포함할 수 있다. 제어부는 메모리 트랜잭션의 수신에 응답하여 하나 이상의 메모리 어레이에 대하여 데이터를 기입 및 독출하도록 구성될 수 있다. 메모리 트랜잭션은 다수의 메모리 기입 명령 타입을 포함한다. 그러나, 각각의 메모리 기입 명령 타입은 대응하는 데이터 페이로드를 전달하기 위한 상이한 스케쥴에 대응한다.

- [0005] 일 특정 구현예에 있어서, 각각의 메모리 트랜잭션은 제1 명령 슬롯과 제2 명령 슬롯을 갖는 적어도 하나의 프레임을 포함한다. 또한, 메모리 기입 명령 타입들 중 하나는 제1 프레임, 제2 프레임, 및 제3 프레임을 포함한다. 제1 프레임은 제1 슬롯 또는 제2 명령 슬롯 중 하나에 위치하는 대응하는 메모리 기입 명령을 포함한다. 제2 프레임은 대응하는 데이터 페이로드의 제1 부분을 전달하며, 제3 프레임은 대응하는 데이터 페이로드의 나머지 부분을 전달한다.

- [0006] 또 다른 특정 구현예에 있어서, 메모리 기입 명령 타입들 중 하나는 제1 프레임과 제2 프레임을 포함한다. 제1 프레임은 제1 명령 슬롯과 제2 명령 슬롯 중 하나에 위치하는 대응하는 메모리 기입 명령을 포함한다. 제2 프레임은 제1 명령 슬롯 내의 대응하는 데이터 페이로드의 제1 부분 및 제2 명령 슬롯 내의 대응하는 데이터 페이로드의 나머지 부분을 전달한다.

- [0007] 또 다른 실시예에 있어서, 시스템은 시스템 메모리에 대한 메모리 요청을 시작하도록 구성될 수 있는 호스트 장치를 포함한다. 시스템은 또한 메모리 요청들을 수신하여 메모리 인터페이스를 통해 메모리 장치에 전달되는 메모리 트랜잭션으로 메모리 요청들을 포맷하도록 구성될 수 있는 메모리 컨트롤러를 포함한다. 메모리 트랜잭션은 복수의 메모리 기입 명령 타입들을 포함한다. 각각의 메모리 기입 명령 타입은 대응하는 데이터 페이로드를 전달하기 위한 상이한 해당 스케쥴에 대응한다.

#### 발명의 효과

[0008] 본 발명에 따르면, 메모리 송수신시의 활용가능한 대역폭을 효율적으로 사용할 수 있다.

#### 도면의 간단한 설명

[0009] 도 1은 메모리 서브시스템을 포함하는 시스템의 일 실시예를 나타낸 블록도이다.

- 도 2는 비한정적인 메모리 트랜잭션 프레임의 일 실시예를 나타낸 도면이다.

- 도 3은 메모리 독출 트랜잭션의 일 실시예를 나타낸 도면이다.

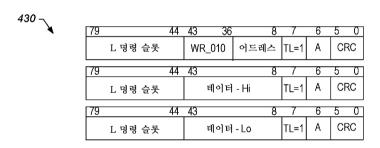

- 도 4a는 메모리 기입 트랜잭션의 일 실시예를 나타낸 도면이다.

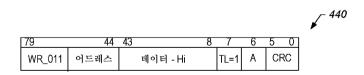

- 도 4b는 5개의 프레임을 포함하는 버스트 메모리 기입 트랜잭션의 일 실시예를 나타낸 블록도이다.

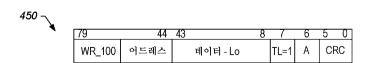

- 도 4c는 메모리 기입 트랜잭션의 또 다른 실시예를 나타낸 도면이다.

- 도 4d는 메모리 기입 트랜잭션의 또 다른 실시예를 나타낸 도면이다.

- 도 4e는 메모리 기입 트랜잭션의 또 다른 실시예를 나타낸 도면이다.

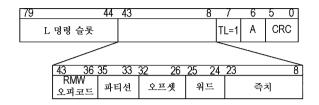

- 도 5는 메모리 독출-변경-기입 트랜잭션의 일 실시예를 나타낸 도면이다.

- 도 6은 도 1에 도시된 시스템의 일 실시예의 동작을 나타낸 흐름도이다.

## 발명을 실시하기 위한 구체적인 내용

- [0010] 특정 실시예들을 도면 내의 예시를 통해서 나타내어, 본 명세서에서 상세하게 설명하고자 한다. 그러나, 도면 과 상세한 설명들은 청구범위를 개시된 특정 실시예들에 한정하고자 한 것은 아니며, 특정한 특징에 대하여는 하나의 실시예만이 설명되어 있다는 것을 이해할 수 있을 것이다. 반면, 이는 본 개시물의 이익을 향유하는 당업자에는 명백한 모든 변경예, 균등물, 및 대체예들을 포괄하고자 의도한 것이다. 개시물에 제공되는 특징의예들은 달리 명시하지 않는 한 한정적이 아니라 예시적인 것을 의도한 것이다.

- [0011] 본 출원서를 통해 사용되는 바와 같이, "할 수도 있다(may)"라는 단어는 의무적인 의미(즉, 해야한다(must)의 의미)가 아니라 허용적인 의미(즉, 잠재적으로 할 수도 있다는 의미)로 사용된다. 마찬가지로, "포함한 (include, including, includes)"라는 단어는 "포함하지만 이에 한하지 않는다"는 뜻이다.

- [0012] 다양한 유닛, 회로, 또는 기타의 성분들을 "작업(task or tasks)"를 수행하도록 "~~하도록 구성되는(configured to)" 것으로 설명할 수 있다. 이러한 문맥에 있어서, "~~하도록 구성되는"은 일반적으로 동작시에 작업 또는 작업들을 수행하는 "회로를 갖는 것"을 의미하는 광의의 구조에 대한 인용이다. 이와 같이, 유닛/회로/성분은 유닛/회로/성분이 현재 온되어 있지 않을 시라도 작업을 수행하도록 구성될 수 있다. 일반적으로, "~~하도록 구성되는"에 대응하는 구조를 형성하는 회로는 하드웨어 회로를 포함할 수 있다. 마찬가지로, 설명의 편의를 위하여, 다양한 유닛/회로/성분들을 작업 또는 작업들을 수행하는 것으로 기재할 수 있다. 이러한 기재는 "~~ 하도록 구성되는"의 어구를 포함하는 것으로 해석되어야 한다. 하나 이상의 작업을 수행하도록 구성되는 유닛/회로/성분을 인용하는 것은 명시적으로는 그 유닛/회로/성분에 대한 미국 특허법 35 U.S.C. § 112, 6장의 해석을 인용하고자 하는 것은 아니다.

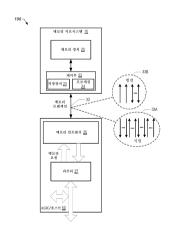

- [0013] 도 1을 참조하면, 메모리 서브시스템을 포함하는 시스템의 일 실시예의 블록도가 도시되어 있다. 시스템(100)은 인터페이스(33)를 통해 메모리 서브시스템(15)에 결합되는 ASIC(Application Specific Integrated Circuit)/호스트(50)를 포함한다. 도시된 실시예에 있어서, ASIC/호스트(50)는 메모리 컨트롤러(25)에 결합되는 라우터(27)를 포함한다. 메모리 서브시스템(15)은 메모리 장치(20)에 결합되는 제어부(22)를 포함한다.

- [0014] 일 실시예에 있어서, ASIC/호스트(50)는 내부 또는 외부 소오스로부터 메모리 요청을 수신할 수 있다. 라우터 (27)는 메모리 요청을 메모리 컨트롤러(25)에 전달할 수 있다. 메모리 컨트롤러(25)는 메모리 요청을 인터페이스(33)를 통해 메모리 서브시스템(15)으로의 전송에 적합한 메모리 트랜재션으로 포맷할 수 있다. 다양한 실시예에 있어서, 메모리 트랜잭션은 메모리 기입 트랜잭션, 메모리 독출 트랜잭션, 및 메모리 독출-변경-기입(RMW: Read-Modify-Write) 트랜잭션을 포함할 수 있다. 도 2 내지 도 5에 도시된 바와 같이, 메모리 트랜잭션은 80-비트의 프레임으로 포맷될 수 있으나, 다른 비트수 또한 가능한 것으로 상정될 수 있다. 일 실시예에 있어서, 트랜잭션 계층에서는 프레임들이 사용될 수 있다.

- [0015] 도 4a 내지 도 4d의 설명과 연계하여 이하에서 더 설명하는 바와 같이, 메모리 기입 트랜잭션은 다수의 상이한 타입의 기입 명령들을 포함할 수 있다. 더 구체적으로, 메모리 컨트롤러(25)는 상이한 데이터 페이로드 스케쥴 링을 갖는 상이한 타입의 기입 명령들을 사용하여 인터페이스(33)를 통한 활용가능한 대역폭을 활용하도록 메모리 기입 트랜잭션을 포맷하도록 구성될 수 있다.

- [0016] 도 1에 있어서, 제어부(22)는 메모리 컨트롤러(25)로부터 메모리 트랜잭션을 수신하여, 상이한 명령 오피코드 (opcode)들을 디코딩하고, 트랜잭션을 리포맷하여, 이들을 메모리 장치(20)에 송신할 수 있다. 따라서, 제어부

(22)는 메모리 장치(20)의 동작과 이에 대한 송수신을 제어하도록 구성될 수 있다. 도시된 바와 같이, 제어부 (22)는 저장부(23)를 포함한다. 일 실시예에 있어서, 저장부(23)는 독출-변경-기입 동작시 사용될 수 있는 다수의 베이스 어드레스(base address)들을 저장할 수 있다. 도 5 및 도 6의 설명과 연계하여 이하에서 더 상세하게 설명하는 바와 같이, 베이스 어드레스는 특수한 기입 프레임(write frame)을 이용하여 기입될 수 있다. 또한, 제어부(22)의 처리부(24)는 메모리 장치(20)로부터 독출된 데이터에 대한 다수의 논리 및 산술연산 함수들을 독출-변경-기입(RMW) 메모리 트랜잭션의 변경 양상의 일부로서 수행하도록 구성된다.

- [0017] 다양한 실시예에 있어서, 인터페이스(33)는 특정 구현예에 따라서 직렬로 상호연결되거나 병렬로 상호연결되어 있을 수 있다. 직렬 상호연결의 구현(예컨대, 33A)의 경우, 인터페이스(33)는 하나 이상의 직렬 채널을 포함할 수 있다. 각각의 채널은 하나 이상의 단방향성 또는 양방향성의 통신 레인을 포함할 수 있다. 단일 직렬 레인의 구현예에 있어서, 주어진 프레임은 레인을 통해 하나의 비트스트림에서 직렬로 송신될 수 있다. 그러나, 채널당 다수의 레인을 포함하는 구현예에 있어서는, 주어진 채널 내의 하나 이상의 레인을 통해 80 비트의 프레임이 전송될 수 있다. 병렬의 구현예(예컨대, 33B)에 있어서, 인터페이스(33)는 병렬 버스를 이루는 다수의 단방향성 명령 및 어드레스 신호 경로들 및 다수의 양방향성 데이터 신호 경로들을 포함할 수 있으며, 80 비트의 프레임은 병렬 버스를 통해 전통적인 병렬 포맷으로 전송될 수 있다. 인터페이스(33)에 대하여 직렬 인터페이스를 사용하는 구현예에 있어서, 메모리 컨트롤러(25)는 다양한 상이한 메모리 트랜잭션들을 인터페이스(33)의 상이한 채널들 상에서 동시에 송신할 수 있다.

- [0018] 메모리 장치(20)는 데이터 저장을 위하여 하나 이상의 메모리 어레이를 포함할 수 있다. 예를 들어, 일 특정 구현예에 있어서, 메모리 장치(20)의 하나 이상의 메모리 어레이들은 1T-SRAM 셀을 사용하여 구현될 수 있다. 일 실시예에 있어서, 메모리 장치(20) 및 제어부(22)는 병렬 상호연결을 통해 결합될 수 있으나, 다른 실시예에 있어서는 임의의 상호연결이 사용될 수 있는 것으로 상정한다. 또한, 메모리 장치(20) 및 제어부(20)는 동일한 IC(Intergrated Circuit) 다이 상에서 구현될 수 있다. 또한, 일 실시예에 있어서, 메모리 서브시스템(15) 및 ASIC/호스트(50)는 또한 동일한 IC 다이 상에서 구현될 수도 있다.

- [0019] 이하에서 더 설명하는 바와 같이, 메모리 컨트롤러(25)는 대역폭 향상을 위하여 상이한 타입의 메모리 트랜잭션들을 활용할 수 있다. 더 구체적으로, 상이한 타입의 메모리 독출 및 기입 트랜잭션들을 사용함으로써, 다양한 메모리 기입 트랜잭션 및 메모리 독출 트랜잭션들이 조합될 수 있으며, 얼마나 많은 데이터가 메모리 장치(20)에 대한 독출 또는 기입에 필요로 하는지에 따라서, 메모리 컨트롤러(25)는 상이한 횟수로 메모리 독출 및 기입명령들 중 다른 하나를 선택할 수 있다.

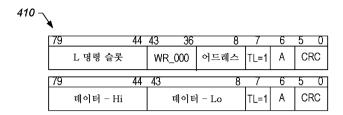

- [0020] 도 2를 참조하면, 비한정적인 메모리 트랜잭션 프레임의 일 실시예를 나타내는 도면이 도시되어 있다. 프레임 (200)은 다수의 필드를 포함하는 80 비트의 프레임이다. 도시된 실시예에 나타낸 바와 같이, 프레임(200)은 비트 0 내지 5에 CRC(Cyclic Redundancy Code) 필드를 포함하고 있다. 비트 6은 ACK 비트에 대응하는 반면, 비트 7은 1의 인코딩이 프레임이 트랜잭션 계층 프레임인 것을 나타내는 트랜잭션 계층 필드에 대응한다. 비트 8 내지 43은 여기서는 R(즉, 우측) 명령 슬롯으로 지정되어 있는 하나의 명령 슬롯에 대응하며, 비트 44 내지 79는 여기서는 L(즉, 좌측) 명령 슬롯으로 지정되어 있는 또 다른 명령 슬롯에 대응한다. 이하에서 더 설명하는 바와 같이, L 명령 슬롯과 R 명령 슬롯 각각은 프레임 내에 또는 선행하는 프레임 내에 어떠한 정보가 있는지에 따라서 독출 명령, 기입 명령, RMW 명령, 또는 데이터에 대응하는 정보를 포함할 수 있다. 다양한 실시예에 있어서, 프레임의 명령 슬롯들 중 하나 또는 양측 모두가 주어진 트랜잭션에서 사용될 수가 있다.

- [0021] 도 3을 참조하면, 메모리 독출 트랜잭션의 일 실시예를 나타낸 도면이 도시되어 있다. 독출 프레임(300)은 독출 명령 오피코드(opcode) 및 어드레스를 포함한다. 도시된 바와 같이, 독출 명령 오피코드 및 어드레스는 독출 프레임(300)의 L 명령 슬롯에 위치된다. 도시된 바와 같이, R 명령 슬롯은 비어있다. 그러나, 다른 실시예에 있어서, 2개의 독출 명령은 하나의 프레임에서 발행될 수 있다. 이와 같이, L 명령 슬롯과 R 명령 슬롯 양측 모두는 독출 명령 오피코드와 관련 어드레스를 포함한다. 또한, 이하에서 더 설명하는 바와 같이, 하나의 명령 슬롯(예컨대, L 명령 슬롯)에 독출 명령이 발행될 수 있으며, 다른 명령 슬롯에 기입 명령이 포함될 수 있다.

- [0022] 다양한 실시예에 있어서, 각각 상이한 타입의 독출 트랜잭션을 지정하는 다수의 상이한 독출 오피코드들이 존재할 수 있다. 예를 들어, 일 실시예에 있어서, 하나의 독출 오피코드가 독출 프레임에 지정된 어드레스에 데이터의 독출 동작을 지정할 수 있다. 따라서, 그 독출 오피코드는 제어부(22)에 대하여 특정된 어드레스에서 독출 동작을 수행하도록 지시할 수 있다. 또 다른 실시예에 있어서, 상이한 독출 오피코드가 특정 길이의 버스트 독출 동작을 지정할 수 있으며, 독출 트랜잭션 내의 어드레스는 버스트의 시작 어드레스일 수 있다.

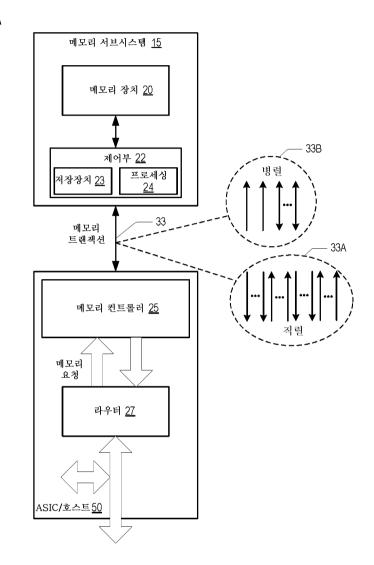

- [0023] 도 4a를 참조하면, 2개의 프레임을 포함하는 메모리 기입 트랜잭션의 일 실시예를 나타낸 도면이 도시되어 있다. 도 3의 독출 트랜잭션 프레임과 마찬가지로, 기입 트랜잭션(410)의 최상부 프레임의 제1 비트 0 내지 7은 CRC 비트와 트랜잭션 계층 지시 비트 등의 다양한 제어 비트들을 포함한다. 도시된 실시예에 있어서, L 명령 슬롯은 비어 있는 반면, R 명령 슬롯은 기입 명령 오피코드 및 어드레스를 포함하고 있다. 그러나, 최하부 프레임에는, 상기 기입 명령에 대한 테이터가 비트 8 내지 79에서 전송되어, 72 비트의 테이터 페이로드를 제공한다. 여기서, 최상부 프레임을 명령 프레임이라 지칭하며, 최하부 프레임을 테이터 프레임이라 지칭한다. 데이터 프레임에 있어서, 테이터 페이로드는 테이터 Hi 및 테이터 Lo로 분해되며, 이 때, 테이터 Hi는 비트 44 내지 79 (예컨대, L 명령 슬롯)에서 전송되며, 데이터 Lo는 비트 8 내지 43 (예컨대, R 명령 슬롯)에서 전송된다. 전술한 바와 같이, 본 실시예에 있어서 명령 프레임의 L 명령 슬롯은 비어 있으므로, 독출 명령은 L 명령 슬롯에 놓여져 있다는 점에 유의한다. 도시된 바와 같이, 기입 명령(WR\_000)은 도 1의 제어부(22)에 대하여 이 기입 명령에 대한 전체 72 비트의 테이터 페이로드가 다음 프레임에 이어서 오게 된다는 것을 지시하는 특정 오피코드 인코딩에 대응한다.

- [0024] 도 4b를 참조하면, 5개의 프레임을 포함하는 버스트 메모리 기입 트랜잭션의 일 실시예를 나타내는 도면이 도시되어 있다. 도시된 실시예에 있어서, 기입 트랜잭션(420)의 최상부 프레임은 명령 프레임이다. 도 4b의 명령 프레임은 도 4a의 명령 프레임과 유사하지만, 이 기입 명령에 대하여는 오피코드 인코딩이 상이하다. 더 구체적으로, 도 4b에 있어서, 기입 명령 오피코드는 WR\_001로 인코딩되어 있다. 일 실시예에 있어서, WR\_001 오피코드는 도 1의 제어부(22)에 대하여 각각 72 비트의 데이터 페이로드를 포함하는 명령 프레임 후에 4개의 후속하는 데이터 페이로드 프레임이 있게 된다는 것을 지시한다. 도 4b에는 4개의 후속하는 데이터 페이로드 프레임이 도시되어 있지만, 다른 실시예에 있어서, 상이한 수의 데이터 페이로드 프레임들이 메모리 컨트롤러(25)에 의해 발행될 수 있는 것으로 상정된다. 도 4a에 도시된 명령 프레임과 마찬가지로, 전술한 바와 같이, L 명령슬롯은 비어 있다. 그러나, L 명령슬롯은, 예를 들어, 독출 또는 기타의 명령 등의 비기입(non-write) 명령을 포함한다. 일 실시예에 있어서, 제어부(22)는 L 명령 슬롯에 독출 명령을 갖는 명령 프레임 수신시, 독출 명령을 먼저 처리한 후 기입 명령을 처리할 수 있다.

- [0025] 도 4c를 참조하면, 3개의 프레임을 포함하는 메모리 기입 트랜잭션의 일 실시예를 나타낸 도면이 도시되어 있다. 도시된 실시예에 있어서, 기입 트랜잭션(430)의 명령 프레임은 도 4b 및 도 4a에 나타낸 명령 프레임과 유사하다. 그러나, 기입 트랜잭션(430)에 있어서, 기입 명령 오피코드는 WR\_010으로 인코딩된다. 따라서, 일실시예에 있어서, 이러한 인코딩은 제어부(22)에 대하여 다음 2개의 후속하는 프레임에 있어서 한번에 하나의 36비트의 하프 워드(half word)씩 데이터 페이로드가 전송되게 된다는 것을 지시한다. 그러나, 도 4c에 도시된 바와 같이, 데이터 Hi 하프 워드는 다음의 후속하는 프레임에서 전송되는 반면, 데이터 Lo 하프 워드는 두번째 후속하는 프레임에서 전송된다. 다시, 트랜잭션(430)의 모든 3개의 프레임 중에서, L 명령 슬롯은 비어 있다. 그러나, 전술한 바와 같이, 이러한 L 명령 슬롯들 각각에는 비기입 명령이 삽입될 수 있다. 따라서, 메모리 컨트롤러(25)는, 예를 들어, 독출 명령 등의 명령을 이러한 프레임 각각에 삽입함으로써 활용가능한 대역폭을 활용할 수 있다.

- [0026] 도 4d를 참조하면, 기입 트랜잭션의 또 다른 실시예를 나타낸 도면이 도시되어 있다. 도시된 실시예에 있어서, 트랜잭션(440)은 L 명령 슬롯에 기입 명령 오피코드를 포함하고 R 명령 슬롯에 데이터 페이로드를 포함하는 하나의 프레임을 포함한다. 도시된 바와 같이, 기입 명령은 WR\_011로 인코딩된다. 도시된 실시예에 있어서, 데이터 페이로드는 하프 워드로서 보내진다. 더 구체적으로, 데이터 Hi 하프 워드는 R 명령 슬롯에서 보내진다. 따라서, 기입 오피코드(WR\_011)은 제어부(22)에 대하여 72 비트의 데이터 페이로드의 상부 하프 워드만이 현재 프레임에서 전송되고 있다는 것을 지시한다.

- [0027] 도 4e를 참조하면, 기입 트랜잭션의 또 다른 실시예를 나타낸 도면이 도시되어 있다. 도 4d의 트랜잭션(440)과 마찬가지로, 도 4e의 트랜잭션(450)은 L 명령 슬롯에 기입 명령 오피코드를 포함하고 R 명령 슬롯에 데이터 페이로드를 포함하는 하나의 프레임을 포함한다. 그러나, 도 4e에 있어서, 기입 오피코드는 WR\_100으로 인코딩된다. 도 4e의 실시예에 있어서, 데이터 페이로드 또한 하프 워드로서 보내진다. 더 구체적으로, 데이터 Lo 하프 워드는 R 명령 슬롯에서 보내진다. 따라서, 기입 오피코드(WR\_100)는 제어부(22)에 대하여 72 비트의 데이터 페이로드의 하부 하프 워드만이 현재의 프레임에서 전송되고 있다는 것을 지시한다.

- [0028] 일 실시예에 있어서, 도 4d 및 도 4e에 나타낸 트랜잭션은 원하는 바에 따라 함께 또는 분리되어 사용될 수 있다. 따라서, 도 4a 내지 도 4e에 도시된 상기 실시예들로부터, 메모리 컨트롤러(25)는 다양한 상이한 타입의 기입 명령들을 사용함으로써 활용가능한 대역폭을 가장 잘 사용할 수 있다.

- [0029] 또 다른 실시예에 있어서, 하프 워드 기입 트랜잭션은 추가의 방법으로 수행될 수 있다. 더 구체적으로, 메모리 컨트롤러(25)는 하프 워드 기입을 수행하기 위하여 추가의 기입 오피코드를 사용할 수 있으며, 여기서, 기입 오피코드는 상부 또는 하부의 하프 워드 중 어느 것이 보내지고 있는지를 지정할 수 있다. 일 실시예에 있어서, R 명령 슬롯에서 기입 명령이 보내질 수 있으며, 데이터의 하프 워드는 다음 프레임의 R 명령 슬롯 또는 L 명령 슬롯에서 보내지게 된다. 이러한 실시예에 있어서, 기입 오피코드는 데이터 페이로드가 데이터 Hi 하프 워드인지 또는 데이터 Lo 하프 워드 인지와 R 명령 슬롯 또는 L 명령 슬롯 중 어느 것을 데이터가 점유하게 되는지를 지정할 수 있다.

- [0030] 도 5를 참조하면, 하나의 프레임을 포함하는 독출-변경-기입 트랜잭션의 일 실시예를 나타낸 도면이 도시되어 있다. 도 3의 독출 트랜잭션 프레임 및 도 4a 내지 도 4e의 기입 트랜잭션 프레임들과 마찬가지로, RMW 트랜잭션(500)의 최상부 프레임의 제1 비트 0 내지 7은 CRC 비트들 및 트랜잭션 계층 지시 비트와 같은 각종 제어 비트들을 포함한다. 도시된 실시예에 있어서, L 명령 슬롯은 비어 있는 반면, R 명령 슬롯은 RMW 명령 오피코드를 포함한다. 그러나, 독출 및 기입 명령 프레임에서와 같이 어드레스 필드 내의 어드레스와는 달리, RMW 어드레싱이 상이하다. 도 5의 실시예에 있어서, 비트 8 내지 35는 16 비트의 중간 오퍼랜드(operand)를 포함하며, 비트 24 내지 35는 2 비트의 워드 인코딩을 포함하며, 비트 26 내지 32는 7 비트의 오프셋을 포함하며, 비트 33 내지 35는 3 비트의 파티션 인코딩을 포함한다.

- [0031] 도 1의 시스템(100)에 있어서, RMW 트랜잭션은 메모리 데이터가 최소수의 메모리 트랜잭션이 인터페이스(33)를 통해 보내지도록 하여 변경되도록 할 수 있다. 예를 들어, 인터페이스(33)를 통해 보내지는 하나의 RMW 트랜잭션은 특정 주소의 데이터가 변경되도록 한다. 메모리 어드레스들은 도 1의 저장장치(23)에 프리로딩(preload)될 수 있는 베이스 어드레스에 대한 오프셋으로서 주어질 수도 있다.

- [0032] 일 실시예에 있어서, RMW 변경 연산은 포화 가감산(saturating addition subtraction) 및 모듈로-2<sup>n</sup> (modulo 2<sup>n</sup>) 가감산 등의 가감산 연산을 포함하는 16 비트, 32 비트,및 64비트의 ALU(Arithmetic Logic Unit) 연산을 포함한다. 또한, AND, OR, 및 XOR(Exclusive-OR) 등의 논리 연산들이 수행될 수도 있다. 또한, 시프트, 비교, 증분, 감분, 등의 다양한 다른 산술연산 또는 논리연산이 수행될 수 있다. 또한, 이러한 상이한 타입의 RMW 연산 각각은 대응하는 RMW 명령 오피코드 인코딩을 가질 수 있다. 일 실시예에 있어서, 제어부(22)는 이러한 연산들을 수행하기 위한 처리 기능(24) 등을 포함할 수 있다.

- [0033] 도 5를 다시 참조하면, 일 실시예에 있어서, RMW 명령 각각은 프레임의 비트 [23:8] 중에서 16 비트의 즉치 (immediate) 오퍼랜드와 RMW 오피코드에 의해 지정된 바와 같은 메모리 장치(20) 내의 어드레스에 저장된 16 비트, 32 비트, 또는 64 비트의 오퍼랜드와의 사이의 연산을 수행한다. 일단 메모리 오퍼랜드가 변경되었다면, 제어부(22)는 그 결과를 메모리 장치에 다시 기입한다. 메모리 어드레스는 오프셋 필드(예컨대, 비트 [32:26])와 저장장치(23)에 앞서 로딩된 베이스 어드레스와의 조합(예컨대, 가산, XOR, 등)에 의해 계산될 수 있다. 파티션 필드(예컨대, 비트 [35:33])는 저장장치(23) 내에 저장될 수 있는 베이스 어드레스 중 하나를 선택한다. 데이터의 크기와 정렬은 워드(Word) 필드와 조합하여 RMW 오피코드에 의해 판정될 수 있다. 더 구체적으로, 16 비트 및 32 비트의 RMW 명령에 있어서 워드(Word) 값은 메모리 오퍼랜드 중 어느 비트가 데이터인지를 판정할 수 있는 반면, 64 비트의 RMW 명령에 있어서 워드(Word) 필드는 데이터가 모두 64 비트임을 의미하므로 무시된다.

- [0034] 또 다른 실시예에 있어서, 하나 이상의 추가의 RMW 오피코드는 연산되어야 하는 가변 데이터 크기를 지정할 수 있다. 더 구체적으로, 하나의 RMW 오피코드는 메모리 오퍼랜드의 2개의 상이한 부분들 상에서 수행되는 2개의 상이하며 독립적인 연산을 지정할 수 있다. 예를 들어, 하나의 이러한 RMW 오피코드는 메모리 오퍼랜드의 하나의 부분이 40 비트가 되며, 다른 부분이 24 비트가 되는 것을 지정할 수 있다. 또한, 동일한 RMW 오피코드는 제어부(22)가, 예를 들어, 24비트의 부분 상에서 증분 또는 감분 등의 하나의 연산을 수행하며, 예를 들어, 40 비트의 부분 상에서 프레임의 16 비트의 즉치 오퍼랜드와의 XOR 등의 또 다른 연산을 수행하도록 지정할 수 있다. 따라서, 하나의 RMW 오피코드에 있어서, 2개의 독립적인 연산이 메모리 오퍼랜드로부터 데이터 중 2개의 상이한 부분(동일 또는 상이한 크기) 상에서 수행될 수 있다. 여기서, 메모리 오퍼랜드 상에서 수행될 수 있는 전술한 바와 같은 임의의 연산은 양측 부분에서 수행될 수 있다.

- [0035] 전술한 바와 같이, 저장장치(23)는 다수의 기입 베이스 어드레스들을 다수의 저장 위치에 유지할 수 있다. 메모리 컨트롤러(25)는 도 3 내지 도 5에 도시된 프레임들과 유사할 수 있는 기입 베이스 명령(write base command) 프레임을 사용하여 메모리 베이스 어드레스들을 저장장치(23)에 로딩할 수 있다. 더 구체적으로, 일

실시예에 있어서, 기입 베이스 명령 프레임은 표준 프레임의 둘 중 어느 하나의 명령 슬롯 내에 기입 베이스 명령을 포함할 수 있다. 기입 베이스 명령은 기입 베이스 오피코드, 베이스 어드레스, 및 파티션을 포함할 수 있다. 기입 베이스 명령 프레임 수신시, 제어부(22)는 프레임 내의 베이스 어드레스를 저장 위치 중 하나에 기입할 수 있다.

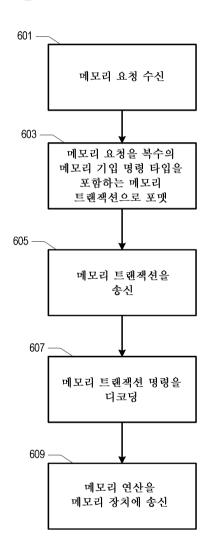

- [0036] 도 6을 참조하면, 도 1의 시스템의 실시예의 동작을 나타내는 흐름도가 도시되어 있다. 블록 601에서 시작하여, 메모리 컨트롤러(25)는 라우터(27)로부터 메모리 요청을 수신한다. 메모리 컨트롤러(25)는 메모리 요청을 메모리 트랜잭션으로 포맷한다(블록 603). 전술한 바와 같이, 활용가능한 대역폭 및 기타의 인자에 따라서, 메모리 컨트롤러(25)는 데이터를 메모리 장치(20)에 기입하기 위해 메모리 기입 명령들 중 임의의 것을 사용할 수 있다. 더 구체적으로, 상기 도면들에서 전술한 바와 같이, 다수의 미처리(outstanding) 독출 요청 및 기입 요청이 존재하면, 예를 들어, 메모리 컨트롤러(25)는 동일한 명령 프레임 내에 독출 명령을 포함하는 능력뿐만 아니라 기입 명령들의 스케쥴링 가변성을 활용할 수 있다. 다른 방법으로서, 데이터의 버스트가 존재하면, 메모리 컨트롤러(25)는 도 28에 나타낸 바와 같이 메모리 기입 버스트 명령을 활용할 수 있다. 전술한 바와 같이, 하나 이상의 기입 프레임, 독출 프레임, 및/또는 RMW 프레임들이 트랜잭션 계층에서 포맷될 수 있다.

- [0037] 일단 메모리 트랜잭션이 포맷되어 있으면, 메모리 컨트롤러(25)는 인터페이스(33)를 통해 메모리 트랜잭션을 메모리 서브시스템(15)에 전송할 수 있다(블록 605). 인터페이스(33) 상의 물리 계층을 통해서 포맷된 프레임들이 보내질 수 있다.

- [0038] 메모리 트랜잭션 명령의 수신시, 제어부(22)는 각 프레임 내의 명령들을 디코딩한다(블록 607). 일단 명령이 디코딩되면, 제어부(22)는 명령을 리포맷하여 이를 메모리 장치(20)에 보낼 수 있다(블록 609). 더 구체적으로, 기입 명령의 경우, 제어부(22)는 데이터를 메모리 장치(20)의 어드레스에 보낼 수 있다. 독출 명령의 경우, 제어부는 메모리 장치(20) 상에서 독출 동작을 수행할 수 있으며, 요청된 데이터가 메모리 장치(20)에 의해 리턴되는 때에, 제어부(22)는 요청된 데이터를 메모리 컨트롤러(25)에 되돌려 보낼 수 있다. 그러나, RMW 명령의 경우, 제어부(22)는 RMW 프레임 내의 정보로부터 제어부(22)에 의해 계산되는 바와 같이 특정 메모리 어드레스의 독출 동작을 수행할 수 있다. 제어부(22)는 그 후 RMW 오피코드에 지정된 바와 같이 독출 데이터를 변경할 수 있으며, 그 후, 변경된 데이터를 메모리 장치(20)의 어드레스에 다시 기입할 수 있다.

- [0039] 상기 실시예들을 상세하게 설명하였지만, 상기 개시 내용을 충분히 이해한다면 다양한 변형예와 변경예들이 당업자에 대하여 명백할 것이다. 이하의 청구항들은 이러한 모든 변형예와 변경예들을 포괄하는 것으로 해석되고자 의도한 것이다.

# 도면

# 도면1

# 도면2

| 79 |         | 44 4 | 3       | 8 | 7    | 6 | 5 0 |

|----|---------|------|---------|---|------|---|-----|

|    | L 명령 슬롯 |      | R 명령 슬롯 |   | TL=1 | Α | CRC |

# 도면3

| ı | 79         | . 44 | 43 |         | 8 | 7    | 6 | 5  | 0  |

|---|------------|------|----|---------|---|------|---|----|----|

|   | 독출<br>오피코드 | 어드레스 |    | R 명령 슬롯 |   | TL=1 | Α | CF | 3C |

# 도면4a

## 도면4b

| 79 |          | 44 | 43 36  | 8    | 7    | 6 | 5 0 | <sub>_</sub> - 420 |

|----|----------|----|--------|------|------|---|-----|--------------------|

|    | L 명령 슬롯  |    | WR_001 | 어드레스 | TL=1 | Α | CRC | •                  |

| 79 |          | 44 | 43     | 8    | 7    | 6 | 5 0 |                    |

|    | 데이터 - Hi |    | 데이터    | - Lo | TL=1 | Α | CRC |                    |

| 79 |          | 44 | 43     | 8    | 7    | 6 | 5 0 |                    |

|    | 데이터 - Hi |    | 테이터    | - Lo | TL=1 | Α | CRC |                    |

| 79 |          | 44 | 43     | 8    | 7    | 6 | 5 0 |                    |

|    | 데이터 - Hi |    | 테이터    | - Lo | TL=1 | Α | CRC |                    |

| 79 |          | 44 | 43     | 8    | 7    | 6 | 5 0 |                    |

|    | 데이터 - Hi |    | 데이터    | - Lo | TL=1 | Α | CRC |                    |

# *도면4c*

# 도면4d

# *도면4e*

# 도면5

# 도면6