(19) **日本国特許庁(JP)**

# (12) 特許公報(B2)

(11)特許番号

特許第4904625号 (P4904625)

(45) 発行日 平成24年3月28日 (2012.3.28)

(24) 登録日 平成24年1月20日(2012.1.20)

神奈川県川崎市川崎区田辺新田1番1号

富士電機株式会社内

| (51) Int.Cl. |        |           | FΙ   |       |      |

|--------------|--------|-----------|------|-------|------|

| HO1L         | 29/739 | (2006.01) | HO1L | 29/78 | 655B |

| HO1L         | 29/78  | (2006.01) | HO1L | 29/78 | 653A |

| HO1L         | 21/336 | (2006.01) | HO1L | 29/78 | 658A |

|              |        |           | HO1L | 29/78 | 658G |

請求項の数 6 (全 12 頁)

最終頁に続く

| (21) 出願番号 | 特願2001-36353 (P2001-36353)    | (73)特許権者 000005234 |                    |  |

|-----------|-------------------------------|--------------------|--------------------|--|

| (22) 出願日  | 平成13年2月14日 (2001.2.14)        |                    | 富士電機株式会社           |  |

| (65) 公開番号 | 特開2002-246597 (P2002-246597A) |                    | 神奈川県川崎市川崎区田辺新田1番1号 |  |

| (43) 公開日  | 平成14年8月30日 (2002.8.30)        | (74) 代理人           | 100150441          |  |

| 審査請求日     | 平成19年7月17日 (2007.7.17)        |                    | 弁理士 松本 洋一          |  |

|           |                               | (72) 発明者           | 脇本 博樹              |  |

|           |                               |                    | 神奈川県川崎市川崎区田辺新田1番1号 |  |

|           |                               |                    | 富士電機株式会社内          |  |

|           |                               | (72) 発明者           | 吉川 功               |  |

|           |                               |                    | 神奈川県川崎市川崎区田辺新田1番1号 |  |

|           |                               |                    | 富士電機株式会社内          |  |

|           |                               | (72) 発明者           | 上野 勝曲              |  |

(54) 【発明の名称】半導体装置

# (57)【特許請求の範囲】

## 【請求項1】

第1導電型半導体基板の第1主面の表面層に、選択的に形成された第2導電型ベース領域 と、該第2導電型ベース領域の表面層に選択的に形成された第1導電型エミッタ領域と、 該第1導電型エミッタ領域と前記第1導電型半導体基板に挟まれた前記第2導電型ベース 領域上にゲート絶縁膜を介して形成されたゲート電極と、前記第1導電型エミッタ領域上 と前記第2導電型ベース領域上に形成されたエミッタ電極と、前記第1導電型半導体基板 を150μm以下に薄くした第2主面の表面層に形成された厚さが1μm以下の第2導電 型コレクタ領域と、該第2導電型コレクタ領域上に形成されたコレクタ電極とを具備する 半導体装置であって、

前記第2導電型コレクタ領域と離して前記第1導電型半導体基板の不純物濃度より高い 不純物濃度で、第1導電型半導体基板内に形成された第1導電型フィールドストップ領域 とを有し、該第1導電型フィールドストップ領域と前記第2導電型コレクタ領域との間が 前記第1導電型半導体基板の不純物濃度の領域で分離されていることを特徴とする半導体 装置。

## 【請求項2】

第1導電型半導体基板の第1主面の表面層に、選択的に形成された第2導電型ベース領域 と、該第2導電型ベース領域の表面層に選択的に形成された第1導電型エミッタ領域と、 該第1導電型エミッタ領域と前記第1導電型半導体基板に挟まれた前記第2導電型ベース 領域上にゲート絶縁膜を介して形成されたゲート電極と、前記第1導電型エミッタ領域上

と前記第 2 導電型ベース領域上に形成されたエミッタ電極と、前記第 1 導電型半導体基板を 1 5 0 μm以下に薄くした第 2 主面の表面層に形成された<u>厚さが 1 μm以下の</u>第 2 導電型コレクタ領域と、該第 2 導電型コレクタ領域上に形成されたコレクタ電極とを具備する半導体装置であって、

前記第 2 導電型コレクタ領域と離して前記第 1 導電型半導体基板の不純物濃度より高い不純物濃度で、第 1 導電型半導体基板内に形成された第 1 導電型フィールドストップ領域とを有し、該第 1 導電型フィールドストップ領域の不純物ピーク濃度が 1 0 <sup>1 5</sup> ~ 1 0 <sup>1</sup> <sup>7</sup> c m <sup>3</sup> であり、該第 1 導電型フィールドストップ領域と前記第 2 導電型コレクタ領域との間が前記第 1 導電型半導体基板の不純物濃度より1桁以内の不純物濃度高さの領域で分離されていることを特徴とする半導体装置。

10

## 【請求項3】

前記第1導電型フィールドストップ領域が離れて複数個形成されることを特徴とする請求項1または2に記載の半導体装置。

## 【請求項4】

前記第 2 導電型コレクタ領域の表面から前記第 1 導電型半導体基板内に到達するように形成された複数個の溝と、該溝内を充填する絶縁膜と、該溝の各先端部に個別に形成された前記第 1 導電型フィールドストップ領域とを有することを特徴とする請求項 3 に記載の半導体装置。

## 【請求項5】

前記第1導電型フィールドストップ領域の前記第2主面に投影した平面形状が、格子状であることを特徴とする請求項1または2に記載の半導体装置。

20

#### 【請求項6】

前記第1導電型フィールドストップ領域の前記第2主面に投影した平面形状が、セル状も しくはストライプ状であることを特徴とする請求項3または4に記載の半導体装置。

#### 【発明の詳細な説明】

## [0001]

#### 【発明の属する技術分野】

この発明は、電力変換装置などに用いられる絶縁ゲート型バイポーラトランジスタ(以下、IGBTと称す。IGBT: Insulated Gate Bipolar Transisitor)などの半導体装置に関する。

30

#### [0002]

#### 【従来の技術】

近年、600~1200 V 耐圧の I G B T などの M O S 制御型の電力用半導体デバイスでは、動作時のエネルギー損失の低減と、ウェハコストの削減のために、エピタキシャル基板よりも安価な F Z ( F l o t i n g Z o n e ) 基板を用いて、その F Z 基板の厚さを  $150\mu$  m以下と極めて薄く加工し、デバイスを作り込む技術が脚光を浴びている。特に、耐圧が 1200 V クラスの I G B T では、オン電圧や順阻止耐圧などで、良好な電気的特性が得られるフィールドストップ ( F i e l d S t o p ) 型 I G B T (以下、 F S - I G B T と称す ) と呼ばれる I G B T が注目されている。

## [0003]

40

50

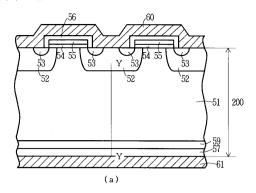

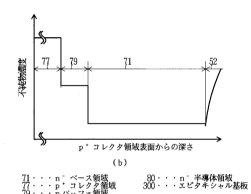

図7は、従来のFS-IGBTであり、同図(a)は要部断面図、同図(b)は同図(a)のY-Y線上での不純物濃度分布図である。

同図(a)において、n<sup>-</sup> 半導体基板 2 0 0 の第 1 主面側の表面層に p ベース領域 5 2 を形成し、 p ベース領域 5 2 の表面層に n<sup>+</sup> エミッタ領域 5 3 を形成し、 n<sup>-</sup> 半導体基板 2 0 0 と n<sup>+</sup> エミッタ領域 5 3 に挟まれた p ベース領域 5 2 上にゲート絶縁膜 5 4 を介してゲート電極 5 5 を形成し、その上に層間絶縁膜 5 6 を形成し、 n<sup>+</sup> エミッタ領域 5 3 上と p ベース領域 5 2 上にエミッタ電極 6 0 を形成する。その上に図示しないパッシベーション膜を被覆する。

## [0004]

一方、 n <sup>-</sup> 半導体基板 2 0 0 の第 2 主面側の表面層に n 型 F S 領域 5 9 を形成し、この

n型FS領域59の表面層にp<sup>+</sup>コレクタ領域57を形成し、p<sup>+</sup>コレクタ領域57上にコレクタ電極61を形成する。n<sup>-</sup>半導体基板200の各領域が形成されない領域が、n<sup>-</sup>ベース領域51となる。

この従来のFS-IGBTでは、前記したように、エミッタ電極60が形成される前に、コレクタ側のウエハ表面に、リンイオンなどの n 型不純物とボロンイオンなどの p 型不純物をイオン注入により打ち込み、400 程度の低温で熱処理して電気的に活性化して、 n 型FS領域59と p <sup>+</sup> コレクタ領域57を形成する。以下に説明するこれらの領域の不純物濃度は、活性化した不純物濃度のことである。

#### [0005]

この従来のFS-IGBTは、エピタキシャル基板を用いて形成した従来のパンチスルー型IGBT(PT-IGBT)の数百μmの厚いコレクタ領域を1μm以下と極めて薄くした構造であり、従って、全体の半導体基板200の厚さも150μm以下と極めて薄くなっている。

同図(b)において、空乏層の伸びを抑えるフィールドストップ領域となるn型FS領域59を形成する。このn型FS領域59は、従来のエピタキシャル基板を用いたパンチスルー型IGBT(以下、PT-IGBTという)のnバッファ領域よりも不純物濃度が低いことが特徴である。その理由をつぎに説明する。

#### [0006]

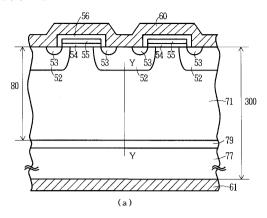

図8は、従来のエピタキシャル基板を用いたパンチスルー型IGBT(PT-IGBT)であり、同図(a)は要部断面図、同図(b)はY-Y線上での不純物濃度分布図である。

図8に示すように、従来のエピタキシャル基板300を用いたPT-IGBTでは、数百μmと厚い高濃度のp+コレクタ領域77となるp+半導体基材上に、比較的高濃度の空乏層をストップさせるnバッファ領域79をエピタキシャル成長で形成する。このnバッファ領域79上に低濃度のn・半導体領域80を形成し、このn・半導体領域80の表面層にpベース領域52やn+エミッタ領域53などを形成する。このn・半導体領域80のpベース領域52を形成しない領域がn・ベース領域71となる。

#### [0007]

この n バッファ領域 7 9 の不純物濃度を比較的高い値にするのは、不純物濃度が極めて高い  $p^+$  コレクタ領域 7 7 からの正孔の注入を抑え、空乏層の伸びを完全に止めるためである。

また、 $p^+$  コレクタ領域 7 7 の不純物濃度を極めて高い値にするのは、 $p^+$  コレクタ領域 7 7 の厚さが数百  $\mu$  m と厚いために、小さなオン電圧(VCE(sat))を得るためには、この  $p^+$  コレクタ領域 7 7 の抵抗を極めて小さな値にしなければならないからである。

## [0008]

一方、従来のFS-IGBTでは、順阻止状態では空乏層の伸びを、 $p^+$  コレクタ領域 5 7 に接して形成される n 型FS領域 5 9 で、ストップするために、 $p^+$  コレクタ領域 5 7 の厚さを  $p^+$  コレクタ領域 5 7 の不純物濃度を、 $p^+$  コレクタ領域 5 7 の不純物濃度を低くすることで、オン状態で  $p^+$  コレクタ領域 5 7 からの  $p^+$  コレクタ領域 5 1 に蓄積されるキャリア量を、 $p^+$  1 G B T と比べて小さくできる。

#### [0009]

n ベース領域 5 1 に蓄積されるキャリア量を少なくすることで、ライフタイムキラーの導入なしでターンオフ時間を短縮できる。また、ライフタイムキラーの導入がないことで、オン電圧を小さくできる。

また、p<sup>+</sup> コレクタ領域57からの正孔の注入効率を所定の値にするために、n型FS 領域59の不純物濃度をp<sup>+</sup> コレクタ領域57の不純物濃度より小さくする必要がある。 その結果、n型FS領域59の不純物濃度は、PT-IGBTのnバッファ領域79の不 純物濃度に比べて低い値となる。このことがFS-IGBTの特徴である。 10

20

30

40

#### [0010]

## 【発明が解決しようとする課題】

しかし、この従来のFS-IGBTのp<sup>+</sup> コレクタ領域57は、前記したように、PT-IGBTのp<sup>+</sup> コレクタ領域77と比べて不純物濃度が低く、厚さが大幅に薄く、また、nバッファ領域79に相当するn型FS領域59の不純物濃度も低いために、p<sup>+</sup> コレクタ領域57やn型FS領域59に部分的な欠損(欠落箇所)が生じ易い。

#### [0011]

イオン注入前に、コレクタ側のウエハの表面に付着したごみ・ほこりなどにより n 型 F S 領域 5 9 の一部分でも形成されない箇所(欠損箇所)があると、 p ベース領域 5 2 側からから伸びてきた空乏層が容易に p <sup>+</sup> コレクタ領域 5 7 にパンチスルーして、 I G B T の耐圧が劣化する。

また、 $p^+$  コレクタ領域 5 7 が形成されない箇所があると、n 型 F S 領域 5 9 の不純物 濃度が通常の p n ダイオードの n 領域と比べて大幅に高くなっているために、 $p^+$  コレクタ領域 5 7 と n 型 F S 領域 5 9 からなる p  $p^+$  コレクタ領域 5 7 から n 型  $p^+$  S 領域 5 9 への正孔の注入が起こり難くなり、オン電圧が上昇する。

#### [0012]

この発明の目的は、前記の課題を解決して、  $p^+$  コレクタ領域と n 型 F S 領域の部分的な欠損が、オン電圧特性や耐圧特性に及ぼす影響を小さくできる半導体装置を提供することにある。

#### [0013]

#### 【課題を解決するための手段】

前記の目的を達成するために、第1導電型半導体基板の第1主面の表面層に、選択的に形成された第2導電型ベース領域と、該第2導電型ベース領域の表面層に選択的に形成された第1導電型エミッタ領域と、該第1導電型エミッタ領域と前記第1導電型半導体基板に挟まれた前記第2導電型ベース領域上にゲート絶縁膜を介して形成されたゲート電極と、前記第1導電型エミッタ領域上と前記第2導電型ベース領域上に形成されたエミッタ電極と、前記第1導電型半導体基板を150μm以下に薄くした第2主面の表面層に形成された厚さが1μm以下の第2導電型コレクタ領域と、該第2導電型コレクタ領域上に形成されたコレクタ電極とを具備する半導体装置であって、

前記第2導電型コレクタ領域と離して前記第1導電型半導体基板の不純物濃度より高い不純物濃度で、第1導電型半導体基板内に形成された第1導電型フィールドストップ領域とを有し、該第1導電型フィールドストップ領域と前記第2導電型コレクタ領域との間が前記第1導電型半導体基板の不純物濃度の領域で分離されている構成とする。

# [0014]

また、第1導電型半導体基板の第1主面の表面層に、選択的に形成された第2導電型ベース領域と、該第2導電型ベース領域の表面層に選択的に形成された第1導電型エミッタ領域と、該第1導電型エミッタ領域と前記第1導電型半導体基板に挟まれた前記第2導電型ベース領域上にゲート絶縁膜を介して形成されたゲート電極と、前記第1導電型エミッタ領域上と前記第2導電型ベース領域上に形成されたエミッタ電極と、前記第1導電型半導体基板を150μm以下に薄くした第2主面の表面層に形成された厚さが1μm以下の第2導電型コレクタ領域と、該第2導電型コレクタ領域上に形成されたコレクタ電極とを具備する半導体装置であって、

前記第 2 導電型コレクタ領域と離して前記第 1 導電型半導体基板の不純物濃度より高い不純物濃度で、第 1 導電型半導体基板内に形成された第 1 導電型フィールドストップ領域とを有し、該第 1 導電型フィールドストップ領域の不純物ピーク濃度が 1 0 <sup>1 5</sup> ~ 1 0 <sup>1</sup> <sup>7</sup> c m <sup>3</sup> であり、該第 1 導電型フィールドストップ領域と前記第 2 導電型コレクタ領域との間が前記第 1 導電型半導体基板の不純物濃度より1桁以内の不純物濃度高さの領域で分離されている構成とする。

#### [0015]

20

10

30

40

また、前記第1導電型フィールドストップ領域が離れて複数個形成されるとよい。

また、前記第2導電型コレクタ領域の表面から前記第1導電型半導体基板内に到達するように形成された複数個の溝と、該溝内を充填する絶縁膜と、該溝の各先端部に個別に形成された前記第1導電型フィールドストップ領域とを有するとよい。

[0016]

## [0017]

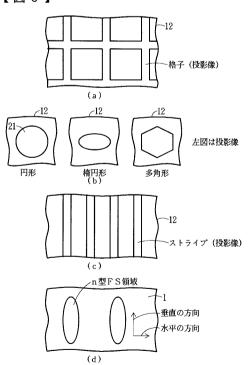

<u>また、</u>前記第1導電型フィールドストップ領域<u>の</u>前記第2主面に投影した平面形状が、 格子状であるとよい。

また、前記第1導電型フィールドストップ領域の前記第2主面に投影した平面形状が、 セル状もしくはストライプ状であるとよい。

[0018]

#### 【発明の実施の形態】

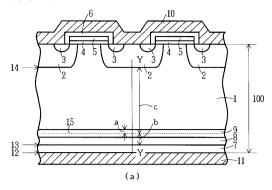

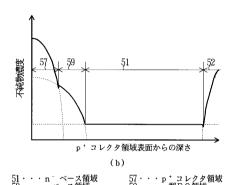

図1は、この発明の第1実施例の半導体装置であり、同図(a)は要部断面図、同図(b)は同図(a)のY-Y線上での不純物濃度分布(拡散プロフィル)図である。従来のFS-IGBTとの違いは、p<sup>+</sup>コレクタ領域7とn型FS領域9が接していない点である。また、以下の実施例では、ゲート部分がトレンチ構造であっても同様の効果がある。

#### [0019]

同図(a)において、n~半導体基板100の第1主面側の表面層にpベース領域2を形成し、このpベース領域2の表面層にn<sup>+</sup> エミッタ領域3を形成する。n<sup>-</sup> 半導体基板100(n<sup>-</sup> ベース領域1)とn<sup>+</sup> エミッタ領域3に挟まれたpベース領域2上にゲート絶縁膜4を介してゲート電極5を形成し、その上に層間絶縁膜6を形成し、層間絶縁膜にコンタクトホールを開けて、前記のn<sup>+</sup> エミッタ領域3上とpベース領域2上にエミッタ電極10を形成する。その後、表面に図示しないパッシベーション膜を被覆する。

#### [0020]

一方、n・半導体基板 1 0 0 の第 2 主面から所定の深さに、空乏層の伸びを抑える働きがあるn型FS領域 9 を形成し、このn型FS領域 9 より低い不純物濃度で、n型FS領域 9 と第 2 主面の間にn領域 8 を形成し、このn領域 8 の表面層に、n型FS領域 9 と離してp<sup>+</sup> コレクタ領域 7 を形成し、p<sup>+</sup> コレクタ領域 7 上にコレクタ電極 1 1 を形成する。n・半導体基板 1 0 0 の各領域が形成されない領域が n・ベース領域 1 となる。

## [0021]

前記のn型FS領域9とp<sup>+</sup> コレクタ領域7およびn領域8は、リンイオンなどのn型不純物およびボロンイオンなどのp型不純物をイオン注入し、400 程度の低温で熱処理してイオン注入された不純物を活性化する。以下の説明で、これらの領域の不純物濃度は、熱処理した後の活性化した不純物濃度のことである。

#### [0022]

尚、図1(a)のn型FS領域9のp<sup>+</sup> コレクタ領域表面12に投影した平面形状は、全面がn型FS領域9であるが、図6(a)に示すような格子状をしていてもよい。

同図(b)において、n型FS領域9がp<sup>+</sup> コレクタ領域7に接しないようにするためには、n型FS領域9の不純物濃度ピーク位置15(不純物濃度がピークとなる位置のこと)からn<sup>-</sup> ベース領域と同等の不純物濃度になる位置まで(n<sup>-</sup> ベース領域1とn型FS領域9とのpn接合の位置)の距離aよりも、n型FS領域の不純物濃度ピーク位置15からp<sup>+</sup> コレクタ領域7とn領域8とのp/n接合(以下、コレクタp/n接合13と称す)までの距離bを大きくする。つまり距離bに対するに対しています。

## [0023]

通常の工程では、  $p^+$  コレクタ領域表面 1 2 からコレクタ p / n 接合 1 3 までの距離(  $p^+$  コレクタ領域の厚さ)は 0 . 2 ~ 0 . 3  $\mu$  m、  $p^+$  コレクタ領域表面 1 2 から n 型 F S 領域 9 の不純物濃度ピーク位置 1 5 は 0 . 8 ~ 1  $\mu$  m程度である。コレクタ p / n 接合 1 3 と n 型 F S 領域 9 が接する場合には、 n 型 F S 領域の半分の厚み(距離 a に相当する)は、 0 . 5 ~ 0 . 8  $\mu$  m となる。従って、距離 b が 0 . 8  $\mu$  m より大きい値(  $p^+$  3  $p^+$  5 領域 9 とは接することはない。

10

20

30

40

#### [0024]

n型FS領域9がpベース領域2に近すぎると、n型FS領域9内が空乏化してしまう可能性があるため、pベース領域2のボトム(pベース領域2とn・ベース領域1のp/n接合(以下、ベースp/n接合14と称す))からn型FS領域9の不純物濃度ピーク位置15までの距離cに対して、距離bを20%程度以下にすることが必要がある。

## [0025]

また、前記の n 型 F S 領域 9 の不純物ピーク濃度が高すぎると、オン電圧の上昇を招くので、  $p^+$  コレクタ領域 7 の不純物ピーク濃度より n 型 F S 領域 9 の不純物ピーク濃度を 2 桁程度以上小さくなるように、設定するのが好ましい。しかし、この n 型 F S 領域 9 の不純物ピーク濃度の高さ(図中、番号 1 5 の位置での濃度の高さ)は、 n 型 F S 領域 9 が完全に空乏化しない程度にすることが望ましい。

#### [0026]

また、前記の $p^+$  コレクタ領域 7 を形成するために、イオン注入した不純物原子は、 4 0 0 程度以下の低温で熱処理(アニール)し、活性化させるが、通常、この活性化した不純物ピーク濃度を 1 0  $^{17}$  c m  $^{-3}$  ~ 1 0  $^{19}$  c m  $^{-3}$ 程度にすることができる。従って、 n 型 F S 領域 9 の不純物ピーク濃度は 1 0  $^{15}$  ~ 1 0  $^{17}$  c m  $^{-3}$  程度とすることが好ましい。

#### [0027]

また、 $p^+$  コレクタ領域 7 と n 型 F S 領域 9 のそれぞれに接して、これらの領域の間に形成される n 領域 8 の不純物ピーク濃度は、 $n^-$  半導体基板 1 0 0 ( $n^-$  ベース領域 1) の不純物濃度より多少高く(1 桁以内の高さ)、n 型 F S 領域 9 の不純物ピーク濃度より低く設定する。

この n 領域 8 は、空乏層が n 型 F S 領域 9 を突き抜けた場合や n 型 F S 領域 9 に部分的な欠損があった場合に、 p \* コレクタ領域 7 に空乏層が到達しないようにする働きと、 p \* コレクタ領域 7 からの正孔の注入を抑制する働きがある。従って、 n 型 F S 領域 9 により、空乏層が p \* コレクタ領域 7 に達せず、且つ、 p \* コレクタ領域 7 からの正孔の注入を抑制する必要がなければ、この n 領域 8 は形成しなくても構わない。また、図 1 では、 n 領域 8 が n 型 F S 領域 9 に接しているが、接しなくても構わない。

#### [0028]

前記の $p^+$  コレクタ領域 7 と離してn型 F S 領域 9 を形成するには、n 型不純物を高エネルギーで加速して、深くイオン注入し、低温の熱処理で活性化させる方法と、エピタキシャル成長による方法がある。イオン注入法では 1  $\mu$  m程度の深さ程度であるが、エピタキシャル成長による方法では、 $p^+$  コレクタ領域表面 1 2 から任意の深さに、n 型 F S 領域 9 を形成することができる。しかし、n 型 F S 領域 9 を深くし過ぎると、前記のように、n ベース領域 1 の幅が狭くなる。その結果、前記のように、n 型 F S 領域内が空乏化してしまう可能性が生じるため、 $p^+$  コレクタ領域表面からの深さを 1 0  $\mu$  m程度以下にすることが望ましい。

## [0029]

本発明のFS-IGBTでは、p<sup>+</sup> コレクタ領域7と離してn型FS領域9を形成し、これらに挟まれた箇所に低濃度のn領域8を形成することで、順阻止状態においては、従来のFS-IGBTと同様に、空乏層をn型FS領域9でストップさせて、耐圧を確保し、一方、オン状態では、p<sup>+</sup> コレクタ領域7に低濃度のn領域8が接しているために、この箇所はノンパンチスルー型IGBT(NPT-IGBT)のコレクタ側と類似しており、p<sup>+</sup> コレクタ領域7からの正孔の注入効率が低下せず、オン電圧を小さくできる。

## [0030]

また、この構造では、 $p^+$  コレクタ領域 7 の部分的な欠損が、オン電圧に与える影響を小さくできる。それは、 $p^+$  コレクタ領域 7 と接する n 領域 8 の不純物濃度が低いために、部分的に $p^+$  コレクタ領域 7 が欠損しても、容易に $p^+$  コレクタ領域 7 と n 領域 8 の  $p^+$  1 レクタ領域 7 から n 領域 8 へ正孔が注入されるためである。

## [0031]

10

20

30

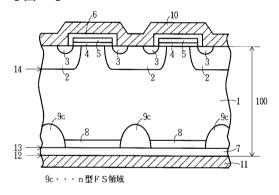

図 2 は、この発明の第 2 実施例の半導体装置の要部断面図である。図 1 との違いは n 型 F S 領域 9 a が複数個に分割されている点である。

$p^+$  コレクタ領域 7 と離して、部分的に n 半導体基板 1 0 0 の不純物濃度よりも大きい不純物濃度ピークを持つ n 型 F S 領域 9 a が複数個、離して、 n ベース領域 1 に埋め込まれるように形成され、この n 型 F S 領域 9 a と  $p^+$  コレクタ領域 7 の間に、 n 型 F S 領域と離して、 n 型 F S 領域 9 a の不純物濃度より低い n 領域 8 を形成する。この埋め込まれた n 型 F S 領域 9 a と n 型 領域 8 は、空乏層の伸びを抑える働きをして、 n 型 F S 領域 9 a のない領域での  $p^+$  コレクタ領域 7 へ、空乏層が達する電圧(パンチスルー電圧)を高めることができる。また、前記したように、コレクタ p / n 接合 1 3 から n 型 p S 領域 9 a の不純物濃度ピーク位置 1 5 までの距離 p は 0 . 8 p m 以上であることが望ましい

10

20

30

#### [0032]

また、ベース p / n 接合 1 4 から n 型 F S 領域 9 a の不純物濃度ピーク位置 1 5 までの距離 c に対して、 n 型 F S 領域 9 a の不純物濃度ピーク位置 1 5 からコレクタ p / n 接合 1 3 までの距離 b が、 2 0 % 程度以下で、十分空乏層の伸びを抑制する効果がある。

[0033]

また、 n 型 F S 領域 9 a の面積割合が小さい場合には、オン電圧の上昇の割合が小さくなるため、 n 型 F S 領域 9 a の不純物ピーク濃度を高くして順阻止耐圧を向上させることができる。

また、この構造では、前記したように、n領域8が低濃度であるため、コレクタ側の構造は、NPT-IGBTに近い構造となり、従来のFS-IGBTより、 $p^+$ コレクタ領域の一部分が欠損しても、オン電圧に及ぼす影響は小さい。尚、前記したように、n型FS領域9aにより、空乏層が $p^+$ コレクタ領域7に達せず、且つ、 $p^+$ コレクタ領域7からの正孔の注入を抑制する必要がなければ、このn領域8は形成しなくても構わない。

#### [0034]

40

## [0035]

また、前記したように、空乏層の伸びを抑るためには、ベース p / n 接合 1 4 から n 型 F S 層 9 b の不純物濃度ピーク位置 1 5 までの距離 c に対して、 n 型 F S 層 9 b の不純物ピーク位置 1 5 からコレクタ p / n 接合 1 3 までの距離 b が、 2 0 %程度以下で十分である。また、前記したように、 n 型 F S 領域 9 b の面積割合が十分小さい場合には、オン電圧が上昇する割合が小さいため、 n 型 F S 領域 9 b の不純物濃度ピーク濃度を高くすることで、順阻止耐圧を向上させることができる。

#### [0036]

この構造は、溝16を形成した後、イオン注入、または、n型不純物を含有した材料を埋め込み、拡散によってn型FS領域9bとn領域8を形成し、最後に溝16を絶縁材1

### [0037]

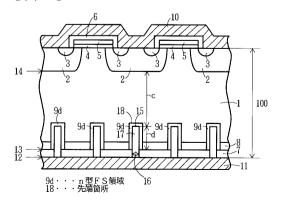

図 4 <u>は</u>、この発明の<u>第 1 参考例</u>の半導体装置の要部断面図である。図 1 から図 3 までとの違いは、複数個形成された n 型 F S 領域 9 c が p  $^+$  コレクタ領域 7 に接している点である。この n 型 F S 領域 9 c の不純物濃度は、前記したように、順阻止状態で完全に空乏化しない程度の濃度とすることが望ましい。n 型 F S 領域 9 c の面積割合が十分小さい場合にはオン電圧が上昇する割合が小さいため、n 型 F S 領域 9 c の不純物ピーク濃度を、高くすることで、順阻止耐圧を向上させることができる。

#### [0038]

また、n型FS領域9cの平面形状は、セル状およびストライプ状のいずれでも良い。この構造においても、順阻止状態では、n型FS領域9cにより、n型FS領域9cがない箇所の空乏層の伸びが抑制され、空乏層が $p^+$  コレクタ領域7に到達し難くなり、耐圧が確保しやすい。この空乏層の伸びは、前記のn 領域8を形成することで、さらに抑えられて、耐圧の確保が容易になる。しかし、空乏層の伸びがn型FS領域9cにより $p^+$  コレクタ領域7へ達せず、且つ、 $p^+$  コレクタ領域7からの正孔の注入を抑制する必要がないならば、このn 領域8は形成しなくても構わない。

## [0039]

## [0040]

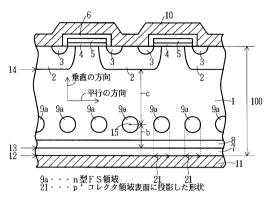

図5は、この発明の<u>第2参考例</u>の半導体装置の要部断面図である。コレクタ側からn・半導体基板100に形成された溝16に絶縁材17が埋め込まれ、それを囲むようにn型FS領域9dが形成されている。またp・コレクタ領域7と接するように、n型FS領域9dより不純物濃度が低いn領域8が形成されている。n型FS領域9dの不純物濃度は、順阻止状態で空乏化しない程度の濃度が望ましい。

## [0041]

また、溝16の深さを深くすることにより、 n型FS領域9 d の p \* コレクタ領域表面 1 2 からの深さを深くすることが可能であるが、空乏層の伸びを効果的に抑えるためには、ベース p / n 接合 1 4 から n 型FS層 9 d の不純物濃度ピーク位置 1 5 までの距離 c に対して、先端箇所 1 8 の n 型FS層 9 d の不純物ピーク位置 1 5 からコレクタ p / n 接合 1 3 までの距離 b が、 2 0 % 程度以下で十分である。

#### [0042]

前記したように、 n 型 F S 領域 9 d の面積割合が十分小さい場合には、オン電圧が上昇する割合が小さいため、 n 型 F S 領域 9 d の不純物濃度  $\underline{o}$  ピーク濃度  $\underline{e}$  高くすることで、順阻止耐圧を向上させることができる。

また、 n 型 F S 領域 9 d o n 平面形状は、 セル状およびストライプ状のいずれでも良い。 また、前記したように、 n 領域 8 は、空乏層の伸びが n 型 F S 領域 9 d により p  $^+$  コレクタ領域 7 に達せず、且つ、 p  $^+$  コレクタ領域 9 d からの正孔の注入を抑制する必要がなければ、形成しなくても構わない。

## [0043]

#### 【発明の効果】

この発明によれば、p<sup>+</sup> コレクタ領域に、n型FS領域を接しないように形成し、p<sup>+</sup> コレクタ領域とn型FS領域の間に低濃度のn領域を形成することで、p<sup>+</sup> コレクタ領域、n型FS領域の部分的な欠損が、オン電圧および順阻止耐圧に及ぼす影響を小さくでき

10

20

30

40

```

る。

```

[0044]

【図面の簡単な説明】

- 【図1】 この発明の第1実施例の半導体装置であり、(a)は要部断面図、(b)は(

- a ) の Y Y 線上での不純物濃度分布図

- 【図2】 この発明の第2実施例の半導体装置の要部断面図

- 【図3】 この発明の第3実施例の半導体装置の要部断面図

- 【図4】 この発明の第1参考例の半導体装置の要部断面図

- 【図5】 この発明の第2参考例の半導体装置の要部断面図

- 【図6】 n型FS領域の形状で、(a)は格子状の図、(b)はセル状の図、(c)は 10 ストライプ状の図、(d)は楕円状の図

- 【図7】 従来のFS-IGBTであり、(a)は要部断面図、(b)は(a)のY-Y 線上での不純物濃度分布図

- 【図8】 従来のエピタキシャル基板を用いたパンチスルー型IGBT(PT-IGBT )であり、(a)は要部断面図、(b)はY-Y線上での不純物濃度分布図

#### 【符号の説明】

- 1 n <sup>·</sup> ベース領域

- 2 pベース領域

- 3 n <sup>+</sup> エミッタ領域

- 4 ゲート絶縁膜

- 5 ゲート電極

- 層間絶縁膜 6

- 7 p <sup>+</sup> コレクタ領域

- 8 n領域

- 9、9a、9b、9c、9d n型FS領域

- 1 0 エミッタ電極

- 1 1 コレクタ電極

- 1 2 p <sup>†</sup> コレクタ領域表面

- 1 3 コレクタp/n接合

- 1 4 ベース p / n 接合

- 不純物濃度ピーク位置 1 5

- 1 6 溝

- 1 7 絶縁材

- 先端箇所 1 8

- 2 1 p <sup>+</sup> コレクタ領域表面に投影した形状

- 1 0 0 n · 半導体基板

20

# 【図1】

# b c c 15 a 14 2 2 13 p コレクタ領域表面からの深さ (b)

# 【図4】

# 【図5】

# 【図2】

# 【図3】

【図6】

【図7】

【図8】

## フロントページの続き

## 審査官 崎間 伸洋

(56)参考文献 特開平06-204481 (JP,A)

特開平10-154755 (JP,A)

特開平09-139353(JP,A)

特開平04-010640(JP,A)

特開平03-261179(JP,A)

特開平09-162398 (JP,A)

特開昭63-127572(JP,A)

特開平03-044969(JP,A)

特開平10-092841(JP,A)

特開平01-045173(JP,A)

特開2002-305305(JP,A)

# (58)調査した分野(Int.CI., DB名)

H01L 29/739

H01L 21/336

H01L 29/78