# (19) 国家知识产权局

# (12) 发明专利申请

(10) 申请公布号 CN 117452110 A (43) 申请公布日 2024.01.26

H02H 9/04 (2006.01) H02J 7/00 (2006.01) H01M 10/42 (2006.01)

(21)申请号 202311411929.9

(22)申请日 2023.08.22

(62) 分案原申请数据

202311060871.8 2023.08.22

(71) 申请人 成都利普芯微电子有限公司 地址 610000 四川省成都市中国(四川) 自 由贸易试验区成都高新区和乐一街71 号4栋2单元19层1901

- (72) 发明人 高兴波 唐永生 黄立

- (74) 专利代理机构 成都立新致创知识产权代理 事务所(特殊普通合伙) 51277

专利代理师 刘俊

(51) Int.CI.

G01R 31/00 (2006.01)

权利要求书1页 说明书9页 附图4页

#### (54) 发明名称

干扰检测电路和电池保护芯片

#### (57) 摘要

本发明实施例提供了一种干扰检测电路和电池保护芯片,涉及集成电路技术领域,该干扰检测电路包括:用于接收干扰信号的包括PN结的检测元件以及干扰判断子电路,当检测元件的PN结受到干扰信号时,PN结的漏电流快速增大,本发明基于这一特性将现有包括PN结的半导体元件作为检测元件,干扰判断子电路基于检测元件截止时的漏电大小判断检测元件是否受到干扰,以此快速自检出电路受到干扰信号影响的情况。

1.一种干扰检测电路,其特征在于,包括:

用于接收干扰信号的包括PN结的检测元件:

干扰判断子电路,基于所述检测元件截止时的漏电大小判断所述检测元件是否受到干扰。

2.根据权利要求1所述的干扰检测电路,其特征在于,

所述干扰判断子电路包括:采样模块和比较模块;

所述采样模块基于所述检测元件截止时漏电产生检测信号:

所述比较模块基于所述检测信号与检测阈值判断所述检测元件是否受到干扰,并在确定所述检测元件受到干扰时输出干扰标志信号。

- 3.根据权利要求2所述的干扰检测电路,其特征在于,所述采样模块包括与所述检测元件串联的第一电阻元件,基于所述第一电阻元件与所述检测元件截止时漏电以产生所述检测信号。

- 4.根据权利要求3所述的干扰检测电路,其特征在于,其中,所述第一电阻元件与所述检测元件之间的连接节点用于产生所述检测信号。

- 5.根据权利要求2所述的干扰检测电路,其特征在于,所述采样模块包括与所述检测元件串联的第一MOS元件,基于所述第一MOS元件与所述检测元件截止时漏电以产生所述检测信号。

- 6.根据权利要求5所述的干扰检测电路,其特征在于,

所述第一MOS元件的漏端或源端用于与所述检测元件串联,所述第一MOS元件的栅端用于接其漏端或接能使所述第一MOS元件导通的外部输入电压Vb;

其中,基于所述第一MOS元件与所述检测元件截止时漏电以产生所述检测信号。

7.根据权利要求6所述的干扰检测电路,其特征在于,

其中,所述第一MOS元件与所述检测元件连接的漏端或源端用于产生所述检测信号。

8.根据权利要求2所述的干扰检测电路,其特征在于,

所述采样模块包括电容元件和复位单元:

所述电容元件与所述检测元件串联,所述电容元件接收所述检测元件流出的漏电流产 生所述检测信号;

所述复位单元按照预设时间间隔将所述电容元件的电压复位至初始状态。

9.根据权利要求2-8任一项所述的干扰检测电路,其特征在于,

所述比较模块包括负载元件和第二MOS元件;其中,所述检测阈值为所述第二MOS元件的导通阈值;

所述负载元件与所述第二MOS元件的源端或漏端连接形成串联电路,所述第二MOS元件的栅端基于所述检测信号与所述导通阈值控制所述串联电路是否导通,以输出所述干扰标志信号。

10.一种电池保护芯片,其特征在于,包括:如权利要求1-9所述的干扰检测电路。

# 干扰检测电路和电池保护芯片

[0001] 本发明是申请日为2023年08月22日,题为"干扰检测电路、静电释放保护电路和电池保护芯片",申请号为202311060871.8的专利申请的分案申请。

#### 技术领域

[0002] 本发明涉及集成电路技术领域,具体涉及一种干扰检测电路和电池保护芯片。

### 背景技术

[0003] 随着如集成电路等电路系统的日益精密、复杂以及多功能化,电路系统易受如射频、电磁干扰的影响,使得其性能和电路稳定性受到影响。

[0004] 现有的电路系统无法快速自检出干扰信号,依靠外部的干扰检测仪来检测干扰信号,不仅存在干扰检测的准确性和及时性的问题,还致使后端电路的抗干扰电路设计受到挑战。

#### 发明内容

[0005] 本发明实施例提供一种干扰检测电路和电池保护芯片,至少可以快速自检出干扰信号,克服前述问题。

[0006] 从第一方面,本发明实施例公开了一种干扰检测电路,包括:

[0007] 用于接收干扰信号的包括PN结的检测元件;

[0008] 干扰判断子电路,基于检测元件截止时的漏电大小判断检测元件是否受到干扰。

[0009] 在本发明一实施例中,干扰判断子电路包括:采样模块和比较模块;

[0010] 采样模块基于检测元件截止时漏电产生检测信号;

[0011] 比较模块基于检测信号与检测阈值判断检测元件是否受到干扰,并在确定检测元件受到干扰时输出干扰标志信号。

[0012] 在本发明一实施例中,采样模块包括与检测元件串联的第一电阻元件,基于第一电阻元件与检测元件截止时漏电以产生检测信号。

[0013] 在本发明一实施例中,其中,第一电阻元件与检测元件之间的连接节点用于产生检测信号。

[0014] 在本发明一实施例中,采样模块包括与检测元件串联的第一MOS元件,基于第一MOS元件与检测元件截止时漏电以产生检测信号。

[0015] 在本发明一实施例中,第一MOS元件的漏端或源端用于与检测元件串联,第一MOS元件的栅端用于接其漏端或接能使第一MOS元件导通的外部输入电压Vb;其中,基于第一MOS元件与检测元件截止时漏电产生检测信号。

[0016] 在本发明一实施例中,其中,第一MOS元件用于与检测元件连接的漏端或源端用于产生该检测信号。

[0017] 在本发明一实施例中,采样模块包括电容元件和复位单元;

[0018] 电容元件与检测元件串联,电容元件接收检测元件流出的漏电流产生检测信号;

2/9 页

[0019] 复位单元按照预设时间间隔将电容元件的电压复位至初始状态。

[0020] 在本发明一实施例中,比较模块包括负载元件和第二MOS元件;其中,检测阈值为 第二MOS元件的导通阈值:

[0021] 负载元件与第二MOS元件的源端或漏端连接形成串联电路,第二MOS元件的栅端基 于检测信号与导通阈值控制串联电路是否导通,以输出干扰标志信号。

[0022] 在本发明一实施例中,负载元件为电阻。

[0023] 在本发明一实施例中,比较模块包括:

[0024] 阈值电压产生子单元,用于产生检测阈值;

[0025] 比较器,用于将检测信号与检测阈值进行比较,以输出干扰标志信号。

[0026] 在本发明一实施例中,干扰检测电路还包括:buffer子电路;

[0027] buffer子电路用于将于扰判断子电路在确定检测元件受到于扰时输出的于扰标 志信号增强后输出。

[0028] 从第二方面,本发明实施例还公开了一种电池保护芯片,包括:如本发明实施例所 述的干扰检测电路。

[0029] 本发明实施例包括以下优点:

[0030] 本发明实施例提供了一种干扰检测电路,包括:用于接收干扰信号的包括PN结的 检测元件以及干扰判断子电路,当检测元件的PN结受到干扰信号时,PN结的漏电流快速增 大,本发明基于这一特性将现有包括PN结的半导体元件作为检测元件,干扰判断子电路基 于检测元件截止时的漏电大小判断检测元件是否受到干扰,以此快速自检出电路受到干扰, 信号影响的情况。

#### 附图说明

[0031] 为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现 有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本 发明的一些实施例。

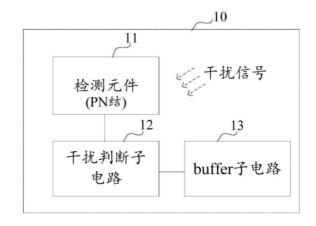

[0032] 图1是本发明一种干扰检测电路的框图示意图;

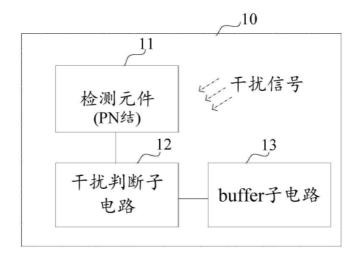

[0033] 图2是本发明一实施例的干扰检测电路的示意图:

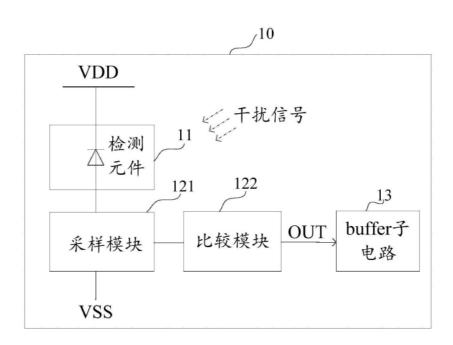

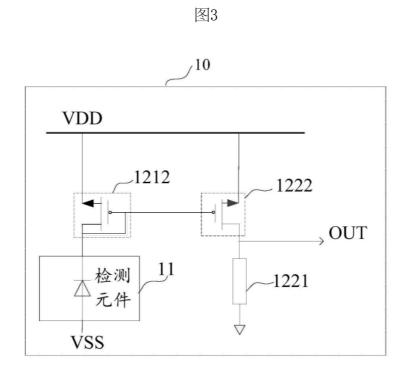

[0034] 图3是图2所示实施例的干扰检测电路的电路示意图一;

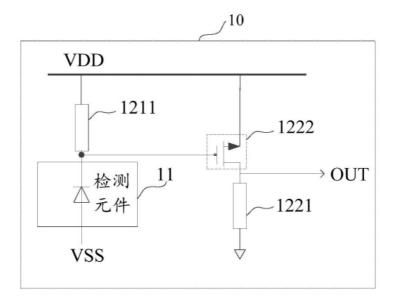

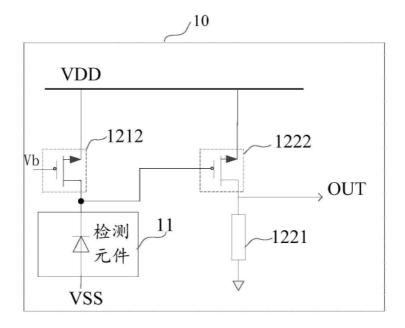

[0035] 图4是图2所示实施例的干扰检测电路的电路示意图二;

[0036] 图5是图2所示实施例的干扰检测电路的电路示意图三;

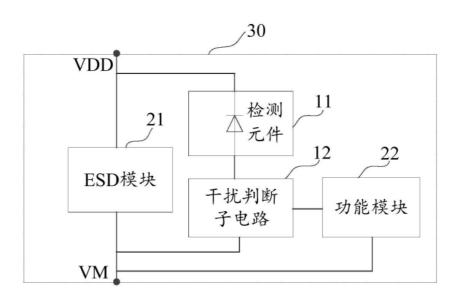

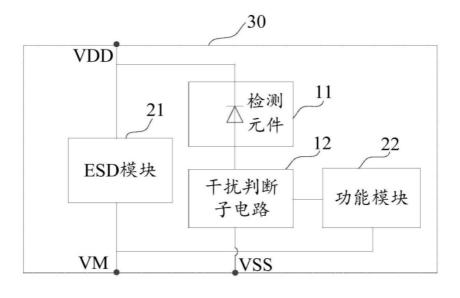

[0037] 图6是本发明一实施例一种电池保护芯片的框图示意图;

[0038] 图7是本发明另一实施例一种电池保护芯片的框图示意图。

[0039] 附图标记说明:

[0040] 10-干扰检测电路;11-检测元件,12-干扰判断子电路,13-buffer子电路;121-采 样模块,122-比较模块,1211-第一电阻元件,1212-第一MOS元件,1221-负载元件,1222-第 二MOS元件:

21-ESD模块,22-功能模块; [0041]

30-电池保护芯片。 [0042]

## 具体实施方式

[0043] 下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。

[0044] 本发明提供了一种干扰检测电路10,如图1所示,包括:

[0045] 用于接收干扰信号的包括PN结的检测元件11;

[0046] 干扰判断子电路12,基于检测元件11截止时的漏电大小判断该检测元件11是否受到干扰。

[0047] PN结具有单向导通特性,当高电压连接到PN结的N端,低电压连接到PN结的P端时,PN结反偏处于截止状态,其等效电阻无限大,PN结在截止时会没有或仅有很微小的电流流向P端,此情况下称为PN结漏电。当检测元件11的PN结受到干扰信号时,PN结的漏电流快速增大,其等效电阻变小。本发明基于这一特性将现有包括PN结的半导体元件作为检测元件11,并控制检测元件11处于截止状态以在该截止状态下接收干扰信号,而干扰判断子电路12与检测元件11连接,通过判断检测元件11的漏电大小,可以识别出检测元件11是否受到干扰。

[0048] 本发明可以快速自检出电路受到干扰信号影响的情况,相比现有技术,本发明无需依靠外部的干扰检测仪来检测干扰信号,也无需设计复杂的接口电路来实现与干扰检测仪的连接,更能节省电路面积和成本。

[0049] 现有包括PN结的半导体元件很多,包括但不限于二极管、三极管、MOS管等。本发明实施例可以将任一种包括PN结的半导体元件用作检测元件11,并将检测元件11连接在高低电压之间,以使检测元件11在截止状态下接收干扰信号。例如,检测元件11为二极管,则将二极管的阳极接低电压,阴极接高电压,以使二极管截止。例如,检测元件11为NMOS管,则可以将NMOS管的源端(为N型掺杂)和栅端共同接低电压(比如接地),然后将其源端(为N型掺杂)接高电压(比如接VDD),形成GGNMOS,此时由于NMOS管的P型衬底(或称P型阱区)的电位低于其源端电位,基于与GGNMOS作为ESD防护器件相同的原理,检测元件11处于截止状态,本发明在此不多赘述。例如,检测元件11为NPN双极型晶体管,NPN双极型晶体管的基极(P型)和发射极(N型)接低电压,集电极(N型)接高电压,以处于截止状态。

[0050] 由于包括PN结的检测元件11是连接于高电压、低电压之间,以处于截止状态,当有干扰信号时,PN结的漏电流显著增大,其等效电阻变小。基于该原理,本发明可以设计不同的干扰判断子电路12。

[0051] 在本发明一实施例中,如图2所示,干扰判断子电路12可以包括采样模块121和比较模块122;采样模块121基于检测元件11截止时漏电产生检测信号;比较模块122基于检测信号与检测阈值判断检测元件11是否受到干扰,并在确定所述检测元件11受到干扰时输出干扰标志信号。在本实施方式中,采样模块121至少包括与检测元件11串联的元件,以基于检测元件11截止时漏电产生检测信号。

[0052] 其中,检测信号可以为电压信号或电流信号等,相应的,若检测信号为检测电压,则检测阈值为所述检测电压对应的电压阈值;若检测信号为检测电流,则检测阈值为该检测电流对应的电流阈值。

[0053] 其中,与检测元件11串联的元件可以为电阻、MOS管、电容等。在附图2中,将检测元件11与采样模块121串联后所连接的高电压以电源电压VDD进行表示,低电压以接公共接地

端电压VSS进行表示,将检测元件11中的PN结以二极管进行示意,将比较模块122所输出的信号以0UT进行表示,其中,当检测元件11受到干扰时,比较模块122所输出的信号0UT有效,表示该干扰标志信号。

[0054] 在一些可能的实现方式中,采样模块121包括与检测元件11串联的第一电阻元件1211,基于第一电阻元件1211与检测元件11截止时漏电以产生检测信号。

[0055] 在本实现方式中,第一电阻元件1211连接在检测元件11所在的串联电路上,第一电阻元件1211与检测元件11可以直接连接也可经过如下文的第一MOS元件1212等元件与检测元件11间接连接。

[0056] 其中,若与检测元件11串联的是多个第一电阻元件1211,则可利用多个第一电阻元件1211之间的一节点来输出检测信号,比如两个第一电阻元件1211串联后与检测元件11串联,则可利用两个第一电阻元件1211的中间节点电压作为检测信号;比如将多个第一电阻元件1211中的至少一个第一电阻元件1211两端的电压差作为检测信号。当然,也可如图3所示,采用一个第一电阻元件1211与检测元件11串联,利用第一电阻元件1211与检测元件11之间的连接节点用于产生检测信号。

[0057] 关于第一电阻元件1211与处于截止状态的检测元件11串联后所输出的检测信号能表征检测元件11是否接收到干扰信号的实现原理可参考后文描述,在此不多赘述。

[0058] 在一些可能的实现方式中,采样模块121包括与检测元件11串联的第一MOS元件1212,基于第一MOS元件1212与检测元件11截止时漏电以产生检测信号。

[0059] 进一步的,如图4或图5所示,第一MOS元件1212的漏端或源端用于与检测元件11串联,第一MOS元件1212的栅端用于接其漏端或接能使第一MOS元件1212导通的外部输入电压 Vb;其中,基于第一MOS元件1212与检测元件11截止时漏电以产生检测信号。

[0060] 在本实现方式中,第一MOS元件1212可以为PMOS管,也可以为NMOS管,其中,第一MOS元件1212的源端或漏端连接在检测元件11所在的串联电路上,第一MOS元件1212的源端或漏端与检测元件11可以直接连接也可经过如电阻等间接连接。

[0061] 其中,若与检测元件11串联的是多个第一MOS元件1212,则可利用任意两个第一MOS元件1212之间的连接节点来输出检测信号。比如两个第一MOS元件1212与检测元件11位于同一串联电路,其中第一个第一MOS元件1212(为便于后文描述,该第一MOS元件1212称为A)的漏端和栅端共同接电源电压VDD,其源端接第二个第一MOS元件1212(为便于后文描述,该第一MOS元件1212称为B)的漏端和栅端,第二个第一MOS元件1212的源端则接检测元件11,检测元件11接地,在该示例中,可以将A的源端作为采样模块121的输出节点以产生该检测信号,或是将B的源端作为作为采样模块121的输出节点以产生该检测信号。

[0062] 可选的,也可采用一个第一MOS元件1212的源端或漏端与检测元件11串联,第一MOS元件1212的栅端接其漏端或接能使第一MOS元件1212导通的外部输入电压Vb,第一MOS元件1212与检测元件11连接的漏端或源端用于产生该检测信号。比如在图4和图5中,都是第一MOS元件1212的漏端与检测元件11直接连接,然后是由第一MOS元件1212的漏端产生该检测信号。

[0063] 关于第一MOS元件1212与处于截止状态的检测元件11串联后所输出的检测信号能表征检测元件11是否接收到干扰信号的实现原理可参考后文描述,在此不多赘述。

[0064] 由于采样模块121与检测元件11连接的电路结构不变,当检测元件11受干扰导致

漏电流增大时,该检测信号也增大或减小。

[0065] 在一些可能的实现方式中(图未示出),采样模块121包括电容元件和复位单元;电容元件与检测元件11串联,所述电容元件接收检测元件11流出的漏电流产生检测信号;复位单元按照预设时间间隔将电容元件的电压复位至初始状态。在本实现方式中,电容元件与检测元件11的P端连接,以接收检测元件11流出的漏电流,漏电流对电容元件充电,使得电容元件的输出电压变化,当检测元件11因接收到干扰信号而产生漏电流时,电容元件输出的电压会变化的比较显著,因此,可以将电容元件的输出电压作为检测信号。由于检测元件11在未接收到干扰信号时也会有微小的漏电流产生,该微小的漏电流持续对电容元件充电也可能使得电容元件的输出电压达到检测阈值,从而误判断。为避免干扰误判断,本实现方式的采样模块121还包括复位单元,复位单元按照预设时间间隔将电容元件的电压复位(如可以采用对电容元件放电的方式)至初始状态,其中,该预设时间间隔应小于前述微小的漏电流对电容元件充电使得电容元件的输出电压达到检测阈值的时长。

[0066] 在一些可能的实现方式中,如图3-5所示,比较模块122包括负载元件1221和第二MOS元件1222,其中,检测阈值为第二MOS元件1222的导通阈值;负载元件1221和第二MOS元件1222的源端或漏端连接形成串联电路,第二MOS元件1222的栅端基于检测信号与其导通阈值控制串联电路是否导通,以输出干扰标志信号。在本实现方式中,检测信号输入第二MOS元件1222的栅端,基于检测信号与第二MOS元件1222的源端之间的差值是否超过该导通阈值,可以控制第二MOS元件1222是否开启,进而实现串联电路是否导通。由于该串联电路导通或不导通时,负载元件1221的输出电压或者说负载元件1221与第二MOS元件1222的连接节点电压肯定会不同,因此本实现方式可以将该负载元件1221与第二MOS元件1222的连接节点的电压信号或该负载元件1221输出的电压信号作为干扰标志信号。

[0067] 其中,第二MOS元件1222可以为NMOS实现,也可以采用PMOS实现。由于NMOS的G电位比S电位高,其VGS一般以正电压表示,PMOS的S电位比G电位高,其VGS一般以负电压表示。为便于描述,本发明所指的第二MOS元件1222的导通阈值应理解为VGS的绝对值。

[0068] 其中,干扰标志信号可以设计为在串联电路导通时输出或在不导通时输出,本发明可以基于实际应用设计该干扰检测电路10,进而决定干扰标志信号的信号波形。

[0069] 其中,负载元件1221可以为电阻、MOS管、电容等元件。在图3-5的示例中,负载元件1221和第二MOS元件1222形成串联电路连接在电源电压与地之间,关于该串联电路中是负载元件1221或是第二MOS元件1222接地,本发明不做限定。

[0070] 基于前述一些实现方式,以图3-图5所示的一些电路为例,对干扰标志信号的输出进行说明。

[0071] 在一示例中,如图3所示,采样模块121为一个第一电阻元件1211,其中,第一电阻元件1211的一端与电源电压连接,另一端与检测元件11的N端连接,检测元件11的P端连接公共接地电压(VSS),其中,第一电阻元件1211与检测元件11连接的一端用于输出检测信号。比较模块122包括负载元件1221和第二MOS元件1222,第二MOS元件1222为PMOS,其源端接电源电压VDD,栅端接检测信号,漏端通过负载元件1221接地。

[0072] 当检测元件11未受到干扰时,因检测元件11截止,检测元件11的等效电阻无限大,第一电阻元件1211与检测元件11所在电路相当于开路,虽然此时检测元件11上仅有极少的漏电流产生,但该漏电流大小不足以将第一电阻元件1211与检测元件11的中间节点电压拉

低,因此此时检测信号基本等于VDD。由于检测信号基本等于VDD,检测信号与第二MOS元件1222的源端之间的差值小于检测阈值VGS,此时第二MOS元件1222也不会开启,负载元件1221和第二MOS元件1222的连接节点电压被地拉至0电位,此时负载元件1221和第二MOS元件1222形成串联电路输出低电平的信号OUT,表明检测元件11未受到干扰。

[0073] 当检测元件11接收到干扰信号时,检测元件11上产生的漏电流瞬间增大,检测元件11的等效电阻急剧变小,将第一电阻元件1211与检测元件11之间的连接节点电压迅速拉低,即检测信号被拉低,检测信号与第二MOS元件1222的源端之间的差值变大且超过检测阈值VGS,此时负载元件1221和第二MOS元件1222形成串联电路导通,负载元件1221和第二MOS元件1222形成串联电路导通,负载元件1221和第二MOS元件1222的连接节点电压被抬高,输出信号OUT为高电平(干扰标志信号),表明检测元件11受到干扰。

[0074] 在另一示例中,在图3所示的其他电路不变的情况下,第二MOS元件1222也可以采用NMOS实现,干扰标志信号设为低电平。当检测元件11未受到干扰时,检测信号基本等于VDD,第二MOS元件1222开启,负载元件1221和第二MOS元件1222的连接节点电压输出高电平,表明检测元件11未受到干扰;当检测元件11接收到干扰信号时,检测元件11上产生的漏电流瞬间增大,第一电阻元件1211与检测元件11之间的连接节点电压迅速被拉低,即将检测信号迅速拉低,检测信号与第二MOS元件1222的源端之间的差值小于检测阈值VGS,第二MOS元件1222关闭,负载元件1221和第二MOS元件1222的连接节点电压被地拉至0电位,此时负载元件1221上输出低电平的干扰标志信号,表明检测元件11受到干扰。此种方式的功耗会更高些,一般不优选。

[0075] 在又一示例中,在图3所示的其他电路不变的情况下,若检测元件11的N端接电源电压,P端通过第一电阻元件1211接公共接地电压,第一电阻元件1211则基于检测元件11流出的漏电流产生检测信号。当检测元件11受到干扰时,第一电阻元件1211的产生检测信号显著增大。第二MOS元件1222可采用NMOS实现,检测信号与第二MOS元件1222的源端之间的差值大于VGS,第二MOS元件1222开启,使得串联电路导通,负载元件1221和第二MOS元件1222的连接节点电压被抬高,输出高电平的干扰标志信号,表明检测元件11受到干扰。

[0076] 在又一示例中,就图4的方案而言,第一MOS元件1212与第二MOS元件1222都采用PMOS实现,第一MOS元件1212与第二MOS元件1222组成共栅端的电流镜结构。第一MOS元件1212的源端与电源电压VDD连接,栅端和漏端与检测元件11的N端连接,检测元件11的P端连接公共接地电压VSS。

[0077] 当检测元件11未受到干扰时,因检测元件11截止,检测元件11的等效电阻无限大,第一MOS元件1212与检测元件11所在电路相当于开路,此时第一MOS元件1212的源端、栅端以及漏端基本同电位,即第一MOS元件1212的栅端所输出的检测信号基本等于VDD,第二MOS元件1222也不会开启,负载元件1221和第二MOS元件1222的连接节点电压被地拉至0电位,此时负载元件1221和第二MOS元件1222形成串联电路输出低电平,表明检测元件11未受到干扰。

[0078] 当检测元件11接收到干扰信号时,检测元件11上产生的漏电流瞬间增大,检测元件11的等效电阻急剧变小,将第一MOS元件1212的栅端和漏端的电位拉低,第一MOS元件1212和第二MOS元件1222导通,第二MOS元件1222对第一MOS元件1212与检测元件11所在电路的电流进行复制,负载元件1221基于该复制电流输出高电平的干扰标志信号,表明检测

元件11受到干扰。

[0079] 在又一示例中,与图4不同的是,图5所示方案中,第一MOS元件1212的栅端可以接外部输入电压Vb,在输入电压Vb的作用下,第一MOS元件1212微微导通,但因检测元件11未受到干扰时检测元件11的等效电阻无限大,此时第一MOS元件1212的漏端所输出的检测信号也基本接近VDD,无法开启第二MOS元件1222;当检测元件11接收到干扰信号时,第一MOS元件1212的漏端电位被拉低,使得检测信号与第二MOS元件1222的源端之间的差值大于其VGS,第二MOS元件1222导通,最终负载元件1221和第二MOS元件1222的连接节点电压被抬高,输出高电平的干扰标志信号,表明检测元件11受到干扰。

[0080] 在一些可能的实现方式中(图未示出),比较模块122包括阈值电压产生子单元和比较器:其中,阈值电压产生子单元用于产生检测阈值;比较器用于将检测信号与检测阈值进行比较,以输出干扰标志信号。基于与前述相似的描述,当检测元件11受干扰导致漏电流增大时,该检测信号也会变化,通过将该检测信号与检测阈值进行比较,可以有效识别出检测元件11是否受到干扰,从而在检测元件11受到干扰时输出干扰标志信号。

[0081] 若检测信号大于检测阈值表明检测元件11受到干扰,则将检测信号大于检测阈值时的比较器输出的逻辑信号作为该干扰标志信号;若检测信号小于检测阈值表明检测元件11受到干扰,则将检测信号小于检测阈值时比较器输出的逻辑信号作为该干扰标志信号。

[0082] 基于前述内容可以看出,当检测元件11受到干扰信号影响时,检测元件11的高电位会被拉低,低电位会被拉低。因此,在一些其他的实施例中,本发明可以将干扰判断子电路12与检测元件11所连接的高电压或低电压直接连接,通过判断该高电位是否被显著拉低或该低电位是否被显著拉高,可以识别出检测元件11是否受到干扰,在该高电位被显著拉低或该低电位被显著拉高时则输出干扰标志信号,确定检测元件11受到干扰。具体电路中,干扰判断子电路12可以包括比较模块122;检测元件11连接于电压A和电压B之间以处于截止状态;比较模块122基于电压A或电压B以及阈值电压,确定检测元件11是否受到干扰。其中,阈值电压在该电压A或电压B的基础上进行设定,以与非干扰信号导致的漏电显著区别。

[0083] 在本发明一实施例中,如图1和图2所示,本发明的干扰检测电路10还可以包括: buffer子电路13;buffer子电路13用于将干扰判断子电路12在确定检测元件11受到干扰时输出的干扰标志信号增强后输出。

[0084] 基于本发明实施例所提供干扰检测电路10,可以快速自检出电路受到干扰信号影响的情况,在实际应用中,可将干扰检测电路10与芯片内一些容易受干扰信号影响的目标电路结合,使得目标电路基于干扰检测电路10输出的干扰标志信号做一些处理,以减小干扰对目标电路的影响。

[0085] 基于同一发明构思,本发明还提供了一种电池保护芯片30,包括:如本发明实施例所述的干扰检测电路。

[0086] 现有的集成电路一直面临着ESD(Electro-Static discharge,静电放电)的威胁,因此,现有的一些芯片电路普遍都设置有用于静电释放保护的ESD模块21。ESD模块21连接在两个高低电压之间,形成截止通道,避免静电释放影响芯片电路正常工作。然而,当ESD模块21受到如射频或电磁波等辐射干扰时,其产生的漏电流会瞬间变得较大,此种漏电会导致ESD模块21所连接的两个高低电压受到影响,比如高电压被拉低,低电压被拉高,进而影响了基于该高电压或低电压的功能模块的工作稳定性以及相关检测结果的准确性。

[0087] 有鉴于此,如图6和图7所示,在一个具体的应用中,该电池保护芯片30还包括:

[0088] 用于对过流检测端的电压进行静电释放保护的一个或多个ESD模块21;

[0089] 如本发明实施例所述的干扰检测电路10,其中,干扰检测电路10包括用于接收干扰信号的包括PN结的检测元件11以及干扰判断子电路12,干扰判断子电路12基于所述检测元件11截止时的漏电大小判断所述检测元件11是否受到干扰,并在确定所述检测元件11受到干扰时输出干扰标志信号,干扰检测电路10输出的干扰标志信号用于表征ESD模块21有受干扰信号影响;

[0090] 以及,与过流检测端的电压相关的功能模块22,该功能模块22在接收到干扰标志信号时停止工作或切换工作状态。

[0091] 检测元件11所在电路所连接的高低电压与ESD模块21可以相同,也可不同。例如,一个或多个ESD模块21连接于电源电压VDD与过流检测端(在附图中以VM端子进行表示)电压之间,或连接于过流检测端电压与公共接地端电压之间;在干扰检测电路10中,采样模块121与检测元件11串联后可连接于电源电压VDD与过流检测端电压之间,或连接于过流检测端电压与公共接地端电压之间,或连接于电源电压VDD与公共接地端电压VSS之间。

[0092] 其中,图6和图7不同的是,在图6中,干扰判断子电路12与检测元件11串联后连接在电源电压VDD与过流检测端(在附图中以VM端子进行表示)电压之间,使得检测元件11能有效、及时接收到干扰信号,进而使得与过流检测端电压相关的功能模块22能更及时停止工作或切换工作状态;在图7中,干扰判断子电路12与检测元件11串联后连接在电源电压VDD与公共接地端电压VSS之间,以尽可能的在干扰检测阶段就降低漏电流对过流检测端电压的影响。

[0093] 在一些可能的实现方式,干扰检测电路10中的检测元件11与ESD模块21的结构相同(图未示出)。由于检测元件11与ESD模块21的结构相同,两者对干扰信号的接收能力会无限接近,如此当检测元件11接收到干扰信号时,大概率ESD模块21也接收到了干扰信号,此情况下干扰检测电路10输出的干扰标志信号更能有效表征ESD模块21有受干扰信号影响。

[0094] 在一些可能的实现方式中,检测元件11的尺寸小于ESD模块21,有利于节约电路面积。特别是干扰检测电路10中的检测元件11与现有的ESD模块21的结构相同的情况下,采用更小尺寸的检测元件11可节省较大的芯片面积。如ESD模块21和检测元件11均采用GGNMOS实现,则检测元件11可采用尺寸更小的GGNMOS。

[0095] 目前的电池保护芯片30中一般设置有充电过流检测模块、放电过流检测模块以及短路检测模块等,充电过流检测模块、放电过流检测模块以及短路检测模块都会对过流检测端的电压进行检测,然后将检测得到的电压与其各自的检测阈值进行比较,从而判断电池是否充电过流、放电过流以及短路等。本发明实施例的功能模块22可以为充电过流检测模块、放电过流检测模块以及短路检测模块中的至少一者。

[0096] 在电池保护芯片30中,一个或多个ESD模块21可以连接于过流检测端与公共接地端之间,也可以连接于电源电压VDD与过流检测端之间,当ESD模块21受到如射频等干扰信号的影响时,一个或多个ESD模块21会产生较大的漏电流,漏电流流向过流检测端使其电压变大或流向更低电位将过流检测端的电压拉低。此种情况下,充电过流检测模块、放电过流检测模块以及短路检测模块所检测得到的电压就不准确了,进而影响了其各自判断电池是否充电过流、放电过流以及短路的准确性。基于本发明实施例,当干扰检测电路10输出的干

扰标志信号时,则表征ESD模块21有受干扰信号影响的风险,此时与过流检测端的电压相关的电过流检测模块、放电过流检测模块以及短路检测模块中至少一者在接收到干扰标志信号时停止工作,以此可以有效降低干扰信号对其各自功能的影响。

[0097] 由于如射频等干扰信号一般是断断续续的或者可理解为周期性的,其单次作用于 ESD模块21的时间较短,而短路检测的触发时间较短,因此干扰信号对短路检测模块的影响 最大,优选的,功能模块22至少为短路检测模块。当短路检测模块在接收到干扰标志信号时停止工作,以避免误判电路短路。同时也因干扰信号的持续时间较短,当干扰信号消失后,干扰检测电路10则不会输出干扰标志信号或者说所输出的信号会翻转,使得短路检测模块恢复正常工作状态,如此也不会影响短路检测模块的短路检测功能。

[0098] 需要说明的是,本说明书中的各个实施例均采用递进的方式描述,每个实施例重点说明的都是与其他实施例的不同之处,各个实施例之间相同相似的部分互相参见即可。

[0099] 以上对本发明所提供的技术方案进行了详细介绍,本文中应用了具体个例对本发明的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本发明,本说明书内容不应理解为对本发明的限制。同时,对于本领域的一般技术人员,依据本发明,在具体实施方式及应用范围上均会有不同形式的改变之处,这里无需也无法对所有的实施方式予以穷举,而由此所引伸出的显而易见的变化或变动仍处于本发明的保护范围之中。

图1

图2

图4

图5

图6

图7