## (19)中华人民共和国国家知识产权局

# (12)发明专利

(10)授权公告号 CN 108430165 B (45)授权公告日 2019.12.20

(21)申请号 201810153175.4

(22)申请日 2018.02.08

(65)同一申请的已公布的文献号 申请公布号 CN 108430165 A

(43)申请公布日 2018.08.21

(73)专利权人 广州兴森快捷电路科技有限公司 地址 510663 广东省广州市广州高新技术 产业开发区科学城光谱中路33号

**专利权人** 深圳市兴森快捷电路科技股份有限公司

天津兴森快捷电路科技有限公司

(72)发明人 谢添华 徐娟 江武骏

(74)专利代理机构 广州华进联合专利商标代理 有限公司 44224

代理人 王瑞

(51) Int.CI.

*H05K 3/06*(2006.01) *G01B 21/18*(2006.01)

(56)对比文件

CN 202133391 U,2012.02.01,全文. CN 101686603 A.2010.03.31,全文.

审查员 赵萌

权利要求书1页 说明书4页 附图2页

#### (54)发明名称

PCB板蚀刻检测方法

#### (57)摘要

本发明公开了一种PCB板蚀刻检测方法,包括以下步骤:在基板的表面贴设保护膜;在所述保护膜上开设多个通孔;对所述基板靠近所述保护膜的一侧进行蚀刻处理;记录所述基板靠近所述保护膜的侧面上被蚀刻的深度。上述PCB板蚀刻检测方法,通过在基板表面贴设保护膜,并在保护膜上开设通孔,当对基板靠近保护膜的侧面进行蚀刻时,保护膜可保护基板不被蚀刻,同时在基板上与上述通孔对应的位置处,基板被蚀刻,由于通孔为多个,会导致基板上多处被蚀刻,此时可记录各处被蚀刻处的深度,并通过比对各蚀刻处的深度,了解上述蚀刻处理能否对基板进行均匀蚀刻。上述PCB板蚀刻检测方法能够直观行均匀蚀刻。上述PCB板蚀刻检测方法能够直观的了解蚀刻处理的均匀性,检测效果较好。

1.一种PCB板蚀刻检测方法,其特征在于,包括以下步骤:

在基板的表面贴设保护膜,所述保护膜为感光干膜;

对所述保护膜依次进行曝光、显影处理,使所述保护膜上形成多个通孔;

所述基板包括树脂层及支撑层,所述保护膜设于所述树脂层远离所述支撑层的一侧, 对所述基板靠近所述保护膜的一侧进行蚀刻处理,所述树脂层上被蚀刻出的加工孔均为盲孔;

记录所述基板靠近所述保护膜的侧面上被蚀刻的深度。

- 2. 根据权利要求1所述的PCB板蚀刻检测方法,其特征在于,所述通孔呈阵列设置。

- 3.根据权利要求1所述的PCB板蚀刻检测方法,其特征在于,上述对所述基板靠近所述 保护膜的一侧进行蚀刻处理,具体包括以下步骤:

将所述基板放入等离子蚀刻设备腔体内,对基板靠近所述保护膜的一侧进行等离子蚀刻处理。

- 4.根据权利要求3所述的PCB板蚀刻检测方法,其特征在于,所述基板沿水平方向或竖直方向设于所述等离子蚀刻设备腔体内。

- 5.根据权利要求4所述的PCB板蚀刻检测方法,其特征在于,所述基板与所述等离子蚀刻设备的腔体匹配。

- 6.根据权利要求3所述的PCB板蚀刻检测方法,其特征在于,上述对所述基板靠近所述 保护膜的一侧进行等离子蚀刻,还包括以下步骤:

控制等离子蚀刻的时间,使所述树脂层上被蚀刻出的加工孔均为盲孔。

7.根据权利要求1-6任一项所述的PCB板蚀刻检测方法,其特征在于,上述记录所述基板靠近所述保护膜的侧面上被蚀刻的深度之前,还包括以下步骤:

去除所述保护膜。

8.根据权利要求1-6任一项所述的PCB板蚀刻检测方法,其特征在于,上述记录所述基板靠近所述保护膜的侧面上被蚀刻的深度,还包括以下步骤:

生成所述基板上各处被蚀刻的深度的分布图。

- 9.根据权利要求1-6任一项所述的PCB板蚀刻检测方法,其特征在于,所述通孔均匀间隔设置。

- 10.根据权利要求1-6任一项所述的PCB板蚀刻检测方法,其特征在于,所述保护膜的尺寸与所述基板的尺寸匹配,所述保护膜的边角处均设有所述通孔。

# PCB板蚀刻检测方法

#### 技术领域

[0001] 本发明涉及PCB板测试技术领域,特别是涉及一种PCB板蚀刻检测方法。

#### 背景技术

[0002] 随着电子产品向小型化、高密度化、高集成度和多功能化的方向迅速发展,对印制线路板提出的要求也越来越高,PCB制作过程也需更加精细化。

[0003] 在PCB板的制作过程中,需要对PCB板进行蚀刻,而蚀刻设备能否对PCB板进行均匀的蚀刻会影响PCB板的性能,传统对蚀刻后的PCB板进行检测的方法为重量差法,但重量差法检测效果差,不能很好的对蚀刻的均匀性进行评估。

## 发明内容

[0004] 基于此,本发明在于克服现有技术的缺陷,提供一种检测效果好的PCB板蚀刻检测方法。

[0005] 其技术方案如下:

[0006] 一种PCB板蚀刻检测方法,包括以下步骤:

[0007] 在基板的表面贴设保护膜;

[0008] 在所述保护膜上开设多个通孔;

[0009] 对所述基板靠近所述保护膜的一侧进行蚀刻处理;

[0010] 记录所述基板靠近所述保护膜的侧面上被蚀刻的深度。

[0011] 上述PCB板蚀刻检测方法,通过在基板表面贴设保护膜,并在保护膜上开设通孔, 当对基板靠近保护膜的侧面进行蚀刻时,保护膜可保护基板不被蚀刻,同时在基板上与上 述通孔对应的位置处,基板被蚀刻,由于通孔为多个,会导致基板上多处被蚀刻,此时可记 录各处被蚀刻处的深度,并通过比对各蚀刻处的深度,了解上述蚀刻处理能否对基板进行 均匀蚀刻。上述PCB板蚀刻检测方法,能够直观的了解蚀刻处理的均匀性,检测效果较好。

[0012] 进一步地,所述通孔呈阵列设置。

[0013] 进一步地,上述对所述基板靠近所述保护膜的一侧进行蚀刻处理,具体包括以下步骤:

[0014] 将所述基板放入等离子蚀刻设备腔体内,对基板靠近所述保护膜的一侧进行等离子蚀刻处理。

[0015] 进一步地,所述基板沿水平方向或竖直方向设于所述等离子蚀刻设备腔体内。

[0016] 讲一步地,所述基板与所述等离子蚀刻设备的腔体匹配。

[0017] 进一步地,所述基板包括树脂层及支撑层,所述保护膜设于所述树脂层远离所述支撑层的一侧,上述对所述基板靠近所述保护膜的一侧进行等离子蚀刻,还包括以下步骤:

[0018] 控制等离子蚀刻的时间,使所述树脂层上被蚀刻出的加工孔均为盲孔。

[0019] 进一步地,上述记录所述基板靠近所述保护膜的侧面上被蚀刻的深度之前,还包括以下步骤:

[0020] 去除所述保护膜。

[0021] 进一步地,上述记录所述基板靠近所述保护膜的侧面上被蚀刻的深度,还包括以下步骤:

[0022] 生成所述基板上各处被蚀刻的深度的分布图。

[0023] 进一步地,所述通孔均匀间隔设置。

[0024] 进一步地,所述保护膜的尺寸与所述基板的尺寸匹配,所述保护膜的边角处均设有所述通孔。

## 附图说明

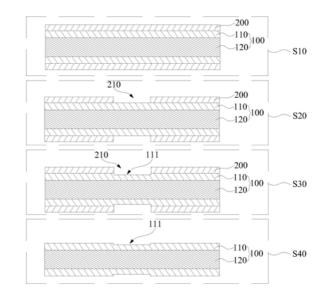

[0025] 图1为本发明实施例所述的PCB板蚀刻检测方法的原理示意图;

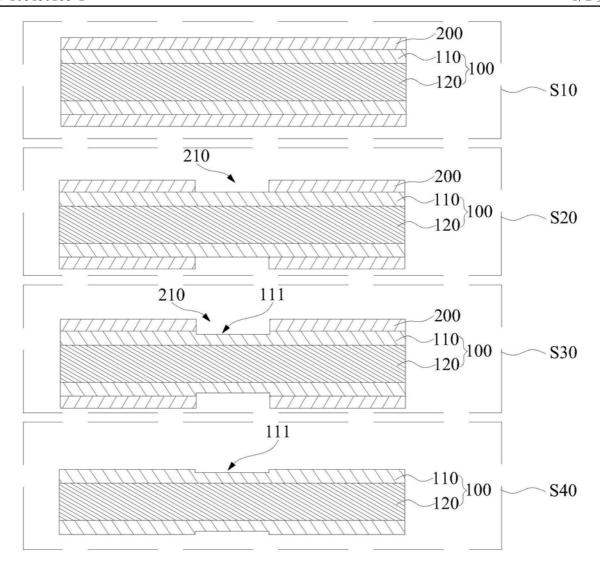

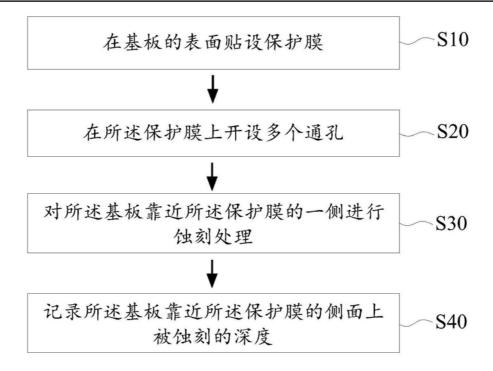

[0026] 图2为本发明实施例所述的PCB板蚀刻检测方法的流程示意图;

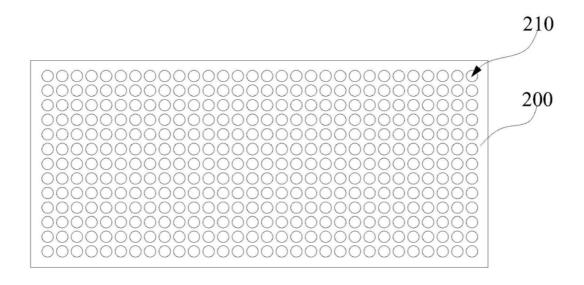

[0027] 图3为本发明实施例所述的保护膜的结构示意图。

[0028] 附图标记说明:

[0029] 100、基板,110、树脂层,111、加工孔,120、支撑层,200、保护膜,210、通孔。

#### 具体实施方式

[0030] 为了便于理解本发明,下面将参照相关附图对本发明进行更全面的描述。附图中给出了本发明的较佳实施方式。但是,本发明可以以许多不同的形式来实现,并不限于本文所描述的实施方式。相反地,提供这些实施方式的目的是使对本发明的公开内容理解的更加透彻全面。

[0031] 需要说明的是,本文所使用的术语"垂直的"、"水平的"、"左"、"右"以及类似的表述只是为了说明的目的,并不表示是唯一的实施方式。

[0032] 除非另有定义,本文所使用的所有的技术和科学术语与属于本发明的技术领域的技术人员通常理解的含义相同。本文中在本发明的说明书中所使用的术语只是为了描述具体的实施方式的目的,不是旨在于限制本发明。本文所使用的术语"和/或"包括一个或多个相关的所列项目的任意的和所有的组合。

[0033] 一实施例中,如图1及图2所示,PCB板蚀刻检测方法包括以下步骤:

[0034] 在基板100的表面贴设保护膜200;

[0035] 在保护膜200上开设多个通孔210:

[0036] 对基板100靠近保护膜200的一侧进行蚀刻处理;

[0037] 记录基板100靠近保护膜200的侧面上被蚀刻的深度。

[0038] PCB板蚀刻检测方法,通过在基板100表面贴设保护膜200,并在保护膜200上开设通孔210,当对基板100靠近保护膜200的侧面进行蚀刻时,保护膜200可保护基板100不被蚀刻,同时在基板100上与通孔210对应的位置处,基板100被蚀刻,由于通孔210为多个,会导致基板100上多处被蚀刻,此时可记录各处被蚀刻处的深度,并通过比对各蚀刻处的深度,了解蚀刻处理能否对基板100进行均匀蚀刻。PCB板蚀刻检测方法,能够直观的了解蚀刻处理的均匀性,检测效果较好。

[0039] 具体地,通过开窗工艺在保护膜200上开设多个通孔210。

[0040] 可选地,根据蚀刻的设备或工艺,也可对基板100的两侧面均贴设保护膜200并开

孔。用于对蚀刻的均匀性进行检测。

[0041] 可选地,保护膜200为感光干膜。

[0042] 具体地,在保护膜200上开设多个通孔210,具体包括以下步骤:

[0043] 对保护膜200依次进行曝光、显影处理,使保护膜200上形成多个通孔210。

[0044] 可选地,通孔210为圆孔,通孔210的孔径为50µm~1000µm。此时检测效果更好。

[0045] 进一步地,如图3所示,通孔210呈阵列设置。此时在基板100上进行蚀刻处理时,基板100上被蚀刻处也呈阵列设置,可更好的了解在基板100的不同位置处,蚀刻处理的均匀性。

[0046] 进一步地,上述对基板100靠近保护膜200的一侧进行蚀刻处理,具体包括以下步骤:

[0047] 将基板100放入等离子蚀刻设备腔体内,对基板100靠近保护膜200的一侧进行等离子蚀刻处理。

[0048] 本实施例中,通过将基板100放入等离子蚀刻设备腔体内并进行等离子蚀刻,可了解等离子蚀刻设备在蚀刻处理时能否对基板100上的各处进行均匀蚀刻,以便对等离子蚀刻设备的蚀刻效果进行评估。

[0049] 可选地,等离子蚀刻设备内具有多个用于等离子蚀刻的腔体,可设置至少两个基板100,并分别贴设保护膜200及开设通孔210,用于对等离子蚀刻设备内的不同腔体进行检测。

[0050] 进一步地,基板100沿水平方向或竖直方向设于等离子蚀刻设备腔体内。此时可确保基板100上各处的试验条件相同,以便排除干扰条件,更好的对蚀刻效果进行评估。

[0051] 进一步地,基板100与等离子蚀刻设备的腔体匹配。此时基板100可对等离子蚀刻设备的腔体内的蚀刻效果进行全面的检测,检测效果更好。

[0052] 进一步地,如图1所示,基板100包括树脂层110及支撑层120,保护膜200设于树脂层110远离支撑层120的一侧,上述对基板100靠近保护膜200的一侧进行等离子蚀刻,还包括以下步骤:

[0053] 控制等离子蚀刻的时间,使树脂层110上被蚀刻出的加工孔111均为盲孔。

[0054] 若树脂层110上被蚀刻出的加工孔111为通孔210,则无法了解加工孔111被蚀刻的实际深度,也就无法评估基板100上各处被蚀刻的深度是否均匀分布,因此保证树脂层110上被蚀刻出的加工孔111均为盲孔,可便于对蚀刻效果进行评估,检测效果更好。

[0055] 可选地,树脂层110可为FR-4树脂板。

[0056] 可选地,支撑层120可为铜层,在对支撑层120两侧的树脂层110进行支撑的基础上,可模拟电路板被蚀刻时的场景。此外,支撑层120也可选择其他材料,例如非金属材料。

[0057] 具体地,基板100被蚀刻的深度为加工孔111的深度,可利用3D测量仪测量加工孔111的底部与树脂层110远离支撑层120的侧面之间的高度差。

[0058] 进一步地,如图1所示,上述记录基板100靠近保护膜200的侧面上被蚀刻的深度之前,还包括以下步骤:

[0059] 去除保护膜200。

[0060] 保护层200也会收到蚀刻,因此去除保护膜200可方便对基板100上被蚀刻的深度进行测量,可提高检测效率。

[0061] 进一步地,上述记录基板100靠近保护膜200的侧面上被蚀刻的深度,还包括以下步骤:

[0062] 生成基板100上各处被蚀刻的深度的分布图。

[0063] 可通过分布图对蚀刻处理的效果进行评估,并通过上述分布图对蚀刻处理的工艺或设置进行相应的调整。

[0064] 进一步地,上述通孔210均匀间隔设置。此时基板100在进行蚀刻处理后,各个被蚀刻处在基板100上分布均匀,可更好的检测蚀刻的均匀性。

[0065] 进一步地,上述保护膜200的尺寸与上述基板100的尺寸匹配,上述保护膜200的边角处均设有上述通孔210。此时可对基板100的边角处进行蚀刻处理,相应的可对蚀刻的均匀性进行全面的了解,检测效果更好。

[0066] 以上所述实施例的各技术特征可以进行任意的组合,为使描述简洁,未对上述实施例中的各个技术特征所有可能的组合都进行描述,然而,只要这些技术特征的组合不存在矛盾,都应当认为是本说明书记载的范围。

[0067] 以上所述实施例仅表达了本发明的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对发明专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干变形和改进,这些都属于本发明的保护范围。因此,本发明专利的保护范围应以所附权利要求为准。

图1

图2

图3