# (19) 대한민국특허청(KR) (12) 특허공보(B1)

(51) Int. CI.<sup>6</sup> (45) 공고일자 1996년 12월21일 (11) 공고번호 특1996-0016813 H03M 1/14 (24) 등록일자 1996년 12월21일 (21) 출원번호 특 1993-0023927 (65) 공개번호 **특1995−0015928** (22) 출원일자 1993년11월11일 (43) 공개일자 1995년06월 17일 (73) 특허권자 현대전자산업주식회사 김주용 경기도 이천군 부발읍 아미리 산 136-1 (우:467-860) (72) 발명자 서울특별시 강동구 고덕 2동 217 주공아파트 247동 508호 (74) 대리인 김학제

### 심사관 : 김희태 (책자공보 제4761호)

### (54) 다중채널 디지틀/아나로그 변환기

#### 요약

요약없음.

#### 대표도

### 도1

### 명세서

[발명의 명칭]

다중채널 디지틀/아나로그 변환기

[도면의 간단한 설명]

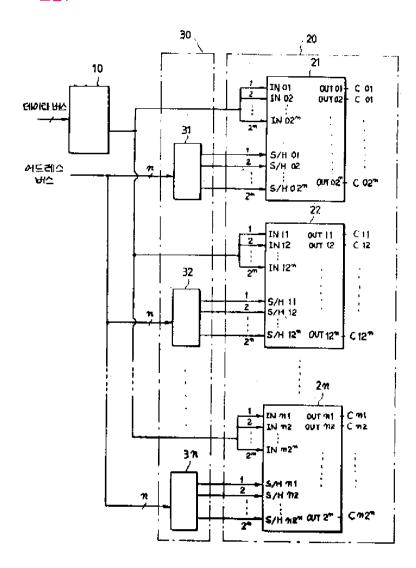

제1도는 본 발명의 단일채널 디지틀/아나로그 변환기에 샘플/홀드 수단을 연결한 구성도.

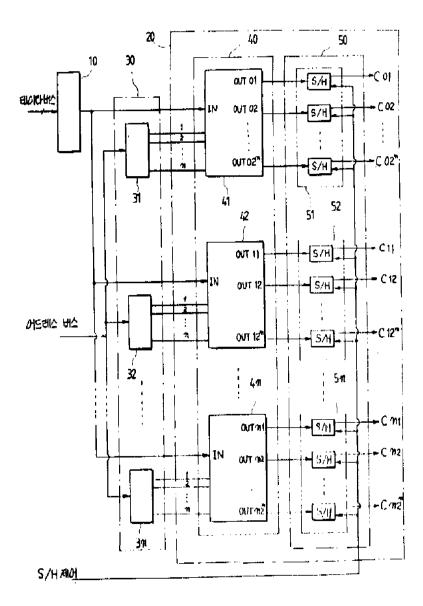

제2도는 본 발명의 단일채널 디지틀/아나로그 변환기에 아나로그 디멀티플렉서와 샘플/홀드 수단을 연결한 구성도.

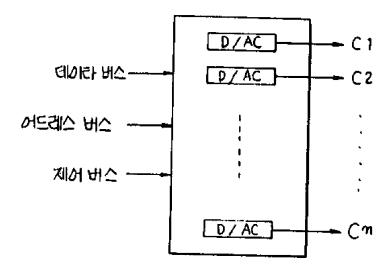

제3도는 종래의 내장형 다중 채널 디지틀/아나로그 변환기의 구성도.

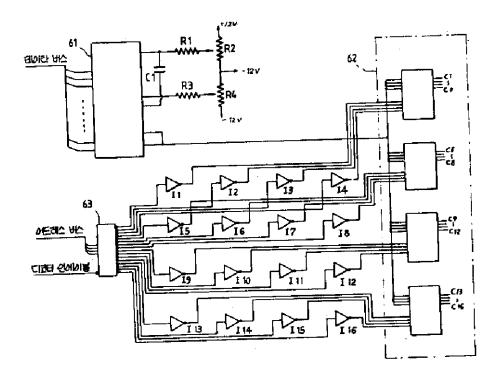

제4도는 본 발명의 16채널 디지틀/아나로그 변환기를 샘플/홀드부를 이용하여 설계한 회로의 예시도이다.

\* 도면의 주요부분에 관한 부호의 설명

10 : 단일채널 디지틀/아나로그 변환기20 : 다중채널 샘플/홀드 수단

30 : 어드레스 디코더부40 : 아나로그 디멀티플렉서부

50 : 단일채널 샘플/홀드 수단

[발명의 상세한 설명]

본 발명은 다중채널 디지틀/아나로그 변환기에 관한 것으로서, 종래의 내장형 다중채널 디지틀/아나로그 변환기를 사용하지 않고 일반적으로 많이 사용하는 단일채널 디지틀/아나로그 변환기와 샘플/홀드 수단을 이용하여 고분해능 및 저분해능의 다중채널 디지틀/아나로그 변환기를 제공하려는 것이다.

일반적으로 다중채널 디지틀/아나로그 변환기는 마이크로프로세서를 이용한 디지틀 자동제어 분야나 오디오, TV, 비디오 그리고 DSP(Digital Signal Processing) 분야에 걸쳐 폭넓게 사용되는 전자부품이다.

지금까지 사용되어 온 종래의 다중채널 디지틀/아나로그 변환기는 제3도에 도시한 바와 같이 여러 개의디지틀/아나로그 회로를 한개의 칩으로 패키지화 한 내장형 다중채널/아나로그 변환기(60)가 사용되어 왔다.

따라서 반도체의 집적도 문제와 그로인한 채널 수의 제약을 받았으며 고가라는 단점이 있다.

그리고 현재 이용 가능한 내장형 다중채널 디지틀/아나로그 변환기는 채널수가 2~36개 정도까지 이며, 이들도 저분해능인 8, 10, 12비트가 주종을 이루고 있으며, 고분해능인 14, 16비트인 경우 이용가능한 디지틀/아나로그 변환기가 거의 없는 실정이다.

본 발명은 종래의 문제점을 해결하기 위한 것으로, 가격이 저렴한 단일채널 디지틀/아나로그 변환기와 샘 플/홀드 수단을 사용하여 다채널을 구현 가능케함을 특징으로 한다.

즉, 본 발명은 단일채널 디지틀/아나로그 변환기의 아나로그 출력을 샘플/홀드 수단을 이용하여 다중채널

아나로그 신호를 얻을 수 있도록 한 것으로, 단일의 채널 디지틀/아나로그 변환기와 다수의 샘플/홀드부 를 조합함에 따라 기존의 단일채널 디지틀/아나로그 변환기로 채널 수의 제한없이 고분해능 및 저분해능 의 다중채널 디지틀/아나로그 변환기를 낮은 가격으로 실현할 수 있도록 한 것이다.

이하 본 발명을 첨부도면을 참조로 하여 상세히 설명한다.

제1도는 본 발명의 일실시예를 나타낸 블럭 구성도로서, 데이타 버스를 통하여입력된 디지틀 신호를 아나로그 신호로 변환시키는 단일채널 디지틀/아나로그 변환기(10)와, 상기 단일채널 디지틀/아나로그 변환기(10)의 출력인 아나로그 신호를 샘플링 및 유지하기 위한 다중채널 샘플/홀드수단(20)과, 어드레스 버스를 통하여 받은 정보로서 상기 다중채널 샘플/홀드수단(20)의 채널을 지정하고 또한 상기 다중채널 샘플/홀드 수단(20)의 각 다중채널 샘플/홀드부(21, 22,…, 2n)를 제어하기 위한 어드레스 디코더부(30)로 구성되며, 여기서 어드레스 버스로 어드레스를 전송하는 CPU는 생략하였다.

제2도는 본 발명의 다른 실시예를 나타낸 블럭 구성도로서, 상기 단일 채널 디지틀/아나로그 변환기(10)와, 상기 단일채널 디지틀/아나로그 변환기(10)로부터 받은 복수의 공통 입력으로부터 선택된 하나의 출력단으로 출력하기 위한 아나로그 디멀티플렉서부(40)와, 어드레스 버스를 통하여 전송된 어드레스로서상기 아나로그 디멀티플렉서부(40)의 출력선을 지정하기 위한 어드레스디코더부(30)와, 상기 아나로그 디멀티플렉서부(40)의 출력값을 샘플링 및 유지하기 위한 다수의 샘플/홀드부(51, 52, …, 5n)로 이루어진샘플/홀드수단(50)으로 구성되며, 여기서 어드레스 버스로 어드레스를 전송하는 CPU는 생략하였다.

상기 아나로그 디멀티플렉서브(40)와 단일채널 샘플/홀드수단(50)은 다중 채널 샘플/홀드수단(20)을 이룬 다

제4도는 본 발명의 구체적인 실시예로써, 디지틀/아나로그 변환기(61)는 16비트의 디지틀 입력을 아나로 그 신호로 변환시키며, 상기 디지틀/아나로그 변환기(61)에 연결된  $R_1$ ,  $R_2$ ,  $R_3$ ,  $R_4$  및  $C_1$ 은 인가전압(+12 V)를 조정하기 위한 저항 및 콘덴서이며, 상기 디지틀/아나로그 변환기(61)의 출력인 아나로그 신호는 4개의 채널을 가지고 있는 4개의 샘플/홀드부(62)로 공통으로 입력된다.

그리고 4비트 어드레스 버스로부터 정보를 받고, 인에이블(enable)선을 가지고 있는 어드레스 디코더(6 3)는 상기 샘플/홀드부(62)의 채널을 지정하는 기능과 상기 샘플/홀드부를 제어하는 기능도 가지고 있다. 상기 어드레스 디코더부(63)는 액티브 로우(active low)인 칩(chip)으로 설계되었으므로 칩의 각 출력선에 대응하여 16개의 인버터(I 1~I 16)를 배치시켰다. 제4도의 동작 과정은 제1도의 경우와 같다. 상기 인버터(I 1~I 16)는 액티브 하이로 설계할 경우는 생략하여 구성함을 알 수 있을 것이다. 상기 단일채널 디지틀/아나로그 변환기(61)는 AD DA C71-C0B-V로 구현할 수 있고, 상기 어드레스 디코더(63)는 74LS 154로 구현 가능하며, 상기 샘플/홀드부(62)는 AD 684JQ로 구현할 수 있다.

다음은 본 발명의 전반적인 동작과정 및 효과에 대하여 설명한다.

제1도에 도시한 바와같이, 아나로그 신호를 원하는 채널에 출력하기 위해서는 우선 디지틀/아나로그 변환기(10)의 데이타 버스에 출력을 원하는 아나로그 값에 해당하는 디지틀 값을 입력하면, 상기 단일채널 디지틀/아나로그 변환기(10)의 출력인 아나로그 신호는 각 다중채널 샘플/홀드부(21, 22, …, 2n)에 공통으로 입력된다. 이때 어드레스 디코더부(30)의 각 어드레스 디코더(31, 32, …, 3n)는 어드레스 버스로 전송된 주소로 지정된 출력선에만 신호를 내므로써 상기 다중채널 샘플/홀드부(21, 22, …, 2n)중 하나의채널을 지정하고, 각 다중채널 샘플/홀드부(21, 22, …, 2n)를 제어한다. 즉, 상기 각 어드레스 디코더(31, 32, …, 3n)는 n비트 어드레스 버스를 통하여 받은 정보로부터 하나의 채널을 지정할 뿐만 아니라, 상기 다중채널 샘플/홀드부(21, 22, …, 2n)가 상기 단일채널 디지틀/아나로그 변환기(10)로부터 입력된아나로그 신호를 샘플링 및 유지하도록 제어함으로써, 원하는 채널에 아나로그 값이 출력되도록 할 수 있다.

한편, 제2도에 도시한 바와같이 아나로그 신호를 원하는 채널에 출력하기 위해서는 우선 상기 디지틀/아나로그 변환기(10)의 데이타 버스의 출력을 원하는 아나로그 값에 해당하는 디지틀 값을 입력하면 상기한디지틀/아나로그 변환기(10)의 출력인 아나로그 신호는 아나로그 디멀티플렉서부(40)의 각 디멀티플렉서(41, 42, …, 4n)에 입력되고, 어드레스 버스에 의하여 정보를 받은 어드레스 디코더부(30)의 각 디코더들(31, 32, …, 3n)은 상기 각 아나로그 디멀티플렉서(41, 42, …, 4n)의 출력선을 지정한다. 이때 샘플/홀드 신호를 보내면 원하는 채널에 아나로그 값이 출력된다. 그리고 단일채널 샘플/홀더부(51, 52, …, 5n)의 S/H 제어선은 입력값이 1이면 아나로그 디멀티플렉서부(41, 42, …, 4n)의 아나로그 신호치를 샘플 링하고 입력값이 0이면 샘플링 값을 유지하는 제어기능을 갖는다.

이상에서 상세히 설명한 바와 같이 본 발명은 일반적으로 사용되는 단일채널 디지틀/아나로그 변환기와 샘플/홀드장치를 사용하면 낮은 가격으로 채널수를 확장시킬 수 있으며, 저분해능 다중채널 디지틀/아나 로그 변환기 뿐만 아니라 고분해능 다중채널 디지틀/아나로그 변환기를 실현시킬 수 있는 효과가 있다.

특히 디지틀 자동제어 분야에서 하나의 단일채널 디지틀/아나로그 변환기를 사용해서 여러개의 구동기 (actuator)를 구동하거나 또는 VTR, TV 등의 조정개소가 많은 제품에서 반고정 또는 가변저항 대신에 사용하면 실장 면적의 고밀도화를 꾀할 수 있다.

또한 고정밀도를 요구하는 고분해능 내장형 디지틀/아나로그 변환기는 아직 상용화되어 있지 않아 본 기술을 이용하면 쉽게 고분해능 다중채널 디지틀/아나로그 변환기를 실현할 수 있다.

### (57) 청구의 범위

### 청구항 1

데이타 버스를 통하여 입력된 디지틀 신호를 아나로그 신호로 변환시키는 단일채널 디지틀/아나로그 변환 기(10)와, 상기 단일채널 디지틀/아나로그 변환기(10)의 출력인 아나로그 신호를 동시에 각각 제공받아 샘플링 및 홀드하기 위해 다수의 샘플/홀드부(21~2n)를 포함하여 이루어진 샘플/홀드수단(20)과, 어드레

스 버스와 각각 병렬접속되며, 어드레스 버스를 통한 정보로부터 상기 샘플/홀드수단(20)의 출력 채널을 선택하도록 상기 샘플/홀드수단(20)의 각 샘플/홀드부에 대응하는 각각 제어하는 다수의 어드레스 디코더 (31, 32, …, 3n)로 이루어진 어드레스 디코더부(30)로 구성됨을 특징으로 하는 다중채널 디지틀/아나로 그 변환기.

### 청구항 2

데이타 버스를 통하여 입력된 디지틀 신호를 아나로그 신호로 변환시키는 단일채널 디지틀/아나로그 변환기(10)와; 어드레스 디코더부(30)의 각 어드레스 디코더 각 어드레스 디코더(31, 32, …, 3n)에 대응하여 출력선이 지정되는 각 아나로그 디멀티플렉서(41, 42, …, 4n)로 이루어진 아날로그 디멀티플럭서브(40)와, S/H제어선(Sample Hold Control)에 의하여 제어되고 각 디멀티플렉서(41, 42, …, 4n)의 출력을 제공받아 샘플링 및 홀딩하는 다수의 단일 채널 샘플/홀드부(51, 52, …, 5n)로 이루어진 단일채널 샘플/홀드수단(10)으로 구성되는 다중채널 샘플/홀드수단(20); 및 어드레스버스를 통한 정보로부터 상기 각 아나로그 디멀티 플렉서(41, 42, …, 4n)로 이루어진 어드레스 디코더부(30)로 구성됨을 특징으로 하는 다중채널 디지틀/아나로그 변환기.

### 도면

### 도면1

### 도면2

도면3

## 도면4