### (19) **日本国特許庁(JP)**

(51) Int. CL.

# (12) 特 許 公 報(B2)

FL

(11)特許番号

特許第5282776号 (P5282776)

(45) 発行日 平成25年9月4日(2013.9.4)

(24) 登録日 平成25年6月7日(2013.6.7)

| 110 11 01/000 | /000¢ 04\                    | 97/04            | Á                        |

|---------------|------------------------------|------------------|--------------------------|

| HO1L 21/822   | •                            |                  | A                        |

| HO1L 27/04    | <b>(2006.01)</b> GO9G        | 3/36             |                          |

| GO9G 3/36     | ( <b>2006.01</b> ) GO 9 G    | 3/20 €           | 3 1 2 D                  |

| GO9G 3/20     | (2006.01) GO9G               | 3/20 €           | S 1 1 A                  |

| GO2F 1/133    | •                            |                  | 6 1 1 J                  |

| 0021 1/100    | (2000.01)                    |                  |                          |

|               |                              |                  | 請求項の数 10 (全 32 頁) 最終頁に続く |

| (21) 出願番号     | 特願2010-238858 (P2010-238858) | (73) 特許権法        | <del></del>              |

| (22) 出願日      | 平成22年10月25日 (2010.10.25)     | (10) 14 # 11 # 5 | セイコーエプソン株式会社             |

|               |                              |                  |                          |

| (62) 分割の表示    | 特願2006-34498 (P2006-34498)   |                  | 東京都新宿区西新宿2丁目4番1号         |

|               | の分割                          | (74) 代理人         | 100090479                |

| 原出願日          | 平成18年2月10日 (2006.2.10)       |                  | 弁理士 井上 一                 |

| (65) 公開番号     | 特開2011-77527 (P2011-77527A)  | (74) 代理人         | 100104710                |

| (43) 公開日      | 平成23年4月14日 (2011. 4. 14)     | ( )              | 弁理士 竹腰 昇                 |

| 審査請求日         | 平成22年11月19日 (2010.11.19)     | (74) 代理人         | 100124682                |

| H TWATH       | 1 // (2010:11:10)            | (1) (1)          | 弁理士 黒田 泰                 |

|               |                              | <br> (72) 発明者    | 守屋                       |

|               |                              | (12) 光明音         | • / /                    |

|               |                              |                  | 長野県諏訪市大和3丁目3番5号 セイコ      |

|               |                              |                  | ーエプソン株式会社内               |

|               |                              | (72) 発明者         | 伊藤 悟                     |

|               |                              |                  | 東京都日野市日野421-8 エプソント      |

|               |                              |                  | ヨコム株式会社内                 |

|               |                              |                  | 最終頁に続く                   |

(54) 【発明の名称】表示ドライバ及び電子機器

## (57)【特許請求の範囲】

## 【請求項1】

第1の短辺と第2の短辺と第1の長辺と第2の長辺とを有する表示ドライバであって、前記第1の短辺から前記第2の短辺へ向かう方向を第1の方向、前記第1の長辺から前記第2の長辺へ向かう方向を第2の方向とした場合に、

電源回路ブロックに配置される1次昇圧トランジスタと、

前記1次昇圧トランジスタのドレイン又はソースと1次昇圧用キャパシタを電気的に接続するためのパッドであって、パッド配置領域に前記第1方向に沿って位置する1次昇圧用パッドと、

前記パッド配置領域に配置されるK次昇圧トランジスタ(Kは2以上の整数)と、

前記 K 次昇圧トランジスタのドレイン又はソースと K 次昇圧用キャパシタを電気的に接続するためのパッドであって、前記パッド配置領域に前記第 1 方向に沿って位置する K 次昇圧用パッド(K は 2 以上の整数)と、を含み、

前記 K 次昇圧用パッドが前記 K 次昇圧トランジスタの一部又は全部に平面視においてオーバーラップする、

ことを特徴とする表示ドライバ。

# 【請求項2】

請求項1において、

入力側インターフェース領域と、

出力側インターフェース領域と、

前記入力側インターフェース領域と前記出力側インターフェース領域との間に位置する 第1~第Nの回路ブロック(Nは2以上の整数)と、を含み、

前記第1~第Nの回路ブロックが前記第1の方向に並んでおり、

前記K次昇圧トランジスタは、前記入力側インターフェース領域の前記パッド配置領域 に配置される、

ことを特徴とする表示ドライバ。

## 【請求項3】

請求項2において、

前記第1~第Nの回路ブロックのうちの2つの回路ブロックが第1のメモリブロックと 第2のメモリブロックであり、

10

20

30

前記第1のメモリブロックと前記第2のメモリブロックとが隣接して配置されている、 ことを特徴とする表示ドライバ。

#### 【請求項4】

請求項2又は3において、

前記第1~第Nの回路ブロックのうちの1つの回路ブロックが前記電源回路ブロックで

前記1次昇圧用パッドが前記K次昇圧用パッドよりも前記電源回路ブロックの近くに位 置する、

ことを特徴とする表示ドライバ。

### 【請求項5】

請求項2乃至4のいずれかにおいて、

前記第1~第Nの回路ブロックのうちの1つの回路ブロックが階調電圧生成回路ブロッ クであり、

前記階調電圧生成回路ブロックが使用する電圧が前記K次昇圧トランジスタを用いて生 成されるものである、

ことを特徴とする表示ドライバ。

### 【請求項6】

請求項2乃至5のいずれかにおいて、

前記出力側インターフェース領域の前記第2の方向における幅をW1、前記入力側イン ターフェース領域の前記第 2 の方向における幅をW 2 、前記第 1 ~ 第 N の回路ブロックの 前記第2の方向における幅をWBとしたとき、WB>W1+W2である、

ことを特徴とする表示ドライバ。

### 【請求項7】

請求項2乃至6のいずれかにおいて、

前記表示ドライバの前記第2の方向における幅をW、前記第1~第Nの回路ブロックの 前記第2の方向における幅をWBとしたとき、W<2×WBである、

ことを特徴とする表示ドライバ。

### 【請求項8】

請求項1乃至7のいずれかにおいて、

静電気保護素子が前記パッド配置領域に配置される、

ことを特徴とする表示ドライバ。

#### 【請求項9】

請求項1乃至8のいずれかにおいて、

電源間保護回路が前記パッド配置領域に配置される、

ことを特徴とする表示ドライバ。

## 【請求項10】

請求項1乃至9のいずれかに記載の表示ドライバと、

前記表示ドライバにより駆動される表示パネルと、

を含むことを特徴とする電子機器。

# 【発明の詳細な説明】

40

#### 【技術分野】

### [0001]

本発明は、表示ドライバ及び電子機器に関する。

### 【背景技術】

## [0002]

液晶パネルなどの表示パネルを駆動する集積回路装置として表示ドライバ(LCDドライバ)がある。この表示ドライバでは、低コスト化のためにチップサイズの縮小が要求される。

### [0003]

しかしながら、携帯電話機などに組み込まれる表示パネルの大きさはほぼ一定である。 従って、微細プロセスを採用し、表示ドライバの集積回路装置を単純にシュリンクしてチップサイズを縮小しようとすると、実装が困難になるなどの問題を招く。

#### 【先行技術文献】

## 【特許文献】

## [0004]

【特許文献1】特開2001-22249号公報

### 【発明の概要】

【発明が解決しようとする課題】

#### [0005]

本発明は、以上のような技術的課題に鑑みてなされたものであり、その目的とするところは、回路の小面積化や実装時の不具合防止を実現できる<u>表示ドライバ</u>及びこれを含む電子機器を提供することにある。

### 【課題を解決するための手段】

#### [0006]

本発明は、昇圧用キャパシタを用いたチャージポンプにより電圧を昇圧して電源電圧を生成する電源回路ブロックと、パッドが配置されるパッド配置領域とを含み、チャージポンプにより電圧の1次昇圧を行う1次昇圧回路の1次昇圧トランジスタが、前記電源回路ブロック内に配置され、チャージポンプにより電圧のK次昇圧(Kは2以上の整数)を行い、前記1次昇圧回路よりも絶対値が大きな電圧を生成するK次昇圧回路のK次昇圧トランジスタが、前記パッド配置領域に配置される集積回路装置に関係する。

#### [0007]

本発明では、1次昇圧回路の1次昇圧トランジスタについては、電源回路ブロック内に配置される。一方、K次昇圧回路のK次昇圧トランジスタについては、電源回路ブロックではなくパッド配置領域に配置される。このようにすれば、1次昇圧回路の昇圧動作の高効率を維持しながら、集積回路装置の小面積化を図れる。

#### [00008]

また本発明では、前記パッド配置領域には、前記1次昇圧トランジスタのドレイン又は ソースと1次昇圧用キャパシタとを電気的に接続するための1次昇圧用パッドと、前記 K 次昇圧トランジスタのドレイン又はソースと K 次昇圧用キャパシタとを電気的に接続する ための K 次昇圧用パッドとが配置され、前記1次昇圧用パッドの第1の方向側に、前記 K 次昇圧用パッドが配置され、前記第1の方向に直交する方向を第2の方向とした場合に、 前記1次昇圧用パッドの前記第2の方向側に、前記1次昇圧トランジスタが配置されても よい。

## [0009]

このようにすれば、1次昇圧トランジスタの近くに1次昇圧用パッドを配置できるようになり、1次昇圧回路の昇圧動作の高効率を維持できる。

#### [0010]

また本発明では、前記K次昇圧トランジスタは、その少なくとも一部が前記K次昇圧用パッドにオーバラップするように、前記K次昇圧用パッドの下層に配置されてもよい。

## [0011]

50

20

10

30

このようにすれば、パッドの下層の領域を有効活用してK次昇圧トランジスタを配置でき、集積回路装置の小面積化を図れる。

### [0012]

また本発明では、複数の前記 1 次昇圧用パッドの中にはダミーパッドが配置されず、複数の前記 K 次昇圧用パッドの中にはダミーパッドが配置されてもよい。

#### [0013]

このようにすれば、K次昇圧用パッド間の距離を離すことが可能になり、実装時の不具合等を解消できる。

## [0014]

また本発明では、前記電源回路ブロックを含む第1~第Nの回路ブロック(Nは2以上の整数)が、前記第1の方向に沿って配置され、前記第2の方向の反対方向を第4の方向とした場合に、前記K次昇圧トランジスタは、前記第1~第Nの回路ブロックの前記第4の方向側に、前記第1の方向に沿って配置されてもよい。

### [0015]

このようにすれば、配線効率の向上や昇圧用キャパシタの実装の容易化等を図れる。

#### [0016]

また本発明では、前記1次昇圧トランジスタに昇圧クロックを供給する1次昇圧制御回路と、前記K次昇圧トランジスタに昇圧クロックを供給するK次昇圧制御回路を含み、前記1次昇圧制御回路は前記電源回路プロック内に配置され、前記K次昇圧制御回路は前記パッド配置領域に配置されてもよい。

### [0017]

このようにすれば、昇圧クロックの配線長が長くなったり、配線長にバラツキが生じる ことなどによる不具合の発生を防止できる。

#### [0018]

また本発明では、データ線を駆動するための少なくとも1つのデータドライバブロックと、昇圧電圧を調整し、調整電圧を少なくとも前記データドライバブロックに供給するレギュレータを含み、前記レギュレータは、前記電源回路ブロック内に配置され、且つ、前記1次昇圧トランジスタと前記データドライバブロックとの間に配置されてもよい。

## [0019]

このようにすれば、無駄の無いショートパスの経路で電源電圧を供給できる。

#### [0020]

また本発明では、前記パッド配置領域には、前記レギュレータからの調整電圧を出力するためのレギュレータ用パッドと、前記1次昇圧トランジスタのドレイン又はソースと1次昇圧用キャパシタとを電気的に接続するための1次昇圧用パッドと、前記K次昇圧トランジスタのドレイン又はソースとK次昇圧用キャパシタとを電気的に接続するためのK次昇圧用パッドとが配置され、前記レギュレータ用パッドは、前記1次昇圧用パッドと前記K次昇圧用パッドの間に配置されてもよい。

### [0021]

このようにすれば、パッド配置領域の無駄の無い利用が可能になる。

#### [0022]

また本発明では、チャージポンプにより電圧の2次昇圧を行う2次昇圧回路の2次昇圧 トランジスタが、前記電源回路ブロック内に配置されてもよい。

#### [0023]

このようにすれば、2次昇圧回路の昇圧動作の高効率を維持できる。

#### [0024]

また本発明は、集積回路装置の短辺である第1の辺から対向する第3の辺へと向かう方向を第1の方向とし、集積回路装置の長辺である第2の辺から対向する第4の辺へと向かう方向を第2の方向とした場合に、前記第1の方向に沿って配置される第1~第Nの回路ブロック(Nは2以上の整数)と、前記第1~第Nの回路ブロックの前記第2の方向側に前記第4の辺に沿って設けられ、パッド配置領域となる第1のインターフェース領域と、

10

20

30

40

前記第2の方向の反対方向を第4の方向とした場合に、前記第1~第Nの回路ブロックの前記第4の方向側に前記第2の辺に沿って設けられ、パッド配置領域となる第2のインターフェース領域とを含み、前記第1~第Nの回路ブロックは、昇圧用キャパシタを用いたチャージポンプにより電圧を昇圧して電源電圧を生成する電源回路ブロックと、他の回路ブロックを含み、チャージポンプにより電圧の1次昇圧を行う1次昇圧回路の1次昇圧トランジスタが、前記電源回路ブロック内に配置され、チャージポンプにより電圧のK次昇圧(Kは2以上の整数)を行い、前記1次昇圧回路よりも絶対値が大きな電圧を生成するK次昇圧回路のK次昇圧トランジスタが、前記第2のインターフェース領域に配置される集積回路装置に関係する。

## [0025]

10

本発明によれば、1次昇圧回路の昇圧動作の高効率を維持しながら、集積回路装置の小面積化を図れる。

#### [0026]

また本発明は、集積回路装置の短辺である第1の辺から対向する第3の辺へと向かう方向を第1の方向とし、集積回路装置の長辺である第2の辺から対向する第4の辺へと向かう方向を第2の方向とした場合に、前記第1~第Nの回路プロックの前記第2の方向側に前記第4の辺に沿って設けられ、パッド配置領域となる第1のインターフェース領域との前記第2の方向の反対方向を第4の方向とした場合に、前記第1~第Nの回路プロックが、複数列配置される東積回路装置に関係する。

## [0027]

30

20

本発明によれば、第1のエリアでは、第2の方向に沿ってI個配列された電源回路ブロック用パッドの列が、複数列配置される。同様に第2のエリアにおいても、第2の方向に沿ってI個配列されたパッドの列が、複数列配置される。このようにすれば、集積回路装置に掛かる応力を均一化でき、応力の不均一を原因とする不具合の発生を防止できる。

### [0028]

また本発明では、前記第1のエリアには、I行J列(Jは2以上の整数)の前記電源回路ブロック用パッドが配置され、前記第2のエリアにも、I行J列のパッドが配置されてもよい。

### [0029]

また本発明では、チャージポンプにより電圧の1次昇圧を行う1次昇圧回路の1次昇圧トランジスタが、前記電源回路ブロック内に配置され、前記第2のインターフェース領域に配置される前記電源回路ブロック用のパッドは、前記1次昇圧トランジスタのドレイン又はソースと1次昇圧用キャパシタとを電気的に接続するための1次昇圧用パッドであってもよい。

## [0030]

また本発明では、1個の前記1次昇圧トランジスタのドレイン又はソースに対して、複数個の前記1次昇圧用パッドが接続されてもよい。

#### [0031]

このようにすれば、例えば集積回路装置を実装したときのパッドでの接触抵抗値の減少等を図れ、1次昇圧回路の昇圧動作の高効率を維持できる。

## [0032]

また本発明では、チャージポンプにより電圧の K 次昇圧( K は 2 以上の整数)を行い、前記 1 次昇圧回路よりも絶対値が大きな電圧を生成する K 次昇圧回路の K 次昇圧トランジスタと、前記 K 次昇圧トランジスタのドレイン又はソースと K 次昇圧用キャパシタとを電気的に接続するための K 次昇圧用パッドが、前記第 2 のインターフェース領域に配置されてもよい。

#### [0033]

このようにすれば、1次昇圧回路の昇圧動作の高効率を維持しながら、集積回路装置の 小面積化を図れる。

[0034]

また本発明では、前記K次昇圧トランジスタは、前記第1~第Nの回路ブロックの前記 第4の方向側に、前記第1の方向に沿って配置されてもよい。

[0035]

このようにすれば、配線効率の向上や昇圧用キャパシタの実装の容易化等を図れる。

[0036]

また本発明は、上記のいずれかに記載の集積回路装置と、前記集積回路装置により駆動される表示パネルとを含む電子機器に関係する。

【図面の簡単な説明】

[0037]

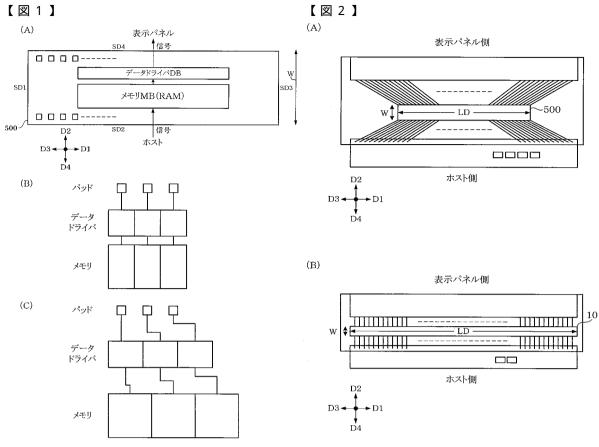

- 【図1】図1(A)(B)(C)は本実施形態の比較例の説明図。

- 【図2】図2(A)(B)は集積回路装置の実装についての説明図。

20

30

40

10

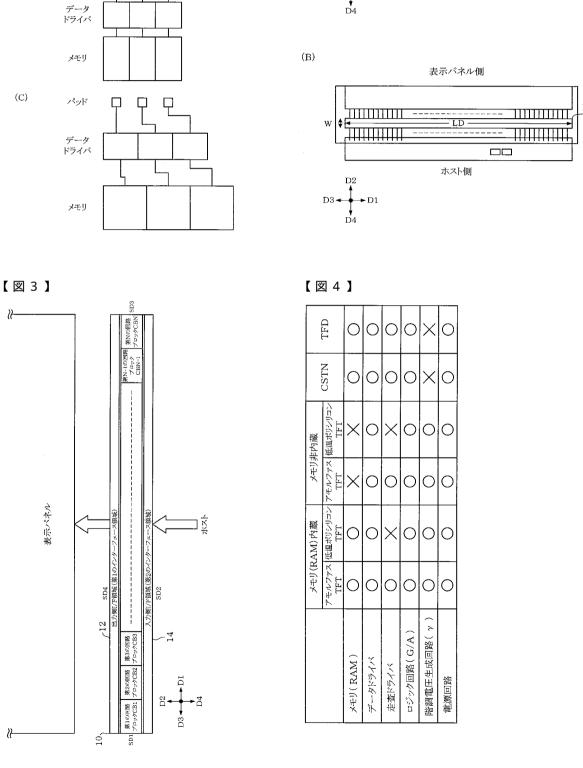

- 【図3】本実施形態の集積回路装置の構成例。

- 【図4】種々のタイプの表示ドライバとそれが内蔵する回路ブロックの例。

- 【図5】図5(A)(B)は本実施形態の集積回路装置の平面レイアウト例。

- 【図6】図6(A)(B)は集積回路装置の断面図の例。

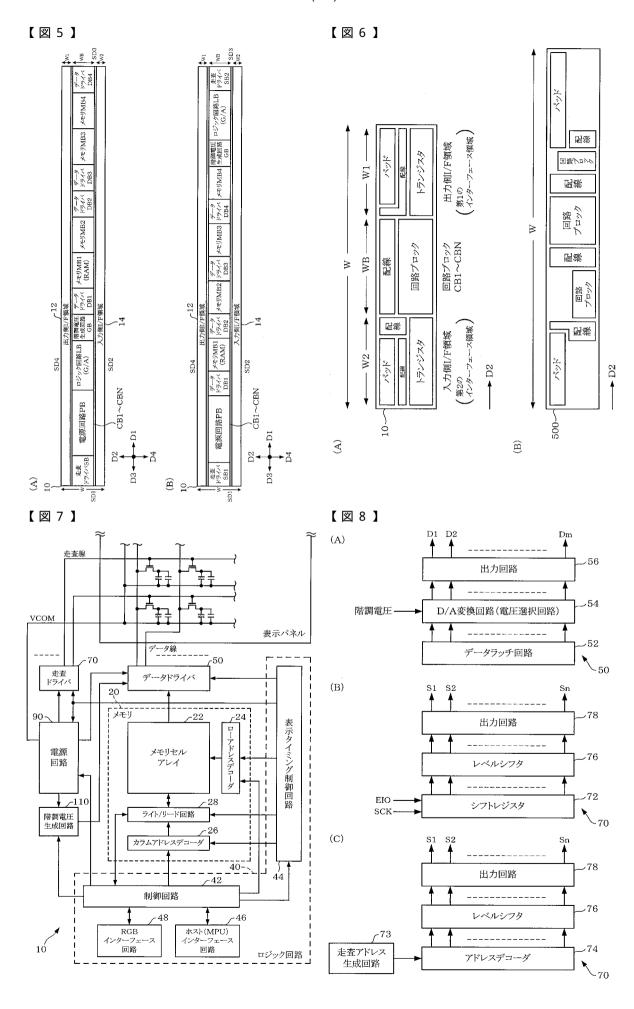

- 【図7】集積回路装置の回路構成例。

- 【図8】図8(A)(B)(C)はデータドライバ、走査ドライバの構成例。

- 【図9】図9(A)(B)は電源回路、階調電圧生成回路の構成例。

- 【図10】図10(A)(B)(C)はD/A変換回路、出力回路の構成例。

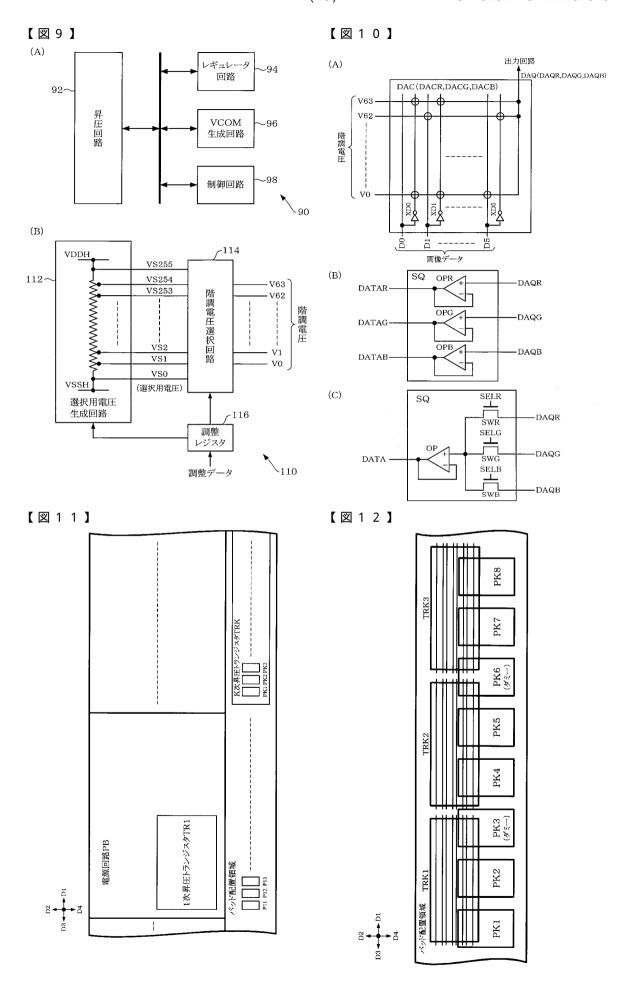

- 【図11】本実施形態の昇圧トランジスタの配置手法の説明図。

- 【図12】 K次昇圧トランジスタ、 K次昇圧用パッドのレイアウト例。

【図13】 K次昇圧トランジスタの配置例。

- 【図14】電源回路ブロックの詳細な構成及び配置例。

- 【図15】図15(A)(B)は昇圧回路の動作の説明図。

- 【図16】図16(A)(B)は1次昇圧回路、2次昇圧回路の構成例。

- 【図17】図17(A)(B)は3次昇圧回路、4次昇圧回路の構成例。

- 【図18】図18(A)(B)は応力均一化のためのパッド配置手法の説明図。

- 【図19】図19(A)(B)はメモリやデータドライバのブロック分割手法の説明図。

- 【図20】1水平走査期間に画像データを複数回読み出す手法の説明図。

- 【図21】データドライバ、ドライバセルの配置例。

- 【図22】図22(A)(B)は電子機器の構成例。

【発明を実施するための形態】

[0038]

以下、本発明の好適な実施の形態について詳細に説明する。なお以下に説明する本実施 形態は特許請求の範囲に記載された本発明の内容を不当に限定するものではなく、本実施 形態で説明される構成の全てが本発明の解決手段として必須であるとは限らない。

# [0039]

1. 比較例

図 1 ( A )に本実施形態の比較例となる集積回路装置 5 0 0 を示す。図 1 ( A )の集積回路装置 5 0 0 はメモリブロック M B (表示データ R A M )とデータドライバブロック D B を含む。そしてメモリブロック M B とデータドライバブロック D B は D 2 方向に沿って

配置されている。またメモリブロックMB、データドライバブロックDBは、D1方向に沿った長さがD2方向での幅に比べて長い超扁平なブロックになっている。

#### [0040]

ホスト側からの画像データはメモリブロックMBに書き込まれる。そしてデータドライバブロックDBは、メモリブロックMBに書き込まれたデジタルの画像データをアナログのデータ電圧に変換して、表示パネルのデータ線を駆動する。このように図1(A)において画像データの信号の流れはD2方向である。このため、図1(A)の比較例では、この信号の流れに合わせて、メモリブロックMBとデータドライバブロックDBをD2方向に沿って配置している。このようにすることで、入力と出力の間がショートパスになり、信号遅延を最適化でき、効率の良い信号伝達が可能になる。

[0041]

ところが図1(A)の比較例では以下のような課題がある。

## [0042]

第1に、表示ドライバなどの集積回路装置では、低コスト化のためにチップサイズの縮小が要求される。ところが、微細プロセスを採用し、集積回路装置 5 0 0 を単純にシュリンクしてチップサイズを縮小すると、短辺方向のみならず長辺方向も縮小されてしまう。従って図 2 (A)に示すように実装の困難化の問題を招く。即ち出力ピッチは、例えば 2 μ m 以上であることが望ましいが、図 2 (A)のような単純シュリンクでは例えば 1 7 μ m ピッチになってしまい、狭ピッチのために実装が困難になる。また表示パネルのガラスの額縁が広くなり、ガラスの取れ数が減少し、コスト増を招く。

[0043]

第2に、表示ドライバでは、表示パネルの種類(アモルファスTFT、低温ポリシリコンTFT)や画素数(QCIF、QVGA、VGA)や製品の仕様などに応じて、メモリやデータドライバの構成が変わる。従って図1(A)の比較例では、ある製品では図1(B)のように、パッドピッチとメモリのセルピッチとデータドライバのセルピチが一致していたとしても、メモリやデータドライバの構成が変わると、図1(C)に示すようにこれらのピッチが一致しなくなる。そして図1(C)のようにピッチが一致しなくなると、回路ブロック間に、ピッチの不一致を吸収するための無駄な配線領域を形成しなければならなくなる。特にD1方向にブロックが扁平している図1(A)の比較例では、ピッチの不一致を吸収するための無駄な配線領域が大きくなる。この結果、集積回路装置500のD2方向での幅Wが大きくなり、チップ面積が増加し、コスト増を招く。

[0044]

一方、このような事態を避けるために、パッドピッチとセルピッチが揃うようにメモリやデータドライバのレイアウトを変更すると、開発期間が長期化し、結局、コスト増を招く。即ち図1(A)の比較例では、各回路ブロックの回路構成やレイアウトを個別設計し、その後にピッチ等を合わせるという作業を行うため、無駄な空き領域が生じたり、設計が非効率化するなどの問題が生じる。

[0045]

## 2.集積回路装置の構成

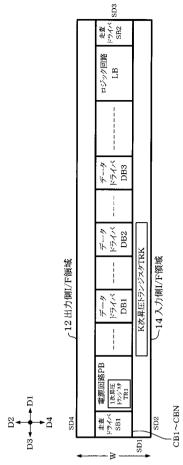

以上のような問題を解決できる本実施形態の集積回路装置10の構成例を図3に示す。本実施形態では、集積回路装置10の短辺である第1の辺SD1から対向する第3の辺SD3へと向かう方向を第1の方向D1とし、D1の反対方向を第3の方向D3としている。また集積回路装置10の長辺である第2の辺SD2から対向する第4の辺SD4へと向かう方向を第2の方向D2とし、D2の反対方向を第4の方向D4としている。なお、図3では集積回路装置10の左辺が第1の辺SD1で、右辺が第3の辺SD3になっているが、左辺が第3の辺SD3で、右辺が第1の辺SD1であってもよい。

#### [0046]

図3に示すように本実施形態の集積回路装置10は、D1方向に沿って配置される第1~第Nの回路ブロックCB1~CBN(Nは2以上の整数)を含む。即ち、図1(A)の比較例では回路ブロックがD2方向に並んでいるが、本実施形態では回路ブロックCB1

10

20

30

40

20

30

40

50

~ CBNがD1方向に並んでいる。また各回路ブロックは、図1(A)の比較例のような 超扁平なブロックになっておらず、比較的スクウェアなブロックになっている。

### [0047]

また集積回路装置10は、第1~第Nの回路ブロックCB1~CBNのD2方向側に辺SD4に沿って設けられる出力側I/F領域12(広義には第1のインターフェース領域)を含む。また第1~第Nの回路ブロックCB1~CBNのD4方向側に辺SD2に沿って設けられる入力側I/F領域14(広義には第2のインターフェース領域)を含む。より具体的には、出力側I/F領域12(第1のI/O領域)は、回路ブロックCB1~CBNのD2方向側に、例えば他の回路ブロック等を介さずに配置される。また入力側I/F領域14(第2のI/O領域)は、回路ブロックCB1~CBNのD4方向側に、例えば他の回路ブロック等を介さずに配置される。即ち少なくともデータドライバブロックが存在する部分において、D2方向において1つの回路ブロック(データドライバブロック)だけが存在する。なお集積回路装置10をIP(Intellectual Property)コアとして用いて他の集積回路装置に組み込む場合等には、I/F領域12、14の少なくとも一方を設けない構成とすることもできる。

#### [0048]

出力側(表示パネル側) I / F 領域 1 2 は、表示パネルとのインターフェースとなる領域であり、パッドや、パッドに接続される出力用トランジスタ、保護素子などの種々の素子を含む。具体的には、データ線へのデータ信号や走査線への走査信号を出力するための出力用トランジスタなどを含む。なお表示パネルがタッチパネルである場合等には、入力用トランジスタを含んでもよい。

#### [0049]

入力側(ホスト側) I / F 領域 1 4 は、ホスト(M P U、画像処理コントローラ、ベースバンドエンジン)とのインターフェースとなる領域であり、パッドや、パッドに接続される入力用(入出力用)トランジスタ、出力用トランジスタ、保護素子などの種々の素子を含むことができる。具体的には、ホストからの信号(デジタル信号)を入力するための入力用トランジスタやホストへの信号を出力するための出力用トランジスタなどを含む。

#### [0050]

なお、短辺である辺SD1、SD3に沿った出力側又は入力側I/F領域を設けるようにしてもよい。また外部接続端子となるバンプ等は、I/F(インターフェース)領域12、14に設けてもよいし、それ以外の領域(第1~第Nの回路ブロックCB1~CBN)に設けてもよい。I/F領域12、14以外の領域に設ける場合には、金バンプ以外の小型バンプ技術(樹脂をコアとするバンプ技術など)を用いることで実現される。

### [0051]

また第1~第Nの回路ブロックCB1~CBNは、少なくとも2つ(或いは3つ)の異なる回路ブロック(異なる機能を持つ回路ブロック)を含むことができる。集積回路装置10が表示ドライバである場合を例にとれば、回路ブロックCB1~CBNは、データドライバ、メモリ、走査ドライバ、ロジック回路、階調電圧生成回路、電源回路のブロックの少なくとも2つを含むことができる。更に具体的には回路ブロックCB1~CBNは、少なくともデータドライバ、ロジック回路のブロックを含むことができ、更に階調電圧生成回路のブロックを含むことができる。またメモリ内蔵タイプの場合には更にメモリのブロックを含むことができる。

## [0052]

例えば図4に種々のタイプの表示ドライバとそれが内蔵する回路ブロックの例を示す。 メモリ(RAM)内蔵のアモルファスTFT(Thin Film Transistor)パネル用表示ドラ イバでは、回路ブロックCB1~CBNは、メモリ、データドライバ(ソースドライバ) 、走査ドライバ(ゲートドライバ)、ロジック回路(ゲートアレイ回路)、階調電圧生成 回路( 補正回路)、電源回路のブロックを含む。一方、メモリ内蔵の低温ポリシリコン (LTPS)TFTパネル用表示ドライバでは、走査ドライバをガラス基板に形成できる ため、走査ドライバのブロックを省略できる。またメモリ非内蔵のアモルファスTFTパ

20

30

ネル用では、メモリのブロックを省略でき、メモリ非内蔵の低温ポリシリコンTFTパネル用では、メモリ及び走査ドライバのブロックを省略できる。またCSTN(Color Super Twisted Nematic)パネル、TFD(Thin Film Diode)パネル用では、階調電圧生成回路のブロックを省略できる。

## [0053]

図 5 ( A ) ( B ) に本実施形態の表示ドライバの集積回路装置 1 0 の平面レイアウトの例を示す。図 5 ( A ) ( B ) は、メモリ内蔵のアモルファスTFTパネル用の例であり、図 5 ( A ) は例えばQCIF、 3 2 階調用の表示ドライバをターゲットとし、図 5 ( B ) はQVGA、 6 4 階調用の表示ドライバをターゲットとしている。

## [0054]

図 5 ( A )( B )では、第 1 ~第 N の回路 ブロック C B 1 ~ C B N は、第 1 ~第 4 の メモリブロック M B 1 ~ M B 4 (広義には第 1 ~ 第 I の メモリブロック。 I は 2 以上の整数)を含む。また第 1 ~ 第 4 の メモリブロック M B 1 ~ M B 4 の A 々に対して、 D 1 方向に沿ってその A 々が隣接して配置される第 1 ~ 第 4 の データドライバブロック D B 1 ~ D B 4 (広義には第 1 ~ 第 I の データドライバブロック)を含む。具体的にはメモリブロック M B 1 と データドライバブロック D B 1 が D 1 方向に沿って 隣接して配置され、 メモリブロック M B 2 と データドライバブロック D B 2 が D 1 方向に沿って 隣接して配置される。 そして データドライバブロック D B 1 が データ線を 駆動する ために 用いる 画像 データ (表示 データ)は、 隣接する メモリブロック M B 1 が 記憶 し、 データドライバブロック D B 2 が データ線を 駆動する ために 用いる 画像 データ は、 隣接する メモリブロック M B 2 が 記憶 する。

## [0055]

また図5(A)では、メモリブロックMB1~MB4のうちのMB1(広義には第Jのメモリブロック。1 J<I)のD3方向側に、データドライバブロックDB1~DB4のうちのDB1(広義には第Jのデータドライバブロック)が隣接して配置される。またメモリブロックMB1のD1方向側に、メモリブロックMB2(広義には第J+1のメモリブロックMB2のD1方向側に、データドライバブロック)が隣接して配置される。そしてメモリブロックMB2のD1方向側に、データドライバブロックDB3、DB4の配置される。メモリブロックMB3、MB4、データドライバブロックDB3、DB4の配置も同様である。このように図5(A)では、MB1、MB2の境界線に対して線対称にMB1、DB1とMB2、DB2が配置され、MB3、MB4の境界線に対して線対称にMB3、DB3とMB4、OB4とが配置される。なお図5(A)では、DB2とDB3が隣接して配置されているが、これらを隣接させずに、その間に他の回路ブロックを配置してもよい。

## [0056]

一方、図5(B)では、メモリブロックMB1~MB4のうちのMB1(第Jのメモリブロック)のD3方向側に、データドライバブロックDB1~DB4のうちのDB1(第Jのデータドライバブロック)が隣接して配置される。またMB1のD1方向側にDB2(第J+1のデータドライバブロック)が配置される。またDB2のD1方向側にMB2(第J+1のメモリブロック)が配置される。DB3、MB3、DB4、MB4も同様に配置される。なお図5(B)では、MB1とDB2、MB2とDB3、MB3とDB4が、各々、隣接して配置されているが、これらを隣接させずに、その間に他の回路ブロックを配置してもよい。

# [0057]

図5(A)のレイアウト配置によれば、メモリブロックMB1とMB2や、MB3とMB4の間で(第J、第J+1のメモリブロックの間で)、カラムアドレスデコーダを共用できるという利点がある。一方、図5(B)のレイアウト配置によれば、データドライバブロックDB1~DB4から出力側I/F領域12へのデータ信号出力線の配線ピッチを均一化でき、配線効率を向上できるという利点がある。

## [0058]

50

なお本実施形態の集積回路装置10のレイアウト配置は図5(A)(B)に限定されない。例えばメモリブロックやデータドライバブロックのブロック数を2、3或いは5以上にしてもよいし、メモリブロックやデータドライバブロックをブロック分割しない構成にしてもよい。またメモリブロックとデータドライバブロックが隣接しないようにする変形実施も可能である。またメモリブロック、走査ドライバブロック、電源回路ブロック又は階調電圧生成回路ブロックなどを設けない構成としてもよい。また回路ブロックCB1~CBNと出力側I/F領域12や入力側I/F領域14の間に、D2方向での幅が極めて狭い回路ブロック(WB以下の細長回路ブロック)を設けてもよい。また回路ブロックCB1~CBNが、異なる回路ブロックがD2方向に多段に並んだ回路ブロックを含んでもよい。例えば走査ドライバ回路と電源回路を1つの回路ブロックとした構成としてもよい

10

20

30

### [0059]

図6(A)に本実施形態の集積回路装置10のD2方向に沿った断面図の例を示す。ここでW1、WB、W2は、各々、出力側I/F領域12、回路プロックCB1~CBN、入力側I/F領域14のD2方向での幅である。またWは集積回路装置10のD2方向での幅である。

### [0060]

本実施形態では図6(A)に示すように、D2方向において、回路ブロックCB1~CBN(データドライバブロックDB)と出力側、入力側 I / F領域 I 2、 I 4 との間に他の回路ブロックが介在しない構成にできる。従って、W1+WB+W2-W<W1+2×WB+W2とすることができ、細長の集積回路装置を実現できる。具体的には、D2方向での幅Wは、W<2mmとすることができ、更に具体的にはW<1.5mmとすることができる。なおチップの検査やマウンティングを考慮すると、W>0.9mmであることが望ましい。また長辺方向での長さLDは、I 5 mm<LD<27mmとすることができる。またチップ形状比SP=LD/Wは、SP>10とすることができ、更に具体的にはSP>12とすることができる。

[0061]

なお図6(A)の幅W1、WB、W2は、各々、出力側I/F領域12、回路ブロックCB1~CBN、入力側I/F領域14のトランジスタ形成領域(バルク領域、アクティブ領域)の幅である。即ちI/F領域12、14には、出力用トランジスタ、入力用トランジスタ、入出力用トランジスタ、静電保護素子のトランジスタが形成される。また回路ブロックCB1~CBNには、回路を構成するトランジスタが形成される。そび1、WB、W2は、このようなトランジスタが形成されるウェル領域や拡散領域などを基準に決められる。例えば、よりスリムな細長の集積回路装置を実現するためには、回路とでは、よりでである。例れば、そのコアが樹脂で形成され、樹脂の表面に金属層が形成された樹脂コアバンプなどをトランジスタの上にもバンプの形成領域の幅ではなく、バンプの下に形成されるトランジスタ形成領域の幅である。

40

## [0062]

また回路ブロック C B 1 ~ C B N の各々の D 2 方向での幅は、例えば同じ幅に統一できる。この場合、各回路ブロックの幅は、実質的に同じであればよく、例えば数  $\mu$  m ~ 2 0  $\mu$  m (数  $\mu$  m ) 程度の違いは許容範囲内である。また回路ブロック C B 1 ~ C B N の中に、幅が異なる回路ブロックが存在する場合には、幅W B は、回路ブロック C B 1 ~ C B N の幅の中の最大幅とすることができる。この場合の最大幅は、例えばデータドライバブロックの D 2 方向での幅とすることができる。或いはメモリ内蔵の集積回路装置の場合にはメモリブロックの D 2 方向での幅とすることができる。なお回路ブロック C B 1 ~ C B N と I / F 領域 1 2 、 1 4 の間には、例えば 2 0 ~ 3 0  $\mu$  m 程度の幅の空き領域を設けることができる。

20

30

40

#### [0063]

また本実施形態では、出力側 I / F 領域 1 2 には D 2 方向での段数が 1 段又は複数段となるパッドを配置できる。従ってパッド幅(例えば 0 . 1 mm)やパッドピッチを考慮すると、出力側 I / F 領域 1 2 の D 2 方向での幅 W 1 は、 0 . 1 3 mm W 1 0 . 4 mmとすることができる。また入力側 I / F 領域 1 4 には、 D 2 方向での段数が 1 段となるパッドを配置できるため、入力側 I / F 領域 1 4 の幅 W 2 は、 0 . 1 mm W 2 0 . 2 mmとすることができる。また細長の集積回路装置を実現するためには、回路ブロック C B 1 ~ C B N 上に、ロジック回路ブロックからのロジック信号や、階調電圧生成回路プロックからの階調電圧信号や、電源配線を、グローバル配線により形成する必要があり、これらの配線幅は合計で例えば 0 . 8 ~ 0 . 9 mm程度になる。従って、これらを考慮すると、回路ブロック C B 1 ~ C B N の幅 W B は、 0 . 6 5 mm W B 1 . 2 mmとすることできる。

#### [0064]

そしてW 1 = 0 . 4 mm、W 2 = 0 . 2 mmであったとしても、0 . 6 5 mm W B 1 . 2 mmであるため、W B > W 1 + W 2 が成り立つ。またW 1、W B、W 2 が最も小さい値である場合には、W 1 = 0 . 1 3 mm、W B = 0 . 6 5 mm、W 2 = 0 . 1 mmとなり、集積回路装置の幅はW = 0 . 8 8 mm程度になる。従って、W = 0 . 8 8 mm < 2 × W B = 1 . 3 mmが成り立つ。またW 1、W B、W 2 が最も大きい値である場合には、W 1 = 0 . 4 mm、W B = 1 . 2 mm、W 2 = 0 . 2 mmとなり、集積回路装置の幅はW = 1 . 8 mm程度になる。従って、W = 1 . 8 mm < 2 × W B = 2 . 4 mmが成り立つ。従ってW < 2 × W B の関係式が成り立ち、細長の集積回路装置を実現できる。

#### [0065]

図1(A)の比較例では、図6(B)に示すように2以上の複数の回路ブロックがD2方向に沿って配置される。またD2方向において、回路ブロック間や、回路ブロックとI/F領域の間に配線領域が形成される。従って集積回路装置500のD2方向(短辺方向)での幅Wが大きくなり、スリムな細長チップを実現できない。従って微細プロセスを利用してチップをシュリンクしても、図2(A)に示すようにD1方向(長辺方向)での長さLDも短くなってしまい、出力ピッチが狭ピッチになるため、実装の困難化を招く。

## [0066]

これに対して本実施形態では図3、図5(A)(B)に示すように複数の回路ブロック CB1~CBNがD1方向に沿って配置される。また図6(A)に示すように、パッド(バンプ)の下にトランジスタ(回路素子)を配置できる(能動面バンプ)。また回路ブロック内の配線であるローカル配線よりも上層(パッドよりも下層)で形成されるグローバル配線により、回路ブロック間や、回路ブロックとI/F領域間等での信号線を形成できる。従って図2(B)に示すように、集積回路装置10のD1方向での長さLDを維持したままで、D2方向での幅Wを狭くでき、超スリムな細長チップを実現できる。この結果、出力ピッチを例えば22μm以上に維持することができ、実装を容易化できる。

### [0067]

また本実施形態では複数の回路ブロックCB1~CBNがD1方向に沿って配置されるため、製品の仕様変更等に容易に対応できる。即ち共通のプラットフォームを用いて様々な仕様の製品を設計できるため、設計効率を向上できる。例えば図5(A)(B)において、表示パネルの画素数や階調数が増減した場合にも、メモリブロックやデータドライバブロックのブロック数や、1水平走査期間での画像データの読み出し回数等を増減するだけで対応できる。また図5(A)(B)はメモリ内蔵のアモルファスTFTパネル用の例であるが、メモリ内蔵の低温ポリシリコンTFTパネル用の製品を開発する場合には、ロ路ブロックCB1~CBNの中から走査ドライバブロックを取り除くだけで済む。またメモリ非内蔵の製品を開発する場合には、メモリブロックを取り除けば済む。そしてこのように仕様に合わせて回路ブロックを取り除いても、本実施形態では、それが他の回路ブロックに及ぼす影響が最小限に抑えられるため、設計効率を向上できる。

## [0068]

20

30

40

50

また本実施形態では、各回路ブロックCB1~CBNのD2方向での幅(高さ)を、例えばデータドライバブロックやメモリブロックの幅(高さ)に統一できる。そして各回路ブロックのトランジスタ数が増減した場合には、各回路ブロックのD1方向での長さを増減することで調整できるため、設計を更に効率化できる。例えば図5(A)(B)において、階調電圧生成回路ブロックや電源回路ブロックの構成が変更になり、トランジスタ数が増減した場合にも、階調電圧生成回路ブロックや電源回路ブロックのD1方向での長さを増減することで対応できる。

## [0069]

なお第2の比較例として、例えばデータドライバブロックをD1方向に細長に配置し、データドライバブロックのD4方向側に、メモリブロックなどの他の複数の回路ブロックをD1方向に沿って配置する手法も考えられる。しかしながらこの第2の比較例では、メモリブロックなどの他の回路ブロックと出力側I/F領域との間に、幅の大きなデータドライバブロックが介在するようになるため、集積回路装置のD2方向での幅Wが大きくなり、スリムな細長チップの実現が困難になる。またデータドライバブロックとメモリブロックの間に無駄な配線領域が生じてしまい、幅Wが更に大きくなってしまう。またデータドライバブロックやメモリブロックの構成が変わった場合には、図1(B)(C)で説明したピッチの不一致の問題が生じ、設計効率を向上できない。

## [0070]

また本実施形態の第3の比較例として、同一機能の回路ブロック(例えばデータドライバブロック)だけをブロック分割して、D1方向に並べて配置する手法も考えられる。しかしながら、この第3の比較例では、集積回路装置に同一機能(例えばデータドライバの機能)だけしか持たせることができないため、多様な製品展開を実現できない。これに対して本実施形態では、回路ブロックCB1~CBNは、少なくとも2つの異なる機能を有する回路ブロックを含む。従って図4、図5(A)(B)に示すように、様々なタイプの表示パネルに対応した多様な機種の集積回路装置を提供できるという利点がある。

## [0071]

## 3.回路構成

図7に集積回路装置10の回路構成例を示す。なお集積回路装置10の回路構成は図7に限定されるものではなく、種々の変形実施が可能である。メモリ20(表示データRAM)は画像データを記憶する。メモリセルアレイ22は複数のメモリセルを含み、少なとも1フレーム(1画面)分の画像データ(表示データ)を記憶する。この場合、1回転は例えばR、G、Bの3サブピクセル(3ドット)で構成され、各サブピクセルについ例えば6ビット(kビット)の画像データが記憶される。ローアドレスデコーダ24(MPU/LCDローアドレスデコーダ)はローアドレスについてのデコード処理を行い、メモリセルアレイ22のワード線の選択処理を行う。カラムアドレスデコーダ26(MPUカラムアドレスデコーダ)はカラムアドレスについてのデコード処理を行い、メモリセルアレイ22のピット線の選択処理を行う。ライト/リード回路28(MPUライト/リード回路)はメモリセルアレイ22への画像データのライト処理や、メモリセルアレイ22のからの画像データのリード処理を行う。なおメモリセルアレイ22のアクセス領域はスタートアドレス及びローアドレスでアクセス領域が定義され、メモリアクセスが行われる。

## [0072]

ロジック回路40(例えば自動配置配線回路)は、表示タイミングを制御するための制御信号やデータ処理タイミングを制御するための制御信号などを生成する。このロジック回路40は例えばゲートアレイ(G/A)などの自動配置配線により形成できる。制御回路42は各種制御信号を生成したり、装置全体の制御を行う。具体的には階調電圧生成回路110に階調特性(特性)の調整データ(補正データ)を出力したり、電源回路90の電圧生成を制御する。またローアドレスデコーダ24、カラムアドレスデコーダ26、ライト/リード回路28を用いたメモリへのライト/リード処理を制御する。表示タイ

20

30

40

50

ミング制御回路44は表示タイミングを制御するための各種の制御信号を生成し、メモリから表示パネル側への画像データの読み出しを制御する。ホスト(MPU)インターフェース回路46は、ホストからのアクセス毎に内部パルスを発生してメモリにアクセスするホストインターフェースを実現する。RGBインターフェース回路48は、ドットクロックにより動画のRGBデータをメモリに書き込むRGBインターフェースを実現する。なおホストインターフェース回路46、RGBインターフェース回路48のいずれか一方のみを設ける構成としてもよい。

## [0073]

図 7 において、ホストインターフェース回路 4 6 、 R G B インターフェース回路 4 8 からは 1 画素単位でメモリ 2 0 へのアクセスが行われる。一方、データドライバ 5 0 へは、ホストインターフェース回路 4 6 、 R G B インターフェース回路 4 8 とは独立した内部表示タイミングにより、ライン周期毎に、ラインアドレスで指定されライン単位で読み出された画像データが送られる。

## [0074]

データドライバ50は表示パネルのデータ線を駆動するための回路であり、図8(A)にその構成例を示す。データラッチ回路52は、メモリ20からのデジタルの画像データをラッチする。D/A変換回路54(電圧選択回路)は、データラッチ回路52にラッチされたデジタルの画像データのD/A変換を行い、アナログのデータ電圧を生成する。具体的には階調電圧生成回路110から複数(例えば64段階)の階調電圧(基準電圧)を受け、これらの複数の階調電圧の中から、デジタルの画像データに対応する電圧を選択して、データ電圧として出力する。出力回路56(駆動回路、バッファ回路)は、D/A変換回路54からのデータ電圧をバッファリングして表示パネルのデータ線に出力し、データ線を駆動する。なお、出力回路56の一部(例えば演算増幅器の出力段)をデータドライバ50には含ませずに、他の領域に配置する構成としてもよい。

#### [0075]

走査ドライバ70は表示パネルの走査線を駆動するための回路であり、図8(B)にその構成例を示す。シフトレジスタ72は順次接続された複数のフリップフロップを含み、シフトクロック信号SCKに同期してイネーブル入出力信号EIOを順次シフトする。レベルシフタ76は、シフトレジスタ72からの信号の電圧レベルを、走査線選択のための高電圧レベルに変換する。出力回路78は、レベルシフタ76により変換されて出力された走査電圧をバッファリングして表示パネルの走査線に出力し、走査線を選択駆動する。なお走査ドライバ70は図8(C)に示す構成であってもよい。図8(C)では、走査アドレス生成回路73が走査アドレスを生成して出力し、アドレスデコーダ74が走査アドレスのデコード処理を行う。そしてこのデコード処理により特定された走査線に対して、レベルシフタ76、出力回路78を介して走査電圧が出力される。

## [0076]

電源回路90は各種の電源電圧を生成する回路であり、図9(A)にその構成例を示す。昇圧回路92は、入力電源電圧や内部電源電圧を、昇圧用キャパシタや昇圧用トランジスタを用いてチャージポンプ方式で昇圧し、昇圧電圧を生成する回路であり、1次~4次昇圧回路などを含むことができる。この昇圧回路92により、走査ドライバ70や階調電圧生成回路110が使用する高電圧を生成できる。レギュレータ回路94は、昇圧回路92により生成された昇圧電圧のレベル調整を行う。VCOM生成回路96は、表示パネルの対向電極に供給するVCOM電圧を生成して出力する。制御回路98は電源回路90の制御を行うものであり、各種の制御レジスタなどを含む。

#### [0077]

階調電圧生成回路(補正回路)110は階調電圧を生成する回路であり、図9(B)にその構成例を示す。選択用電圧生成回路112(電圧分割回路)は、電源回路90で生成された高電圧の電源電圧VDDH、VSSHに基づいて、選択用電圧VS0~VS25(広義にはR個の選択用電圧)を出力する。具体的には選択用電圧生成回路112は、直列に接続された複数の抵抗素子を有するラダー抵抗回路を含む。そしてVDDH、VS

SHを、このラダー抵抗回路により分割した電圧を、選択用電圧VS0~VS255として出力する。階調電圧選択回路114は、ロジック回路40により調整レジスタ116に設定された階調特性の調整データに基づいて、選択用電圧VS0~VS255の中から、例えば64階調の場合には64個(広義にはS個。R>S)の電圧を選択して、階調電圧V0~V63として出力する。このようにすれば表示パネルに応じた最適な階調特性(補正特性)の階調電圧を生成できる。なお極性反転駆動の場合には、正極性用のラダー抵抗回路と負極性用のラダー抵抗回路を選択用電圧生成回路112に設けてもよい。またラダー抵抗回路の各抵抗素子の抵抗値を、調整レジスタ116に設定された調整データに基づいて変更できるようにしてもよい。また選択用電圧生成回路112や階調電圧選択回路114に、インピーダンス変換回路(ボルテージフォロワ接続の演算増幅器)を設ける構成にしてもよい。

10

### [0078]

図10(A)に、図8(A)のD/A変換回路54が含む各DAC(Digital Analog Converter)の構成例を示す。図10(A)の各DACは、例えばサブピクセル毎(或いは画素毎)に設けることができ、ROMデコーダ等により構成される。そしてメモリ20からの6ビットのデジタルの画像データD0~D5とその反転データXD0~XD5に基づいて、階調電圧生成回路110からの階調電圧V0~V63のいずれかを選択することで、画像データD0~D5をアナログ電圧に変換する。そして得られたアナログ電圧の信号DAQ(DAQR、DAQG、DAQB)を出力回路56に出力する。

20

## [0079]

なお低温ポリシリコンTFT用の表示ドライバ等で、R用、G用、B用のデータ信号をマルチプレクスして表示ドライバに送る場合(図10(C)の場合)には、R用、G用、B用の画像データを、1つの共用のDACを用いてD/A変換することもできる。この場合には図10(A)の各DACは画素毎に設けられる。

[0800]

図10(B)に、図8(A)の出力回路56が含む各出力部SQの構成例を示す。図10(B)の各出力部SQは画素毎に設けることができる。各出力部SQは、R(赤)用、G(緑)用、B(青)用のインピーダンス変換回路OPR、OPG、OPB(ボルテージフォロワ接続の演算増幅器)を含み、DACからの信号DAQR、DAQG、DAQBのインピーダンス変換を行って、データ信号DATAR、DATAG、DATABをR、G、B用のデータ信号出力線に出力する。なお例えば低温ポリシリコンTFTパネルの場合には、図10(C)に示すようなスイッチ素子(スイッチ用トランジスタ)SWR、SWG、SWBを設け、R用、G用、B用のデータ信号が多重化されたデータ信号の名TAを、インピーダンス変換回路OPが出力するようにしてもよい。またデータ信号の多重化を複数画素に亘って行うようにしてもよい。また出力部SQに、図10(B)(C)のようなインピーダンス変換回路を設けずに、スイッチ素子等だけを設ける構成にしてもよい。

30

## [0081]

### 4.電源回路

## 4.1 K次昇圧トランジスタの配置

本実施形態では、集積回路装置のD2方向での幅を小さくし、細長のチップを実現するために、通常は回路ブロック内に配置されるべき素子についても、出力側I/F領域、入力側I/F領域などのパッド配置領域に配置している。

40

## [0082]

ここで、表示ドライバなどの集積回路装置には、LV(Low Voltage)領域やMV(Mid dle Voltage)領域やHV(High Voltage)領域が形成される場合がある。ここでLV領域(広義には第1の回路領域)は、LVの電圧レベル(広義には第1の電圧レベル)の電源で動作する回路が配置される領域である。またMV領域(広義には第2の回路領域)は、LVよりも高いMVの電圧レベル(広義には第2の電圧レベル)の電源で動作する回路が配置される領域である。またHV領域(広義には第3の回路領域)は、MVよりも高いHVの電圧レベル(広義には第3の電圧レベル)の電源で動作する回路が配置され領域で

20

30

40

50

ある。例えばロジック回路ブロックやメモリブロックの回路は L V 領域に形成される。またデータドライバブロックが有する D / A 変換器や演算増幅器は M V 領域に形成され、走査ドライバの出力トランジスタは H V 領域に形成される。

## [0083]

このようなLV、MV、HVの電源電圧を生成するために、本実施形態の集積回路装置には図11に示すような電源回路ブロックPBが設けられている。この電源回路ブロックPBでは、昇圧用キャパシタ(フライングキャパシタ)を用いたチャージポンプにより電圧を昇圧して、電源電圧を生成している。このため図11では、チャージポンプにより電圧の1次昇圧を行う1次昇圧回路の1次昇圧トランジスタTR1が設けられる。また、チャージポンプにより電圧のK次昇圧(Kは2以上の整数)を行い、1次昇圧回路よりも絶対値が大きな電圧(負電圧又は正電圧)を生成するK次昇圧回路のK次昇圧トランジスタTRK(複数のK次昇圧トランジスタ)が設けられる。ここでK次昇圧トランジスタTRKは、例えば2次或いは3次以上の次数の高い昇圧回路の昇圧トランジスタである。

### [0084]

チャージポンプ方式で昇圧を行う場合、昇圧用キャパシタに電荷を蓄積させる必要がある。そのため、プッシュプル接続される昇圧トランジスタのオン抵抗値をできるだけ低くする必要がある。抵抗値が高くなると、昇圧用キャパシタに蓄積される電荷量が少なくなり、昇圧動作の効率が悪くなるからである。このため、昇圧トランジスタのサイズは十分に大きくする必要がある。従って、このようなサイズの大きい全ての昇圧トランジスタを電源回路ブロックPB内に配置しようとすると、電源回路ブロックPBの面積が大きくなり、集積回路装置が大規模化する。

#### [0085]

一方、電源回路ブロック P B は、前述のように L V、M V、H V などの種々の電圧レベルの電源電圧を生成している。そして例えば M V の電源は、データドライバ内の演算増幅器、D / A 変換器や、各種アナログ回路の電源として使用され、その消費電力は大きい。従って M V の電源電圧の生成に使用される 1 次昇圧トランジスタについては、そのオン抵抗値のみならず、1 次昇圧トランジスタと 1 次昇圧用パッドとを接続する配線の寄生抵抗値も低くする必要がある。即ち 1 次昇圧トランジスタのオン抵抗値と配線の寄生抵抗値を含む 1 次昇圧回路の出力抵抗値を例えば 5 0 ~ 1 0 0 オーム以下にする必要がある。このため、1 次昇圧トランジスタの配置位置は、1 次昇圧用パッドになるべく近いことが望ましい。

## [0086]

これに対して、HV電源は、走査ドライバの出力トランジスタの電源に使用される。そして走査ドライバは、各水平走査において走査線を選択して、表示パネルのゲートを駆動するだけであるため、HV電源の消費電力はMV電源に比べて格段に少ない。従ってHVの電源電圧の生成に使用される3次、4次などのK次昇圧トランジスタに要求されるオン抵抗の設計値は大きく、例えばK次昇圧回路の出力抵抗値は500~1Kオーム以上である。従って、このようなK次昇圧トランジスタでは、K次昇圧トランジスタとK次昇圧用パッドとを接続する配線の寄生抵抗値は問題にならない。

#### [0087]

そこで本実施形態では図11に示すように、1次昇圧トランジスタTR1については電源回路プロックPB内に配置し、その近傍に1次昇圧用パッドP11、P12、P13・・・を配置する。このようにすれば、1次昇圧トランジスタTR1と1次昇圧用パッドP11、P12、P13・・・とを接続する配線の長さを短くでき、配線の寄生抵抗値を低くできる。従って1次昇圧トランジスタTR1のオン抵抗値と配線の寄生抵抗値を合わせた抵抗値も低くなり、MV電源で動作する回路に対する電源供給能力を高めることができる。なお1次昇圧用パッドは、例えば1次昇圧トランジスタTR1のドレイン又はソースと1次昇圧用キャパシタを電気的に接続するためのパッドなどである。

### [0088]

一方、図11では、高次の昇圧回路のトランジスタであるK次昇圧トランジスタTRK

20

30

40

50

( K次昇圧トランジスタ群)については、パッド配置領域に配置する。このようにすれば、 K次昇圧トランジスタTRKを電源回路プロックPBに配置しなくても済むようになり、パッド配置領域のパッド下の空きスペースにK次昇圧トランジスタTRKを配置できる。従って電源回路プロックPBの面積を小さくでき、集積回路装置の小面積化を図れる。なおパッド配置領域に昇圧用パッド以外のパッドを配置したり、ダミーのパッドを配置してもよい。或いは静電気保護素子(ダイオード)や電源間保護回路(電圧クランプ回路)を配置してもよい。またパッド配置領域は、例えば回路プロックの辺(境界、縁)と集積回路装置の辺(例えば第2、第4の辺)との間の領域であり、例えば図3の出力側I/F領域12、入力側I/F領域14である。パッドは少なくともその中心位置(パッドセンター)がパッド配置領域に配置されていればよい。従ってパッド配置領域の1次昇圧用パッドの一部が、電源回路プロックPB内の1次昇圧トランジスタの一部にオーバラップするようなレイアウトであってもよい。

[0089]

また図11では、1次昇圧用パッドP11、P12、P13・・・と、K次昇圧トランジスタTRKのドレイン又はソースとK次昇圧用キャパシタとを電気的に接続するためのK次昇圧用パッドPK1、PK2、PK3・・・が、パッド配置領域に配置される。そして1次昇圧用パッドP11、P12、P13・・・のD1方向側に、K次昇圧用パッドP81、9m3・・が配置され、1次昇圧用パッドP11、P12、P13・・・のD2方向側に、1次昇圧トランジスタTR1が配置される。このような配置によれば、1次昇圧用パッドP11、P12、P13・・・は、1次昇圧トランジスタTR1の直ぐ近くに配置されるようになり、1次昇圧用パッドP11、P12、P13・・・と1次昇圧トランジスタTR1(1次昇圧トランジスタ群)を接続する配線の寄生抵抗値をより一層低くできる。これによりMVの電源供給能力を向上できる。またこの配置によれば、K次昇圧用パッドPK1、PK2、PK3・・・についてもK次昇圧トランジスタTRKの近くに配置できる。従って、K次昇圧用パッドPK1、PK2、PK3・・・とK次昇圧トランジスタTRK(K次昇圧トランジスタ群)を接続する配線の引き回しが簡素になり、配線領域の面積増加が抑えられ、集積回路装置の小面積化を図れる。

[0090]

図12にK次昇圧トランジスタとK次昇圧用パッドの詳細なレイアウト例を示す。図12では、K次昇圧トランジスタTRK1、TRK2、TRK3は、その少なくとも一部がK次昇圧用パッド(パッドメタル)PK1~PK8にオーバラップするように、K次昇圧用パッドPK1~PK8の下層(下方)に配置される。別の言い方をすれば、K次昇圧トランジスタTRK1~TRK3の一部又は全部に平面視においてオーバラップするように、TRK1~TRK3の上層にK次昇圧用パッドPK1~PK8が配置される。なおK次昇圧トランジスタTRK1~TRK3はK次昇圧用パッドPK1~PK8以外のパッドの下層にも配置できる。

[0091]

パッドの下層にトランジスタを配置すると、ボンディングワイヤの接着時やバンプ実装時にパッドに加わった応力が原因となって、トランジスタのしきい値電圧が変動してしまう可能性がある。またトランジスタの層間膜の容量も設計時の容量に比べて変動する可能性がある。このためウェハ上でのトランジスタの特性が、実装時の特性とは異なるものになる不具合が生じるおそれがある。従って例えば演算増幅器などを構成するアナログ回路としてのトランジスタのように、アナログ電圧を出力するためのトランジスタについては、敢えてパッドの下層に配置しない。

[0092]

一方、 K 次昇圧トランジスタTR K 1 ~ T R K 3 のように、デジタルスイッチとして機能するトランジスタについては、パッドの下層に配置する。こうすることで、上記の不具合の発生を回避できると共に、集積回路装置のレイアウト面積を削減でき、集積回路装置の D 2 方向での幅をより一層小さくできる。例えば K 次昇圧トランジスタTR K 1 ~ T R K 3 の面積は大きいため、面積削減の効果は顕著である。

#### [0093]

また図12では、K次昇圧用パッドPK1~PK8の中にダミーパッドPK3、PK6を含ませて配置している。即ちK次昇圧回路では高い電位の電圧が生成される。従ってK次昇圧用パッド間の電位差は大きい。従ってパッド間の距離を離さないと、集積回路装置を実装したときにマイグレーションによるショート状態が発生するおそれがある。この点、図12のような、信号が接続されないダミーのパッドPK3、PK6等をK次昇圧用パッドPK1~PK8の中に含ませれば、ダミーではないK次昇圧用パッド間の距離を離すことができる。この結果、マイグレーションによるショート等の不具合を防止できる。

[0094]

一方、本実施形態では、1次昇圧用パッドの中にダミーパッドは配置しない。即ち後述するように本実施形態では、1次昇圧回路の1次昇圧トランジスタのソース又はドレイン(端子)に対して複数の1次昇圧用パッドを接続して、接触抵抗値を低減している。従って、1次昇圧用パッドの占有面積は大きく、この1次昇圧用パッドの中にダミーパッドを含ませると、更にその占有面積が大きくなってしまう。この結果、1次昇圧トランジスタと1次昇圧用パッドとの間の距離が離れてしまい、配線の寄生抵抗値が増え、1次昇圧回路の電源供給能力が低下する。また1次昇圧の場合には、K次昇圧の場合とは異なり、1次昇圧用パッド間に大きな電位差は生じず、マイグレーションによるショートの可能性も少ない。このため、本実施形態では、K次昇圧用パッドの中にはダミーパッドを配置しるいようにしている。

[0095]

図13に、図11の本実施形態の配置手法を図3の構成の集積回路装置に適用した場合の例を示す。図13では集積回路装置はD1方向に沿って配置される回路ブロックCB1~CBNを含み、これらのCB1~CBNは電源回路ブロックPBを含む。また走査ドライバブロックSB1、SB2、データドライバブロックDB1、DB2、DB3・・・、ロジック回路ブロックLBを含む。

[0096]

そして図13では、D2方向の反対方向をD4方向とした場合に、K次昇圧トランジスタTRKは、回路ブロックCB1~CBNのD4方向側にD1方向に沿って配置される。即ちD1方向に沿った細長の領域にK次昇圧トランジスタTRK(K次昇圧トランジスタ群)が配置される。

[0097]

即ち図13の集積回路装置をガラス基板等に実装した場合に、昇圧用キャパシタは集積回路装置のD4方向側に実装される。従って図13のように回路ブロックCB1~CBNのD4方向側にK次昇圧トランジスタTRK(複数のK次昇圧トランジスタ)を配置すれば、K次昇圧トランジスタTRKのドレイン又はソースと昇圧用キャパシタとを昇圧用パッドを介してショートパスの経路を接続できる。また昇圧用キャパシタの実装には、ある程度の実装面積が必要になるが、図13のように昇圧トランジスタTRKをD1方向に沿って細長に配置すれば、昇圧用キャパシタの実装を容易化できる。

[0098]

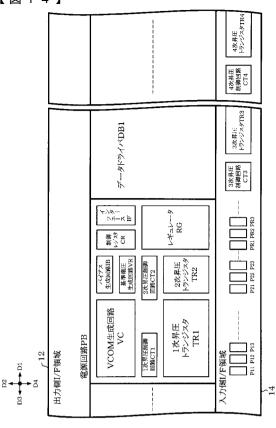

4.2 詳細な構成

図14に電源回路ブロックPBの詳細な構成例を示す。電源回路ブロックPBは、1次昇圧用トランジスタTR1、1次昇圧制御回路CT1、2次昇圧用トランジスタTR2、2次昇圧制御回路CT2を含む。またレギュレータRG、VCOM生成回路VC、バイアス生成回路IB、基準電圧生成回路VR、制御レジスタCR、インターフェースIF含む

[0099]

1次昇圧制御回路 C T 1 は 1 次昇圧回路の制御を行う回路であり、 1 次昇圧トランジスタ T R 1 に昇圧クロックを供給する。 2 次昇圧制御回路 C T 2 は 2 次昇圧回路の制御を行う回路であり、 2 次昇圧トランジスタ T R 2 に昇圧クロックを供給する。

[0100]

10

20

30

20

30

40

50

レギュレータRGは、昇圧電圧の調整を行い、調整電圧(レギュレーション電圧)を生成し、データドライバブロックDB1などの回路ブロックに供給する。VCOM生成回路VCは、表示パネルの対向電極に印加されるコモン電圧を生成する。バイアス生成回路IBは、演算増幅器などのアナログ回路に使用されるバイアス電流(バイアス電圧)を生成し、基準電圧生成回路VRは一定電圧である基準電圧を生成する。制御レジスタCRは、電源回路ブロックPBを制御するためのコマンドレジスタ等として機能する。インターフェースIFは、電源回路ブロックPBと他の回路ブロックとの間のインターフェース処理を行う。

### [0101]

また図14では、 K 次昇圧トランジスタである3次昇圧トランジスタTR3や4次昇圧トランジスタTR4が、パッド配置領域である入力側I/F領域14に配置されている。 更に3次昇圧トランジスタTR3に昇圧クロックを供給する3次昇圧制御回路CT3や、 4次昇圧トランジスタTR4に昇圧クロックを供給する4次昇圧制御回路CT4も、パッド配置領域である入力側I/F領域14に配置される。

### [0102]

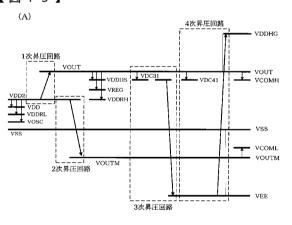

次に図15(A)の電位関係図を用いて昇圧回路の動作について説明する。1次昇圧トランジスタにより構成される1次昇圧回路は、図15(A)に示すように、昇圧用基準電源電圧VDD2と接地電源電圧VSSの間の電圧を正方向に昇圧し、1次昇圧電圧である電源電圧VDD2と接地電源電圧VSSの間の電圧を負方向に昇圧し、VSSよりも低電位の2次昇圧電圧である電源電圧VOUTMを生成する。3次昇圧トランジスタにより構成される3次昇圧回路は、選択入力された電源電圧VDC31と接地電源電圧VSSの間の電圧を負方向に昇圧し、走査ドライバ用の負電源電圧VEE(ゲートオフ電圧)を生成する。4次昇圧トランジスタにより構成される4次昇圧回路は、選択入力された電源電圧VDC41と電源電圧VEEの間の電圧を正方向に昇圧し、電源電圧VDDHG(ゲートオン電圧)を生成する。

### [0103]

レギュレータRGは、基準電源電圧VDD2の電位を調整(降圧)して、電源電圧VDD、VDDRL、VOSCを生成する。ここでVDD、VDDRL、VSOCは、各々、ロジック電源電圧、最小階調電圧、発振用電源電圧である。またレギュレータRGは、1次昇圧により得られた電源電圧VOUTの電位を調整して、電源電圧VDDHS、VREG、VDDRHは、各々、データドライバ用電源電圧、基準電圧、最大階調電圧である。

## [0104]

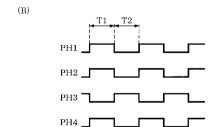

図15(B)に、1次昇圧制御回路CT1が生成する昇圧クロックPH1、PH2、PH3、PH4の波形例を示す。1次昇圧制御回路CT1は、これらの昇圧クロックPH1、PH2、PH2、PH4、PH4を1次昇圧トランジスタに供給して、そのゲートを制御する。この場合に1次昇圧トランジスタの貫通電流を防止するために、これらの昇圧クロックPH1~PH4は、その立ち上がリタイミング及び立ち下がリタイミングが重複せず、そのアクティブ期間がノンオーバラップとなるクロックになっている。なお2次、3次、4次昇圧制御回路CT2、CT3、CT4も図15(B)と同様の昇圧クロックを生成する。

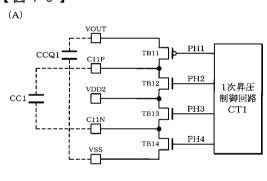

図16(A)に1次昇圧回路の構成例を示す。この1次昇圧回路は、1次昇圧トランジスタであるP型トランジスタTB11、N型トランジスタTB12、TB13、TB14と、1次昇圧制御回路CT1を含む。そしてVOUT、C11P、VDD2、C11N、VSSのパッド(1次昇圧用パッド)には、トランジスタTB11、TB12、TB13、TB14のドレイン又はソースが接続される。またC11P、C11Nのパッドには1次昇圧用キャパシタCC1(外付けキャパシタ)が接続される。

## [0106]

図15(B)の期間T1では、1次昇圧制御回路CT1からの昇圧クロックPH2、P

20

30

40

50

H4が共にHレベルになり、トランジスタTB12、TB14がオンになる。また昇圧クロックPH1、PH3がHレベル、Lレベルになり、トランジスタTB11、TB13がオフになる。これにより昇圧用キャパシタCC1の上側電極には昇圧用の基準電源電圧VDD2が供給され、下側電極には接地電源電圧VSSが供給される。従って昇圧用キャパシタCC1には、VDD2とVSSの電圧差に応じた電荷が蓄積される。

### [0107]

図15(B)の期間T2では、1次昇圧制御回路CT1からの昇圧クロックPH2、PH4が共にLレベルになり、トランジスタTB12、TB14がオフになる。また昇圧クロックPH1、PH3がLレベル、Hレベルになり、トランジスタTB11、TB13がオンになる。これにより昇圧用キャパシタCC1の下側電極には基準電源電圧VDD2が供給される。従って昇圧用キャパシタCC1の上側電極(VOUTのパッド)の電圧は、2×VDD2になる。即ちVOUT=2×VDD2の電源電圧が生成される。

#### [0108]

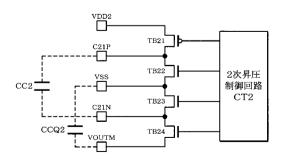

図16(B)に2次昇圧回路の構成例を示す。この2次昇圧回路は、2次昇圧トランジスタであるトランジスタTB21~TB24と2次昇圧制御回路CT2を含む。そしてC21P、C21Nのパッドには2次昇圧用キャパシタCC2が接続される。この2次昇圧回路では、VOUTM=-1×VDD2の電源電圧が生成される。

## [0109]

図17(A)に3次昇圧回路の構成例を示す。この3次昇圧回路は、3次昇圧トランジスタであるトランジスタTB31~TB38と3次昇圧制御回路CT3を含む。そしてC31P、C31Nのパッドと、C32P、C32Nのパッドには、各々、3次昇圧用キャパシタCС31、CC32が接続される。また図17(B)に4次昇圧回路の構成例を示す。この4次昇圧回路は、4次昇圧トランジスタであるトランジスタTB41~TB44と4次昇圧制御回路CT4を含む。そしてС41P、С41Nのパッドには、4次昇圧用キャパシタCС4が接続される。

## [0110]

## 4.3 昇圧制御回路、レギュレータの配置

図14に示すように本実施形態では、1次昇圧トランジスタTR1に昇圧クロックを供給する1次昇圧制御回路CT1は、電源回路ブロックPB内に配置される。一方、3次、4次昇圧トランジスタ(広義にはK次昇圧トランジスタ)TR3、TR4に昇圧クロックを供給する3次、4次昇圧制御回路(広義にはK次昇圧制御回路)CT3、CT4は、パッド配置領域である入力側I/F領域14に配置される。

#### [0111]

即ち図14において、3次、4次昇圧制御回路CT3、CT4を電源回路プロックPB内に設けると、電源回路プロックPBから3次、4次昇圧トランジスタTR3、TR4までの距離が長いため、昇圧クロックの供給線の配線長も長くなり、配線の引き回しにより配線長にバラツキが生じるおそれがある。ところが、前述のように3次、4次昇圧制御回路CT3、CT4は、貫通電流防止のために、そのアクティブ期間がノンオーバラップになる昇圧クロックを生成して、3次、4次昇圧トランジスタTR3、TR4に供給している。従って昇圧クロックの供給線の配線長が長くなったり、配線長にバラツキが生じると、昇圧クロックのアクティブ期間がノンオーバラップにならなくなり、貫通電流などの不具合が生じるおそれがある。特に図13に示すように3次、4次昇圧トランジスタTR3、TR4をD1方向に沿って細長に配置すると、昇圧クロックの供給線の配線長が非常に長くなるため、このような不具合が生じる可能性が高い。

#### [ 0 1 1 2 ]

この点、図14では、3次、4次昇圧制御回路CT3、CT4は、電源回路ブロックPB内ではなく、パッド配置領域である入力側I/F領域14に配置される。従って、3次、4次昇圧制御回路CT3、CT4を、各々、3次、4次昇圧トランジスタTR3、TR4の近く(例えば隣)に配置できる。従って、長い配線長や配線長のバラツキによる不具合の発生を防止できる。

#### [0113]

また図14では、レギュレータRGは、電源回路ブロックPB内に配置される共に、1次昇圧トランジスタTR1とデータドライバブロックDB1の間に配置される。またレギュレータ用パッドPR1、PR2、PR3・・・は、1次昇圧用パッドP11、P12、P13・・・と、3次、4次昇圧用パッド(図11に示すK次昇圧用パッドPK1、PK2、PK3・・・)の間に配置される。

#### [0114]

即ち図15(A)に示すようにレギュレータRGは、1次昇圧電圧である電源電圧VOUTを調整し、調整電圧であるデータドライバ用の電源電圧VDDHSをデータドライバブロックDB1に供給している。従って図14のように、レギュレータRGを1次昇圧トランジスタTR1とデータドライバブロックDB1の間に設ければ、1次昇圧トランジスタTR1とデータドライバブロックDB1の間に設ければ、1次昇圧トスタTR1で生成された電源電圧VOUTをレギュレータRGに供給し、レギュレータRGで調整された電源電圧VDDHSをデータドライバDB1に供給するというように、無駄のないショートパスの経路で電源電圧を供給できる。特に電源電圧を供給する電源線の上できる。またデータドライバブロックDB1の消費電力は大きいため、図14のようなにできる。またデータドライバDB1になるべく近づけることで、寄生配線抵抗による電源電圧低下も抑制できる。また図14のようなパッド配置にすれば、レギュレータRGで生成された調整電圧をパッドPR1、PR2、PR3・・・に接続したり、レータRGで生成された調整電圧をパッドPR1、PR2、PR3・・・を介して外部に出力してモニタできる。従ってパッド配置領域の無駄の無い利用が可能になる。

#### [ 0 1 1 5 ]

4.4 応力の均一化

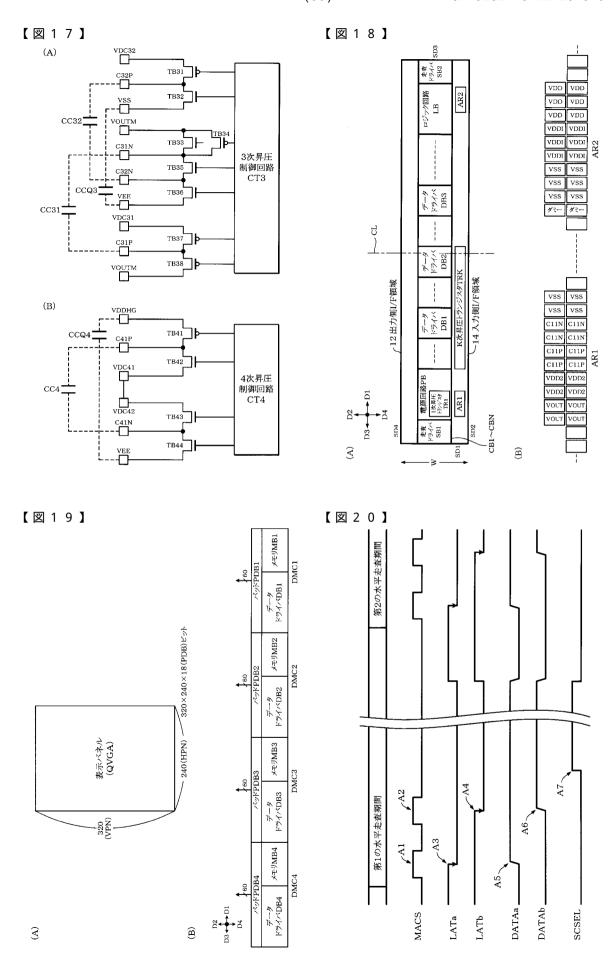

図18(A)に示すように本実施形態では、電源回路ブロックPBのD4方向側にある第1のエリアAR1に、電源回路ブロックPB用のパッドが配置される。例えば、電源回路ブロックPB内の1次昇圧トランジスタTR1のD4方向側(直下)に、電源回路ブロックPB用パッドとなる1次昇圧用パッドが配置される。

#### [0116]

また本実施形態では、集積回路装置のD2方向に沿った中心線CLを基準に、第1のエリアAR1と線対称(略線対称の場合を含む)の位置にある第2のエリアAR2にも、応力均一化用(応力緩和用)に疑似配列されたパッドが配置される。

## [0117]

具体的には図18(B)に示すように、電源回路ブロックPBの下側のエリアAR1では、D2方向に沿って2個(広義にはI個。Iは2以上の整数)ずつ配列された電源回路ブロック用パッドの列が、10列(広義には複数列)に亘って配置される。例えばI=2、J=10とすれば、エリアAR1にはI行J列(2行10列)の電源回路ブロック用パッドが配置される。即ちエリアAR1の両側では1行(広義にはG行。GはG<I・1となる自然数)のパッドしか配置されていないのに、エリアAR1では2行(I行)のパッドが配置されている。

### [0118]

一方、エリアAR1と線対称の位置にあるエリアAR2(ロジック回路ブロックLBの下側)においても、D2方向に沿って2個(I個)ずつ配列されたパッドの列が、10列(複数列)に亘って配置される。例えばI=2、J=10とすれば、エリアAR2にも応力均一化用にI行J列(2行10列)のパッドがされる。即ちエリアAR2の両側では1行(G行)のパッドしか配置されていないのに、エリアAR2では2行(I行)のパッドが配置されている。

### [0119]

10

20

30

40

列(I行H列)のC11Pのパッド、2行2列のC11Nのパッド、2行2列のVSSのパッドが配置される。このようにしてエリアAR1には、合計で2行10列(I行J列)の1次昇圧用パッドが配置される。

### [0120]

そして、これらの2行2列の1次昇圧用パッドは図示しない金属配線で電気的に接続される。例えば2行2列の4個のVOUTのパッドは金属配線で接続される。同様に2行2列のVDD2、C11P、C11N、VSSのパッドも金属配線で接続される。そして図16(A)に示すように、これらの2行2列のVOUT、VDD2、C11P、C11N、VSSのパッドは、1次昇圧トランジスタTB11、TB12、TB13、TB14のドレイン又はソースに接続される。即ち図18(B)では、1個の1次昇圧トランジスタTB11、TB12、TB13、TB14のドレイン又はソースに対して、2行2列の複数個の1次昇圧用パッド(VOUT、VDD2、C11P、C11N、VSSのパッド)が接続されていることになる。

## [0121]

このように1個の1次昇圧トランジスタのドレイン又はソースに対して複数個(4個)の1次昇圧用パッドを接続すれば、集積回路装置を実装したときのパッドでの接触抵抗値を減少できる。具体的には集積回路装置を例えばCOG(Chip On Glass)実装した場合のバンプ等での接触抵抗値を減少できる。そして、このように接触抵抗値が減少すれば、1次昇圧回路によるチャージポンプ動作時の寄生抵抗値が減り、1次昇圧回路の昇圧動作の効率(電源供給能力)を高めることができる。

### [0122]

しかしながら、エリアAR1において図18(B)に示すようなパッド配置を行うと、 集積回路装置の左側と右側とで応力の掛かり方が均一にならず、結局、接触抵抗値が上昇 してしまうおそれがある。特に本実施形態のように細長の集積回路装置では、応力の不均 一を原因として接触抵抗値が上昇するおそれが大きい。

### [0123]

そこで図18(B)では、エリアAR1の線対称の位置にあるエリアAR2においても、アリアAR1と同様のパッド配置を行っている。即ちエリアAR1においてI行」列にパッドを配置した場合には、図18(B)に示すように、エリアAR2においてもI行」列にパッドを疑似配置する。このようにすることで、集積回路装置を実装したときに、集積回路装置の左側と右側とで応力を均一化でき、応力の不均一を原因として接触抵抗値が上昇する事態を効果的に防止できる。

#### [0124]

なおエリアAR1、AR2でのパッド配置は完全に対称にする必要はなく、応力を均一化できる程度に対称であればよい。例えばエリアAR1とAR2でパッドの列数を異ならせる変形実施も可能である。また図18(B)では、I=2、J=10の場合を示しているが、本実施形態はこれに限定されない。例えばI=2であってもよいし、Jは10以外であってもよい。

## [0125]

5. データドライバブロック、メモリブロックの詳細

## 5 . 1 ブロック分割

図19(A)に示すように表示パネルが、垂直走査方向(データ線方向)での画素数が VPN=320であり、水平走査方向(走査線方向)での画素数がHPN=240である QVGAのパネルであったとする。また1画素分の画像(表示)データのビット数 PDBが、R、G、Bの各々が6ビットであり、PDB=18ビットであったとする。この場合には、表示パネルの1フレーム分の表示に必要な画像データのビット数は、 $VPN \times HPN \times PDB=320 \times 240 \times 18$ ビットになる。従って集積回路装置のメモリは、少なくとも320 ×240 ×18ビット分の画像データを記憶することになる。またデータドライバは、1水平走査期間毎(1本の走査線が走査される期間毎)に、HPN=240本分のデータ信号(240 ×18ビット分の画像データに対応するデータ信号)を表示パネ

10

20

30

40

ルに対して出力する。

## [0126]

そして図19(B)では、データドライバは、DBN=4個のデータドライバブロックDB1~DB4に分割される。またメモリも、MBN=DBN=4個のメモリブロックMB1~MB4に分割される。即ち、例えばデータドライバブロック、メモリブロック、パッドブロックをマクロセル化した4個のドライバマクロセルDMC1、DMC2、DMC3、DMC4がD1方向に沿って配置される。従って、各データドライバブロックDB1~DB4は、1水平走査期間毎にHPN/DBN=240/4=60本分のデータ信号を表示パネルに出力する。また各メモリブロックMB1~MB4は、(VPN×HPN×PDB)/MBN=(320×240×18)/4ビット分の画像データを記憶する。

[0127]

5.2 1水平走査期間に複数回読み出し

図 1 9 ( B ) では、各データドライバブロック D B 1 ~ D B 4 は、 1 水平走査期間に 6 0 本分 ( R 、 G 、 B を 3 本とすると、 6 0 × 3 = 1 8 0 本 ) のデータ信号を出力する。従って D B 1 ~ D B 4 に対応するメモリブロック M B 1 ~ M B 4 からは、 1 水平走査期間毎に 2 4 0 本分のデータ信号に対応する画像データを読み出す必要がある。

### [0128]

しかしながら、1水平走査期間毎に読み出す画像データのビット数が増えると、D2方向に並ぶメモリセル(センスアンプ)の個数を多くする必要が生じる。この結果、集積回路装置のD2方向での幅Wが大きくなり、チップのスリム化が妨げられる。またワード線WLが長くなり、WLの信号遅延の問題も招く。

[0129]

そこで本実施形態では、各メモリブロックMB1~MB4から各データドライバブロックDB1~DB4に対して、各メモリブロックMB1~MB4に記憶される画像データを 1水平走査期間において複数回(RN回)読み出す手法を採用している。

[0130]

例えば図20ではA1、A2に示すように、1水平走査期間においてRN=2回だけメモリアクセス信号MACS(ワード選択信号)がアクティブ(ハイレベル)になる。これにより各メモリブロックから各データドライバブロックに対して画像データが1水平走査期間においてRN=2回読み出される。すると、データドライバブロック内に設けられた図21のデータドライバDRa、DRbが含むデータラッチ回路が、A3、A4に示すラッチ信号LATa、LATbに基づいて、読み出された画像データをラッチする。そしてデータドライバDRa、DRbが含むD/A変換回路が、ラッチされた画像データのD/A変換を行い、DRa、DRbが含む出力回路が、D/A変換により得られたデータ信号DATAa、DATAbをA5、A6に示すようにデータ信号出力線に出力する。その後、A7に示すように、表示パネルの各画素のTFTのゲートに入力されて保持される。

[0131]

なお図20では第1の水平走査期間で画像データを2回読み出し、同じ第1の水平走査期間においてデータ信号DATAa、DATAbをデータ信号出力線に出力している。しかしながら、第1の水平走査期間で画像データを2回読み出してラッチしておき、次の第2の水平走査期間で、ラッチされた画像データに対応するデータ信号DATAa、DATAbをデータ信号出力線に出力してもよい。また図20では、読み出し回数RN=2である場合を示しているが、RN 3であってもよい。

[0132]

図20の手法によれば、図21に示すように、各メモリブロックから30本分のデータ信号に対応する画像データが読み出され、各データドライバDRa、DRbが30本分のデータ信号を出力する。これにより各データドライバブロックからは60本分のデータ信号が出力される。このように図20では、各メモリブロックからは、1回の読み出しにおいて30本分のデータ信号に対応する画像データを読み出せば済むようになる。従って1

10

20

30

40

20

30

40

50

水平走査期間に1回だけ読み出す手法に比べて、図21のD2方向でのメモリセル、センスアンプの個数を少なくすることが可能になる。この結果、集積回路装置のD2方向での幅を小さくでき、超スリムな細長チップを実現できる。特に1水平走査期間の長さは、QVGAの場合は52 $\mu$ sec程度である。一方、メモリの読み出し時間は例えば40nsec程度であり、52 $\mu$ secに比べて十分に短い。従って、1水平走査期間での読み出し回数を1回から複数回に増やしたとしても、表示特性に与える影響はそれほど大きくない。

## [0133]

また図19(A)はQVGA(320×240)の表示パネルであるが、1水平走査期間での読み出し回数を例えばRN=4にすれば、VGA(640×480)の表示パネルに対応することも可能になり、設計の自由度を増すことができる。

[0134]

なお1水平走査期間での複数回読み出しは、各メモリブロック内で異なる複数のワード線をローアドレスデコーダ(ワード線選択回路)が1水平走査期間において選択する第1の手法で実現してもよいし、各メモリブロック内で同じワード線をローアドレスデコーダ(ワード線選択回路)が1水平走査期間において複数回選択する第2の手法で実現してもよい。或いは第1、第2の手法の両方の組み合わせにより実現してもよい。

[0135]

5.3 データドライバ、ドライバセルの配置

図 2 1 にデータドライバと、データドライバが含むドライバセルの配置例を示す。図 2 1 に示すように、データドライバブロックは、D 1 方向に沿って並んで配置される複数のデータドライバDRa、DRb(第1~第mのデータドライバ)を含む。また各データドライバDRa、DRbは、複数の30個(広義にはQ個)のドライバセルDRC1~DRC30を含む。

[0136]

データドライバDRaは、メモリブロックのワード線WL1aが選択され、図20のA1に示すように1回目の画像データがメモリブロックから読み出されると、A3に示すラッチ信号LATaに基づいて、読み出された画像データをラッチする。そしてラッチされた画像データのD/A変換を行い、1回目の読み出し画像データに対応するデータ信号DATAaを、A5に示すようにデータ信号出力線に出力する。

[0137]

一方、データドライバDRbは、メモリブロックのワード線WL1bが選択され、図20のA2に示すように2回目の画像データがメモリブロックから読み出されると、A4に示すラッチ信号LATbに基づいて、読み出された画像データをラッチする。そしてラッチされた画像データのD/A変換を行い、2回目の読み出し画像データに対応するデータ信号DATAbを、A6に示すようにデータ信号出力線に出力する。

[0138]

このようにして、各データドライバDRa、DRbが30個の画素に対応する30本分のデータ信号を出力することで、合計で60個の画素に対応する60本分のデータ信号が出力されるようになる。

[0139]

図21のように、複数のデータドライバDRa、DRbをD1方向に沿って配置(スタック)するようにすれば、データドライバの規模の大きさが原因になって集積回路装置のD2方向での幅Wが大きくなってしまう事態を防止できる。またデータドライバは、表示パネルのタイプに応じて種々の構成が採用される。この場合にも、複数のデータドライバをD1方向に沿って配置する手法によれば、種々の構成のデータドライバを効率良くレイアウトすることが可能になる。なお図21ではD1方向でのデータドライバの配置数が2個である場合を示しているが、配置数は3個以上でもよい。

[0140]

また図21では、各データドライバDRa、DRbは、D2方向に沿って並んで配置さ

れる30個(Q個)のドライバセルDRC1~DRC30を含む。ここでドライバセルDRC1~DRC30の各々は、1画素分の画像データを受ける。そして1画素分の画像データのD/A変換を行い、1画素分の画像データに対応するデータ信号を出力する。このドライバセルDRC1~DRC30の各々は、データのラッチ回路や、図10(A)のDAC(1画素分のDAC)や、図10(B)(C)の出力部SQを含むことができる。

[0141]

そして図21において、表示パネルの水平走査方向の画素数(複数の集積回路装置により分担して表示パネルのデータ線を駆動する場合には、各集積回路装置が受け持つ水平走査方向の画素数)をHPNとし、データドライバブロックのブロック数(ブロック分割数)をDBNとし、ドライバセルに対して1水平走査期間に入力される画像データの入力回数をINとしたとする。なおINは、図20で説明した1水平走査期間での画像データの読み出し回数RNと等しくなる。この場合に、D2方向に沿って並ぶドライバセルDRC1~DRC30の個数Qは、Q=HPN/(DBN×IN)と表すことができる。図21の場合には、HPN=240、DBN=4、IN=2であるため、Q=240/(4×2)=30個になる。

[0142]

なおドライバセルDRC1~DR30のD2方向での幅(ピッチ)をWDとした場合に、第1~第Nの回路ブロックCB1~CBNのD2方向での幅WB(最大幅)は、QxWD WB<(Q+1)xWDと表すことができる。またメモリブロックが含む周辺回路部分(ローアドレスデコーダRD、配線領域等)のD2方向での幅をWPCとした場合には、QxWD WB<(Q+1)xWD+WPCと表すことができる。

[0143]

また表示パネルの水平走査方向の画素数をHPNとし、1画素分の画像データのビット数をPDBとし、メモリブロックのブロック数をMBN(=DBN)とし、1水平走査期間においてメモリブロックから読み出される画像データの読み出し回数をRNとしたとする。この場合に、センスアンプブロックSABにおいてD2方向に沿って並ぶセンスアンプ(1ビット分の画像データを出力するセンスアンプ)の個数Pは、P=(HPNxPDB)/(MBNxRN)と表すことができる。図21の場合には、HPN=240、PDB=18、MBN=4、RN=2であるため、P=(240x18)/(4x2)=540個になる。なお個数Pは、有効メモリセル数に対応する有効センスアンプ数であり、ダミーメモリセル用のセンスアンプ等の有効ではないセンスアンプの個数は含まない。

[0144]

またセンスアンプブロックSABが含む各センスアンプのD2方向での幅(ピッチ)をWSとした場合には、センスアンプブロックSAB(メモリブロック)のD2方向での幅WSABは、WSAB=PxWSと表すことができる。そして、回路ブロックCB1~CBNのD2方向での幅WB(最大幅)は、メモリブロックが含む周辺回路部分のD2方向での幅をWPCとした場合には、PxWS WB<(P+PDB)xWS+WPCと表すこともできる。

[0145]

6.電子機器

図22(A)(B)に本実施形態の集積回路装置10を含む電子機器(電気光学装置)の例を示す。なお電子機器は図22(A)(B)に示されるもの以外の構成要素(例えばカメラ、操作部又は電源等)を含んでもよい。また本実施形態の電子機器は携帯電話機には限定されず、デジタルカメラ、PDA、電子手帳、電子辞書、プロジェクタ、リアプロジェクションテレビ、或いは携帯型情報端末などであってもよい。

[0146]

図 2 2 ( A ) ( B ) においてホストデバイス 4 1 0 は、例えば M P U ( Micro Processo r Unit ) 、ベースバンドエンジン(ベースバンドプロセッサ)などである。このホストデバイス 4 1 0 は、表示ドライバである集積回路装置 1 0 の制御を行う。或いはアプリケーションエンジンやベースバンドエンジンとしての処理や、圧縮、伸長、サイジングなどの

10

20

30

40

グラフィックエンジンとしての処理を行うこともできる。また図22(B)の画像処理コントローラ(表示コントローラ)420は、ホストデバイス410に代行して、圧縮、伸長、サイジングなどのグラフィックエンジンとしての処理を行う。

### [0147]

表示パネル400は、複数のデータ線(ソース線)と、複数の走査線(ゲート線)と、データ線及び走査線により特定される複数の画素を有する。そして、各画素領域における電気光学素子(狭義には、液晶素子)の光学特性を変化させることで、表示動作を実現する。この表示パネル400は、TFT、TFDなどのスイッチング素子を用いたアクティブマトリクス方式のパネルにより構成できる。なお表示パネル400は、アクティブマトリクス方式以外のパネルであってもよいし、液晶パネル以外のパネルであってもよい。

[0148]

図22(A)の場合には、集積回路装置10としてメモリ内蔵のものを用いることができる。即ちこの場合には集積回路装置10は、ホストデバイス410からの画像データを、一旦内蔵メモリに書き込み、書き込まれた画像データを内蔵メモリから読み出して、表示パネルを駆動する。一方、図22(B)の場合には、集積回路装置10としてメモリ非内蔵のものを用いることができる。即ちこの場合には、ホストデバイス410からの画像データは、画像処理コントローラ420の内蔵メモリに書き込まれる。そして集積回路装置10は、画像処理コントローラ420の制御の下で、表示パネル400を駆動する。

[0149]

なお、上記のように本実施形態について詳細に説明したが、本発明の新規事項および効果から実体的に逸脱しない多くの変形が可能であることは当業者には容易に理解できるであろう。従って、このような変形例はすべて本発明の範囲に含まれるものとする。例えば、明細書又は図面において、少なくとも一度、より広義または同義な異なる用語(第1のインターフェース領域、第2のインターフェース領域、K次等)と共に記載された用語(出力側I/F領域、入力側I/F領域、3次・4次等)は、明細書又は図面のいかなる箇所においても、その異なる用語に置き換えることができる。また昇圧トランジスタの配置等に関する本実施形態の手法は、図3とは異なる配置・構成の集積回路装置にも適用できる。

## 【符号の説明】

## [0150]

CB1~CBN 第1~第Nの回路ブロック、PB 電源回路ブロック、

TR1 1次昇圧トランジスタ、TRK、 K次昇圧トランジスタ、

P 1 1 ~ P 1 3 1 次昇圧用パッド、P K 1 ~ P K 8 K 次昇圧用パッド、

CT1~CT4 1次~4次昇圧制御回路、

TR1~TR4 1次~4次昇圧トランジスタ、DB1 データドライバブロック、

- 10 集積回路装置、12 出力側I/F領域、14 入力側I/F領域、

- 20 メモリ、22 メモリセルアレイ、24 ローアドレスデコーダ、

- 26 カラムアドレスデコーダ、28 ライト/リード回路、

- 40 ロジック回路、42 制御回路、44 表示タイミング制御回路、

- 46 ホストインターフェース回路、48 RGBインターフェース回路、

- 50 データドライバ、52 データラッチ回路、54 D/A変換回路、

- 56 出力回路、70 走査ドライバ、72 シフトレジスタ、

- 7.3 走査アドレス生成回路、7.4 アドレスデコーダ、7.6 レベルシフタ、

- 78 出力回路、90 電源回路、92 昇圧回路、94 レギュレータ回路、

- 96 VCOM生成回路、98 制御回路、110 階調電圧生成回路、

- 112 選択用電圧生成回路、114 階調電圧選択回路、116 調整レジスタ

20

10

30

30

【図14】

【図15】

【図16】

(B)

【図21】 【図22】 (A) (B) WPC WB -400 -400 メモリセルアレイ ローアドレスデコーダRD 表示パネル 表示パネル PTTM HTSP メモリブロック -10 -10 集積回路装置 (表示ドライバ) メモリ内蔵 集積回路装置 (表示ドライバ) メモリ非内蔵  $P = \frac{\frac{\text{HPN} \times \text{PDB}}{\text{MBN} \times \text{RN}}}{= 540 \text{MB}}$ -420 410 画像処理コントローラ ドライバセル DRC30 ホストデバイス ( ベースバンド ) 、 エンジン ) データドライバブロック -410  $Q = \frac{\text{HPN}}{\text{DBN} \times \text{IN}} = 30/18$ ホストデバイス (ベースバンド エンジン ドライバセル DRC30 ライバセルDRC3 D2

## フロントページの続き

(51) Int.CI. F I

G 0 9 G 3/20 6 1 1 H G 0 9 G 3/20 6 1 2 P G 0 2 F 1/133 5 3 5 G 0 2 F 1/133 5 5 0 G 0 9 G 3/20 6 2 1 M

(72)発明者 森口 昌彦

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

(72)発明者 前川 和広

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

(72)発明者 熊谷 敬

東京都日野市日野421-8 エプソントヨコム株式会社内

## 審査官 瀧内 健夫

(56)参考文献 特開2003-330426(JP,A)

特開2002-006334(JP,A)

特開2002-244624(JP,A)

(58)調査した分野(Int.CI., DB名)

$H\ 0\ 1\ L$   $2\ 7\ /\ 0\ 4$

H01L 21/822

G 0 9 G 3 / 0 0 - 3 / 3 8

G02F 1/133